1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

#### DESCRIPTION

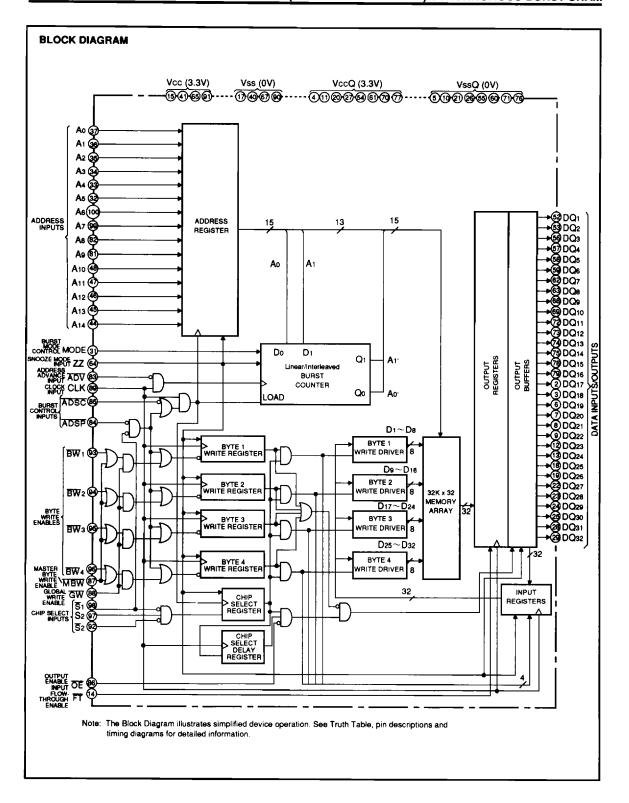

The M5M5V1132FP is a family of 1M bit synchronous SRAMs organized as 32768-words of 32-bit. The M5M5V1132FP provides a high speed secondary cache solution for microprocessors. The design integrates a 2-bit burst counter, input and output registers with the ultra fast 1M bit SRAM on a single monolithic circuit. This design reduces component count of cache data RAM solutions. Mitsubishi's SRAMs are fabricated with high-performance, low power CMOS technology, providing greater reliability. This device operates on a single 3.3V power supply and are directly LVTTL compatible.

**FEATURES**

| <ul> <li>Access times /Cycle times</li> </ul> |

|-----------------------------------------------|

| M5M5V1132FP-6 5.5ns/10.0ns (100MHz)           |

| M5M5V1132FP-7, -7L 7.0ns/13.3ns (75MHz)       |

| M5M5V1132FP-8, -8L 8.0ns/15.0ns (66MHz)       |

| M5M5V1132FP-10, -10L 10.0ns/16.7ns (60MHz)    |

| ◆ Low power dissipation                       |

| Active (66MHz) 415mW (typ)                    |

| Stand-by (-6, -7, -8, -10) 0.7mW (typ)        |

| Stand-by (-7L, -8L, -10L)                     |

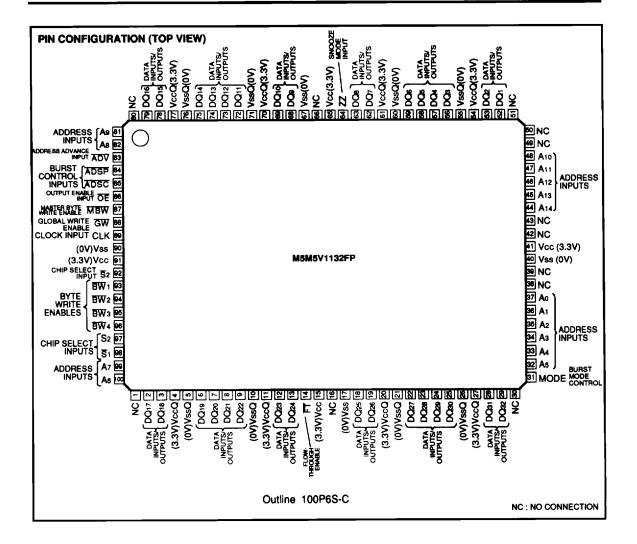

Package

100pin QFP, Body Size (14.0×20.0 mm2)

Pin Pitch (0.65 mm)

- ullet Single 3.3V power supply (3.13  $\sim$  3.60V)

- Fully registered inputs and outputs (Pipeline operation)

- Global write control or individual byte write control

- MODE pin allows either liner or interleaved burst

- Snooze mode pin (ZZ) for power down

- CLK stopped stand by mode.

- 32-bit wide data I/O

#### **APPLICATION**

486/Pentium<sup>TM</sup>/PowerPC<sup>TM</sup> processor second level caches

#### FUNCTION

Synchronous circuitry allows for precise cycle control triggered by a positive edge clock transition. Synchronous signals include: all addresses, all data inputs, all chip selects (\$1, \$2, \$2), burst control inputs (\$\overline{ADSC}, \overline{ADSP}, \overline{ADV}) and write enables (\$\overline{MBW}, \overline{GW}, \overline{BW}, \overline{BW}, \overline{BW}, \overline{BW}, \overline{SW}, \overline{BW}, \overline{SW}, \overline{BW}, \overline{SW}, \overline{BW}, \overline{SW}, \ov

The write operation can be performed by two methods. The global write enable ( $\overline{GW}$ ) will perform a write to all 32 bits. Byte wide writes are controlled by the master byte write enable ( $\overline{MWB}$ ) and the 4 individual byte write enables ( $\overline{BW1}\sim\overline{BW4}$ ). The byte write cycle will write from one to four bytes. The write cycle is internally self-timed, eliminating the complex signal generation of an off chip write.

Asynchronous signals are output enable (OE), snooze mode pin (ZZ) and clock (CLK). The HIGH input of ZZ pin puts the SRAM in the power-down state. When ZZ is pulled to LOW, the SRAM normally operates after 30ns of the wake up period.

When CLK is stopped and all inputs (Address, Burst control, CLK etc.) are fixed in CMOS level, the SRAM becomes in the power-down state that is called "CLK stopped stand-by mode". During CLK stopped stand-by mode, power supply current is almost same as snooze mode even if the SRAM is selected. When CLK is active again, the SRAM immediately recovers from CLK stopped stand-by mode to normal operation mode.

The burst mode control (MODE), and the flow-through enable (FT) are DC operated pins. MODE pin will allow the choice of either an interleaved burst, or a linear burst. FT pin normally is pulled HIGH. When FT is pulled LOW, the SRAM changes non-pipelined type with flow-through output. FT LOW input is only used for a test mode.

The burst operation is initiated by either address status processor (ADSP) or address status controller (ADSC). The burst advance pin (ADV) controls subsequent burst addresses.

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

## PIN FUNCTIONS

| Pin                       | Name                                     | Function                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ao~A14                    | Synchronous<br>Address Inputs            | These inputs are registered and must meet the setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                                                                       |

| MBW                       | Synchronous Master<br>Byte Write Enables | This active LOW input is used to enable the individual byte write operation. The individual byte write operation is performed when MBW is LOW and GW is HIGH. The global write operation (a write to all 32 bits) is performed when GW is LOW.                                                                                                                                          |

| GW                        | Synchronous Global<br>Write Enables      | This active LOW input is used to enable the global write operation (a write to all 32 bits) and must meet the setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                       |

| BW 1, BW 2,<br>BW 3, BW 4 | Synchronous Byte<br>Write Enables        | These active LOW inputs allow individual bytes to be written and must meet the setup and hold times around the rising edge of CLK. A byte write enables is LOW for a WRITE cycle and HIGH for a READ cycle. BW1 controls DQ1~DQ8. BW2 controls DQ9~DQ16. BW3 controls DQ17~DQ24. BW4 controls DQ25~DQ32. Data I/O are tristated if any of these four inputs are LOW.                    |

| CLK                       | Clock Input                              | This signal latches the address, data, chip enables, byte write enables and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                                                              |

| <u>\$</u> 1               | Synchronous<br>Chip Select Input         | This active LOW input is used to enable the device and conditions internal use of ADSP. This input is sampled only when a new external address is loaded.                                                                                                                                                                                                                               |

| ₹2                        | Synchronous<br>Chip Select Input         | This active LOW input is used to enable the device. This input is sampled only when a new external address is loaded. This input can be used for memory depth expansion.                                                                                                                                                                                                                |

| S2                        | Synchronous<br>Chip Select Input         | This active HIGH input is used to enable the device. This input is sampled only when a new external address is loaded. This input can be used for memory depth expansion.                                                                                                                                                                                                               |

| ŌĒ                        | Output Enable Input                      | This active LOW asynchronous input enables the data I/O output drivers.                                                                                                                                                                                                                                                                                                                 |

| DQ1∼DQ32                  | Data I/O                                 | Byte 1 is DQ1~DQe; Byte 2 is DQ9~DQ16; Byte 3 is DQ17~DQ24; Byte 4 is DQ25~DQ32.  Input data must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                              |

| ZZ                        | Snooze Mode Input                        | This asynchronous input allows the selection either normal operation mode or snooze mode that the SRAM is in the powerdown state even if CLK is operated. This active HIGH asynchronous input puts the SRAM in the snooze mode. When ZZ=HIGH, Input leak current flows to this pin. When this pin is pulled to LOW or NC, the SRAM normally operates.                                   |

| MODE                      | Burst Mode Control                       | This DC operated pin allows the choice of either a interleaved burst or a linear burst. If this pin is HIGH or NC, an interleaved burst occurs. When this pin is tied LOW, a linear burst occurs, and input leak current flows.                                                                                                                                                         |

| FT                        | Flow-through Enable                      | This DC operated pin is used as a test mode pin. Normally, this pin is pulled HIGH or NC. When this pin is tied LOW, the SRAM changes non-pipelined type with flow-through output, and input leak current flows.                                                                                                                                                                        |

| ADSP                      | Synchronous<br>Address Status Processor  | This active LOW input interrupts any ongoing burst, causing a new external address to be latched. A READ is performed using the new address, independent of the byte write enables and ADSC but dependent upon S2 and S2. ADSP is ignored if S1 is HIGH. Power-down state is entered if S2 is LOW or S2 is HIGH.                                                                        |

| ADSC                      | Synchronous<br>Address Status Controller | This active LOW input interrupts any ongoing burst and causes a new external address to be latched. A READ or WRITE is performed using the new address if all chip enables are active. Power-down state is entered if one or more chip enables are inactive.                                                                                                                            |

| ADV                       | Synchronous<br>Address Advance           | This active LOW input is used to advance the internal burst counter, controlling burst access after the external address is loaded. A HIGH on this pin effectively causes wait states to be generated (no address advance). This pin must be HIGH at the rising edge of the first clock after an ADSP cycle is initiated if a WRITE cycle is desired (to ensure use of correct address) |

| Vcc                       | Vcc                                      | Power Supply (3.3V)                                                                                                                                                                                                                                                                                                                                                                     |

| Vss                       | Vss                                      | Ground (0V)                                                                                                                                                                                                                                                                                                                                                                             |

| VccQ                      | VccQ                                     | I/O Buffer Supply (3.3V)                                                                                                                                                                                                                                                                                                                                                                |

| VssQ                      | VssQ                                     | I/O Buffer Ground (0V)                                                                                                                                                                                                                                                                                                                                                                  |

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

#### **DC OPERATED TRUTH TABLE**

| Name | input status | Operation                      |

|------|--------------|--------------------------------|

| MODE | H or NC      | Interleaved Burst Sequence     |

| MODE | L            | Linear Burst Sequence          |

|      | H or NC      | Pipelined SRAM                 |

| FT   | L            | Non-pipelined SRAM (Test mode) |

- Note 1. MODE and FT are DC operated pins.

2. H means logic HIGH or NC. L means logic LOW. NC meons No-Connection

- 3. Normally, FT is pulled to HIGH or NC. FT LOW input is only used for a test mode.

- 4. See BURST SEQUENCE TABLE about Interleaved and Linear Burst Sequence.

#### **BURST SEQUENCE TABLE**

#### Interleaved Burst Sequence (when MODE = HIGH or NC)

| Operation                            | A14 -A2         | <b>A</b> 1 | <b>A</b> o |

|--------------------------------------|-----------------|------------|------------|

| First access, latch external address | A14 -A2         | A1         | Ao         |

| Second access (first burst address)  | latched A14 -A2 | latched A1 | latched ⊼o |

| Third access (second burst address)  | latched A14 -A2 | latched Ti | latched Ao |

| Fourth access (third burst address)  | latched A14 -A2 | latched A1 | latched To |

#### Linear Burst Sequence (when MODE = LOW)

| Operation                            | A14 -A2         | A1, A0 |      |      |      |

|--------------------------------------|-----------------|--------|------|------|------|

| First access, latch external address | A14 -A2         | 0, 0   | 0, 1 | 1, 0 | 1, 1 |

| Second access (first burst address)  | latched A14 -A2 | 0, 1   | 1, 0 | 1, 1 | 0, 0 |

| Third access (second burst address)  | latched A14 -A2 | 1, 0   | 1, 1 | 0, 0 | 0, 1 |

| Fourth access (third burst address)  | latched A14 -A2 | 1, 1   | 0, 0 | 0, 1 | 1, 0 |

Note 5. The burst sequence wraps around to its initial state upon completion.

#### SYNCHRONOUS TRUTH TABLE

| ছ1 | ₹2 | S2 | ADSP | ADSC | ADV | Write | CLK | Address<br>used | Operation                    |

|----|----|----|------|------|-----|-------|-----|-----------------|------------------------------|

| Н  | ×  | Х  | Х    | L    | Х   | Х     | L-H | None            | Deselected Cycle, Power-down |

| L  | Х  | L  | L    | Х    | Х   | Х     | L-H | None            | Deselected Cycle, Power-down |

| L  | Н  | Х  | L    | Х    | Х   | X     | L-H | None            | Deselected Cycle, Power-down |

| L  | Х  | L  | X    | L    | Х   | Х     | L-H | None            | Deselected Cycle, Power-down |

| L  | Н  | Х  | Х    | L    | Х   | Х     | L-H | None            | Deselected Cycle, Power-down |

| L  | L  | Н  | L    | Х    | Х   | X     | L-H | External        | READ Cycle, Begin Burst      |

| L  | L  | Н  | Н    | L    | Х   | L     | L-H | External        | WRITE Cycle, Begin Burst     |

| L  | L  | Н  | Н    | L    | Х   | Н     | L-H | External        | READ Cycle, Begin Burst      |

| Х  | X  | Х  | Н    | Н    | L   | Н     | L-H | Next            | READ Cycle, Continue Burst   |

| Н  | Х  | Х  | х    | Н    | L   | н     | L-H | Next            | READ Cycle, Continue Burst   |

| Х  | Х  | Х  | Н    | Н    | L   | L     | L-H | Next            | WRITE Cycle, Continue Burst  |

| Н  | Х  | Х  | Х    | Н    | L   | L     | L-H | Next            | WRITE Cycle, Continue Burst  |

| Х  | Х  | Х  | Н    | Н    | Н   | Н     | L-H | Current         | READ Cycle, Suspend Burst    |

| Н  | Х  | Х  | Х    | Н    | Н   | Н     | L-H | Current         | READ Cycle, Suspend Burst    |

| Х  | х  | х  | Н    | Н    | Н   | L     | L-H | Current         | WRITE Cycle, Suspend Burst   |

| Н  | Х  | Х  | Х    | Н    | Н   | L     | L-H | Current         | WRITE Cycle, Suspend Burst   |

Note 6. X means "don't care". H means logic HIGH. L means logic LOW.

- 7. Write =L means "WRITE" operation in WRITE TRUTH TABLE.

- Write =H means "READ" operation in WRITE TRUTH TABLE.

- 8. All inputs in this table must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 9. ADSP LOW always initiates an internal READ at the L-H edge of CLK.

- 10. Operation finally depends on status of asynchronous input pins (ZZ and  $\overline{\text{OE}}$ ). See ASYNCHRONOUS TRUTH TABLE.

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

#### WRITE TRUTH TABLE

| gw | WBW | BW <sub>1</sub> | BW2 | BW3 | BW4 | Operation         |

|----|-----|-----------------|-----|-----|-----|-------------------|

| Н  | Н   | Х               | Х   | X   | Х   | READ              |

| Н  | L   | H               | H   | Η   | Н   | READ              |

| Н  | L   | L               | Н   | Н   | Н   | WRITE BYTE 1      |

| Н  | L   | Н               | L   | Н   | Н   | WRITE BYTE 2      |

| н  | L   | Н               | Н   | Ĺ   | Н   | WRITE BYTE 3      |

| Н  | L   | Ή               | H   | Н   | L   | WRITE BYTE 4      |

| Н  | L   | ٦               | L   | H   | Н   | WRITE BYTE1 and 2 |

| Н  | L   | H               | Н   | Ļ   | Ĺ   | WRITE BYTE3 and 4 |

| Н  | L   | L               | L   | Ĺ   | L   | WRITE ALL BYTE    |

| L  | Х   | X_              | Х   | Х   | Х   | WRITE ALL BYTE    |

#### **ASYNCHRONOUS TRUTH TABLE**

| zz      | ŌĒ | Operation of synchronous truth table | Operation   | I/O Status |

|---------|----|--------------------------------------|-------------|------------|

| Н       | х  | X                                    | Snooze mode | High-Z     |

| L or NC | L  | READ                                 | READ        | Q          |

| L or NC | н  | READ                                 | READ        | High-Z     |

| L or NC | X  | WRITE                                | WRITE       | High-Z - D |

| L or NC | Х  | Deselected                           | Deselected  | High-Z     |

Note 13. For a write operation following a read operation,  $\overline{\text{OE}}$  must be HIGH before the input data required setup time and held HIGH through the input data hold time.

- 14. In I/O STATUS, Q means output data during a read cycle, and D means input data during a write cycle.

15. "Snooze mode" means power down state of which stand-by current does not depend on cycle time.

16. "Deselected" means power down state of which stand-by current depends on cycle time.

17. When ZZ is pulled to LOW, the SRAM normally operates after 30ns of the wake up period.

Note 11. X means "don't care". H means logic HIGH. L means logic LOW.

12. All inputs in this table must meet setup and hold ties around the rising edge (LOW to HIGH) of CLK.

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol     | Parameter                  | Conditions          | Ratings                      | Unit |

|------------|----------------------------|---------------------|------------------------------|------|

| Vcc        | Power supply voltage       |                     | -2.0 + ~4.6                  | ٧    |

| Veca       | I/O buffer supply voltage  | Mish seemed to OND  | -2.0 + ∼Vcc+0.5<br>(max 4.6) | ٧    |

| VI         | Input voltage              | With respect to GND | -2.0 + ∼Vcc+0.5<br>(max 4.6) | ٧    |

| Vo         | Output voltage             |                     | -2.0 • ~4.6                  | ٧    |

| Pa         | Maximum power dissipation  |                     | 1.2                          | W    |

| Торг       | Operating temperature      |                     | 0~70                         | r    |

| Tstg(bias) | Storage temperature (bias) |                     | -10~85                       | ŗ    |

| Tatg       | Storage temperature        |                     | <i>-</i> 65∼150              | Ċ    |

<sup>\*</sup> This is -2.0V when pulse width ≤ 10ns, and -0.5V in case of DC.

## DC ELECTRICAL CHARACTERISTICS (Ta = $0 \sim 70\,^{\circ}\text{C}$ ; Vcc = 3.13 $\sim$ 3.60V, unless otherwise noted)

|        | B                                    | <b>T</b>                                                                  | dia)                                         |           | Limits |         | 1.1 |

|--------|--------------------------------------|---------------------------------------------------------------------------|----------------------------------------------|-----------|--------|---------|-----|

| Symbol | Parameter                            | Test con-                                                                 | Min                                          | Тур       | Max    | Unit    |     |

| Vcc    | Power supply voltage                 |                                                                           |                                              | 3.13      |        | 3.60    | ٧   |

| Vcca   | I/O buffer supply voltage            |                                                                           |                                              | Vcc - 0.3 |        | Vcc+0.3 | ٧   |

| ViH    | High-level input voltage             |                                                                           |                                              | 2.0       |        | Vcc+0.3 | ٧   |

| VIL    | Low-level input voltage              |                                                                           |                                              | - 0.3 •   |        | 0.8     | ٧   |

| Voн    | High-level output voltage            | 1он = - 4mA                                                               |                                              | 2.4       |        |         | ٧   |

| Vol    | Low-level output Voltage             | IoL = 8mA                                                                 |                                              |           |        | 0.4     | ٧   |

|        | Input current except ZZ, MODE and FT | Vi = 0V~Vcc                                                               |                                              |           |        | 2       |     |

|        | Insulation and AMODE and EX          | VI = Vcc                                                                  |                                              |           |        | 2       |     |

| h      | Input current of MODE and FT         | VI = 0V                                                                   |                                              |           |        | 100     | μA  |

|        | Innut suggest of 77                  | VI = Vcc                                                                  |                                              |           |        | 200     |     |

|        | Input current of ZZ                  | VI = 0V                                                                   |                                              |           |        | 2       |     |

| loz    | Off - State output current           | Vi (OE) ≥ViH, Vo = 0                                                      | -Vcc                                         |           |        | 10      | μА  |

| lcc1   | Active power supply current          | Output open                                                               | AC (10.0ns cycle,100MHz                      | )         | 250    | 300     |     |

|        |                                      | Device selected                                                           | AC (13.3ns cycle,75MHz)                      |           | 140    | 200     |     |

|        |                                      | Vi ≨Vil or Vi ≧ViH                                                        | AC (15.0ns cycle,66MHz)                      |           | 125    | 170     | mA  |

|        |                                      | ZZ≦VıL                                                                    | AC (16.7ns cycle,60MHz)                      |           | 110    | 160     |     |

|        | TTL Stand-by current                 |                                                                           | AC (10.0ns cycle,100MHz                      | )         | 75     | 95      |     |

|        |                                      | j                                                                         | AC (13.3ns cycle,75MHz)                      |           | 55     | 70      |     |

| lcc2   |                                      | Device deselected Vi ≦ViL or Vi ≧ViH ZZ≦ViL                               | AC (15.0ns cycle,86MHz)                      |           | 50     | 65      |     |

| 1002   | The stand by solven.                 |                                                                           | AC (16.7ns cycle,60MHz)                      |           | 45     | 60      | mA  |

|        |                                      |                                                                           | CLK frequency=<br>0MHz<br>All inputs statics |           | 15     | 20      |     |

| Icca   | CMOS Stand-by current                | Output open VI ≤0.2V or VI ≥VCC- 0.2V ZZ≤0.2V,                            | -6, -7, -8, -10                              |           | 0.2    | 2       | mA  |

| 1003   | (CLK stopped stand-by mode)          | FT≥Vcc- 0.2V<br>MODE≥Vcc- 0.2V<br>CLK frequency±0MHz<br>All inputs static | -7L, -8L, -10L                               |           | 5      | 200     | μΑ  |

| Icc4   | Snooze mode                          | Snooze mode<br>ZZ≧Vcc -0.2V                                               | -6, -7, -8, -10                              |           | 0.2    | 2       | mA  |

| ICC4   | Stand-by current                     | FT≥Vcc- 0.2V<br>MODE≥Vcc- 0.2V                                            | -7L, -8L, -10L                               |           | 5      | 200     | μΑ  |

Note 18. Vi∟min \* is −2.0V in case of AC (Pulse width ≤10ns).

19. "Device Deselected" means device is in POWER-DOWN mode as defined in the truth table.

20. Spec of Icc3 canbe supported by stopping CLK evenif device selected state.

21. Icc4 does not depend on CLK frequency and input level.

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

#### CAPACITANCE

| Cumbal | Parameter          | Test conditions                  |     | 1111 |     |      |

|--------|--------------------|----------------------------------|-----|------|-----|------|

| Symbol | i algillotei       | 1 651 CONGIBORIS                 | Min | Тур  | Max | Unit |

| Ci     | Input capacitance  | Vi = GND, Vi = 25mVrms, f = 1MHz |     |      | 6   | ρF   |

| Со     | Output capacitance | Vo = GND, Vo = 25mVrms, f = 1MHz |     |      | 8   | рF   |

This parameter is sampled.

#### THERMAL RESISTANCE

| Symbol Parameter                              | Barratar                                 | Test conditions                                                                  |     | Limits |      |     |

|-----------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|-----|--------|------|-----|

|                                               | 19st conditions                          | Min                                                                              | Тур | Max    | Unit |     |

| θ JA Thermal resistance - Junction to Ambient | Suspended in still air                   |                                                                                  | 89  |        |      |     |

|                                               | Thermal resistance - Junction to Ambient | Mounted on 70×70×1.6t Mitsubishi standard PC board, Air velocity = 0 m/s         |     | 72     |      | ¢w. |

|                                               |                                          | Mounted on 70×70×1.6t Mitsubishi<br>standard PC board, Air velocity<br>= 1.0 m/s |     | 57     |      |     |

| θ JC                                          | Thermal resistance - Junction to Case    | Immersed in fluorinert                                                           |     | 19     |      | ₩2  |

This parameter is sampled.

## AC ELECTRICAL CHARACTERISTICS (Ta = 0~70°C; Vcc = 3.13 ~ 3.60V, unless otherwise noted)

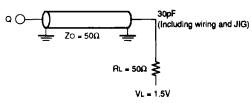

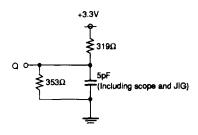

(1) MEASUREMENT CONDITIONS

Fig. 1 Output load

Fig. 2 Output load for ten, tdis

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

#### (2) TIMING CHARACTERISTICS

| Symbol     | Parameter                           |              | Limits |                  |    |                  |     |                    |    |      |

|------------|-------------------------------------|--------------|--------|------------------|----|------------------|-----|--------------------|----|------|

|            |                                     | 100MHz<br>-6 |        | 75MHz<br>-7, -7L |    | 66MHz<br>-8, -8L |     | 60MHz<br>-10, -10L |    | Unit |

|            |                                     |              |        |                  |    |                  |     |                    |    |      |

|            |                                     | Clock        |        |                  |    |                  |     |                    |    |      |

| tkc        | Clock cycle time                    | 10           |        | 13.3             |    | 15               |     | 16.7               |    | ns   |

| tкн        | Clock HIGH time                     | 3.5          |        | 5                |    | 6                |     | 6                  |    | ns   |

| tkl        | Clock LOW time                      | 3.5          |        | 5                |    | 6                |     | 6                  |    | ns   |

| Output Tir | nes                                 |              |        |                  |    |                  |     |                    |    |      |

| ta(K)      | Clock access time                   |              | 5.5    |                  | 7  |                  | 8.0 |                    | 10 | ns   |

| tv(K)      | Data valid time from Clock          | 2            |        | 2                |    | 3                |     | 3                  |    | ns   |

| ten(K)     | Output enable time from Clock       | 0            |        | 0                |    | 0                |     | 0                  |    | ns   |

| tdis(K)    | Output disable time from Clock      | 1            | 5.5    | 2                | 6  | 2                | 6   | 2                  | 6  | ns   |

| ta(OE)     | OE access time                      |              | 5.5    |                  | 6  |                  | 6   |                    | 6  | ns   |

| ten(OE)    | Output enable time from OE          | 0            |        | 0                |    | 0                |     | 0                  |    | ns   |

| tdis(OE)   | Output disable time from OE         | 1            | 5      | 2                | 6  | 2                | 6   | 2                  | 6  | ns   |

| Setup Tim  | es                                  | ·            |        |                  |    | ·                |     |                    |    |      |

| tsu(A)     | Address                             | 2            |        | 2.5              |    | 2.5              |     | 2.5                |    | ns   |

| tsu(AS)    | Address Status (ADSC, ADSP)         | 2            |        | 2.5              |    | 2.5              |     | 2.5                |    | ns   |

| tsu(AA)    | Address Advance (ADV)               | 2            |        | 2.5              |    | 2.5              |     | 2.5                | _  | ns   |

| tsu(W)     | Byte Write Enables (MBW, GW, BWs)   | 2            |        | 2.5              |    | 2.5              |     | 2.5                |    | ns   |

| tsu(D)     | Data-In                             | 2            |        | 2.5              |    | 2.5              |     | 2.5                |    | ns   |

| tsu(S)     | Chip Select enables (\$1, \$2, \$2) | 2            |        | 2.5              |    | 2.5              |     | 2.5                |    | ns   |

| Hold Time  | s                                   | •            |        |                  |    |                  |     |                    |    |      |

| th(A)      | Address                             | 0.5          |        | 0.5              |    | 0.5              |     | 0.5                |    | ns   |

| th(AS)     | Address Status (ADSC, ADSP)         | 0.5          |        | 0.5              |    | 0.5              |     | 0.5                |    | ns   |

| th(AA)     | Address Advance (ADV)               | 0.5          |        | 0.5              |    | 0.5              |     | 0.5                |    | ns   |

| th(W)      | Byte Write Enables (MBW, GW, BWs)   | 0.5          |        | 0.5              |    | 0.5              |     | 0.5                |    | ns   |

| th(D)      | Data-In                             | 0.5          |        | 0.5              |    | 0.5              |     | 0.5                |    | ns   |

| th(S)      | Chip Select (\$1, \$2, \$2)         | 0.5          |        | 0.5              |    | 0.5              |     | 0.5                |    | ns   |

| ZZ, MODE   | FT                                  | •            |        |                  |    |                  |     |                    |    |      |

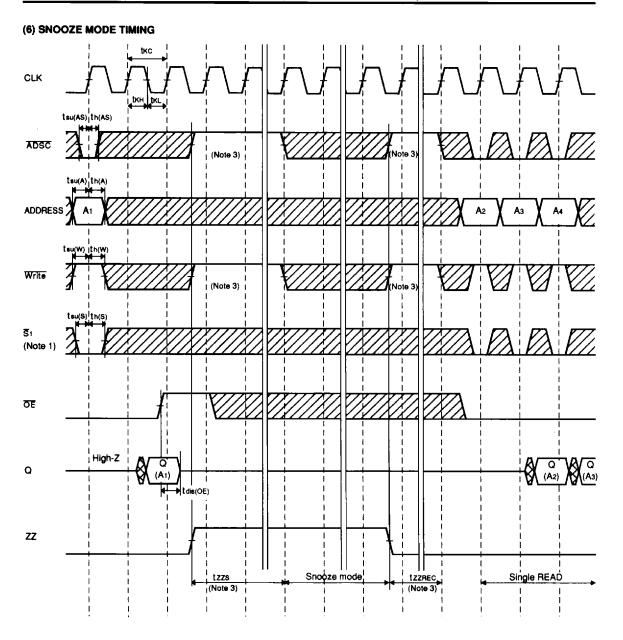

| tzzs       | ZZ Stand-by                         |              | 30     |                  | 30 |                  | 30  |                    | 30 | ns   |

| tzzrec     | ZZ Recovery                         | 30           |        | 30               |    | 30               |     | 30                 |    | ns   |

| tcFG       | Config setup (MODE, FT)             | 40           |        | 53.3             |    | 60               |     | 66.7               |    | ns   |

Note 22. All parameters except tzzs, tzznec in this table are measured on condition that ZZ = LOW fix.

23. Test conditions is specified with the output loading shown in Fig. 1 unless otherwise noted.

24. When enable and disable time (ten, tdie) are measured, Output loading is specified with CL = 5pF as in Fig. 2.

The transition is measured±500mV from steady state voltage.

<sup>25.</sup> The enable and disable time are sampled.

<sup>26.</sup> ADSP and ADSC must not be asserted during tzzs and tzzrec, due to a guarantee of data retention for snooze mode. If synchronous inputs are made combinations of WRITE state during tzzs, memorized data may be destroyed.

27. Configuration signals ( MODE and FT ) are static and must not change during normal operation.

## 1048576-BIT(32768-WORD BY 32-BIT) SYNCHRONOUS BURST SRAM

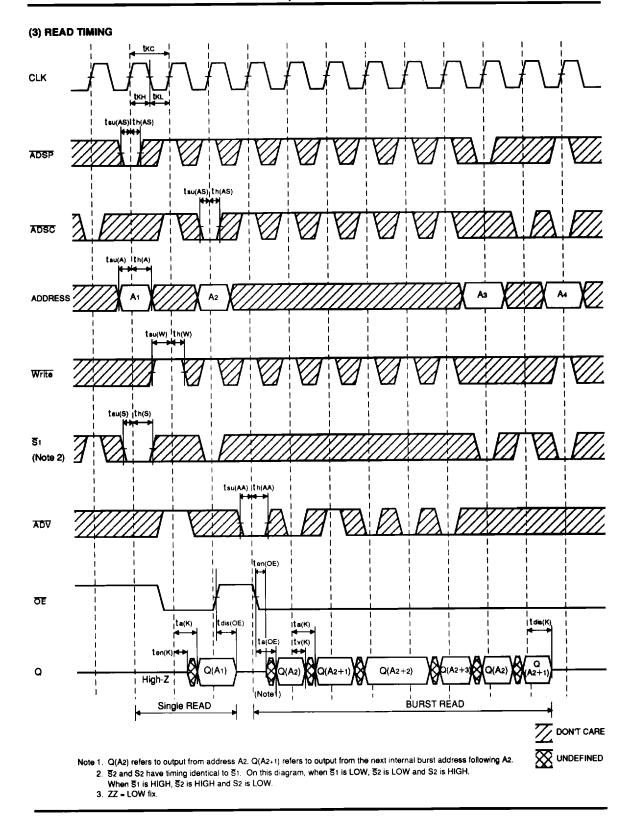

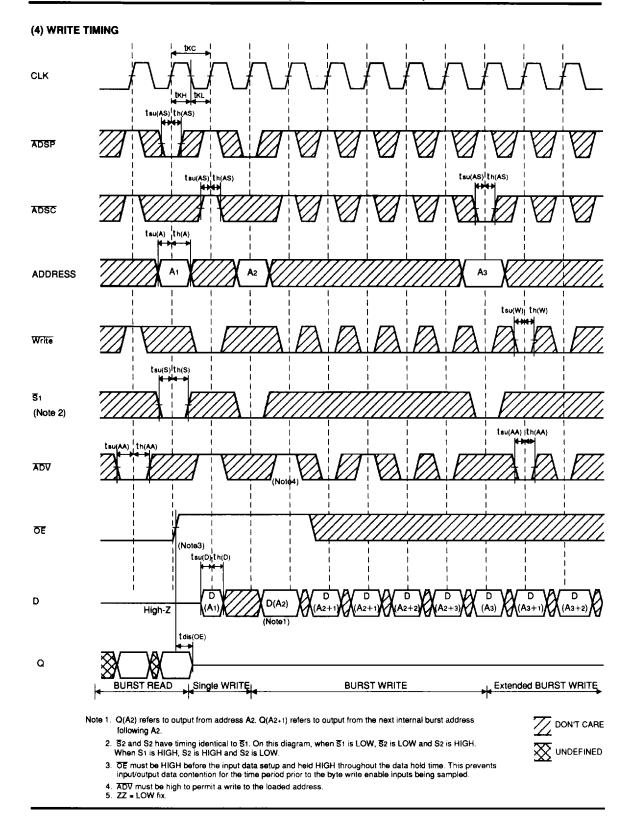

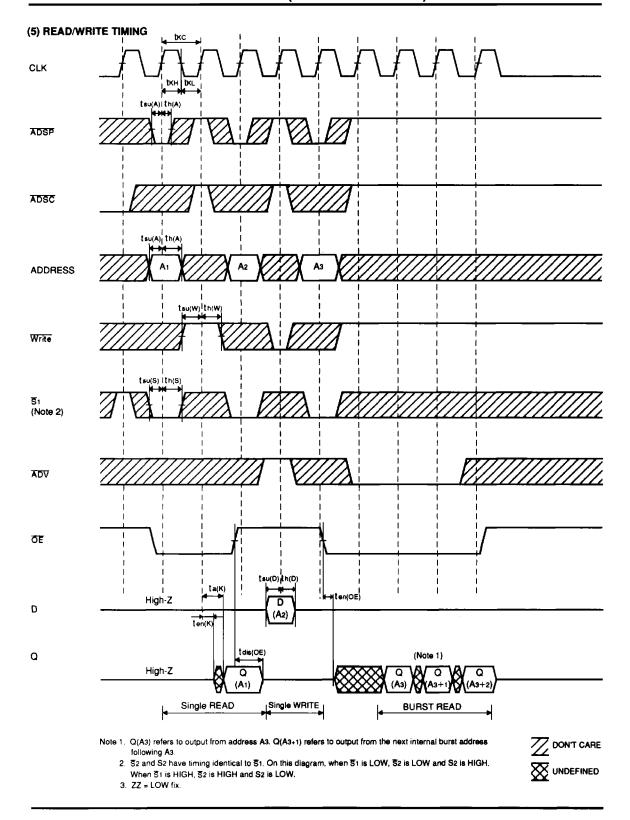

Note 1. \$\overline{S}\$2 and \$S\$2 have timing identical to \$\overline{S}\$1. On this diagram, when \$\overline{S}\$1 is LOW, \$\overline{S}\$2 is LOW and \$S\$2 is HIGH. When \$\overline{S}\$1 is HIGH, \$\overline{S}\$2 is HIGH and \$S\$2 is LOW.

Z DON'T CARE

2. On this timing chart,  $\overline{\text{ADSP}} = \text{HIGH fix}$ ,  $\overline{\text{ADV}} = \text{X}$ .

UNDEFINED

3. ADSP and ADSC must not be asserted during tzzs and tzzrec, due to a guarantee of data retention for snooze mode. If synchronous inputs are made combinations of WRITE state during tzzs and tzzrec, memorized data may be destroyed.