### Description

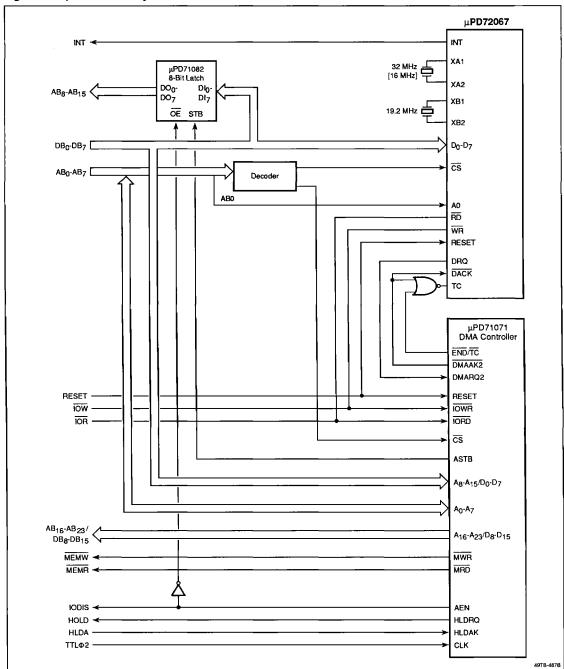

The μPD72067 Floppy-Disk Controller (FDC) is a CMOS device that integrates onto a single chip the peripheral logic necessary for todays's high-performance, low-power designs. It maintains complete microcode compatibility with the NEC μPD765 and μPD72065 devices, long established as the industry standard for floppy-disk control.

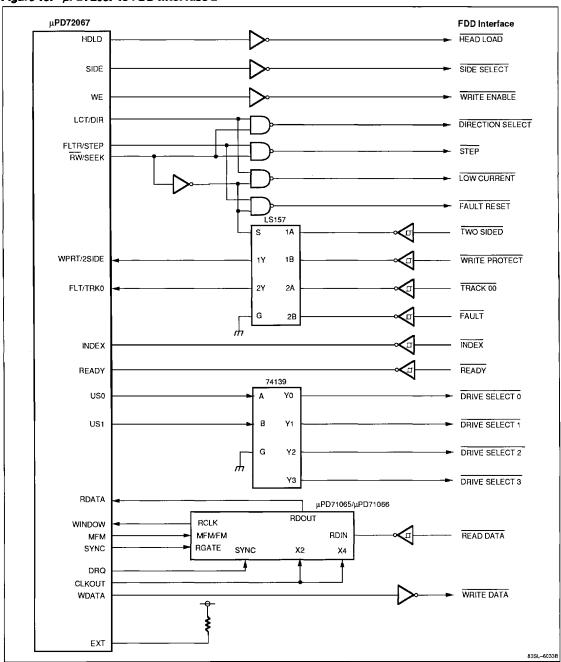

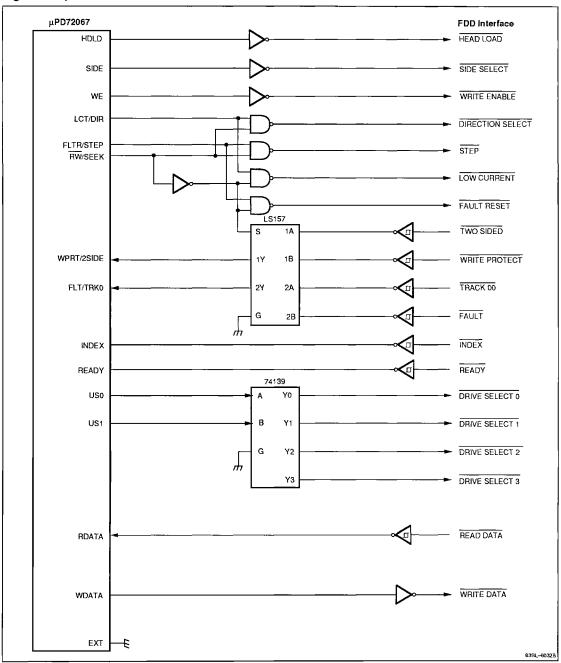

The µPD72067 incorporates on-chip clock generation/ switching, selectable write precompensation, and all the circuitry required for directly interfacing four floppy- disk drives.

An internal high-performance digital phase-locked loop (DPLL) enables reliable data separation at data transfer rates up to 500 kb/s.

### Features

- Command compatible with µPD765A, 765A-2, 765B, 7265, 72065, 72065B, 72066

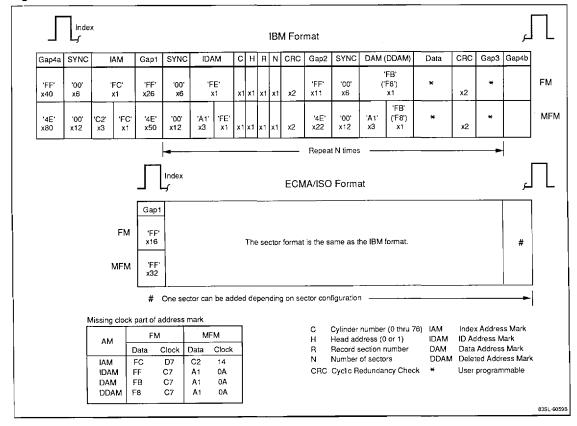

- □ IBM diskette compatible

- Single-sided, 128/256/512 bytes/sector

- -- Double-sided, 256 bytes/sector

- Double-sided, double-density, 256/1024 bytes/ sector

- ECMA/ISO minifloppy-disk format compatible

- ECMA66 (ISO/TC 97/SC11 N419), single-sided, single-density, 256 bytes/sector

- ECMA70 (ISO/TC 97/SC11 N475), double-sided, double-density, 256 bytes/sector

- Data transfer rates: 125, 150, 250, 300, 500 kb/s

- Standby function

- On-chip peripheral circuits

- VFO (DPLL) for window signal generation

- Write precompensation

- System clock generator

- Write clock generator

- External VFO (such as μPD71065/71066) can be connected

- □ Spindle motor control

- □ FM, MFM control (specified in each command)

- Variable record length: 128, 256, 512, 1024, 2048, 4096, or 8192 bytes/sector

- Multisector and multitrack functions

- Controls up to four FDDs

- Mixed floppy-disks: single- and double-sided, singleand double-density

- □ Simultaneous seek operation on four FDDs

- Intermediate or incomplete sector read/write can be specified (FM, 128 bytes/sector)

- Internal CRC generation and check (x<sup>16</sup> + x<sup>12</sup> + x<sup>5</sup> + 1)

- Stepping speed programmable

- Head load and unlead times programmable

- Data scan function: detection of sector satisfying equal-to, greater-than, or less-than condition with main memory data)

- DMA or non-DMA (interrupt) data transfer

- □ CMOS

- □ Single +5-volt power supply

### **Ordering Information**

| Part Number    | Package                                   |

|----------------|-------------------------------------------|

| μPD72067C      | 48-pin plastic DIP (600 mil)              |

| μPD72067GC-3B6 | 52-pin plastic miniflat                   |

| μPD72067L      | 52-pin PLCC (plastic leaded chip carrier) |

### Pin Configurations

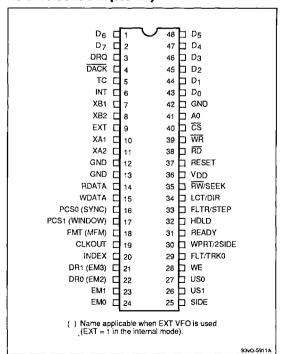

### 48-Pin Plastic DIP (600 mil)

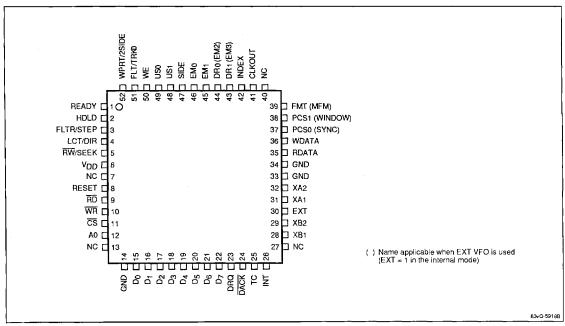

### 52-Pin Plastic Miniflat

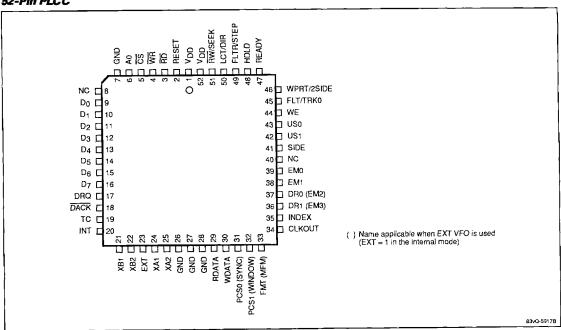

### 52-Pin PLCC

### Pin Identification

| Symbol                         | I/O | Signal Function                                                                                                                                                                                                           |

|--------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0                             | In  | Address 0. Selects μPD72067 registers via address bus.                                                                                                                                                                    |

|                                |     | A0 Registers Status or auxiliary command Data                                                                                                                                                                             |

| CLKOUT                         | Out | When EXT ≈ 1, supplies clock required by a μPD71065/71066 used as an external VFO.  DR1 CLKOUT 16 MHz 1 19.2 MHz  Note: CLKOUT goes low when EXT = 0.                                                                     |

| <del>cs</del>                  | ìn  | Chip Select. Validates RD and WR signals.                                                                                                                                                                                 |

| D <sub>0</sub> -D <sub>7</sub> | I/O | Bidirectional, three-state data bus.                                                                                                                                                                                      |

| DACK                           | In  | DMA Acknowledge. Enables DMA cycle.                                                                                                                                                                                       |

| DRO, DR1                       | ln  | Data Rate. Sets data transfer rate in external mode.                                                                                                                                                                      |

| (EM2, EM3)                     | Out | Enable Motor. Controls spindle motor in internal mode.                                                                                                                                                                    |

| DRQ                            | Out | DMA Request. Requests data transfer in DMA mode.                                                                                                                                                                          |

| EMO, EM1                       | Out | Enable Motor. Controls spindle motor.                                                                                                                                                                                     |

| EXT                            | în  | External VFO. Selects VFO in Internal mode.  EXT VFO Internal  External  In external mode, the input to EXT is not significant.                                                                                           |

| FLTR/STEP                      | Out | FLTR (Fault Reset). When FW/SEEK is set to 0, FLTR releases the drive fault state. STEP. When FW/SEEK is set to 1, STEP generates seek pulses                                                                             |

| FLT/TRK0                       | ln  | FLT (Fault). When RW/SEEK is set to 0, FLT indicates whether the drive is in fault state or not.  RKO (Track 0). When RW/SEEK is set to 1, TRKO indicates whether the read/write head is positioned at cylinder 0 or not. |

| FMT                            | In  | Format. Selects format in external mode.  FMT Format D IBM 1 ECMA                                                                                                                                                         |

| (MFM)                          | Out | MFM Mode. In internal mode, format is specified by the SELECT FORMAT command. The MFM output signal specifies the VFO circuit operation mode.  MFM                                                                        |

| HDLD                           | Out | Head Load. Causes read/write head to contact the diskette.                                                                                                                                                                |

| INDEX In Indicates read/write head is positioned at the physical starting point of the track on the medium.  INT Out Interrupt Request. Requests main system to process the transfer data and execution results.  LCT/DIR Out LCT (Low Current). When FW/SEEK signal is set to 0, LCT indicates the read/write head selects the 43rd or later cylinder.  DIR (Direction). When FW/SEEK signal is set to 1, DIR specifies the seek direction.  DIR (Direction). When FW/SEEK signal is set to 1, DIR specifies the seek direction.  DIR Direction O Outer 1 Inner  PCS0 In Precompensation. In external mode, PCS0 determines the amount of precompensation.  (SYNC) Out VFO Synchronize. In internal mode, SYNC indicates the μPD72067 operation mode.  SYNC Mode O Read operation is inhibited 1 Read operation is being performed This pin should be pulled high or low by resistors if external mode is not used.  PCS1 In Precompensation. In external mode, PCS1 (with PCS0) determines the amount of precompensation.  (MNDOW) in Data Window. In internal mode, the WINDOW signal generated by the VFO circuit samples the RDATA bits. The μPD72067 determines whether a bit is clock or data.  This pin should be tied directly high or low if external mode is not used.  RDATA In Read. Causes the main system to read data from the μPD72067 to the data bus.  READY In Read Causes the main system to read data from the μPD72067 to the data bus.  READY In Indicates the drive is in a ready state.  READY In Indicates the drive is in a ready state.  Places μPD72067 in idie state.  Outputs are low except WDATA is undefined.  In main system, INT and DRQ are low.  D <sub>0</sub> -D <sub>7</sub> are in the input state.  READY Specifies whether certain FDD interface signals are used for read/write or seek.  RW/SEEK Signal function  O Read/write  SiDE Selected  O Head O  1 Head 1  TC In Terminal Count. Indicates data transfer termination.                                                                                                                                                | Symbol  | I/O | Signal Function                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drocess the transfer data and execution results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INDEX   | ln  | physical starting point of the track on the                                                                                                                      |

| to 0, LCT indicates the read/write head selects the 43rd or later cylinder.  DIR (Direction). When RW/SEEK signal is set to 1, DIR specifies the seek direction.  DIR Direction  Outer  1 Inner  PCSO In Precompensation. In external mode, PCSO determines the amount of precompensation.  (SYNC) Out VFO Synchronize. In internal mode, SYNC indicates the µPD72067 operation mode.  SYNC Mode  Read operation is inhibited  1 Read operation is inhibited  1 Read operation is being performed  This pin should be pulled high or low by resistors if external mode is not used.  PCS1 In Precompensation. In external mode, PCS1 (with PCS0) determines the amount of precompensation.  (MINDOW) In Data Window. In internal mode, the WINDOW signal generated by the VFO circuit samples the RDATA bits. The µPD72067 determines whether a bit is clock or data.  This pin should be tied directly high or low if external mode is not used.  RD In Read. Causes the main system to read data from the µPD72067 to the data bus.  RDATA In Read data (consisting of clock and data bits) from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is entered.  READY In Indicates the drive is in a ready state.  Outputs are low except WDATA is undefined.  In main system, INT and DRQ are low.  Dg-Dr7 are in the input state.  Outputs are low except WDATA is undefined.  In main system, INT and DRQ are low.  Dg-Dr7 are in the input state.  Signal function  O Read/write  1 Seek  SIGNAL FREED OUT Selected  O Head 0  Head 0  Head 1  TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INT     | Out |                                                                                                                                                                  |

| O Outer   1   Inner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LCT/DIR | Out | to 0, LCT Indicates the read/write head selects the 43rd or later cylinder.  DIR (Direction). When RW/SEEK signal is set to 1, DIR specifies the seek direction. |

| Country   Cou |         |     | 0 Outer                                                                                                                                                          |

| indicates the μPD72067 operation mode.  SYNC Mode  0 Read operation is inhibited 1 Read operation is being performed This pin should be pulled high or low by resistors if external mode is not used.  PCS1 In Precompensation. In external mode, PCS1 (with PCS0) determines the amount of precompensation.  (MNDOW) In Data Window. In internal mode, the WINDOW signal generated by the VFO circuit samples the RDATA bits. The μPD72067 determines whether a bit is clock or data.  This pin should be tied directly high or low if external mode is not used.  RDATA In Read Causes the main system to read data from the μPD72067 to the data bus.  RDATA In Read data (consisting of clock and data bits) from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is entered.  READY In Indicates the drive is in a ready state.  READY In Indicates the drive is in a ready state.  READY In Indicates the drive is in a ready state.  READY In Places μPD72067 in idle state.  Outputs are low except WDATA is undefined.  In main system, INT and DRQ are low.  D <sub>0</sub> -D <sub>7</sub> are in the input state.  RW/SEEK Signal function  O Read/write  1 Seek  SIDE Out Selects head 0 or head 1 of screen-type drive.  SIDE Selected  O Head 0  1 Head 1  TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCS0    | ln  |                                                                                                                                                                  |

| Read operation is inhibited   1   Read operation is being performed   This pin should be pulled high or low by resistors if external mode is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (SYNC)  | Out |                                                                                                                                                                  |

| resistors if external mode is not used.  PCS1 In Precompensation. In external mode, PCS1 (with PCS0) determines the amount of precompensation.  (WINDOW) In Data Window. In internal mode, the WINDOW signal generated by the VFO circuit samples the RDATA bits. The μPD72067 determines whether a bit is clock or data.  This pin should be tied directly high or low if external mode is not used.  RD In Read. Causes the main system to read data from the μPD72067 to the data bus.  RDATA In Read data (consisting of clock and data bits) from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is entered.  READY In Indicates the drive is in a ready state.  READY In Indicates the drive is in a ready state.  RESET In Places μPD72067 in idle state.  Outputs are low except WDATA is undefined.  In main system, INT and DRQ are low.  D0-D7 are in the input state.  RW/SEEK Signal function  O Read/write  1 Seek  SIDE Out Selects head 0 or head 1 of screen-type drive.  SIDE Selected  O Head 0  Head 1  TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |     | O Read operation is inhibited                                                                                                                                    |

| PCS0  determines the amount of precompensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |                                                                                                                                                                  |

| signal generated by the VFO circuit samples the RDATA bits. The μPD72067 determines whether a bit is clock or data.  This pin should be tied directly high or low if external mode is not used.  RD In Read. Causes the main system to read data from the μPD72067 to the data bus.  RDATA In Read data (consisting of clock and data bits) from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is entered.  READY In Indicates the drive is in a ready state.  RESET In Places μPD72067 in idle state.  • Outputs are low except WDATA is undefined. • In main system, INT and DRQ are low. • D <sub>0</sub> -D <sub>7</sub> are in the input state.  RW/SEEK Out Specifies whether certain FDD interface signals are used for read/write or seek.  RW/SEEK Signal function 0 Read/write 1 Seek  SIDE Out Selects head 0 or head 1 of screen-type drive. SIDE Selected 0 Head 0 1 Head 1  TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PCS1    | In  | PCS0) determines the amount of                                                                                                                                   |

| external mode is not used.  RD In Read. Causes the main system to read data from the μPD72067 to the data bus.  RDATA In Read data (consisting of clock and data bits) from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is entered.  READY In Indicates the drive is in a ready state.  Places μPD72067 in idle state.  Outputs are low except WDATA is undefined.  In main system, INT and DRQ are low.  D <sub>0</sub> -D <sub>7</sub> are in the input state.  RW/SEEK Out Specifies whether certain FDD interface signals are used for read/write or seek.  RW/SEEK Signal function O Read/write 1 Seek  SIDE Out Selects head 0 or head 1 of screen-type drive. SIDE Direction Head 0 Head 1  TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (MNDOW) | In  | signal generated by the VFO circuit samples the $\overline{\text{RDATA}}$ bits. The $\mu\text{PD72067}$ determines whether                                       |

| From the μPD72067 to the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |     |                                                                                                                                                                  |

| from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is entered.  READY  In Indicates the drive is in a ready state.  RESET  In Places µPD72067 in idle state.  • Outputs are low except WDATA is undefined. • In main system, INT and DRQ are low. • D <sub>0</sub> -D <sub>7</sub> are in the input state.  RW/SEEK  Out Specifies whether certain FDD interface signals are used for read/write or seek.  RW/SEEK  Signal function  O Read/write  1 Seek  SIDE  Out Selects head 0 or head 1 of screen-type drive.  SIDE  SIDE  Out Head 0  Head 1  TC  In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RD      | ln  |                                                                                                                                                                  |

| RESET In Places µPD72067 in idle state.  • Outputs are low except WDATA is undefined. • In main system, INT and DRQ are low. • D <sub>0</sub> -D <sub>7</sub> are in the input state.  RW/SEEK Out Specifies whether certain FDD interface signals are used for read/write or seek.  RW/SEEK Signal function 0 Read/write 1 Seek SIDE Out Selects head 0 or head 1 of screen-type drive. SIDE SiDE Selected 0 Head 0 1 Head 1 TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RDATA   | In  | from the drive. If both WINDOW and RDATA are not input at the read state, a deadlock state is                                                                    |

| Outputs are low except WDATA is undefined.     In main system, INT and DRQ are low.     D <sub>0</sub> -D <sub>7</sub> are in the input state.  RW/SEEK Out Specifies whether certain FDD interface signals are used for read/write or seek.  RW/SEEK Signal function Read/write Seek  SIDE Out Selects head 0 or head 1 of screen-type drive. SIDE Selected 0 Head 0 1 Head 1  TC In Terminal Count. Indicates data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | READY   | ln  | Indicates the drive is in a ready state.                                                                                                                         |

| Are used for read/write or seek.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RESET   | In  | <ul> <li>Outputs are low except WDATA is undefined.</li> <li>In main system, INT and DRQ are low.</li> </ul>                                                     |

| SIDE   Selected   Head 0   Head 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RW/SEEK | Out | are used for read/write or seek.  RW/SEEK Signal function Read/write                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SIDE    | Out | SIDE Selected 0 Head 0                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | тс      | In  |                                                                                                                                                                  |

### Pin Identification (cont)

| Symbol          | I/O | Signal Function                                                                                                                                                                                |

|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| US0, US1        | Out | Unit Select. One of four FDDs is selected by decoding US0 and US1.                                                                                                                             |

| WDATA           | Out | Write data (clock and data bits) to FDD.                                                                                                                                                       |

| WE              | Out | Write Enable. Requests FDD to write data.                                                                                                                                                      |

| WPRT/2SIDE      | ln  | WPRT (Write Protected). When RW/SEEK is set to 0, WPRT indicates whether the medium is write-protected.                                                                                        |

|                 |     | 2SIDE (Two Side). When $\overline{\text{RW}}/\text{SEEK}$ is set to 1, 2SIDE indicates whether the medium is double-sided.                                                                     |

| WR              | ln  | Write. Control signal that allows the main system to read data from the μPD72067 to the data bus.                                                                                              |

| XA1, XA2        | In  | Crystal A. To use internal VFO (EXT = 0), connect a 32-MHz quartz crystal resonator to XA1 and XA2. As an alternative, connect a 32-MHz external clock to XA1 and leave XA2 open.              |

|                 |     | To use external VFO (EXT = 1), connect a 16-MHz quartz crystal resonator to XA1 and XA2. As an alternative, connect a 16-MHz external clock to XA1 and leave XA2 open.                         |

| XB1, XB2        | In  | Crystal B. To use the 300-kb/s data transfer rate, connect a 19.2-MHz quartz crystal resonator to XB1 and XB2. As an alternative, connect a 19.2-MHz external clock to XB1 and leave XB2 open. |

| NC              |     | No Connection                                                                                                                                                                                  |

| GND             |     | Ground                                                                                                                                                                                         |

| V <sub>DD</sub> | In  | +5-volt power supply                                                                                                                                                                           |

### Note:

The pin symbol in parentheses applies when external VFO is used.

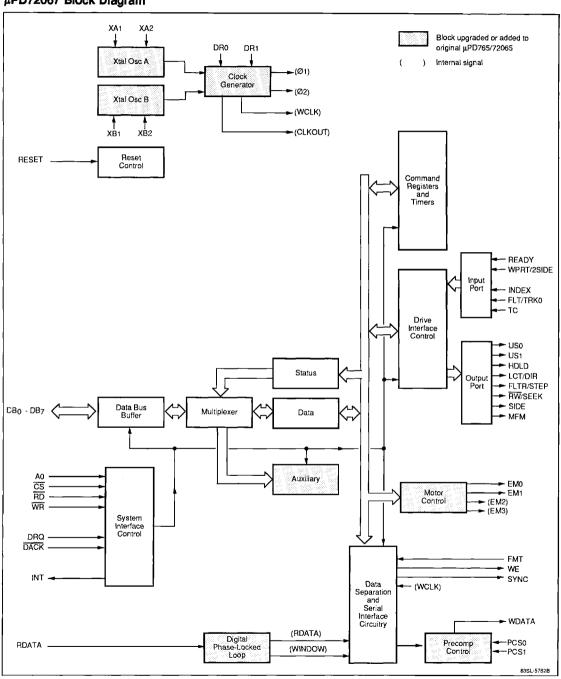

### μPD72067 Block Diagram

### Absolute Maximum Ratings $T_A = +25^{\circ}C$

| - A                                     |              |

|-----------------------------------------|--------------|

| Voltage on any pin                      | -0.5 to +7 V |

| Operating temperature, T <sub>OPT</sub> | -10 to +70°C |

| Storage temperature, T <sub>STG</sub>   | -65 to 150°C |

### Capacitance

$T_A = +25$ °C;  $V_{DD} = 0$  V; f = 1 MHz

| Parameter          | Symbol          | Min | Max | Unit | Conditions               |

|--------------------|-----------------|-----|-----|------|--------------------------|

| Clock capacitance  | Сф              |     | 20  | pF   | Unmeasured               |

| Input capacitance  | C <sub>IN</sub> |     | 10  | рF   | pins returned<br>to 0 V. |

| Output capacitance | Cout            |     | 20  | рF   |                          |

### **DC Characteristics**

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5 \text{ V} \pm 10\%$

| Parameter                           | Symbol           | Min                 | Max                   | Unit | Conditions                        |

|-------------------------------------|------------------|---------------------|-----------------------|------|-----------------------------------|

| Low-level input<br>voltage          | V <sub>IL</sub>  | -0.5                | 8.0                   | ٧    |                                   |

| High-level input voltage            | V <sub>IH</sub>  | 2.2                 | V <sub>DD</sub> + 0.5 | ٧    |                                   |

| Low-level output voltage            | V <sub>OL</sub>  |                     | 0.45                  | ٧    | I <sub>OL</sub> = 2.0<br>mA       |

| High-level output voltage           | V <sub>OH</sub>  | 0.7 V <sub>DD</sub> | V <sub>DD</sub>       | ٧    | l <sub>OH</sub> ≃<br>-200 μA      |

| Low-level input<br>leakage current  | ILIL             |                     | -10                   | μА   | V <sub>IN</sub> = 0 V             |

| High-level input<br>leakage current | LIH              |                     | +10                   | μА   | V <sub>IN</sub> = V <sub>DD</sub> |

| Low-level output<br>leakage current | l <sub>LOL</sub> |                     | -10                   | μА   | V <sub>OUT</sub> =<br>+0.45 V     |

| High-level output leakage current   | (LOH             |                     | + 10                  | μА   | V <sub>OUT</sub> =                |

| V <sub>DD</sub> supply current      | ססן              |                     | 60                    | mA   | Note 1                            |

| Standby current                     | I <sub>DD1</sub> |                     | 100                   | μА   | •                                 |

| Oscillator<br>stabilization<br>time | <sup>t</sup> KS  |                     | 10                    | ms   |                                   |

### Notes:

(1) When a 32-MHz crystal is connected to XA1-XA2 or a 19.2-MHz crystal is connected to XB1-XB2.

AC Characteristics 1; Standard Floppy-Disk Control  $T_A = -10$  to  $+70^{\circ}$ C;  $V_{DD} = +5$  V  $\pm 10\%$ ; MFM data transfer rate = 500 kb/s

| Parameter                       | Figure | Symbol           | Min | Тур | Max | Unit | Conditions       |

|---------------------------------|--------|------------------|-----|-----|-----|------|------------------|

| Main System Side                |        |                  |     |     |     |      |                  |

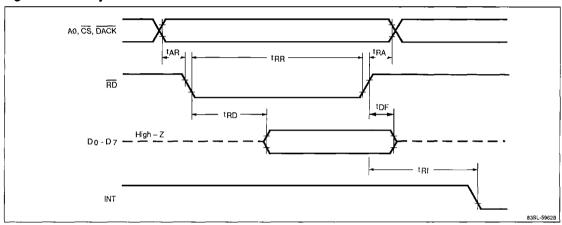

| A0, CS, DACK setup time to RD   | 2      | t <sub>AR</sub>  | 0   |     | .,  | ns   |                  |

| A0, CS, DACK hold time from RD  | 2      | t <sub>RA</sub>  | 0   |     |     | ns   |                  |

| RD pulse width                  | 2      | t <sub>RR</sub>  | 200 |     |     | ns   |                  |

| Data access time from RD ↓      | 2      | tab              |     |     | 140 | ns   |                  |

| Data float delay time from RD 1 | 2      | t <sub>DF</sub>  | 10  |     | 85  | ns   | · ·              |

| INT delay time from RD ↑        | 2      | t <sub>Ri</sub>  |     |     | 400 | ns   | Note 1           |

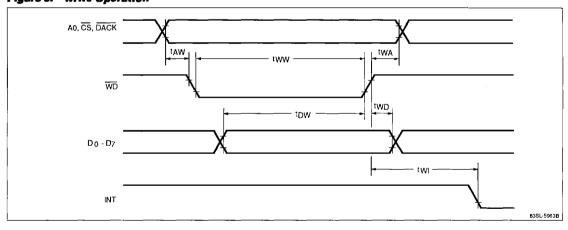

| A0, CS, DACK setup time to WR   | 3      | t <sub>AW</sub>  | 0   |     |     | ns   |                  |

| AO, CS, DACK hold time from WR  | 3      | t <sub>WA</sub>  | 0   |     |     | ns   |                  |

| WR pulse width                  | 3      | tww              | 200 |     |     | ns   |                  |

| Data setup time to WR           | 3      | t <sub>DW</sub>  | 100 |     |     | ns   |                  |

| Data hold time from WA          | 3      | t <sub>WD</sub>  | 0   |     |     | ns   |                  |

| INT delay time from WR ↑        | 3      | t <sub>Wl</sub>  |     |     | 400 | ns   | Note 1           |

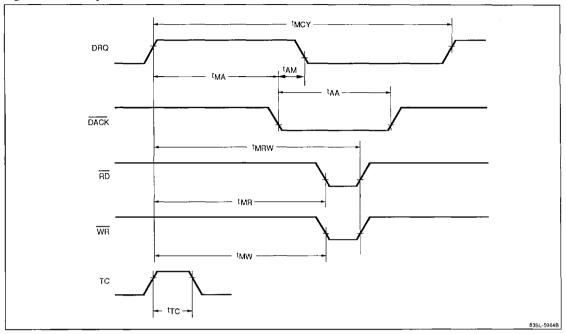

| DRQ cycle time                  | 4      | tMCY             | 13  |     |     | μs   | DR1 = 0, DR0 = 1 |

| DACK 1 response time from DRQ 1 | 4      | t <sub>MA</sub>  | 200 |     |     | ns   | _                |

| DRQ delay time from DACK ↓      | 4      | t <sub>AM</sub>  |     |     | 140 | ns   |                  |

| DACK pulse width                | 4      | t <sub>AA</sub>  | 8   |     |     | Фсү  | Note 5           |

| RD ↓ response time from DRQ ↑   | 4      | t <sub>MR</sub>  | 125 |     |     | ns   | DR1 = 0, DR0 = 1 |

| WR ↓ response time from DRQ ↑   | 4      | t <sub>MW</sub>  | 250 |     |     | ns   | -                |

| WR/RD response time from DRQ ↑  | 4      | t <sub>MRW</sub> |     |     | 12  | μs   |                  |

| TC pulse width                  | 4      | t <sub>TC</sub>  | 60  |     |     | ns   |                  |

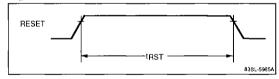

| RESET pulse width               | 5      | tast             | 60  |     |     | фсү  | Note 5           |

### AC Characteristics 1; Standard Floppy-Disk Control (cont)

| Parameter                             | Figure | Symbol           | Min | Тур | Max | Unit | Conditions   |

|---------------------------------------|--------|------------------|-----|-----|-----|------|--------------|

| Drive Side                            |        |                  |     |     |     |      |              |

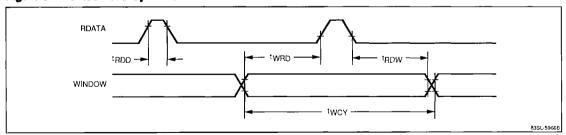

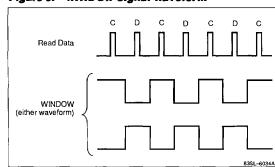

| RDATA high-level width                | 6      | t <sub>RDD</sub> | 40  |     |     | ns   |              |

| WINDOW cycle time (Note 2)            | 6      | twcy             |     | 2   |     | μs   | MFM = 0      |

|                                       |        |                  |     | 1   | -   | μs   | MFM = 1      |

| WINDOW setup time to RDATA (Note 2)   | 6      | t <sub>WRD</sub> | 15  | _   |     | ns   |              |

| WINDOW hold time from RDATA (Note 2)  | 6      | ta DW            | 15  |     |     | ns   |              |

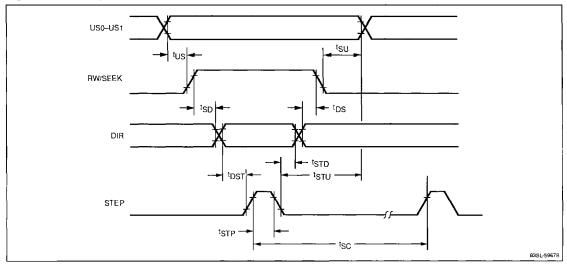

| US0, US1 setup time to SEEK           | 7      | tus .            | 12  |     |     | μs   | Note 3       |

| SEEK setup time to DIR                | 7      | t <sub>SD</sub>  | 7   |     |     | μз   | -            |

| DIR setup time to STEP                | 7      | t <sub>DST</sub> | 1   |     |     | μs   | _            |

| USO, US1 hold time from STEP          | 7      | tsru             | 5   |     |     | μэ   | <del></del>  |

| STEP high-level width                 | 7      | tSTP             | 6   | 7   | 8   | μs   | <b>=</b>     |

| US0, US1 hold time from SEEK (Note 4) | 7      | tsu              | 15  |     |     | μS   | _            |

| SEEK hold time from DIR               | 7      | t <sub>os</sub>  | 30  |     |     | μs   | _            |

| DIR hold time from STEP               | 7      | tSTD             | 24  |     |     | μs   | <del></del>  |

| STEP cycle time                       | 7      | tsc              | 33  |     |     | μз   | -            |

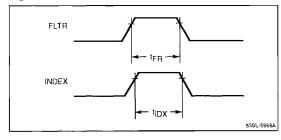

| FLTR high-level width                 | 8      | t <sub>FR</sub>  | 8   |     | 10  | μS   | <del>-</del> |

| INDEX high-level width                | 8      | t <sub>IDX</sub> | 16  |     |     | Фсч  | Note 5       |

- (1) For data transfer in non-DMA mode.

- (2) When external VFO is used.

- (3) The minimum value for drive-side parameters is 50 ns less than the value expressed in  $\mu s$ . For example, 12  $\mu s$  is actually 11.950  $\mu s$ .

- (4) While the unit under test is performing a seek operation, the SENSE DEVICE STATUS command is being executed for the other devices.

- (5) The time  $\phi_{CY}$  is a multiple of the period of a quartz crystal resonator connected to pins XA1-XA2 or an external clock connected to pin XA1. The multiple is four (EXT = 0) or two (EXT = 1).

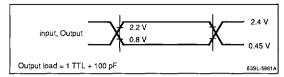

- (6) See figure 1 for timing measurement voltage thresholds.

# AC Characteristics 2; Minifloppy-Disk Control $T_A = -10$ to $+70^{\circ}$ C; $V_{DD} \approx +5 \text{ V} \pm 10\%$ ; MFM data transfer rate = 250 kb/s

| Parameter                       | Figure | Symbol           | Min | Тур          | Max | Unit | Conditions       |

|---------------------------------|--------|------------------|-----|--------------|-----|------|------------------|

| Main System Side                | ·      |                  |     | -            | -   |      |                  |

| A0, CS, DACK setup time to RD   | 2      | t <sub>AR</sub>  | 0   |              |     | ns   |                  |

| AO, CS, DACK hold time from FID | 2      | t <sub>RA</sub>  | 0   |              |     | ns   |                  |

| RD pulse width                  | 2      | t <sub>RR</sub>  | 200 |              |     | ns   |                  |

| Data access time from RD 1      | 2      | t <sub>RD</sub>  |     |              | 140 | ns   |                  |

| Data float delay time from RD 1 | 2      | t <sub>DF</sub>  | 10  |              | 85  | ns   |                  |

| NT delay tíme from ĀD ↑         | 2      | t <sub>RI</sub>  |     |              | 400 | ns   | Note 1           |

| A0, CS, DACK setup time to WR   | 3      | t <sub>AW</sub>  | 0   |              |     | ns   |                  |

| AO, CS, DACK hold time from WR  | 3      | t <sub>WA</sub>  | 0   |              |     | ns   |                  |

| WR pulse width                  | 3      | tww              | 200 |              |     | ns   |                  |

| Data setup time to WR           | 3      | t <sub>DW</sub>  | 100 |              |     | ns   |                  |

| Data hold time from WR          | 3      | two              | 0   |              |     | ns   |                  |

| INT delay time from ₩Ř↑         | 3      | t <sub>W</sub> I |     |              | 400 | ns   | Note 1           |

| DRQ cycle time                  | 4      | tMCY             | 26  |              |     | μs   | DR1 = 0, DR0 = 0 |

| DACK ↓ response time from DRQ ↑ | 4      | t <sub>MA</sub>  | 400 |              |     | ns   |                  |

| DRQ delay time from DACK ↓      | 4      | t <sub>AM</sub>  |     |              | 140 | ns   |                  |

| DACK pulse width                | 4      | t <sub>AA</sub>  | 8   | <del>-</del> |     | PCY  | Note 5           |

| RD ↓ response time from DRQ ↑   | 4      | t <sub>MR</sub>  | 250 |              |     | ns   | DR1 = 0, DR0 = 0 |

| WR ↓ response time from DRQ ↑   | 4      | t <sub>MW</sub>  | 500 |              |     | ns   | <del>-</del>     |

| WR/RD response time from DRQ 1  | 4      | t <sub>MRW</sub> |     |              | 24  | μэ   |                  |

| TC pulse width                  | 4      | tτc              | 60  |              |     | ns   |                  |

| RESET pulse width               | 5      | t <sub>AST</sub> | 60  |              |     | φcγ  | Note 5           |

AC Characteristics 2; Minifloppy-Disk Control (cont)

| Parameter                             | Figure | Symbol           | Min | Тур | Max                                   | Unit | Conditions |

|---------------------------------------|--------|------------------|-----|-----|---------------------------------------|------|------------|

| Drive Side                            |        |                  |     |     |                                       |      | -          |

| RDATA high-level width                | 6      | t <sub>RDD</sub> | 40  |     | · · · · · · · · · · · · · · · · · · · | ns   |            |

| WINDOW cycle time (Note 2)            | 6      | twcy             |     | 4   |                                       | μs   | MFM = 0    |

|                                       |        |                  |     | 2   |                                       | με   | MFM = 1    |

| WINDOW setup time to RDATA (Note 2)   | 6      | t <sub>WRD</sub> | 15  |     |                                       | ns   |            |

| WINDOW hold time from RDATA (Note 2)  | 6      | tabw             | 15  |     |                                       | ns   |            |

| US0, US1 setup time to SEEK           | 7      | tus              | 24  |     |                                       | μs   | Note 3     |

| SEEK setup time to DIR                | 7      | t <sub>SD</sub>  | 14  |     |                                       | μ\$  | _          |

| DIR setup time to STEP                | 7      | tost             | 2   |     |                                       | μs   | _          |

| US0, US1 hold time from STEP          | 7      | tstu             | 10  |     |                                       | μs   | _          |

| STEP high-level width                 | 7      | tSTP             | 12  | 14  | 16                                    | μs   | _          |

| USO, US1 hold time from SEEK (Note 4) | 7      | tsu              | 30  |     |                                       | μs   | _          |

| DIR hold time from STEP               | 7      | tSTD             | 48  |     |                                       | μs   | _          |

| SEEK hold time from DIR               | 7      | t <sub>DS</sub>  | 60  |     |                                       | μs   | _          |

| STEP cycle time                       | 7      | t <sub>SC</sub>  | 66  |     |                                       | μs   | _          |

| FLTR high-level width                 | 8      | t <sub>FR</sub>  | 16  | -   | 20                                    | μs   | _          |

| INDEX high-level width                | 8      | t <sub>iDX</sub> | 16  |     |                                       | фсү  | Note 5     |

- (1) For data transfer in non-DMA mode.

- (2) When external VFO is used.

- (3) The minimum value for drive-side parameters is 50 ns less than the value expressed in μs. For example, 12 μs is actually 11.950 μs.

- (4) While the unit under test is performing a seek operation, the SENSE DEVICE STATUS command is being executed for the other devices.

- (5) φ<sub>CY</sub> is a multiple of the period of a quartz crystal resonator connected to pins XA1-XA2 or an external clock connected to pin XA1. The multiple is eight (EXT = 0) or four (EXT = 1).

- (6) See figure 1 for timing measurement voltage thresholds.

## AC Characteristics 3; High-Speed Floppy-Disk Control $T_A=-10$ to $+70^{\circ}\text{C}$ ; $V_{DD}=+5$ V $\pm10\%$ ; MFM data transfer rate = 300 kb/s

| Parameter                       | Figure | Symbol           | Min   | Тур      | Max | Unit | Conditions                            |

|---------------------------------|--------|------------------|-------|----------|-----|------|---------------------------------------|

| Main System Side                |        |                  |       |          |     |      |                                       |

| AO, CS, DACK setup time to RD   | 2      | t <sub>AR</sub>  | 0     |          |     | ns   |                                       |

| A0, CS, DACK hold time from RD  | 2      | tra              | 0     |          |     | ns   |                                       |

| RD pulse width                  | 2      | t <sub>RR</sub>  | 200   |          |     | ns   | · · · · · · · · · · · · · · · · · · · |

| Data access time from RD ↓      | 2      | t <sub>RD</sub>  |       |          | 140 | ns   |                                       |

| Data float delay time from RD ↑ | 2      | t <sub>DF</sub>  | 10    |          | 85  | ns   |                                       |

| INT delay time from RD↑         | 2      | t <sub>RI</sub>  |       |          | 400 | ns   | Note 1                                |

| A0, CS, DACK setup time to WR   | 3      | t <sub>AW</sub>  | 0     |          |     | ns   |                                       |

| A0, CS, DACK hold time from WA  | 3      | t <sub>WA</sub>  | 0     |          |     | ns   |                                       |

| WA pulse width                  | 3      | t <sub>WW</sub>  | 200   |          |     | กร   |                                       |

| Data setup time to WR           | 3      | tow              | 100   |          |     | ns   |                                       |

| Data hold time from WR          | 3      | t <sub>WD</sub>  | 0     |          |     | ns   |                                       |

| INT delay time from ₩A↑         | 3      | t <sub>Wl</sub>  |       |          | 400 | ns   | Note 1                                |

| DRQ cycle time                  | 4      | tMCY             | 21.7  |          |     | με   | DR1 = 1, DR0 = 1                      |

| DACK ↓ response time from DRQ ↑ | 4      | t <sub>MA</sub>  | 333.3 |          |     | ns   |                                       |

| DRQ delay time from DACK ↓      | 4      | t <sub>AM</sub>  |       |          | 140 | ns   |                                       |

| DACK pulse width                | 4      | taa              | 8     | <u>-</u> |     | φсγ  | Note 5                                |

| RD ↓ response time from DRQ ↑   | 4      | t <sub>MR</sub>  | 208.3 |          |     | ns   | DR1 = 1, DR0 = 1                      |

| WR ↓ response time from DRQ ↑   | 4      | t <sub>MW</sub>  | 416.7 |          |     | ns   |                                       |

| WR/RD response time from DRQ ↑  | 4      | t <sub>MRW</sub> |       |          | 12  | μs   |                                       |

| TC pulse width                  | 4      | t <sub>TC</sub>  | 60    |          |     | ns   |                                       |

| RESET pulse width               | 5      | t <sub>RST</sub> | 60    |          |     | фсү  | Note 5                                |

AC Characteristics 3; High-Speed Floppy-Disk Control (cont)

| Parameter                             | Figure | Symbol           | Min  | Тур  | Max  | Unit | Conditions       |

|---------------------------------------|--------|------------------|------|------|------|------|------------------|

| Drive Side                            |        |                  |      |      |      |      |                  |

| RDATA high-level width                | 6      | t <sub>RDD</sub> | 40   |      |      | ns   |                  |

| WINDOW cycle time (Note 2)            | 6      | twcy             |      | 3.33 |      | μs   | MFM = 0          |

|                                       |        |                  |      | 1.67 |      | μs   | MFM = 1          |

| WINDOW setup time to RDATA (Note 2)   | 6      | twrd             | 15   |      |      | ns   |                  |

| WINDOW hold time from RDATA (Note 2)  | 6      | t <sub>RDW</sub> | 15   |      |      | ns   |                  |

| US0, US1 setup time to SEEK           | 7      | tus              | 20   |      |      | μs   | Note 3           |

| SEEK setup time to DIR                | 7      | t <sub>SD</sub>  | 11.7 |      |      | μs   | _                |

| DIR setup time to STEP                | 7      | <sup>t</sup> DST | 1.7  |      |      | μs   |                  |

| US0, US1 hold time from STEP          | 7      | tstu             | 8.3  |      |      | μs   | •••              |

| STEP high-level width                 | 7      | <sup>t</sup> STP | 10   | 11.7 | 13.3 | μs   | _                |

| USO, US1 hold time from SEEK (Note 4) | 7      | <b>t</b> su      | 25   |      |      | μs   |                  |

| DIR hold time from STEP               | 7      | tst0             | 40   |      |      | μS   | _                |

| SEEK hold time from DIR               | 7      | t <sub>DS</sub>  | 50   |      |      | με   |                  |

| STEP cycle time                       | 7      | tsc              | 55   |      |      | μз   | <del>-</del>     |

| FLTR high-level width                 | 8      | t <sub>FR</sub>  | 13.3 |      | 16.7 | με   | <del>-</del><br> |

| INDEX high-level width                | 8      | t <sub>IDX</sub> | 16   |      |      | ФСҮ  | Note 5           |

- (1) For data transfer in non-DMA mode.

- (2) When external VFO is used.

- (3) The minimum value for drive-side parameters is 50 ns less than the value expressed in μs. For example, 12 μs is actually 11.950 μs.

- (4) While the unit under test is performing a seek operation, the SENSE DEVICE STATUS command is being executed for the other devices.

- (5) φ<sub>CY</sub> is a multiple of the period of a quartz crystal resonator connected to pins XB1-XB2 or an external clock connected to pin XB1. The multiple is four (EXT = 0) or two (EXT = 1).

- (6) See figure 1 for timing measurement voltage thresholds.

Figure 1. Voltage Thresholds for Timing Measurements

Figure 2. Read Operation

Figure 3. Write Operation

Figure 4. DMA Operation

Figure 5. RESET Waveform

Figure 6. Device Read Operation

Figure 7. Seek Operation

Figure 8. FLTR and INDEX Waveforms

### Registers

The  $\mu$ PD72067 contains three 8-bit registers for interfacing the main system—data, status, and auxiliary command. Control signals  $\overline{CS}$ , A0,  $\overline{RD}$ , and  $\overline{WR}$  select a particular register operation as shown in table 1.

The data register temporarily stores information (command, parameter, data, or result status) transferred between the μPD72067 and the main system.

- (2) The status register (table 2) indicates the state of the μPD72067. The main system can read the status register contents at any time.

- (3) The auxiliary command register temporarily stores auxiliary commands given the μPD72067.

Table 1. Register Selection

| A0 | RD      | WR              | Operation                        |

|----|---------|-----------------|----------------------------------|

| 0  | 0       | 1               | Read status register             |

| 0  | 1       | 0               | Write auxiliary command register |

| 1  | 0       | 1               | Read data register               |

| 1  | 1       | 0               | Write data register              |

| ×  | х       | ×               | Not defined                      |

|    | 0 0 1 1 | 0 0 0 1 1 0 1 1 | 0 0 1<br>0 1 0<br>1 0 1<br>1 1 0 |

x = Don't care

- When the DACK input is active low, data register selection is independent of CS and A0.

- (2) When both \(\overline{\overline{\text{CS}}}\) and A0 are set to 0, a write of code other than auxiliary command code (\(\overline{\text{WR}}\) = 0) is inhibited.

| Table 2. St | tatus Regi | ister Contents |

|-------------|------------|----------------|

|-------------|------------|----------------|

| Bit | Name               | Symbol | Description                                                                                                                                                                                  |

|-----|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | Request for master | RQM    | Indicates $\mu PD72067$ is ready to transfer data to and from the main system. Operation depends on the DIO bit D6.                                                                          |

|     |                    |        | When DIO = 0, the main system sends data to $\mu$ PD72067. When the main system writes data into $\mu$ PD72067, RQM is set to 0; when $\mu$ PD72067 reads the data, RQM is set to 1.         |

|     |                    |        | C-phase, wait for command Non-DMA write E-phase SEEK type E-phase                                                                                                                            |

|     |                    |        | When DIO = 1, $\mu$ PD72067 sends data to the main system. When $\mu$ PD72067 places data in the data register, RQM is set to 1; when the main system reads the data, RQM is set to 0.       |

|     |                    |        | R-phase     Non-DMA read E-phase (except for READ ID)                                                                                                                                        |

| D6  | Data input/output  | DIO    | Indicates the data transfer direction between the main system and µPD72067.                                                                                                                  |

|     |                    |        | DIO Direction                                                                                                                                                                                |