vw<del>w.DataSheet4U.com</del>

**PRELIMINARY**

# **Switching Driver with Regulator** for Class-D Headphone Amplifier

## **■** GENERAL DESCRIPTION

The **NJU8716A/B** is switching driver with regulator for class-D headphone amplifier. It incorporates optimum regulator for the driver of headphone amplifier.

The **NJU8716A/B** converts 1bit audio signals such as PWM/PDM to analog audio signals with simple external LC low-pass filter.

The **NJU8716A/B** provides completed digital system and high power-efficiency with class-D operation. Therefore it is suitable for portable audio applications.

#### **■ PACKAGE OUTLINE**

**NJU8716AV, NJU8716BV**

## **■ FEATURES**

- 2-channel 1bit Audio Signal Input

- Headphone Output

- Built-in Regulator for Driver

- Logic Operating Voltage 1.7~3.0V(V<sub>DD</sub>)

- Driver Operating Voltage

1.6~3.5V(V<sub>DDO1</sub>, V<sub>DDO2</sub>)

- Regulator Operating Voltage 4.0~5.75V(V<sub>REG1</sub>)

1.9~4.0V(V<sub>REG2</sub>)

- C-MOS Technology

- Package Outline

SSOP16

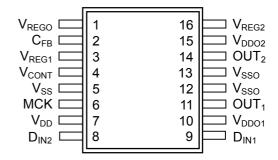

## **■ PIN CONFIGURATION**

## Version Lineup

| Version  | Data Latch              |

|----------|-------------------------|

| NJU8716A | The rising edge of MCK  |

| NJU8716B | The falling edge of MCK |

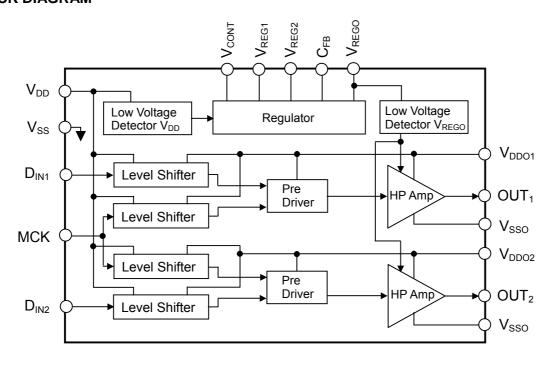

## ■ BLOCK DIAGRAM

# **■ TERMINAL DESCRIPTION**

| No.      | SYMBOL                               | I/O | FUNCTION                                                                                                                                               |

|----------|--------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | $V_{REGO}$                           | 0   | Regulator Output Terminal                                                                                                                              |

| 2        | $C_{FB}$                             | - 1 | Regulator Output Voltage Sense Terminal                                                                                                                |

| 3<br>16  | $V_{REG1} \ V_{REG2}$                | -   | Regulator Power Supply                                                                                                                                 |

| 4        | $V_{CONT}$                           | I   | Regulator Output Voltage Control Terminal                                                                                                              |

| 5        | $V_{SS}$                             | -   | Power GND:V <sub>SS</sub> =0V                                                                                                                          |

| 6        | MCK                                  | I   | Master Clock Input Terminal Audio signals are latched on the edge of MCK. A Version: latched on the rising edge B version: latched on the falling edge |

| 7        | $V_{DD}$                             | -   | Power Supply: V <sub>DD</sub> =2.0V                                                                                                                    |

| 9        | D <sub>IN1</sub><br>D <sub>IN2</sub> | I   | Audio Signal Input Terminal 1,2                                                                                                                        |

| 10<br>15 | $V_{ m DDO1} \ V_{ m DDO2}$          | -   | Driver Power Supply 1,2                                                                                                                                |

| 11<br>14 | OUT <sub>1</sub><br>OUT <sub>2</sub> | 0   | Output Terminal 1,2                                                                                                                                    |

| 12<br>13 | V <sub>SSO</sub>                     | -   | Driver GND: V <sub>SSO</sub> =0V                                                                                                                       |

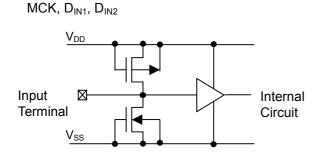

# ■ INPUT TERMINAL STRUCTURE

#### **■ FUNCTIONAL DESCRIPTION**

#### (1) Power Supply

$V_{DD}$ : Power supply for input circuit and control logic. Keep the input logic level less than  $V_{DD}$ .

If  $V_{DD}$  reaches less than sleep detection voltage, power consumption can be saved with halts of built-in

regulator.

$V_{\text{REG1}}: \text{Power supply for built-in regulator. Even after power-on, } V_{\text{REG1}} \text{ line is shut off with transistor switch until the state of the state$

V<sub>DD</sub> has been started up.

$V_{REG2}$ : Power supply for built-in regulator. Apply the required voltage with additional dropout voltage of regulator. By connecting  $V_{REGO}$  (regulator output) to  $V_{DDO1}$ ,  $V_{DDO2}$  (Driver power supply), the power is provided at the drivers. And furthermore, the regulator output should be supplied to  $V_{DDO1}$  and  $V_{DDO2}$  by connecting de-coupling capacitor to get highly smoothed power supply.

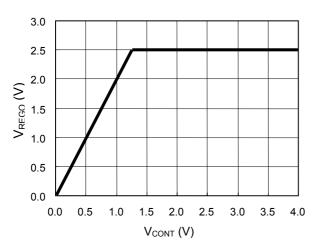

### (2) Regulator Output Voltage Control Terminal (V<sub>CONT</sub>)

$V_{CONT}$  is the control terminal for regulator output voltage.  $V_{REGO}$  terminal generates double the voltage of supplied voltage to  $V_{CONT}$ . (Shorted between  $V_{REGO}$ - $C_{FB}$ )

#### (3) Master Clock (MCK)

Master clock (MCK) synchronizes the audio signal inputs ( $DIN_1$  and  $DIN_2$ ). The setup time and the hold time should be kept in the AC characteristics because  $DIN_1$  and  $DIN_2$  are fetched with the rising edge of MCK in A version, and the falling edge of MCK in B version. During the standby condition, MCK requires "L" level to avoid unnecessary power consumption. In addition, MCK requires jitter-free or jitter as small as possible because the jitter could lead to poor S/N ratio.

#### (4) Signal Output (OUT<sub>1</sub> / OUT<sub>2</sub>)

$OUT_1$  and  $OUT_2$  terminals keep the Hi-z condition if output voltage of  $V_{REGO}$  is lower than detection voltage. Output signals are appeared as PWM signals through the use of  $V_{DDO1}$  and  $V_{DDO2}$  in the  $OUT_1$  and  $OUT_2$  terminals If the output voltage is over than detection voltage. Output signals will be converted to analog signals via 2nd-order or higher LC filter.

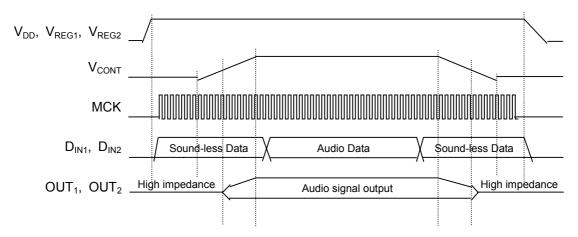

#### ■ POWER ON/DOWN SEQUENCE

The pop-noise can be effectively suppressed with the following sequence when power ON and OFF.

#### (1) Power ON Sequence

- 1) Start up  $V_{DD}$ ,  $V_{REG1}$  and  $V_{REG2}$ .

- 2) Input the master clock (MCK) and audio signals ( $D_{IN1}$ ,  $D_{IN2}$ ) after the start-up of  $V_{DD}$ ,  $V_{REG1}$  and  $V_{REG2}$ . At this time, audio signals must be input as "Sound-less data".

- 3) Increase V<sub>CONT</sub>.

- 4) Input the audio data after V<sub>CONT</sub> reaches a steady state.

#### (2) Power Down Sequence

The sequence must be executed in inverse order of the power ON sequence.

## ■ ABSOLUTE MAXMUM RATINGS

(Ta=25°C)

| PARAMETER             | SYMBOL                           | RATING                      | UNIT |

|-----------------------|----------------------------------|-----------------------------|------|

| Cunnily Voltage       | $V_{DD}$                         | -0.3 ~ +4.0                 | V    |

|                       | V <sub>DDO1</sub> , <sub>2</sub> | -0.3 ~ +4.0                 | V    |

| Supply Voltage        | $V_{REG1}$                       | V <sub>REG2</sub> ~ +6.0    | V    |

|                       | $V_{REG2}$                       | -0.3 ~ +5.5                 | V    |

| Input Voltage         | Vin                              | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| Operating Temperature | Ta                               | -20 ~ +85                   | °C   |

| Storage Temperature   | Tstg                             | -40 ~ +125                  | °C   |

| Power Dissipation     | $P_{D}$                          | 300 (SSOP16)                | mW   |

Note.1) The relations of "V<sub>DDO1</sub>,V<sub>DDO2</sub><V<sub>REG1</sub>", "V<sub>REG2</sub><V<sub>REG1</sub>", and "V<sub>DD</sub><V<sub>REG1</sub>" must be maintained during operations.

## **■ ELECTRICAL CHARACTERISTIC**

#### (1) DC CHARACTERISTIC

$\begin{array}{c} \text{(Ta=25°C, V}_{\text{DD}}\text{=}2.0\text{V, V}_{\text{DDO1}}\text{=}V_{\text{DDO2}}\text{=}1.8\text{V, V}_{\text{REG2}}\text{=}2.15\text{V, V}_{\text{REG1}}\text{=}5.0\text{V, V}_{\text{SS}}\text{=}V_{\text{SSO}}\text{=}0.0\text{V,} \\ \text{Load Impedance=}16\Omega, \ f_{\text{S}}\text{=}44.1\text{kHz, unless otherwise noted)} \end{array}$

| Load impedance-ross, ig-44. Iki iz, diness otherwise i |                  |                                                                                               |                    |      |             |      |

|--------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|--------------------|------|-------------|------|

| PARAMETER                                              | SYMBOL           | CONDITIONS                                                                                    | MIN                | TYP  | MAX         | UNIT |

| Supply Voltage                                         | $V_{DD}$         |                                                                                               | 1.7                | 2.0  | 3.0         | V    |

|                                                        | $V_{DDO}$        |                                                                                               | 1.6                | 1.8  | 3.5         | V    |

| Output Driver<br>High side Resistance                  | R <sub>H</sub>   | OUT <sub>1, 2</sub> =V <sub>DDO</sub> -0.1V                                                   | 1                  | 1.5  | 2           | Ω    |

| Output Driver<br>Low side Resistance                   | $R_L$            | OUT <sub>1, 2</sub> =0.1V                                                                     | ı                  | 1.5  | 2           | Ω    |

| Power Supply Current At Operating (Mute signal input)  | I <sub>DD</sub>  | No-load operating D <sub>IN1</sub> , D <sub>IN2</sub> =16f <sub>S</sub> MCK=256f <sub>S</sub> | -                  | 0.05 | 0.10        | MA   |

|                                                        | I <sub>DDO</sub> |                                                                                               | -                  | 0.25 | 0.5         |      |

| Digital Input Voltage                                  | V <sub>IH</sub>  | MCK, D <sub>IN1</sub> , D <sub>IN2</sub>                                                      | 0.7V <sub>DD</sub> | -    | $V_{DD}$    | V    |

|                                                        | V <sub>IL</sub>  | MCK, D <sub>IN1</sub> , D <sub>IN2</sub>                                                      | 0                  | -    | $0.3V_{DD}$ | V    |

| Input Leakage Current                                  | I <sub>LK</sub>  | MCK, D <sub>IN1</sub> , D <sub>IN2</sub>                                                      | -                  | -    | ±1          | μA   |

Note.2) All voltage are relative to " $V_{SS} = V_{SSO} = 0V$ " reference.

Note.3) The LSI must be used inside of the "Absolute maximum ratings". Otherwise, a stress may cause permanent damage to the LSI.

Note.4) De-coupling capacitors for " $V_{DD}-V_{SS}$ ", " $V_{DDO1}-V_{SSO}$ " and " $V_{DDO2}-V_{SSO}$ " should be connected for stable operation.

## (2) REGULATOR CHARACTERRITICS

(Ta=25°C,  $V_{DD}$ =2.0V,  $V_{DDO1}$ = $V_{DDO2}$ =1.8V,  $V_{REG2}$ =2.15V,  $V_{REG1}$ =5.0V,  $V_{SS}$ = $V_{SSO}$ =0.0V, Load Impedance=16 $\Omega$ ,  $f_S$ =44.1kHz, unless otherwise noted)

| PARAMETER                                               | SYMBOL               |                                                                               | DITIONS                                    | MIN | TYP  | MAX        | UNIT  |

|---------------------------------------------------------|----------------------|-------------------------------------------------------------------------------|--------------------------------------------|-----|------|------------|-------|

| Power Supply                                            | $V_{REG1}$           |                                                                               |                                            | 4.0 | -    | 5.75       | V     |

| Power Suppry                                            | $V_{REG2}$           |                                                                               |                                            | 1.9 | -    | 4.0        | V     |

| Power Supply Current                                    | I <sub>REG2</sub>    | No load                                                                       | D <sub>IN1</sub> =L<br>D <sub>IN2</sub> =L | -   | 0.4  | 0.8        | mA    |

| At Operating                                            | I <sub>REG1</sub>    | - No-load                                                                     |                                            | -   | 0.1  | 0.2        |       |

| Off-Leakage Current                                     | I <sub>REG1OFF</sub> | V <sub>DD</sub> =0.5V<br>or lower                                             | - MCK=L                                    | -   | -    | 1          | μA    |

| Input Voltage                                           | $V_{CONT}$           |                                                                               |                                            | 0   | -    | $V_{REG2}$ | V     |

| Input Leakage Current                                   | I <sub>LK</sub>      | V <sub>CONT</sub>                                                             |                                            | -   | -    | ±1         | μA    |

|                                                         | $V_{REGO1}$          | V <sub>REG2</sub> =2.5V                                                       | ′, V <sub>CONT</sub> =1.0V                 | 1.9 | 2.0  | 2.1        | V     |

| Output Voltage                                          | $V_{REGO2}$          | V <sub>REG2</sub> =2.5V                                                       | , V <sub>CONT</sub> =0V                    | -   | -    | 0.1        | V     |

| Output Current                                          | I <sub>OUT</sub>     |                                                                               |                                            | 70  | -    | -          | mA    |

| Output Sink Current                                     | I <sub>SINK</sub>    |                                                                               |                                            | 60  | -    | -          | mA    |

| V <sub>REG2</sub> -V <sub>REGO</sub><br>Dropout Voltage | $\Delta V_{IO}$      |                                                                               |                                            | -   | -    | 0.2        | V     |

| Ripple Rejection                                        | RR                   | Vr=0.1Vrms<br>fr=1kHz                                                         | s,lout=70mA                                | 36  | 44   | -          | dB    |

| Load Regulation Voltage                                 | $V_{LR}$             | V <sub>OUT1</sub> =V <sub>OUT</sub><br>f <sub>OUT1</sub> =f <sub>OUT2</sub> = | <del>-</del>                               | -   | 690  | 1228       | μVrms |

| V <sub>REGO</sub><br>Low Voltage Detection              | $V_{DET1}$           |                                                                               |                                            | 1.1 | 1.25 | 1.4        | V     |

|                                                         | $V_{DET2}$           | Ta=-20 ~+7                                                                    | ′0°C                                       | 1.0 | 1.25 | 1.5        | V     |

| Sleep Detection Voltage                                 | $V_{DET3}$           |                                                                               |                                            | 0.5 | 0.75 | 1.0        | V     |

Note.5) V<sub>LR</sub> (Load Regulation Voltage) is effective with our measurement PCB only.

The following figure shows a representative example of  $V_{REGO}$  versus  $V_{CONT}$  at  $V_{REG2}$ =2.5V.

Note.6) Output voltage of  $V_{REGO}$  is maximum  $V_{REG2}$ . In  $V_{DDO1}$  and  $V_{DDO2}$  terminals supplied from  $V_{REGO}$ , please set  $V_{REG2}$  and  $V_{CONT}$  not to exceed their operating voltage.

www.DataSheet4U.com

# (3) AC CHARACTERISTICS

$(Ta=25^{\circ}C,\,V_{DD}=2.0V,\,V_{DDO1}=V_{DDO2}=1.8V,\,V_{REG2}=2.15V,\,V_{REG1}=5.0V,\,V_{SS}=V_{SSO}=0.0V,\,\\ Load\ Impedance=16\Omega,\,\,f_S=44.1kHz,\,\,unless\,\,otherwise\,\,noted)$

|                                                |                   | Load Impedal | 100-1032, 15- | TT. IKI IZ, UIIK | COO OTHER WISC | , Hotcu |

|------------------------------------------------|-------------------|--------------|---------------|------------------|----------------|---------|

| PARAMETER                                      | SYMBOL            | CONDITION    | MIN           | TYP              | MAX            | UNIT    |

| MCK Frequency                                  | f <sub>MCKI</sub> |              | 8             | ı                | 25             | MHz     |

| MCK Pulse Width (H)                            | t <sub>MCKH</sub> |              | 12            | -                | -              | ns      |

| MCK Pulse Width (L)                            | t <sub>MCKL</sub> |              | 12            | -                | -              | ns      |

| D <sub>IN1</sub> , D <sub>IN2</sub> Setup Time | t <sub>DS</sub>   |              | 20            | -                | -              | ns      |

| D <sub>IN1</sub> , D <sub>IN2</sub> Hold Time  | t <sub>DH</sub>   |              | 20            | -                | -              | ns      |

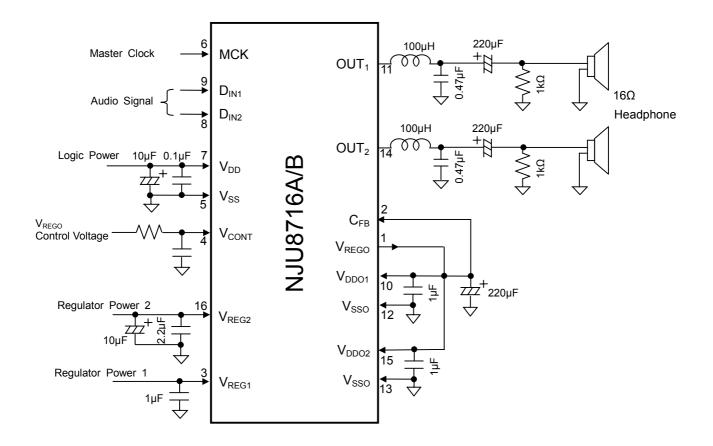

#### ■ APPLICATION CIRCUIT

- Note.7) De-coupling capacitors must be connected between each power supply pin and GND.

The capacitor value should be adjusted on the application circuit and the temperature. It may malfunction if capacity value is small.

- Note.8) A large-capacitance for the de-coupling capacitors for headphone speaker is recommended to improve a low-frequency characteristics. In addition, a low-ESR(Equivalent series resistance) capacitor is recommend for high power efficiency.

- Note.9) The above circuit shows only application example and does not guarantee the any electrical characteristics. Therefore, please test the circuit carafully to fit your application.

#### [CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.