# SALI-25C Device Six ATM Line Interface at 25 Mbit/s TXC-07625

### **DATA SHEET**

#### FEATURES I

- Transmission Convergence

- meets ATM Forum specifications

- maps ATM cells to six 25.6 Mbit/s payloads

- NRZI/NRZ and 5B/4B conversions

- scrambling, cell delineation and rate adaptation

- HEC generate/check with bad cell discard

- transmit GFC insertion for Xon/Xoff

- · Line Interface

- six independent lines each with data and clock

- line rate at 32 Mbaud +/- 100ppm

- detects received illegal 5B codes

- direct interface to 25 Mbit/s 5 volt transceivers

- idle signal generation on the line side

- single transmit clock input for all six line signals

- 8 kHz timing marker output

- 8-bit 33 MHz or UTOPIA Level 1 and 2 Interface

- single cell available cell level control

- 3 cells per line FIFO in the receive direction

- 2 cells per line FIFO in the transmit direction

- optional 4 priority queues per line sharing 2048 or 4096-cell external SRAM buffer for transmit

- · Discarded, received and transmitted cell counts

- · External memory (SRAM) interface

- External transceiver and LED controls

- Intel/Motorola processor interface with interrupts

- Test Access Port (IEEE 1149.1 boundary scan)

- Single +3.3 V, ±5% power supply, 0.6W max.

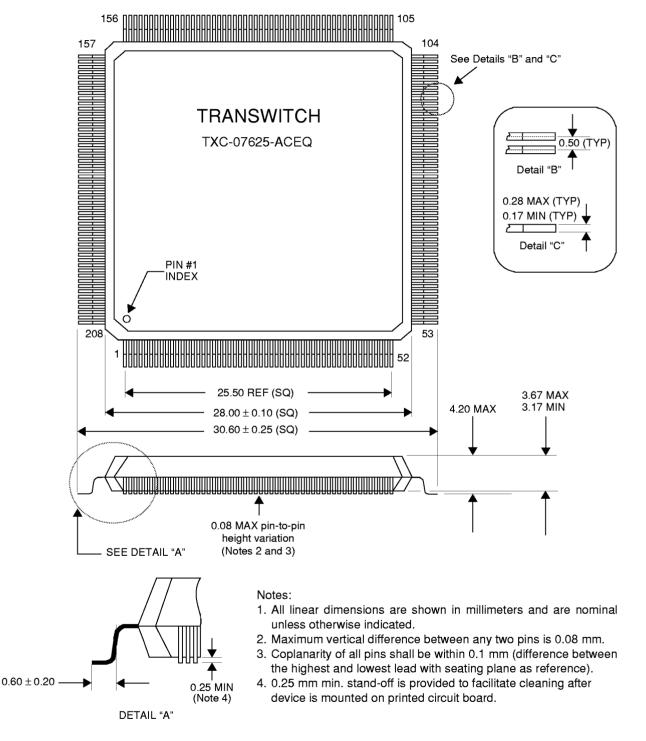

- 208-pin plastic quad flat package

### **DESCRIPTION**

The SALI-25C VLSI device is a controller for six 25.6 Mbit/s ATM Line Interfaces, with a common 8-bit parallel transmit and receive UTOPIA interface on the terminal side. It performs the transmission convergence function of six independent 25.6 Mbit/s bit-serial line signals used for connection to private UNIs, and the terminal side interface employs single cell I/O signals.

The device is designed to interface directly on the line side with PMD devices such as the TranSwitch ALI-25T ATM Line Interface 25 Mbit/s Transceiver (part number TXC-07225-BCPL). It performs NRZI/NRZ conversion, data deserialization, 5B/4B decoding, descrambling, cell delineation, and idle byte discard in the receive direction, and the inverse processes in the transmit direction. The SALI-25C provides an 8-bit 33 MHz multi-PHY UTOPIA cell interface with ATM layer devices. The SALI-25C also provides a special UTOPIA mode for interfacing with the TranSwitch CUBIT or CUBIT-*Pro CellBus* Bus Switch VLSI device (TXC-05801 or TXC-05802).

### **APPLICATIONS** ■

- · PC and Work-station Network Interface Adaptors

- ATM Concentrators

- ATM Hubs

- Local and Campus ATM Switches

- ATM Access Switches

U.S. and/or foreign patents pending. Copyright © 1999 TranSwitch Corporation SARA-2, CUBIT-Pro and CellBus are trademarks of TranSwitch Corporation TranSwitch, TXC, CUBIT and SALI-25C are registered trademarks of TranSwitch Corporation

Document Number: TXC-07625-MB Ed. 4, February 1999

# **TABLE OF CONTENTS**

| Section                                                | <u>Page</u> |

|--------------------------------------------------------|-------------|

| List of Figures                                        |             |

| References                                             |             |

| Block Diagram                                          | 5           |

| Block Diagram Description                              | 6           |

| Receive Direction                                      | 6           |

| Receive Transmission Convergence                       | 6           |

| Port Address Insertion                                 |             |

| Receive Cell Output Block                              | 8           |

| Transmit Direction                                     | 9           |

| Transmit Cell Input                                    |             |

| UTOPIA Interface                                       |             |

| Unicast/Multicast for Single-PHY UTOPIA                |             |

| Unicast/Multicast for Multi-PHY UTOPIA                 |             |

| Delay Sensitive (CBR) Traffic Support                  | 11          |

| Transmit Cell Buffers and SRAM                         | 14          |

| Cell Inlet Burst Rate                                  | 15          |

| TxCLAV Generation                                      |             |

| Effect of TXENn on Cell Buffers                        |             |

| Transmit Transmission Convergence                      |             |

| Microprocessor Interface                               |             |

| Cell Counters                                          |             |

| Multicast Indicators                                   |             |

| External Device Controls                               |             |

| Serial Line Control Interface Port                     |             |

| Transmitter Control                                    |             |

| Loopback Control                                       |             |

| Serial LED Control Interface Port                      |             |

| Interfacing with CUBIT and ALI-25T                     |             |

| Pin Diagram                                            |             |

| Pin Descriptions                                       |             |

| Absolute Maximum Ratings And Environmental Limitations |             |

| Thermal Characteristics                                |             |

| Power Requirements                                     |             |

| Input, Output and I/O Parameters                       |             |

| Timing Characteristics                                 |             |

| Operation                                              |             |

| Test Access Port                                       |             |

| Memory Map                                             |             |

| Memory Map Descriptions                                |             |

| Package Information                                    |             |

| Ordering Information                                   |             |

| Related Products                                       |             |

| Standards Documentation Sources                        |             |

| List of Data Sheet Changes                             |             |

| Documentation Update Registration Form*                | 75          |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

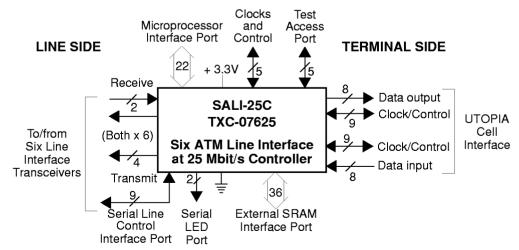

| Figure 1.  | SALI-25C TXC-07625 Block Diagram                                            | 5  |

|------------|-----------------------------------------------------------------------------|----|

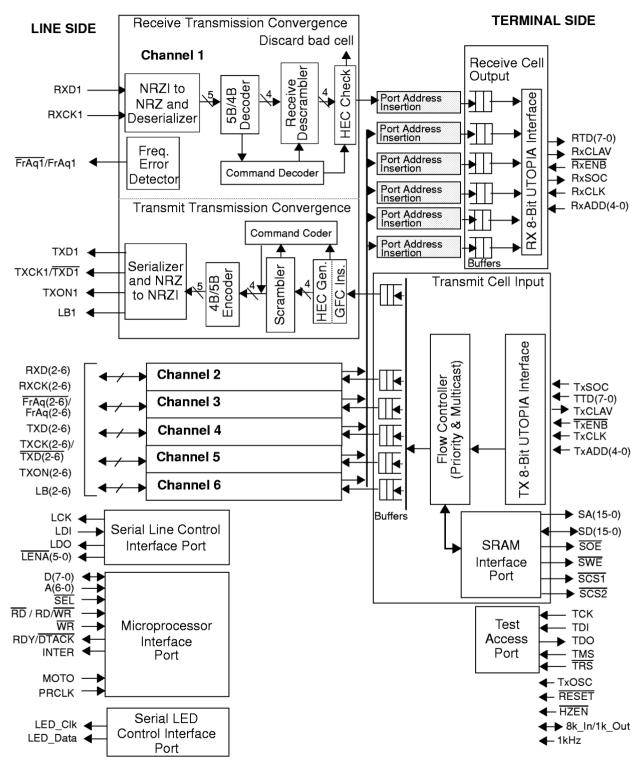

| Figure 2.  | PRNG Logic Diagram                                                          | 7  |

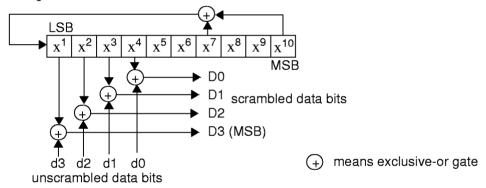

| Figure 3.  | RX Line to UTOPIA Port Address Insertion                                    | 8  |

| Figure 4.  | TX Using Inband Port ID                                                     | 9  |

| Figure 5.  | TX Using Inband Multiport Indicator                                         | 10 |

| Figure 6.  | TX Using Inband Session Indicator                                           | 10 |

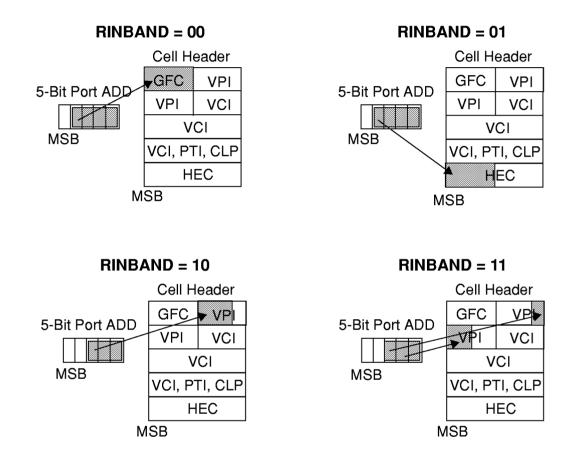

| Figure 7.  | Inband Priority Indicator                                                   | 11 |

| Figure 8.  | Interfacing with one 64k x 16 SRAM                                          | 14 |

| Figure 9.  | Interfacing with two 128k x 8 SRAMs                                         | 15 |

| Figure 10. | Relationships of the Status and Event Indicator Bits to the Alarm Condition | 18 |

| Figure 11. | LED Drivers Circuit                                                         | 20 |

| Figure 12. | Interconnection for SALI-25C, ALI-25T and CUBIT                             | 21 |

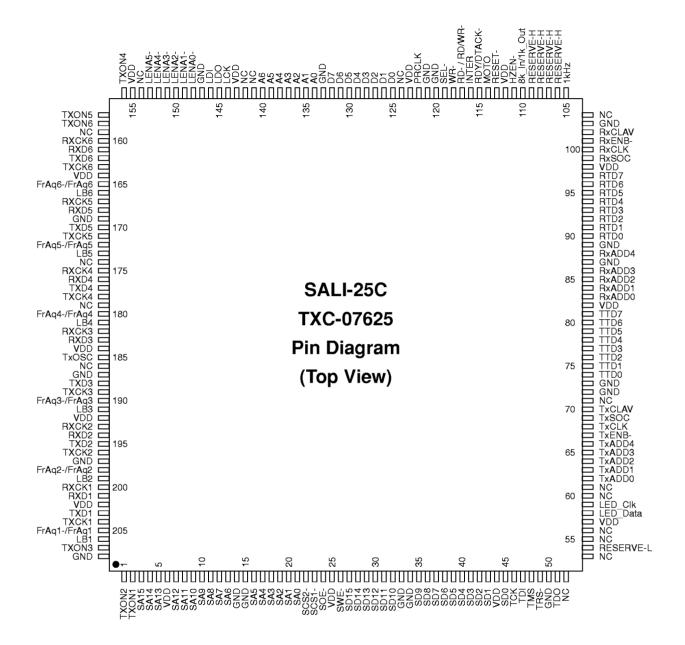

| Figure 13. | SALI-25C TXC-07625 Pin Diagram                                              | 24 |

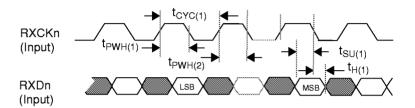

| Figure 14. | Receive/Transmit Line Interface Timing                                      | 34 |

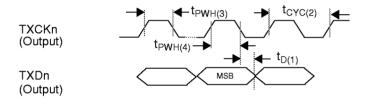

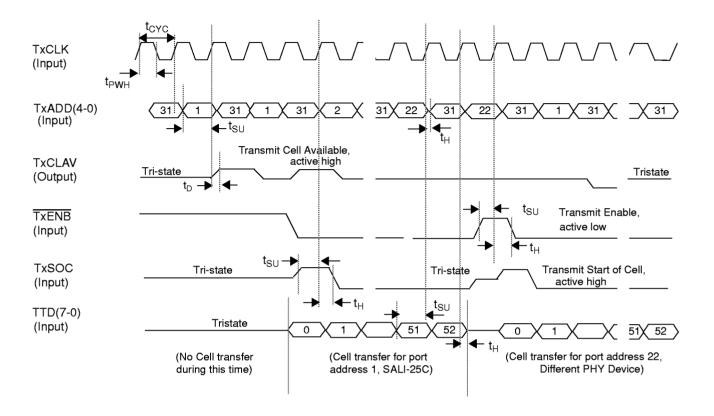

| Figure 15. | Cell Output Timing, Multi-PHY UTOPIA Mode                                   | 35 |

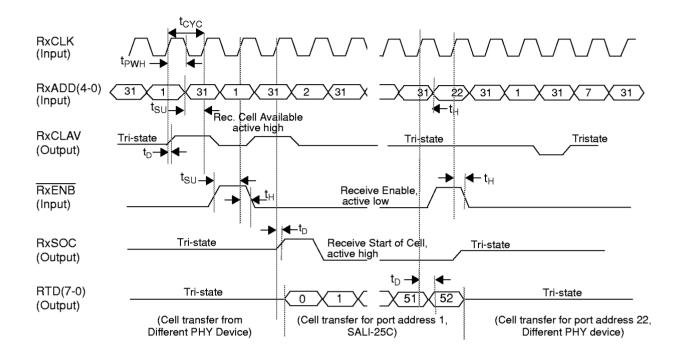

| Figure 16. | Cell Input Timing, Multi-PHY UTOPIA Mode                                    | 36 |

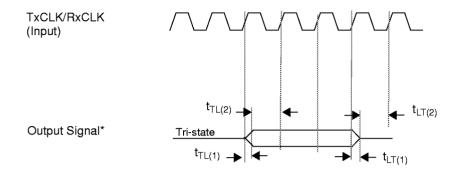

| Figure 17. | Tri-state Timing for UTOPIA Mode                                            | 37 |

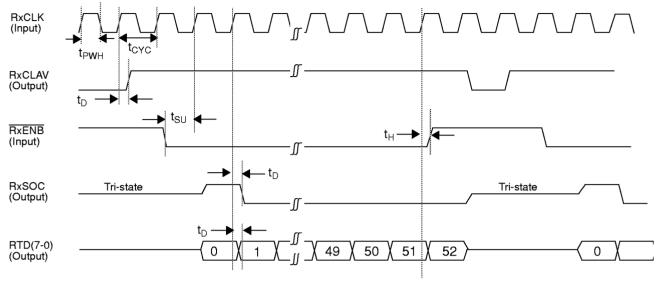

| Figure 18. | Cell Output Timing, single-PHY UTOPIA Mode                                  | 38 |

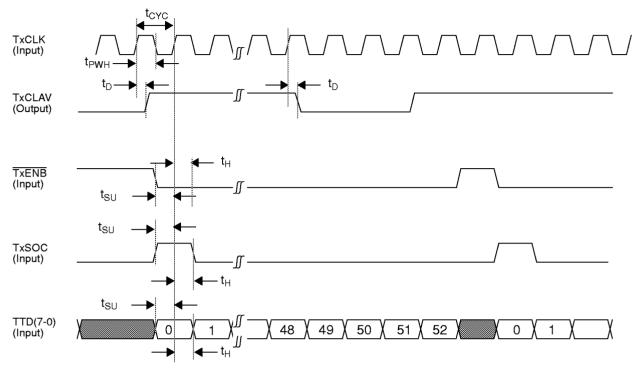

| Figure 19. | Cell Input Timing, single-PHY UTOPIA Mode                                   | 39 |

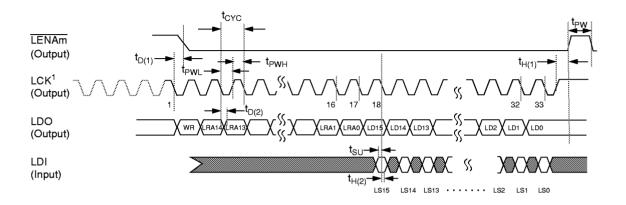

| Figure 20. | Serial Line Control Interface Port Timing                                   | 40 |

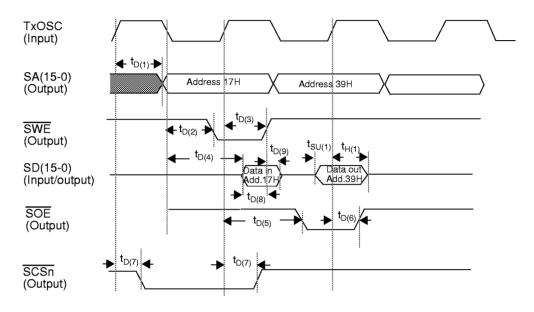

| Figure 21. | External SRAM Timing - Read/Write                                           | 41 |

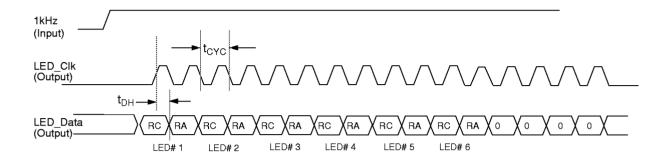

| Figure 22. | Serial LED Control Port Data Output Timing                                  | 42 |

| Figure 23. | Microprocessor Read Timing - Intel Mode                                     | 43 |

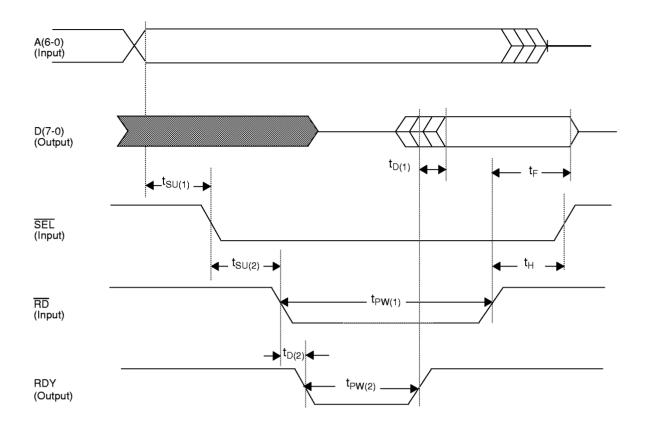

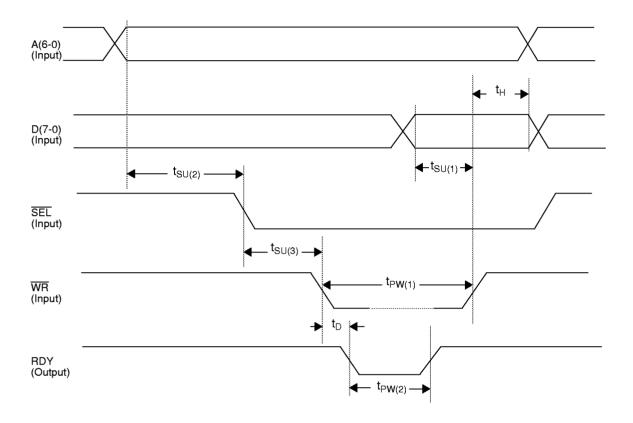

| Figure 24. | Microprocessor Write Timing - Intel Mode                                    | 44 |

| Figure 25. | Microprocessor Read Timing - Motorola Mode                                  | 45 |

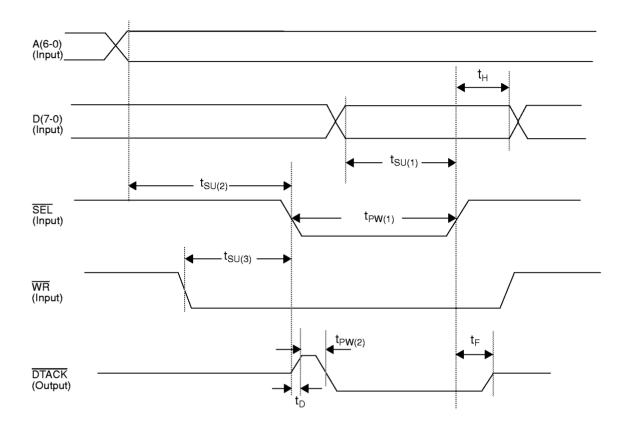

| Figure 26. | Microprocessor Write Timing - Motorola Mode                                 | 46 |

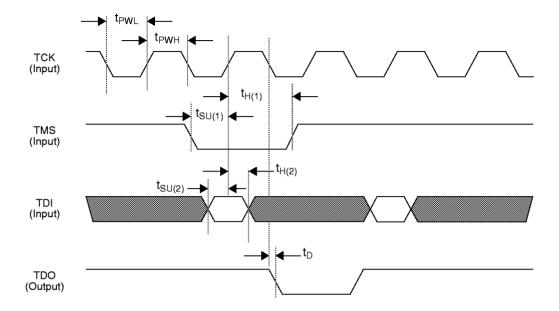

| Figure 27. | Boundary Scan Timing                                                        | 47 |

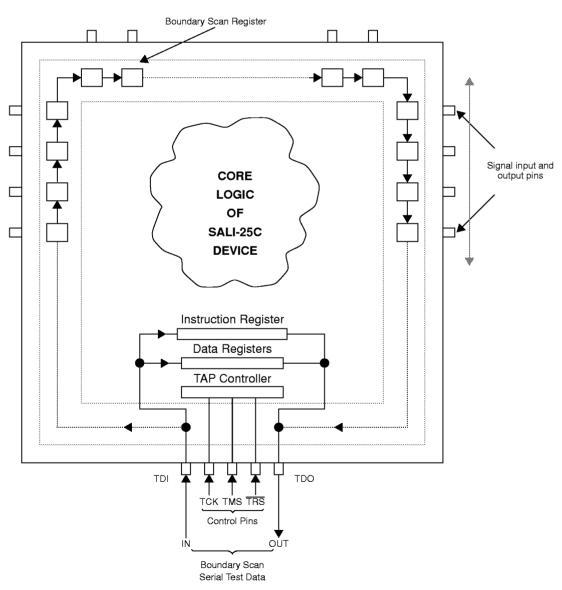

| Figure 28. | Boundary Scan Schematic                                                     | 49 |

| Figure 29. | SALI-25C TXC-07625 208-Pin Plastic Quad Flat Package                        | 67 |

## **REFERENCES**

Copies of the following reference documents may be obtained from the issuing organizations, which are listed in the Standards Documentation Sources section:

Physical Interface Specification for 25.6 Mbit/s Over Twisted Pair Cable, af-phy-0040.000 Letter Ballot, ATM Forum Technical Committee, 6/95.

UTOPIA, an ATM-PHY Interface Specification, Level 2 V1.0, af-phy-0039.000, ATM Forum Technical Committee, 6/95.

BISDN User-Network Interface - Physical Layer Specification, ITU-T Recommendation I.432

### **BLOCK DIAGRAM**

Note: The variable n is used throughout this document to represent a channel/line number (n = 1-6).

Figure 1. SALI-25C TXC-07625 Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

#### RECEIVE DIRECTION

A block diagram of the SALI-25C is shown in Figure 1. On the line side, the Receive data path for channel n (where n = 1-6) takes in serial data at 32 Mbit/s from the ALI-25T or equivalent line transceiver, converts the data from NRZI format to NRZ format (if enabled), and then deserializes it into a parallel 5-bit symbol. The 5-bit symbols are then decoded into a 4-bit nibble of scrambled data and unscrambled control codes. The control nibbles are sent to the command decoder while the data nibbles are send to the descrambler. The receive descrambler converts the scrambled nibble into data. The data nibbles are converted into bytes and stored in a 3-cell buffer after the cell HEC byte is verified and the port address is inserted, if selected. Data is then extracted from the terminal side receive output by an ATM layer device (such as the TranSwitch CUBIT). Throughout the receive data path, the information contained in the control or command symbol-pair is used by the various functional blocks to maintain proper operation and data flow.

### **Receive Transmission Convergence**

#### NRZI to NRZ Format Conversion and Deserializer

The serial data input signal RXDn can be sampled on the rising or falling edge of the input clock RXCKn, as determined by the common control bit FALL. If it is in NRZI format, the received data is converted to NRZ format before being deserialized to 5-bit parallel data symbols. The NRZI to NRZ conversion is bypassed if control bit NRZ is set to 1 for receipt of NRZ data input. The 5-bit symbol X (00010) is used for symbol alignment and recognition of sequential symbol-pairs containing commands. The aligned 5-bit data is sent to the 5B/4B decoder block, which decodes it to 4-bit nibbles. The clocking for this section is provided by the line interface transceiver.

### Frequency Error Detector

The frequency error detector has as inputs the local oscillator (TxOSC) and the recovered receive clock from the line interface transceiver phase-locked loop (RXCKn). This circuit detects the frequency difference between TxOSC, which is used for transmission, and RXCKn, which is used for reception. When a frequency error is detected, it triggers the FREQEn interrupt, if enabled, and the "frequency acquisition" pin ( $\overline{FrAqn}/FrAqn$ ) is asserted (low if control bit INVFRAQ = 0, high if INVFRAQ = 1) for at least 72 microseconds (please see the Memory Map and Memory Map Descriptions sections for details of control bits and other register bits). The  $\overline{FrAqn}/FrAqn$  pin is used to initialize the transceiver device, such as the TranSwitch ALI-25T. The frequency error detector will detect a frequency deviation of (1.2  $\pm$  0.4)% or more. The response time from no transition on the receive clock to assertion of the  $\overline{FrAqn}/FrAqn$  output signal is less than 0.2 microseconds. Repeated FREQEn interrupts can be used as an indicator of loss-of-signal from the associated line.

#### 5B/4B Decoder Block

The 5B/4B Decoder block converts the 5-bit symbols to scrambled nibble data according to the following table:

| 5B Symbol | 00000   | 00001   | 00010   | 00011   | 00100   | 00101   | 00110   | 00111 | 01000   | 01001   | 01010 |

|-----------|---------|---------|---------|---------|---------|---------|---------|-------|---------|---------|-------|

| 4B Data   | Illegal | Illegal | Х       | Illegal | Illegal | Illegal | Illegal | 0100  | Illegal | 0001    | 0010  |

| 5B Symbol | 01011   | 01100   | 01101   | 01110   | 01111   | 10000   | 10001   | 10010 | 10011   | 10100   | 10101 |

| 4B Data   | 0011    | Illegal | 0101    | 0110    | 0111    | Illegal | Illegal | 1000  | Illegal | illegal | 0000  |

| 5B Symbol | 10110   | 10111   | 11000   | 11001   | 11010   | 11011   | 11100   | 11101 | 11110   | 11111   |       |

| 4B Data   | Illegal | 1100    | Illegal | 1001    | 1010    | 1011    | Illegal | 1101  | 1110    | 1111    |       |

The fifteen 5-bit symbols that have no 4-bit decoded equivalent should not occur, and are classified as "illegal". The symbol that represents X is unique, and is used as the first (marker) symbol of a 2-symbol command. Upon its recognition, the decoder detects that the next symbol will be the second symbol of the command symbol-pair. Of the 17 possible commands (XX, X0,...,XF), only three are defined, as follows:

- XX = Start of cell with scrambler / descrambler initialized

- X4 = Start of cell without scrambler / descrambler initialized

- X8 = 8 kHz timing pulse marker (this command is ignored)

- Xi, where i = 0, 1, 2, 3, 5, 6, 7, 9, A, B, C, D, E, and F, are undefined commands and are ignored without affecting the normal operation of the SALI-25C.

The descrambled data derived from a received illegal 5B code is replaced with the previously descrambled legal code at all times including the idle period. The descrambler continues to run during the received illegal code cycle. The received illegal 5B code also triggers the 5BCODEn interrupt, if enabled.

Repeated 5BCODEn interrupts can be used as an indicator of loss-of-data from the associated line.

#### Descrambler/Scrambler

The descrambler takes the 4-bit nibbles and descrambles them in exactly the inverse of the manner in which they were scrambled in the transmit side of the SALI-25C. The scrambler and descrambler are each comprised of a 10-bit pseudo-random number generator (PRNG) based on the polynomial  $x^{10} + x^7 + 1$ . The PRNG logic diagram is shown in Figure 2 below:

Figure 2. PRNG Logic Diagram

Both the scrambler and descrambler are reset to their initial states when the XX command is detected. The three types of command bytes are not scrambled prior to transmission, so they are not descrambled by the receive descrambler.

The PRNG is clocked 4 times after each nibble regardless of whether the command byte, valid data or idle data is being transmitted. The PRNG is reset to its initial state (3FFH) upon every detection of the XX command, regardless of whether the XX nibbles are byte-aligned. The first nibble that follows is exclusive or-gated with the initial F(Hex) of the scrambler sequence in bits  $x^4-x^1$ , unless it is part of a command byte.

#### Cell Header Error Checking and Bad Cell Discard

After descrambling, the header CRC of each received cell is checked for correctness. This is achieved by calculation of a CRC-8 over the first four bytes of each cell and the modulo-2 addition of a 01010101 sequence (the COSET polynomial), and then comparing the resulting value to the received HEC value (the fifth byte) in the cell. If the HEC check fails, or if fewer than 53 bytes are received, the cell is discarded as a bad cell; otherwise, the cell is sent to the port address insertion block and then stored in the 3-cell buffer to be sent as output on the UTOPIA receive terminal interface. A cell that is discarded due to HEC check failure triggers the corresponding RHECEn interrupt, if enabled, and increments the corresponding 24-bit roll-over discarded bad HEC cell counter. Short cells that are discarded would neither cause an interrupt nor increment the discarded cell counter.

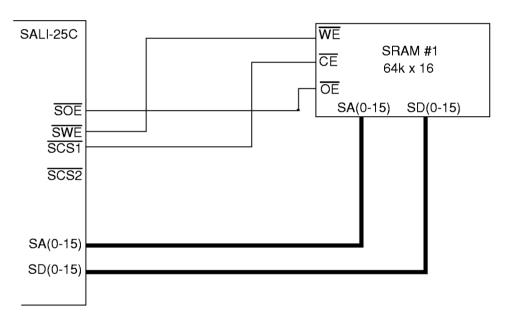

#### **Port Address Insertion**

Port address is inserted inband in the cell header if the SALI-25C is in single-PHY UTOPIA mode. The 3 or 4 LSBs of the 5-bit port address in configuration register ADDn(4-0) are inserted in the 4-bit GFC field if control bits RINBAND = 00, in the HEC 7:4 bits if RINBAND = 01, in the VPI 7:5 bits if RINBAND = 10, or in the VPI 4:2 bits if RINBAND = 11, as shown in Figure 3.

Figure 3. RX Line to UTOPIA Port Address Insertion

#### **Receive Cell Output Block**

The Receive Cell Output Block (RCOB) supports a fully ATM Forum-compliant 8-bit single-PHY or multi-PHY UTOPIA interface on the cell input/output terminal side interface, depending on the state of control bit U1. There is a 3-cell FIFO buffer for each line. A receive line buffer full (RBFULn) interrupt, if enabled, is generated to alert the user when the third cell buffer is being filled with a cell having a correct HEC. This will allow the user a minimum of 0.0146 milliseconds to perform flow control and stop the line input before the 3-cell buffer overflows. The RBFULn status is exited when two empty cell spaces become available. When a cell is ready in the buffer, this block coordinates the transfer of the ATM cell to the ATM layer device and performs all the necessary handshaking to transfer the data between the chips. Only cells which have a correct HEC before the port address insertion block, and the correct 53-byte count, are transferred out of the receive interface. There is no HEC regeneration in the receive direction.

In the single-PHY UTOPIA mode, cells are serviced on a first-come, first-served basis. In the multi-PHY UTOPIA mode, cell transfer is controlled by the ATM layer.

#### TRANSMIT DIRECTION

The ATM terminal passes cells from the UTOPIA interface to the Transmit Cell Input block to be stored in the appropriate channel's cell buffer at its output. A new HEC byte is generated for each cell before scrambling and conversion to symbols by the 4B/5B encoder. The 5-bit symbols are then serialized and converted to NRZI format (if enabled) before they are sent as bit-serial output on the line interface. In addition, flow control and frame synchronization are also supported. Flow control is achieved by setting the GFC nibble to the proper XON/XOFF value before HEC generation, and the 8 kHz frame synchronization symbol is sent out when it is required.

### **Transmit Cell Input**

Fully ATM Forum-compliant 8-bit single-PHY or multi-PHY UTOPIA cell input interfaces are supported. There is a 4-cell buffer at the UTOPIA interface for decoupling the cell input rate from the internal rate.

#### **UTOPIA** Interface

The UTOPIA interface can be set to operate in either single- or multi-PHY mode. The UTOPIA interface can work with either single or priority queueing, and unicasting or multicasting. The assertion of the TxCLAV output pin is dependent on the number of queues serviced by the TxCLAV signal and the value of control bit DROPCELL. Further detail is provided below.

The UTOPIA interface keeps track of the received cell byte count. Received short cells are dropped. Received long cells are transmitted with the extra bytes dropped.

### Unicast/Multicast for Single-PHY UTOPIA

Both unicast and multicast operations are supported in the single-PHY UTOPIA mode. For unicast operation, control bit MCAST must be set to 0. For multicast, MCAST must be set to 1. The ID of the port selected is carried inband using one of the following three methods:

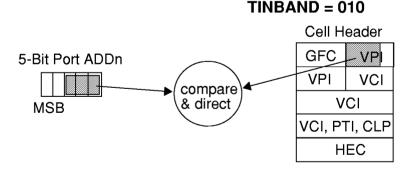

- Uses inband port ID: TINBAND=010 selects this method. In this method, bits VPI 7:5 are used to compare with the 3 LSBs of the stored port ID in register ADDn, i.e., bits ADDn(2-0), as shown in Figure 4. The cell is directed to the channel with matching ADDn(2-0). An unmatched cell is discarded and the ROTOn alarm is triggered. Multicast and priority queuing are not supported.

Figure 4. TX Using Inband Port ID

Uses inband multiport indicator: TINBAND=001, 011 or 100 selects this method. In this method, the ports receiving the cell to be transmitted onto the line are indicated in the multiport indicator, which is a 6-bit port map located in the cell header, as shown in Figure 5. The presence of a 1 in the 6-bit port map indicates that the corresponding port is selected. The 6-bit port map is configured in descending order, with the MSB mapped to port 6. The ports selected for multicasting are indicated only by bits in the 6-bit port map.

Figure 5. TX Using Inband Multiport Indicator

Uses inband session indicator: TINBAND=000 selects this method. This method uses 55-byte mode with a 6-bit inband index carried by the MS tag byte that points to an internal multicast indicator, as shown in Figure 6. This method supports 64 active multicast or unicast transmit sessions simultaneously and is intended for use directly with the TranSwitch CUBIT VLSI device.

Figure 6. TX Using Inband Session Indicator

#### Unicast/Multicast for Multi-PHY UTOPIA

Both unicast and multicast operation are supported in the multicast mode. For unicast operation, control bit MCAST must be set to 0, and the port selection is governed only by the input pins TXADD(4-0). The inband multicast indicator is not used. For multicast operation, control bit MCAST must be set to 1, and the port selection is based on both the input pins TXADD(4-0) and the inband multiport indicator, as described above for the single-PHY mode, i.e., via a 6-bit port map indicated by TINBAND = 001, 011 or 100 (TINBAND = 000 or 010 are not supported). Cells admitted must have the TXADD(4-0) inputs matching the port address stored in registers ADDn and also the same port bit set in the inband multiport indicator. Other ports can also be set in the inband multiport indicator. In addition, the port addresses set in the ADDn registers have to be different from one another, i.e., two ports cannot have the same address.

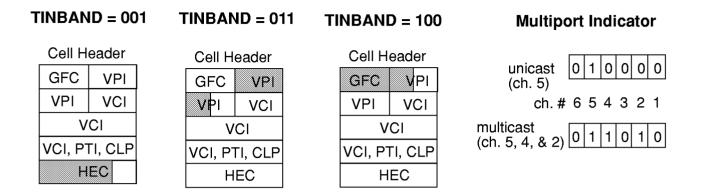

### **Delay Sensitive (CBR) Traffic Support**

Support for CBR traffic is through the use of an external SRAM cell buffer and the queueing of the received cells in pre-determined priority order for transmission onto the line. Setting control bit 4Q=1 allows the user to prioritize up to 4 queues per channel of different priority levels. Priority information is carried in the two bits of the cell header selected by the control bits TINBAND, as shown in Figure 7. For these two priority bits, 00 represents the highest priority and 11 represents the lowest priority. In addition, the user is required to set the minimum number of cell buffer blocks (4 cells per block) used in external SRAM for each priority by specifying registers MINLPij where ij indicates priority 00 to 11. MINLPij can be set to a value from 0 to 14. The number of cell buffer blocks reserved per channel is MINLPij + 1, i.e., if MINLP00 = 0, the external SRAM buffer used for the highest priority per channel is 1 block or 4 cells. Therefore, the range of cell space that can be reserved per channel for any priority is from 4 to 60 cells, in steps of 4, as shown in the table below. This cell buffer setting will provide a guaranteed initial space allocation for cells of the associated priority. In addition, LINKRES must be set to the value LINKRES =  $3 \times [MINLP00 + MINLP10 + MINLP11]$ .

| 4Q = 1, 4K = 0 or 1 |          |             |          |  |  |  |  |

|---------------------|----------|-------------|----------|--|--|--|--|

| Priority            | Register |             |          |  |  |  |  |

| Filotity            | Name     | per channel |          |  |  |  |  |

| Highest             | MINLP00  | 0 - 14      | 4 - 60   |  |  |  |  |

|                     | MINLP01  | 0 - 14      | 4 - 60   |  |  |  |  |

| <b> </b>            | MINLP10  | 0 - 14      | 4 - 60   |  |  |  |  |

| Lowest              | MINLP11  | 0 - 14      | 4 - 60   |  |  |  |  |

|                     | LINKRES  | 0 - 168     | 16 - 240 |  |  |  |  |

## **TINBAND** = 000 (CUBIT Mode)

Cell Header

| MS Tag Byte   |             |  |  |  |  |  |  |  |

|---------------|-------------|--|--|--|--|--|--|--|

| LS Tag        | LS Tag Byte |  |  |  |  |  |  |  |

| GFC           | VPI         |  |  |  |  |  |  |  |

| VPI VCI       |             |  |  |  |  |  |  |  |

| VCI           |             |  |  |  |  |  |  |  |

| VCI, PTI, CLP |             |  |  |  |  |  |  |  |

| HE            | C           |  |  |  |  |  |  |  |

# TINBAND = 001

Cell Header

| GFC    | VPI     |

|--------|---------|

| VPI    | VCI     |

| V      | CI      |

| VCI, P | ΓΙ, CLP |

| Н      | EC      |

TINBAND = 011

Cell Header

| GFC    | VPI     |  |  |  |  |

|--------|---------|--|--|--|--|

| VPI    | VCI     |  |  |  |  |

| V      | CI      |  |  |  |  |

| VCI, P | ΓΙ, CLP |  |  |  |  |

| HEC    |         |  |  |  |  |

TINBAND = 100

Cell Header

| GFC    | VPI     |

|--------|---------|

| VPI    | VCI     |

| V      | CI      |

| VCI, P | ΓI, CLP |

| Н      | EC      |

Figure 7. Inband Priority Indicator

If priority queueing is not used (4Q=0), MINLP11 and MINLP10 are used as byte MINLP. The 6 LSBs of MINLP set the minimum cell buffer size for all 6 channel queues. LINKRES should be set to 3 x MINLP in this case. For 4K=0 or 1, MINLP can be set to a value from 0 to 63, corresponding to reserving 1 to 64 blocks (4 to 256 cells) of buffer per channel, as shown in the table below.

| 4Q = 0, 4K = 0  or  1     |         |         |             |  |  |  |  |

|---------------------------|---------|---------|-------------|--|--|--|--|

| Register Cell Space resei |         |         |             |  |  |  |  |

| Priority                  | Name    | Range   | per channel |  |  |  |  |

| None                      | MINLP   | 0 - 63  | 4 - 256     |  |  |  |  |

|                           | LINKRES | 0 - 189 | 4 - 256     |  |  |  |  |

The queue size, once specified, is fixed and can be changed only after chip reset (software or hardware).

If priority queueing is selected (4Q=1), cells in the highest priority non-empty queue are output until the queue is empty, before a cell from the next priority non-empty queue is sent. The last valid byte is repeatedly sent out when all the queues used for this port are empty.

The following table summarizes the use of the TINBAND control bits for inband port address and priority communications:

| CONTROL BITS | Bits Used to Carry the Multi-port Indicator,                                               | Bits Used For                            |  |  |

|--------------|--------------------------------------------------------------------------------------------|------------------------------------------|--|--|

| TINBAND      | Index, or Port Address                                                                     | Priority Indication                      |  |  |

| 000          | 6 LSBs of the most significant tag byte as an index to the multi-port indicator            | 2 LSBs of the least significant tag byte |  |  |

| 001          | HEC 7:2 is the 6-bit multi-port indicator                                                  | HEC 1:0                                  |  |  |

| 010**        | VPI* 7:5 bits carry the 3 LSBs of the port ID (Multicast and 4-priority queue not allowed) | only single queue<br>allowed             |  |  |

| 011          | VPI* 7:2 is the 6-bit multi-port indicator                                                 | VCI 15:14                                |  |  |

| 100          | 4 GFC bits and VPI* 7:6 contain the multi-port indicator                                   | VPI* 5:4                                 |  |  |

| others       | not used                                                                                   | not used                                 |  |  |

<sup>\*</sup> The VPI bits (2, 3, 4 or 6 bits) and the VCI bits used are reset to zeros before being sent as output to the line. The GFC bits are always replaced with 0000 if XOFFn=0, or the 4-bit value of the XCODE field in register 03H if XOFFn = 1.

<sup>\*\*</sup> TINBAND = 010 should only be used for unicast and single-PHY.

The different UTOPIA interface modes and features that are available if TINBAND is set to 000, 001, 011 or 100 are summarized below:

| Mode      |               |              |        | Control Bits |    |       |    |          |

|-----------|---------------|--------------|--------|--------------|----|-------|----|----------|

| Ext. SRAM | UTOPIA        | Cast         | Queues | XRAM         | U1 | MCAST | 4Q | DROPCELL |

|           | Single-PHY    | Uni          | 1      | 0            | 1  | 0     | 0  | 0/1      |

| No        | Sirigle-FHT   | Multi        | 1      | 0            | 1  | 1     | 0  | 0/1      |

| INO       | Multi-PHY     | Uni          | 1      | 0            | 0  | 0     | 0  | 0        |

|           | Wulli-Ph t    | Multi        | 1      | 0            | 0  | 1     | 0  | 0        |

|           |               | Uni<br>Multi | 1      | 1            | 0  | 0     | 0  | 0        |

|           | Multi-PHY     |              | 4      | 1            | 0  | 0     | 1  | 0/1      |

|           | Widiti-F Fi f |              | 1      | 1            | 0  | 1     | 0  | 0        |

| Yes       |               | IVIUILI      | 4      | 1            | 0  | 1     | 1  | 0/1      |

| res       |               | Uni          | 1      | 1            | 1  | 0     | 0  | 0/1      |

|           | Single-PHY    | Uni          | 4      | 1            | 1  | 0     | 1  | 0/1      |

|           | Siligie-Ffff  | Multi        | 1      | 1            | 1  | 1     | 0  | 0        |

|           |               | IVIUILI      | 4      | 1            | 1  | 1     | 1  | 0/1      |

If TINBAND is set to 010, multicast and priority queueing are not supported and only the following modes are supported:

| Mode                         |            |     |   |      | Cor | ntrol Bit | s  |          |

|------------------------------|------------|-----|---|------|-----|-----------|----|----------|

| Ext. SRAM UTOPIA Cast Queues |            |     |   | XRAM | U1  | MCAST     | 4Q | DROPCELL |

| No                           | Single-PHY | Uni | 1 | 0    | 1   | 0         | 0  | 0/1      |

| Yes                          | Single-PHY | Uni | 1 | 1    | 1   | 0         | 0  | 0/1      |

#### Transmit Cell Buffers and SRAM

There are six internal 2-cell buffers in the Transmit Cell Input block, which are used to send output cells to the lines at about 3.2 MByte/s per line. Each of the 2-cell buffers accepts cells either from the 4-cell UTOPIA buffer or from the external cell buffers (if these are used). Priority queueing is not supported if external cell buffers are not used, and the control bit 4Q is ignored.

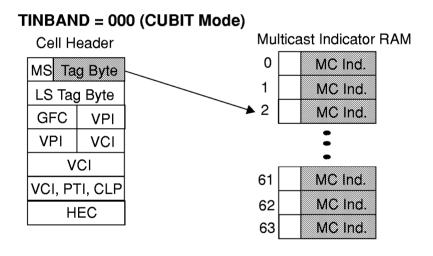

Control bit XRAM must be set to 1 to indicate that external SRAM is used in the transmit path for all six lines. Control bit 4K must be set to 1 to indicate that two SRAMs are used and 4K must be set to 0 to indicate that one SRAM is used. In this mode the transmitted cell is first stored in the external SRAM before it is transferred to the internal cell buffers. Each cell is stored in a 32-word page. The write and read operations to the SRAM are controlled by linked lists. For priority queueing operation there are 25 linked lists, composed of 4 linked lists per line and a free buffer linked list. For single queue operation there are 7 linked lists, composed of 1 linked list per line and a free buffer linked list. The free buffer linked list contains all the cell spaces that are freed up after a stored cell is read out.

If only one SRAM device is used it should be a 64k x 16 SRAM. The SCS1 output should be tied directly to the SRAM's Chip enable pin CE and SCS2 is not used, as shown in Figure 8 below:

Figure 8. Interfacing with one 64k x 16 SRAM

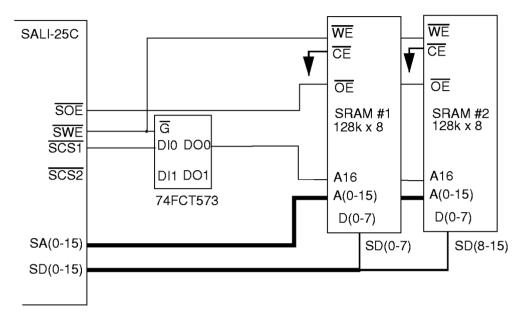

If two SRAM devices are used, they should be 128k x 8 SRAMs. The SCS1 output is used as address pin A16 after being latched by an Integrated Device Technology, Inc. (Tel. 408-727-6116) 74FCT573 or equivalent device. The SCS2 output is not used, and the two SRAM chip enable pins CE should be grounded. The interfacing is shown in Figure 9 below. This dual SRAM configuration is preferred to the single SRAM configuration.

Figure 9. Interfacing with two 128k x 8 SRAMs

Suitable SRAM devices are available from several vendors. The devices selected must satisfy the timing requirements shown in Figure 21. Inquiries related to 64k x 16 devices may be directed to vendors of Micron, NEC and Samsung products. Inquiries related to 128k x 8 devices may be directed to vendors of IDT, Micron, Motorola, NEC, Samsung and Toshiba products.

#### **Cell Inlet Burst Rate**

The cell inlet burst rate depends on whether there is external SRAM and the number of channels to which the incoming cell is multicasted. If external SRAM is not used (register bit XRAM=0) the UTOPIA interface stops transferring cells if there are a total of 2 cells destined to any one port in the combined 2-cell transmit buffer and the 4-cell UTOPIA FIFO.

If external SRAM is used (XRAM=1), input cells are first buffered in the 4-cell UTOPIA FIFO and then transferred to the external SRAM. The difference between the cell rate coming from the UTOPIA interface and the rate at which cells are written to the external SRAM will fill the 4-cell UTOPIA FIFO; this will stop the UTOPIA interface and limit the burst size. The multi-PHY UTOPIA interface stops if an input cell is destined for a full queue in SRAM or if the 4-cell UTOPIA FIFO is full. The single-PHY UTOPIA interface stops if any queue in SRAM is full or if the 4-cell UTOPIA FIFO is full. The following table shows some representative cell burst sizes for different UTOPIA speeds:

| # Ch. Multicasted | UTOPIA Rate |               |                |                |          |          |  |  |  |  |

|-------------------|-------------|---------------|----------------|----------------|----------|----------|--|--|--|--|

| # Cn. Mullicasted | 16 MHz      | 20 MHz        | 25 MHz         | 29 MHz         | 32 MHz   | 33 MHz   |  |  |  |  |

| 1                 | Burst conti | nuously until | the external b | ouffer is full | 22 cells | 17 cells |  |  |  |  |

| 2                 | 22 cells    | 8 cells       | 6 cells        | 5 cells        | 5 cells  | 5 cells  |  |  |  |  |

| 3                 | 6 cells     | 5 cells       | 5 cells        | 4 cells        | 4 cells  | 4 cells  |  |  |  |  |

| 4                 | 5 cells     | 4 cells       | 4 cells        | 4 cells        | 4 cells  | 4 cells  |  |  |  |  |

| 5                 | 4 cells     | 4 cells       | 4 cells        | 4 cells        | 4 cells  | 4 cells  |  |  |  |  |

| 6                 | 4 cells     | 4 cells       | 4 cells        | 4 cells        | 4 cells  | 4 cells  |  |  |  |  |

#### **TxCLAV** Generation

The generation of the TxCLAV output signal depends on the states of the control bits DROPCELL, XRAM, U1, MCAST and on the various cell buffer or queue conditions. Cells received from the UTOPIA interface can be dropped, and the DROPCn interrupt is triggered (if enabled) when DROPCELL is set to 1 and there is no line buffer (internal or external) available for cell transfer from the UTOPIA buffer.

#### Effect of TXENn on Cell Buffers

In order to provide maximum UTOPIA buffer efficiency in all configurations, the incoming cell is only written into the 4-cell UTOPIA cell buffer if at least one of the designated channels is enabled, e.g., if a cell is multicasted to channels 1 and 3, the cell will be written to the cell buffer only if one or both of TXEN1 and TXEN3 are set to 1. The ROTO1 interrupt would be triggered if TXEN1=0 and the ROTO3 interrupt would be triggered if TXEN3=0.

In addition, TXENn has to be 1 in all configurations before a cell is transferred from the 4-cell UTOPIA cell buffer to the channel n internal buffer (if XRAM=0) or to the external channel n SRAM buffer (if XRAM=1).

#### **Transmit Transmission Convergence**

The blocks comprising the Transmit Transmission Convergence function accept byte data from the cell buffer, calculate and add the CRC header, scramble the 53-byte ATM data, add the proper command codes, perform 4B/5B encoding, serialize the symbols, and convert the NRZ serial data to NRZI (if NRZ=0) format before sending it to the line interface for transmission. If the line is idle without any cell pending in the buffer, the last data byte of the last cell is sent as output repeatedly until a new cell arrives.

### **HEC Generation**

The HEC generator calculates and overwrites the HEC byte of a cell received in the 53-byte format. According to standard, the HEC is modified before transmission by the addition, modulo-2, of a 01010101 sequence (the COSET polynomial). The leading "0" bit is added to the first outgoing HEC bit, and the trailing "1" bit is added to the final outgoing HEC bit. On reception, the same 01010101 sequence is added to the received HEC bits before checking. The double addition of the 01010101 pattern, first at the generator, then at the decoder, has no net effect on the HEC process. The purpose of the pattern addition is to increase the probability of state transitions between adjacent bits in the HEC byte.

#### Cell Scrambling

The Transmit Scrambler accepts 4-bit nibbles from the HEC generator block and converts them into 4 bits of pseudo-random data. All 53 bytes in an ATM cell are scrambled.

#### Command Coder

The command coder generates three types of command codes:

- XX, a symbol-pair to indicate start-of-cell with scrambler reset. This command is sent before the first byte of an ATM cell.

- X4, a symbol-pair to indicate start-of-cell without scrambler reset. This command is sent before the first byte of an ATM cell.

- X8, a symbol-pair to indicate an 8 kHz synchronization event. This command is sent immediately after receiving the 8 kHz pulse on a symbol-pair boundary.

The scrambler reset command is sent out every 125 microseconds, or on the first cell transmitted after an idle period of more than 125 microseconds. The SALI-25C uses either an internally generated 8 kHz clock (derived from TxOSC/4000) or an external 8 kHz clock to insert the scrambler reset command. There will not be any command code sent out during an extended idle period. The last byte of the last cell sent out is sent repeatedly during the idle period.

The 8 kHz clock can be sourced externally via the 8k\_ln/1k\_Out pin or generated internally, by setting the control bit EXT8K to 1 or 0, respectively. The 8 kHz marker output on the Tx lines is enabled by setting the 8KEN control bit to 1.

Note: If control bit EXT8K is set to 1 (i.e., the external 8 kHz clock option is selected) and no external 8 kHz clock is provided via the 8k\_ln/1k\_Out pin, then no scrambler reset command will be generated, and synchronization problems may occur.

#### 4B/5B Encoder

The 4B/5B Encoder block takes the input nibbles from the scrambler and converts them into 5-bit symbols. The most important reason for this encoding is to guarantee sufficient data transitions for reliable clock recovery. The second reason is to help identify uniquely the command symbols generated by the Transmit Transmission Convergence block. These nibbles are encoded into non-data 5-bit symbols. This allows the receiver to recognize when a symbol-pair (i.e., the current and the previous 5-bit symbols) are control information and are not a part of the ATM cell itself.

### Serializer and NRZ to NRZI Formatter

The serializer takes the 5-bit symbols from the 4B/5B Encoder and converts them into serial data. The serial data is sent out in NRZ format or further converted into NRZI format before transmission. The transmit clock frequency of 32 MHz is determined by the clock provided at the TxOSC input pin. TXDn is clocked out on the falling edge of the corresponding TXCKn clock that is derived from TxOSC input.

#### Transmit Line Output Control

Control bit TXENn provides individual transmit line output control. In all situations, setting TXENn to 0 holds the TXDn pin low and the TXCKn pin low if control bit NTDAT is set to 0, and holds the TXDn pin low and the TXDn pin high if NTDAT is set to 1. This function is useful in stopping the individual line transmitter without setting the transmitter to the standby (TXONn de-asserted) mode. If TXENn is set to 0 during operation, the corresponding buffer for that line will be flushed.

#### Flow Control

A simple XON/XOFF flow control mechanism is implemented to facilitate flow control on the line. An XOFFn bit is provided for each channel, to set the GFC nibble being sent out on the transmit line n. XOFFn = 1 sets the GFC nibble to use the value stored in XCODE, and 0 sets it to 0000. The GFC nibble is always replaced just before HEC calculation is performed. The GFC nibble can be used with the RBFULn alarm to regulate the traffic flow from the line.

### **MICROPROCESSOR INTERFACE**

The microprocessor interface of the SALI-25C is designed to operate with a microprocessor clock input PRCLK (8.25-28 MHz), a 7-bit address input bus A(6-0), and a bidirectional 8-bit data bus D(7-0). It can be configured, by setting input pin MOTO, to be compatible with either Motorola or Intel type microprocessors.

#### Interrupt

The microprocessor interrupt pin INTER may be asserted on occurrence of any one or more of the following alarms or events:

- 6 alarm conditions each per port (DROPCn, ROTOn, 5BCODEn, RBFULn, RHECEn and FREQEn)

- 6 common port events (CHERRn).

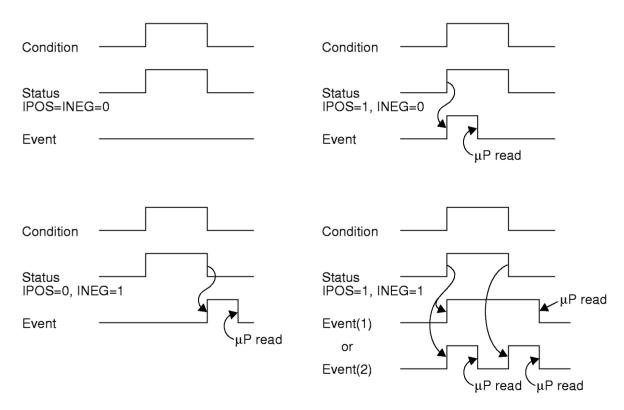

There are three register bits associated with each of these events that may be enabled to cause an interrupt: the interrupt mask bit (read/write), the status bit (read-only), and the event bit (read-only, latched to 1 when set). Each event bit can be enabled to cause an interrupt by setting the corresponding interrupt mask bit to 0. The status bit is pulsed or set to 1 during the occurrence of the alarm condition and is set to 0 at other times. The pulsed status bits (DROCPn and ROTOn) are only used to set the corresponding event bits; they are not to be monitored by the user. The status bits (5BCODEn, RHECEn, RBFULn, and FREQEn) that are set on a condition can be used to monitor on-going conditions. The setting of the event bit is user-selected to be positive edge or negative edge triggered by the corresponding status bit. The event bits can only be cleared on read by the microprocessor. The relationships of the status and event indicator bits to the alarm condition are shown in Figure 10 below:

Figure 10. Relationships of the Status and Event Indicator Bits to the Alarm Condition

There is a common channel event polling register at address 30H (read-only). It contains separate single bits for each channel. Each of these bits is set to 1 while any associated event is latched to 1. The common channel register cannot be enabled to cause an interrupt, but may be used in alarm polling management schemes.

### **Cell Counters**

There are three 24-bit roll-over counters for each port: a discarded cell counter, a received cell counter, and a transmitted cell counter. The discarded cell counter counts all the received cells that are discarded due to invalid HEC. The received cell counter counts all the full length cells (53 bytes) that have valid HEC. The transmitted cell counter counts all the cells that are completely sent as output, i.e., when the 53rd byte of the cell is transferred out of the line buffer. If any channel (n) is disabled by setting TXENn=0, the corresponding transmitted cell counter could be high by 1.

On power-up, these counters are in random states and have to be initialized to 000000H by writing to the counter locations through the microprocessor. Software reset would not change the counter values. Writing to a counter is achieved by loading the 24-bit count to registers 5DH-5FH first, and then writing register 5CH with a 0 in control bit CRW and the desired counter address in CADD(4-0). Reading is achieved by first writing register 5CH with a 1 in CRW and the desired counter address in CADD(4-0), and then reading the 24-bit count from the registers 5DH-5FH.

#### **Multicast Indicators**

There are 64 internal RAM addresses used to support up to 64 different multicast sessions when TINBAND is set to 000 for working with a CUBIT device. These registers have to be configured by writing to the RAM addresses. The read and write operations of these registers are the same as described above for the cell counters except that these RAM locations can only be verified by reading the location twice, immediately after it has been written, and disregarding the result of the first read operation.

#### **EXTERNAL DEVICE CONTROLS**

#### **Serial Line Control Interface Port**

The 9-pin Serial Line Control Interface Port is composed of six serial line enable output pins, a clock output pin, and data input and output pins. The six serial line enable pins allow control and communications to six external line transceiver devices through the registers in the SALI-25C.

To write to an external device, the 16-bit data word is first written into line data word LD(15-0) in registers 15H and 16H. Then a 0 is written into control bit LRW (register 11H, bit 7) together with the 15 line address bits LRA(14-0) in registers 11H and 12H. Upon writing the line number LN(2-0) to register 10H, the LENAm pin (m is set by the line number LN(2-0) of register 10H) is first asserted low and then the 32 bits (in the order of LRW, LRA14, LRA13, ..., LRA0, LD15, ..., LD0) are output on pin LDO on the falling edge of LCK. The LENAm pin is deasserted after the output of the 32nd bit.

To read from an external device, a 1 is written into control bit LRW (register 11H, bit 7) together with the 15 line address bits LRA(14-0) in registers 11H and 12H. Upon writing the line number LN(2-0) to register 10H, the LENAm pin (m is set by the line number LN(2-0) of register 10H) is first asserted low and then the 16 bits (in the order of LRW, LRA14, LRA13, ..., LRA0) are output on pin LDO on the falling edge of LCK. Input data bits LS15 to LS0 are latched on the rising edge of the 17th to 32nd LCK clock pulses after LENAm is asserted. The LENAm pin is deasserted after the output of the 32nd LCK clock. Input line data word LS(15-0) in registers 13H and 14H can be read once the line status bit LSTATUS (register 17H, bit 0) is set to 0, indicating the completion of the read operation.

#### **Transmitter Control**

Six output pins, TXONn, are provided to turn on and off individual transmitters in external line transceiver devices. Each of these pins can be forced low by setting control bit FTOFFn to 1. Control bit INVTXO inverts the output polarity of all these TXONn pins when it is set to 1. FTOFFn = 1 also forces the TXCKn and TXDn pins to low.

### **Loopback Control**

Six output pins, LBn, are provided to set external line transceivers into their Loopback mode. These pins can be set to low by setting control bit FLBn to 0 or to high by setting FLBn to 1.

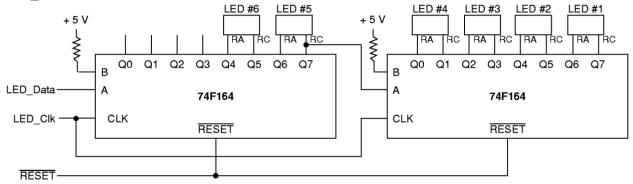

#### Serial LED Control Interface Port

The two output pins of the Serial LED Interface Port, LED\_Clk and LED\_Data, are provided to control six LED drivers through two external shift registers such as those contained in 74F164 devices, as shown in Figure 11. A burst of 16 clocks and data is output on the LED\_Clk and LED\_Data pins once every millisecond, as shown in Figure 22. The clocks on LED\_Clk are used to shift the data on LED\_Data out to the Qn outputs of the external shift registers. The LED\_Clk frequency, 2.06 MHz to 7.00 MHz, is derived from the microprocessor clock PRCLK. LED\_Data, which is a serial signal of 12 data bits and 4 zeros, is output on the falling edge of the LED\_Clk.

Figure 11. LED Drivers Circuit

The 12 data bits are arranged as six sets of RA and RC bits for the 6 LEDs. Each pair of RA and RC bits is set by 3 control bits LEDnC(2-0), where n indicates the line number, as shown in the table below:

| LEDnC(2-0) | RA                                                | RC                   | Condition and LED Color                                                                                  |

|------------|---------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|

| 000        | 0                                                 | 1                    | Received or transmitted a cell on the port line. Port will output this data for a minimum 50 ms (green). |

| (default)  | 0                                                 | 0                    | No Tx or Rx cell (LED off).                                                                              |

| 001        | 0                                                 | 1                    | Set by microprocessor (green).                                                                           |

| 010        | 1                                                 | 0                    | Set by microprocessor (red).                                                                             |

| 011        | $RA = D & RC = \overline{D}$                      | oscillating at 1 kHz | Set by microprocessor (yellow).                                                                          |

| 111        | $RA = D \& RC = \overline{D}$ and turned on/off a |                      | Set by microprocessor (yellow, flashing at 3 Hz).                                                        |

| other      | 0                                                 | 0                    | Set by microprocessor (LED off).                                                                         |

The default setting for each port is LEDnC(2-0) = 000. In this setting the outputs of RA and RC are dependent on the cell traffic on the port. Every cell received or transmitted will trigger a retriggerable  $50 \pm 1$  milliseconds period where RA is set to 0 and RC is set to 1, which is latched in the 74F164 to drive the LED to green. Both RA and RC are reset to 0s if there is no cell traffic for 50 milliseconds.

Other RA and RC outputs are directly controlled by the microprocessor. Setting LEDnC(2-0) = 011 makes RA the inverse of RC, and both bits invert once every 1 millisecond. Inverting the opposite values of RA and RC at 1 millisecond intervals turns on the LED to oscillating green and red to generate yellow. LEDnC(2-0) = 111 is LEDnC(2-0) = 011 gated at  $3 \pm 0.05$  Hz<sup>1</sup>, which is yellow flashing at  $3 \pm 0.05$  Hz<sup>1</sup>.

Note 1: The period is based on the actual input frequency on pin 105 (1 kHz).

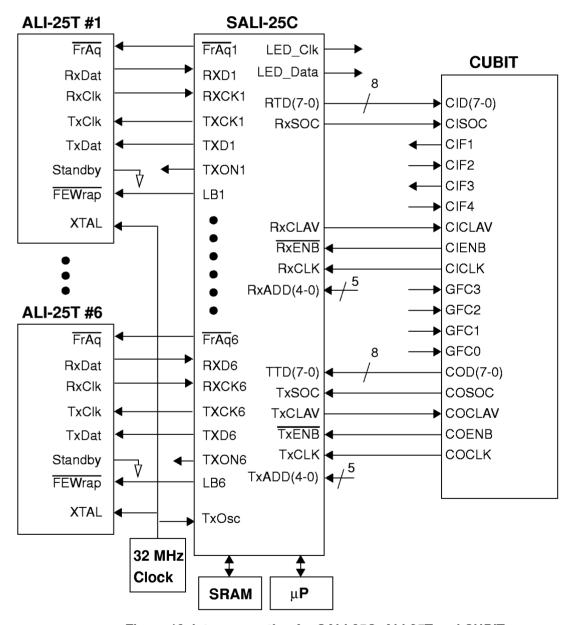

### **INTERFACING WITH CUBIT AND ALI-25T**

Note: This subsection was written for an earlier Edition of the Data Sheet. The ALI-25T device has since been discontinued by our supplier and the CUBIT device is not now recommended for use in new designs. However, similar functionality may be implemented by using another 25 Mbit/s transceiver, such as the six-port Novacom NOV25PMD6, and the CUBIT-Pro (TXC-05802B) successor to the CUBIT. Please refer to the documentation for these devices (see Web sites www.novacom.com and www.transwitch.com).

The SALI-25C can be interfaced to six ALI-25T "B" version transceiver devices (part number TXC-07225-BCPL) with the interconnection and memory configurations shown in Figure 12 and Table 1.

Figure 12. Interconnection for SALI-25C, ALI-25T and CUBIT

When interfacing to a CUBIT device (Figure 12), the CUBIT should be set to NNI mode and the SALI-25C should be set to use external SRAM (control bit XRAM set to 1) and single-PHY UTOPIA (control bits set to U1 = 1, RINBAND = 00, TINBAND = 000). The input signals on the TXADD(4-0) and RXADD(4-0) pins are ignored. There are 53 bytes/cell transferred from the SALI-25C to the CUBIT, and 55 bytes/cell transferred from the CUBIT to the SALI-25C, over the UTOPIA interface. The two extra bytes sent from the CUBIT are tag bytes. The six LSBs of the MS (first) tag byte carry an index, which is used by the SALI-25C to fetch the multiport indicator. The priority queue code is carried in the two LSBs of the LS (second) tag byte. The SALI-25C examines the tag bytes to determine which ports and queue codes are used. The tag bytes are discarded after processing.

Table 1: SALI-25C Memory Configuration for Interfacing with CUBIT and ALI-25T

|    | <u> </u>                                                                                                           |

|----|--------------------------------------------------------------------------------------------------------------------|

| F4 | not Software Reset                                                                                                 |

| F8 | set-up ALI-25T to start frequency acquisition                                                                      |

|    | wait 50 ms                                                                                                         |

| F0 | use SRAM, single-PHY UTOPIA, multicast, priority queues                                                            |

| 80 | set to use positive edge for event trigger                                                                         |

| 8F | set to output 8K timing mark with internal clock and XCODE is FH.                                                  |

| 00 | use 1 SRAM & set RINBAND = TINBAND = 0                                                                             |

| 00 | test pattern set to all 0                                                                                          |

| 1E | LINKRES = 30                                                                                                       |

| 12 | minimum cell buffer size for the lowest priority (11) is 8, for priority 10 is 12                                  |

| 34 | minimum cell buffer size for priority 01 is 16, for priority 00 (highest) is 20                                    |

| 00 | set to 0                                                                                                           |

| 00 | no action needed, reset to 0s                                                                                      |

| 00 | set all TXONn pins to low, keep ALI-25Ts power up                                                                  |

| 3F | set all LBn pins to high, disable loopback of ALI-25Ts                                                             |

| 00 | default state, LED's turn green on RX and TX cells on the port line                                                |

| 00 | counter value of 000000                                                                                            |

| 01 | write to counter 1 (Discarded Cell Counter Channel #6)                                                             |

| 02 | write to counter 2 (Discarded Cell Counter Channel #5)                                                             |

|    | continue incrementing data field for address 5C until 12(hex)                                                      |

| 12 | write to counter 18 (Transmit Cell Counter Channel #1)                                                             |

| •  | uld be used when accessing the Multicast Indicator RAM. Write data and a) once after SALI-25C is first powered up. |

| 00 | Write data 00 hex to Multi-Port Data Register                                                                      |

| 00 | Write Index Address to Multi-Port Index Register                                                                   |

| 00 | Initiates a Write of Data in register 5B to Multi-Port Address pointed by register 5A                              |

|    |                                                                                                                    |

|    | F8   F0  80  8F  00  00  1E  12  34  00  00  00  3F  00  00  01  02  12  sequences show (incorrect data)           |

| Address (Hex)   | Set-up (Hex)                     | Description                                                                                                                                                                                       |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5A              | 00                               | Write Index Address to Multi-Port Index Register                                                                                                                                                  |

| 59              | 80                               | Initiate a Read from this address                                                                                                                                                                 |

| 5B              |                                  | Read the data from the read cycle performed above (incorrect data)                                                                                                                                |

| This sequence   | writes 05 hex t<br>should be use | a verification reads to and from the Multi-Port RAM are as follows: to address 00 hex and verifies it by reading it twice. d as a guide to access all locations in Multi-Port RAM after the above |

| 5B              | 05                               | Write Data 05 hex to Multi-Port Data Register                                                                                                                                                     |

| 5A              | 00                               | Write Index Address to Multi-Port Index Register                                                                                                                                                  |

| 59              | 00                               | Initiates a Write of data in register 5B to Multi-Port Address pointed by register 5A                                                                                                             |

| 5A              | 00                               | Write Index Address to Multi-Port Index Register                                                                                                                                                  |

| 59              | 80                               | Initiate a Read from this address                                                                                                                                                                 |

| 5B              |                                  | Read the data from the read cycle performed above (incorrect data)                                                                                                                                |

| 5A              | 00                               | Write Index Address to Multi-Port Index Register                                                                                                                                                  |

| 59              | 80                               | Initiate a Read from this address                                                                                                                                                                 |

| 5B              |                                  | Read the data again from the read cycle performed above (correct data)                                                                                                                            |

| End of Multi-Po | ort RAM seque                    | nce.                                                                                                                                                                                              |

| 04 <sup>2</sup> | C6                               | turn on channel 6 with ID = 6                                                                                                                                                                     |

| 05 <sup>2</sup> | C5                               | turn on channel 5 with ID = 5                                                                                                                                                                     |

| 06 <sup>2</sup> | C4                               | turn on channel 4 with ID = 4                                                                                                                                                                     |

| 07 <sup>2</sup> | C3                               | turn on channel 3 with ID = 3                                                                                                                                                                     |

| 08 <sup>2</sup> | C2                               | turn on channel 2 with ID = 2                                                                                                                                                                     |

| 09 <sup>2</sup> | C1                               | turn on channel 1 with ID = 1                                                                                                                                                                     |

| 00 <sup>2</sup> | 91                               | Software Reset                                                                                                                                                                                    |

| 00 <sup>2</sup> | F4                               | not Software Reset                                                                                                                                                                                |

### Notes:

<sup>1.</sup> The multicast indicator location content can only be verified by reading the location twice, immediately after writing to the location, and disregarding the incorrect result of the first read operation.

<sup>2.</sup> These registers should be programmed last.

## **PIN DIAGRAM**

Note: Active low (inverted) or active-on-falling-edge signals are indicated by '-' at end of symbol (e.g., SOE- is equivalent to  $\overline{\text{SOE}}$ ).

Figure 13. SALI-25C TXC-07625 Pin Diagram

## **PIN DESCRIPTIONS**

The SALI-25C is packaged as a 208-pin plastic quad flat package device, as shown in Figures 13 and 29. The No Connect pins are reserved for possible use to provide new features in future versions of the device. They are not to be connected, in order to assure backwards-compatibility of the new version in existing application designs. Every output pin is tri-stateable. The variable n identifies one of the six channels in the device, and represents values from 1 to 6.

## **POWER SUPPLY AND GROUND**

| Symbol | Pin No.                                                                                        | I/O/P* | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                        |

|--------|------------------------------------------------------------------------------------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | 6, 25, 44,<br>57, 82, 98,<br>112, 123, 143,<br>155, 164, 184,<br>192, 202                      | Р      |      | V <sub>DD</sub> : +3.3 volt supply, ±5%.                                                                                                                                                                                                                                                                                                                                             |

| GND    | 14, 15, 33,<br>34, 50, 72,<br>73, 87, 89,<br>103, 120, 121,<br>133, 147, 169,<br>187, 197, 208 | Р      |      | Ground: 0 volt reference.                                                                                                                                                                                                                                                                                                                                                            |

| NC     | 52, 53, 55,<br>56, 60, 61,<br>71, 104, 124,<br>141, 142, 154,<br>159, 174, 179,<br>186         |        |      | No Connect: NC pins are not to be connected, not even to another NC pin, but must be left floating. Connection of NC pins may impair performance or cause damage to the device. Some NC pins may be assigned functions in future upgrades of the device. Backwards compatibility of the upgraded device in existing applications may rely upon these pins having been left floating. |

<sup>\*</sup>Note: I = Input; O = Output; P = Power; T= Tri-state capability.

## **LINE INPUT**

| Symbol                       | Pin No.                            | I/O/P | Type*              | Name/Function                                                                                                                                                                                     |

|------------------------------|------------------------------------|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDn<br>(n = 1-6)            | 201, 194,<br>183, 176,<br>168, 161 | I     | TTL                | Receive Line Data Input for Ch. n: Line input bit-<br>serial data at 32 MHz for channels 1 to 6. RXDn is<br>clocked in on the falling/rising edge of RXCKn, as<br>determined by control bit FALL. |

| RXCKn<br>(n = 1-6)           | 200, 193,<br>182, 175,<br>167, 160 | I     | Schmitt<br>Trigger | Receive Line Clock in for Ch. n: Line input clock at 32 MHz.                                                                                                                                      |

| FrAqn/<br>FrAqn<br>(n = 1-6) | 205, 198,<br>190, 180,<br>172, 165 | O(T)  | CMOS<br>2mA        | Frequency Acquisition for Ch. n: Pulses low for at least 72 μs if RXCKn is detected to be out of sync. with TxOSC. Inverted if INVFRAQ=1.                                                         |

<sup>\*</sup> See Input, Output and I/O Parameters section for Type definitions.

## **LINE OUTPUT**

| Symbol                           | Pin No.                            | I/O/P | Туре               | Name/Function                                                                                                                                                               |

|----------------------------------|------------------------------------|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDn<br>(n = 1-6)                | 203, 195,<br>188, 177,<br>170, 162 | O(T)  | CMOS<br>4mA        | Transmit Line Data Out for Ch. n: Line output bit-serial data clocked out on the falling edge of TXCKn.                                                                     |

| $\frac{TXCKn}{TXDn}$ $(n = 1-6)$ | 204, 196,<br>189, 178,<br>171, 163 | O(T)  | CMOS<br>4mA        | Transmit Line Clock Out/Transmit Line Data Inverted Out for Ch. n: Line output clock at 32 MHz derived from TxOSC, or inverted TXDn data output.                            |

| TXONn<br>(n = 1-6)               | 2, 1,<br>207, 156,<br>157, 158     | O(T)  | CMOS<br>2mA        | Transmit Line ON for Ch. n: Active high output used to turn on the transmitter of the external transceiver device.                                                          |

| LBn<br>(n = 1-6)                 | 206, 199,<br>191, 181,<br>173, 166 | O(T)  | CMOS<br>2mA        | <b>Loopback for External Ch. n:</b> Control signal used to set the external transceiver to the loopback mode. The microprocessor can control this pin via control bit FLBn. |

| TxOSC                            | 185                                | ı     | Schmitt<br>Trigger | <b>Transmit Oscillator Input:</b> Local oscillator input at 32 MHz is used for line transmission and is divided internally to provide the 8 kHz marker when EXT8K=0.        |

## **CELL OUTPUT**

| Symbol     | Pin No.                  | I/O/T | Туре                  | Name/Function                                                                                                                                                                                                                                                                                                                                                                  |

|------------|--------------------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxSOC      | 99                       | O(T)  | CMOS<br>4mA<br>(8mA*) | Receive Terminal Start of Cell Output: Active high tri-stateable output, enabled only in cycles following those with RXENB asserted low.                                                                                                                                                                                                                                       |

| RxCLAV     | 102                      | O(T)  | CMOS<br>4mA<br>(8mA*) | Receive Terminal Cell Available Indicator Output: Active high tri-stateable output signal which indicates that a complete cell is available for transfer. RxCLAV is driven only during the clock cycle following the one with matching SALI-25C address, RXADD(4-0). RxCLAV is asserted high to indicate it has a complete cell to transfer, otherwise RxCLAV is asserted low. |

| RTD(7-0)   | 97-90                    | O(T)  | CMOS<br>4mA<br>(8mA*) | Receive Terminal Data Out: Tri-stateable 8-bit cell data output bus, enabled only in cycles following those with RXENB asserted low.                                                                                                                                                                                                                                           |

| RxCLK      | 100                      | I     | Schmitt<br>Trigger    | <b>Receive Input Byte Clock:</b> Data is transferred and sampled on the rising edge of this input clock. The maximum frequency is 33 MHz.                                                                                                                                                                                                                                      |

| RXENB      | 101                      | I     | TTL                   | Receive Terminal Read Enable Input: Active low read enable input signal for cell output. Tri-states RxSOC and RTD(7-0) output pins when set high.                                                                                                                                                                                                                              |

| RXADD(4-0) | 88, 86,<br>85, 84,<br>83 | ı     | TTL                   | Receive Terminal Physical Device Address: Five-bit wide address for the ports programmed in this device on ADDn(4-0).                                                                                                                                                                                                                                                          |

<sup>\*</sup> For UTOPIA Level 2 compliance, these pins are also characterized at 8mA.

## **CELL INPUT**

| Symbol     | Pin No. | I/O/P | Туре                  | Name/Function                                                                                                                                                                                                                                                                                                                              |

|------------|---------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxCLAV     | 70      | O(T)  | CMOS<br>4mA<br>(8mA*) | Transmit Terminal Cell Available Indicator Output: Active high tri-stateable output signal. TxCLAV is driven only during the clock cycle following the one with matching SALI-25C address, TXADD(4-0). TxCLAV is asserted high to indicate that the SALI-25C can accept the transfer of a complete cell, otherwise TxCLAV is asserted low. |

| TTD(7-0)   | 81-74   | l     | TTL                   | Transmit Terminal Data In: Tri-stateable 8-bit cell data input bus, valid when TxENB is asserted low.                                                                                                                                                                                                                                      |

| TxSOC      | 69      | I     | TTL                   | Transmit Terminal Start of Cell Input: Active high input signal that indicates the start of cell input.                                                                                                                                                                                                                                    |

| TxCLK      | 68      | I     | Schmitt<br>Trigger    | <b>Transmit Input Byte Clock:</b> Data is transferred and sampled on the rising edge of this input clock (max. frequency 33 MHz).                                                                                                                                                                                                          |

| TxENB      | 67      | I     | TTL                   | Transmit Terminal Read Enable Input: Active low read enable input signal for cell input.                                                                                                                                                                                                                                                   |