12-Port 10/100Mbps + 1Gbps Ethernet Switch

Data Sheet

#### Features

- 12 10/100 Mbps Autosensing, Fast Ethernet ports with Reduced MII Interface

- Single Gigabit Ethernet port

- Supports both GMII and integrated Physical Coding Sublayer with Ten Bit Interface (TBI) logic to interface directly with Gigabit transceivers

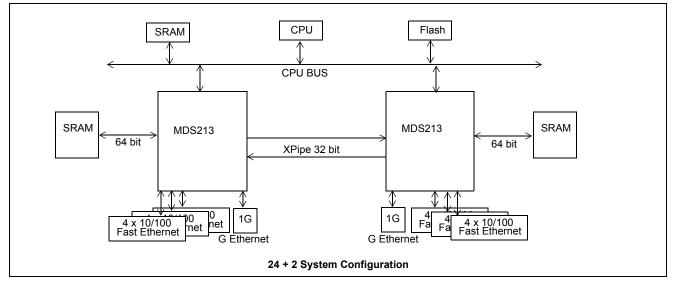

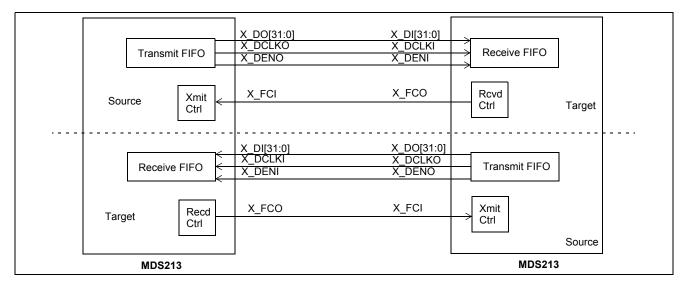

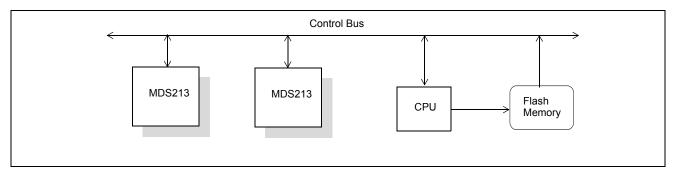

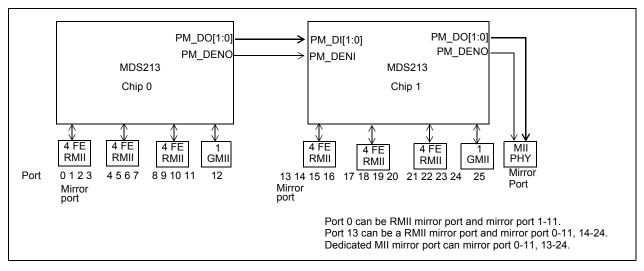

- Two-chip solution for 24+2 configuration

32-bit wide bi-directional pipe at 100 MHz provides 6.4 Gbps pipe to connect two MDS213 chips

- Supports up to 6.548 Mpps system throughput using non-blocking architecture

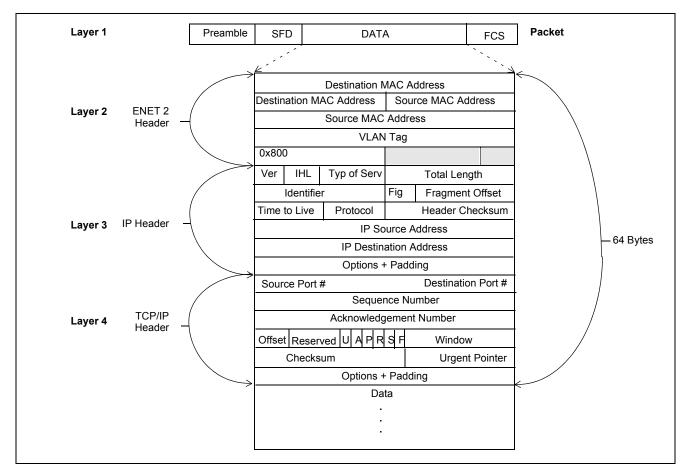

- High performance Layer 2 packet forwarding and filtering at full wire speed.

- Very low latency through single store and forward at ingress port and cut-through switching at destination ports

- Port Trunking and Load Sharing for high bandwidth links between switches

- On-chip address lookup engine and memory for up to 2 K MAC addresses

- Parallel Flash interface for fast self initialization

- Supports packet filtering and port security

System wide filtering

- Static MAC destination and source address filtering

#### April 2006

#### **Ordering Information**

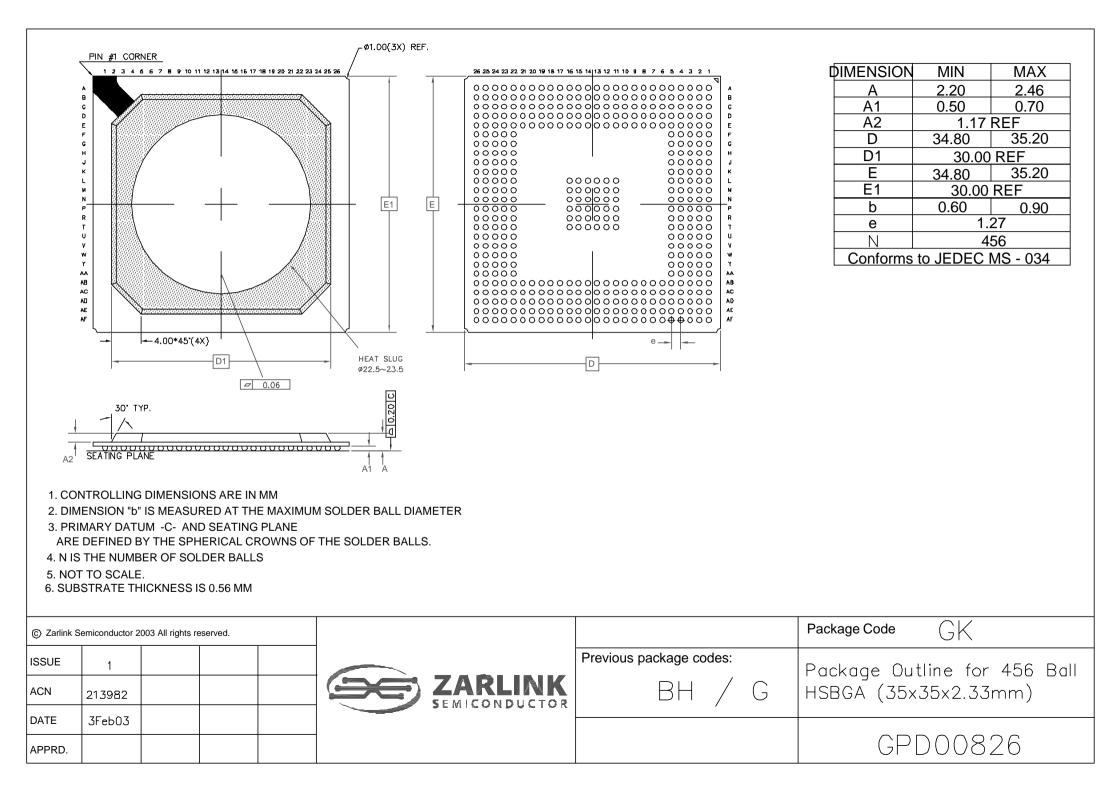

MDS213CG 456 Pin HSBGA Trays MDS213CG2 456 Pin HSBGA\*\* Trays \*\*Pb Free Tin/Silver/Copper 0°C to 70°C

- VLAN for multicast/broadcast filtering

- Protocol filtering

- Local port filtering

- Aging control for secure MAC addresses

- Provides 256-port and ID Tagged Virtual LANs (VLANs) 802.1Q

- ID Tagging Insertion/Extraction

- Supports IP Multicasting through IGMP Snooping

- XpressFlow Quality of Service (QoS), IEEE 802.1p, supports 4 Level transmission priorities, weighted fair queuing based packet scheduling, user mapping of priority levels and weights

- Full duplex Ethernet IEEE 803.2x flow control minimizes traffic congestion

- Supports back-pressure flow control for half duplex mode

- Flooding and Broadcasting control

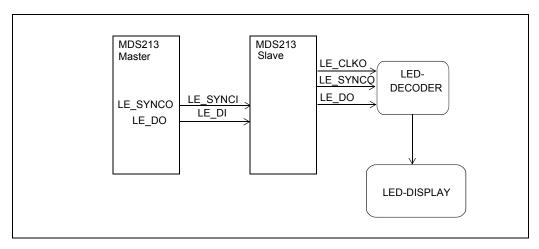

- Link status and TX/RX activity through serial LED interface

Figure 1 - 24 10/100Mbps + 2Gbps Port System Configuration

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003-2006, Zarlink Semiconductor Inc. All Rights Reserved.

- Up to 64 K using management CPU memory

- Up to 16 K using external buffer memory

- Standard software modules available:

- Browser, GUI, and text menu

- IEEE 802.1d Spanning Tree Algorithm

- SNMP management

- Telnet for remote control console

- Automatic Booting via TFTP Protocols.

- Remote Monitoring (RMON) and storage for a management agent

- IGMP for IP multicast

- GVRP, GMRP

- Packaged in 456-Pin Ball Grid Array

#### Description

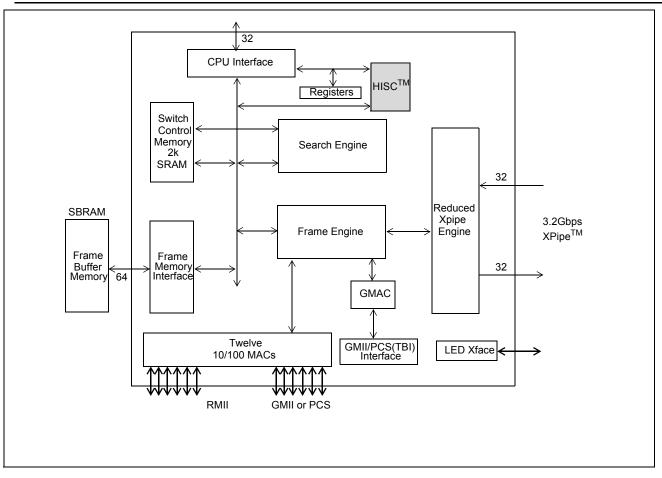

The Zarlink MDS213 is a 12-port 10/100 Mbps + 1 Gbps high-performance, non-blocking Ethernet switch with onchip address memory and address lookup engine. A single chip provides 12 - 10/100 Mbps ports and 1 -1000 Mbps port. The MDS213 can be utilized in both managed and unmanaged switching applications.

The 3.2 Gbps XPipe allows a high-speed connection between two MDS213 chips, providing a optimal, low-cost, workgroup switch with 24 10/100 Fast Ethernet ports and 2 Gigabit Ethernet ports.

In half-duplex mode, all ports support back pressure flow control to minimize the risk of losing data for long activity bursts. In full-duplex mode, IEEE 802.3x frame based flow control is used. With full-duplex capabilities, each Fast Ethernet ports supports 200 Mbps aggregate bandwidth connections, while the Gigabit Ethernet port supports 2 Gbps to desktops, servers, or other high-performance switches. The Physical Coding Sublayer is integrated on-chip with Ten Bit Interface (TBI) and this Physical Coding Sublayer can be bypassed when the GMII interface is used.

The MDS213 supports port trunking/load sharing on the 10/100 Mbps ports. Port trunking/load sharing can be used to group ports between interlinked switches for increased system bandwidth. Ports within a trunk must reside within a single MDS213, such that trunks may not be configured across two switches.

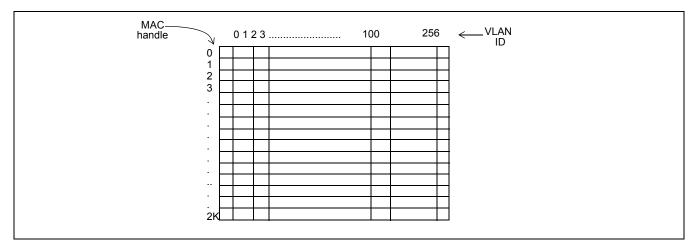

The on-chip address lookup engine supports up to 2 K MAC addresses and up to 256 IEEE 802.1Q Virtual LANs (VLAN). Each port may be programmed to recognize VLANs, and will transmit frames along with their VLAN Tags, for interoperability, to systems that support VLAN Tagging.

Each port independently collects statistical information using SNMP and the Remote Monitoring Management Information Base (RMON - MIB). Access to these statistical counter/registers are provided via the CPU interface. SNMP Management frames may be received and/or transmitted via the CPU interface and thus creates a complete network management solution.

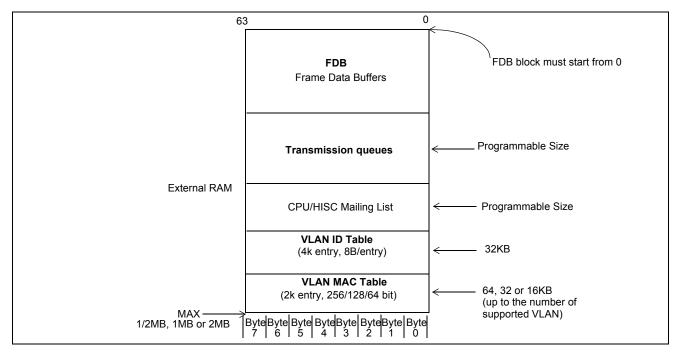

The MDS213 utilizes cost effective, high performance, pipelined SBRAM to achieve full wire speed on all ports simultaneously. Data is buffered into memory, using 0-128 byte bursts, from the ingress ports, and transferred to an internal transmit FIFO, before being sent from the frame memory to the egress output ports. Extremely high memory bandwidth is therefore achieved, which allows each of the ports to be active without creating a memory bottleneck.

The MDS213 is fabricated with 2.5 V technology, where the inputs are 3.3 V tolerant and the outputs are capable of directly interfacing to Low-Voltage TTL levels. The Zarlink MDS213 is packaged in a 456-pin Ball Grid Array.

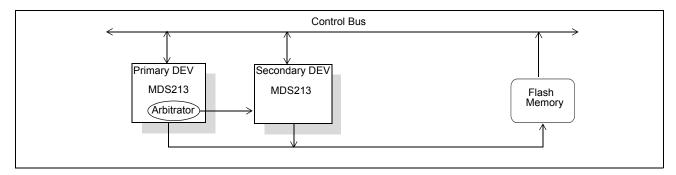

Figure 2 - System Block Diagram

#### Note:

All registers are 32-bit width.

The Control Bus is 32-bits wide and the Memory Bus is 64-bits wide.

The MDS213 contains 12 Fast Ethernet Ports.

The LED interface has 3 output signals (1 data and 2 control).

The XPipe is 32-bits wide.

| 1.0 Ball Signal Descriptions and Assignments            | 11 |

|---------------------------------------------------------|----|

| 1.1 Ball Signal Assignments                             | 12 |

| 2.0 Ball-Signal Descriptions                            | 17 |

| 3.0 The Media Access Control (MAC) and GIGABIT (GMAC)   | 24 |

| 3.1 MAC/GMAC Configuration                              |    |

| 3.2 The Inter-frame Gap                                 |    |

| 3.3 Ethernet Frame Limits                               |    |

| 3.4 Collision Handling and Avoidance                    | 24 |

| 3.5 Auto-negotiation                                    |    |

| 3.6 VLAN Support                                        |    |

| 3.7 MAC Control Frames.                                 |    |

| 3.8 Flow Control                                        |    |

| 3.8.1 Collision-Based Flow Control.                     |    |

| 3.8.2 IEEE 802.3x Flow Control                          |    |

| 3.9 Frame Bursting                                      |    |

| 4.0 Frame Engine Description                            |    |

| 4.1 Transmission scheduling                             |    |

| 4.2 Buffer Management.                                  |    |

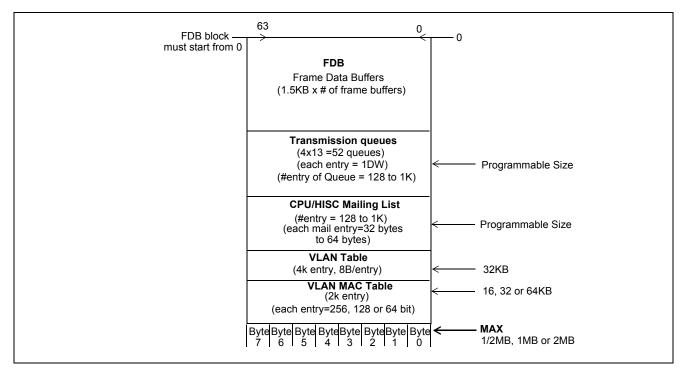

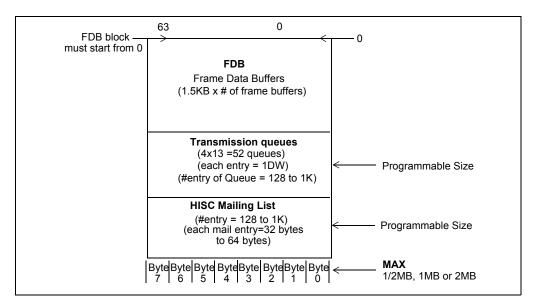

| 5.0 Frame Buffer Memory                                 |    |

| 5.1 Frame Buffer Memory Configuration                   |    |

| 5.2 Frame Buffer memory usage.                          |    |

| 5.2.1 Memory Allocation of a Managed System             |    |

| 5.2.2 Frame Data Buffers                                |    |

| 5.2.3 Transmission Queues                               |    |

| 5.2.4 Mailing List                                      |    |

| 5.2.6 VLAN MAC Association Table                        |    |

| 5.2.7 Unmanaged System Memory Allocation                |    |

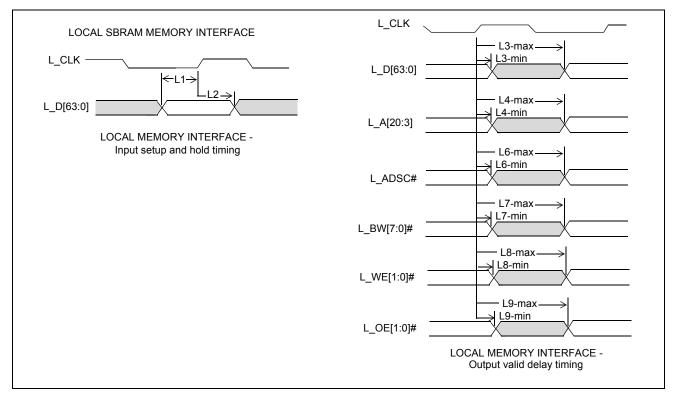

| 5.3 The Frame Memory Interface                          |    |

| 5.3.1 Local Memory Interface                            |    |

| 6.0 Search Engine                                       |    |

| 6.1 Layer 2 Search Process                              |    |

| 6.1.1 VLAN Unaware                                      |    |

| 6.1.2 VLAN Aware                                        |    |

| 6.2 Address and VLAN Learning.                          |    |

| 6.3 Flooding and Packet Control.                        |    |

| 6.4 Packet Filtering                                    | 35 |

| 6.5 Address Aging                                       | 35 |

| 6.6 IP Multicast                                        | 35 |

| 7.0 The High Density Instruction Set Computer (HISC)    | 36 |

| 7.1 Description.                                        |    |

| 7.2 HISC architecture                                   | 36 |

| 7.3 HISC Operations                                     |    |

| 7.3.1 Resource Initialization                           |    |

| 7.3.2 Resource Management                               |    |

| 7.3.3 Switching Database Management                     |    |

| 7.3.4 Send and Receive Frames for Management CPU.       |    |

| 7.3.5 Communication Between HISC and Switching Hardware |    |

| 7.3.6 Communication Between Search Engine and HISC      |    |

| 7.3.7 Communication Between HISC and Frame Engine.      |    |

| 7.4 Communication Between Management CPU and HISC       | 31 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4.1 CPU-HISC Communication Using Queues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                              |

| 7.4.2 Mailbox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                              |

| 7.4.3 CPU-HISC MAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |

| 7.4.4 HISC-CPU Mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |

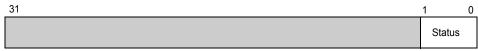

| 8.0 The XPipe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                                                                                                                                                                                                                           |

| 8.1 XPipe Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                                                                                                                                                                           |

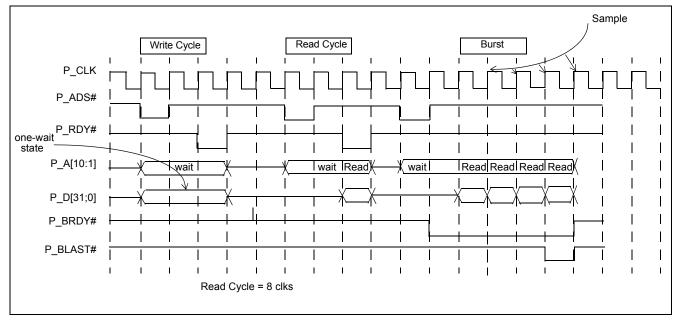

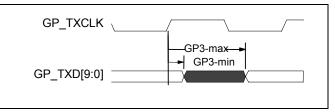

| 8.2 XPipe Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                                                                                                                                                                                                                                           |

| 9.0 Physical Layer (PHY) Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                                                                                           |

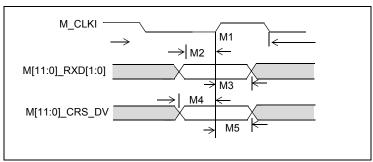

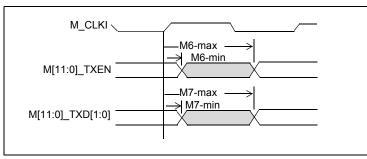

| 9.1 Reduced MII (RMII).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                              |

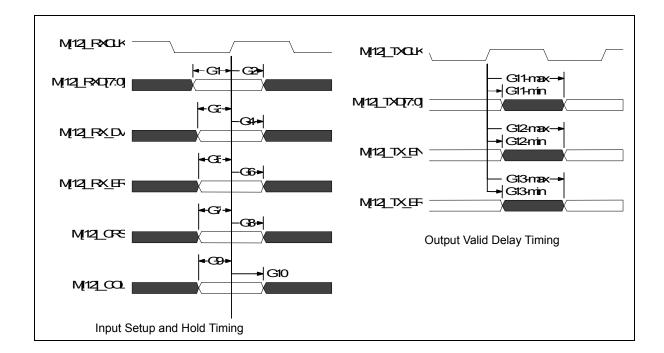

| 9.2 The Gigabit Media Independent Interface (GMII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                              |

| 9.2.1 The MII Management Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                              |

| 9.2.2 MII Command and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                              |

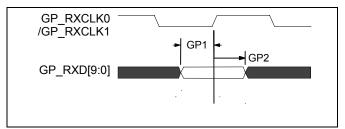

| 9.3 The Physical Coding Sublayer with Ten Bit Interface (TBI):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                              |

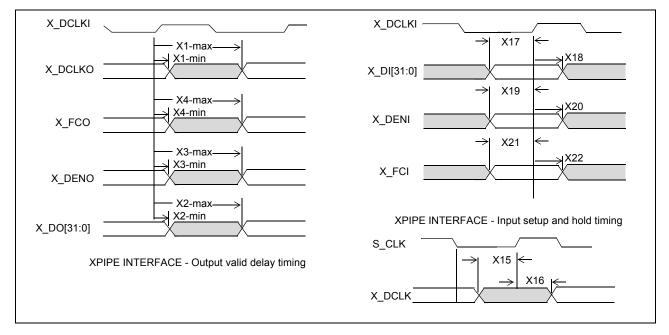

| 10.0 The Control Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |

| 10.1 External CPU Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                              |

| 10.1.1 Power On/Reset Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |

| 10.1.2 CPU Bus Clock Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                              |

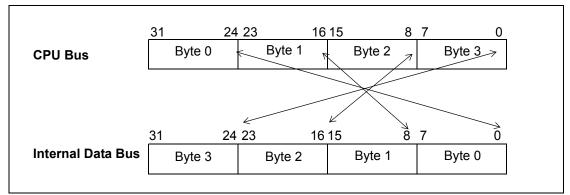

| 10.1.3 Address And Data Buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                              |

| 10.1.4 Bus Master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                              |

| 10.1.5 Input/Output Mapped Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                              |

| 10.1.6 Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |

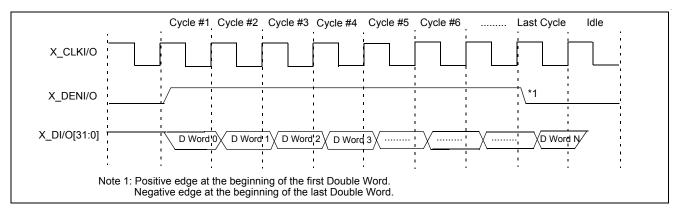

| 10.2 Control Bus Cycle Waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                              |

| 10.3 The CPU Interface in Unmanaged Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                              |

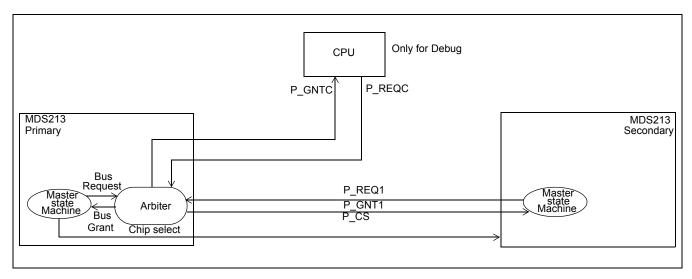

| 10.3.1 Arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                              |

| 10.4 CPU Interface in Managed Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                              |

| 10.4.1 CPU Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                              |

| 10.4.1 CPU Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46                                                                                                                                                                                                                                           |

| 10.4.1 CPU Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b> 46</b><br>46                                                                                                                                                                                                                             |

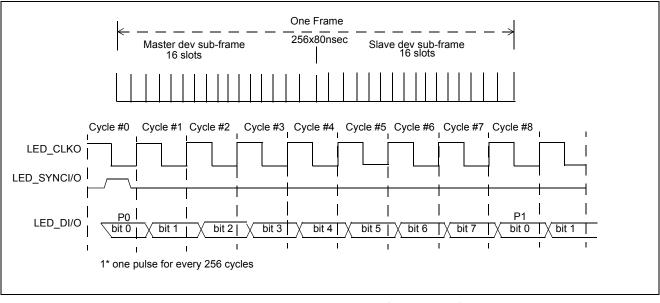

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b> 46</b><br>46<br>47                                                                                                                                                                                                                       |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b> 46</b><br>46<br>47<br>47                                                                                                                                                                                                                 |

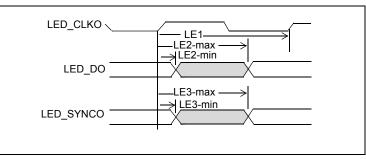

| 10.4.1 CPU Access.<br><b>11.0 The LED Interface</b><br>11.1 LED interface.<br>11.1.1 Function Description<br>11.1.2 Port Status<br>11.1.3 LED Interface Time Diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b> 46</b><br>46<br>47<br>47<br>47                                                                                                                                                                                                           |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46<br>46<br>47<br>47<br>47<br>47<br>48                                                                                                                                                                                                       |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46<br>46<br>47<br>47<br>47<br>47<br>48                                                                                                                                                                                                       |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1 Function Description         11.2 Port Status         11.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46<br>46<br>47<br>47<br>47<br>47<br>48<br>48<br>48                                                                                                                                                                                           |

| 10.4.1 CPU Access.<br>11.0 The LED Interface<br>11.1 LED interface.<br>11.1.1 Function Description<br>11.1.2 Port Status<br>11.1.3 LED Interface Time Diagram.<br>12.0 Data Forwarding Protocol and Data Flow<br>12.1 Data Forwarding Protocol<br>12.1.1 Frame Reception<br>12.1.2 Unicast Frame Forwarding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46<br>46<br>47<br>47<br>47<br>47<br>48<br>48<br>48<br>48                                                                                                                                                                                     |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49                                                                                                                                         |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49                                                                                                                         |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49                                                                                                         |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49                                                                                                         |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device         12.2.3 Multicast Data Frame.                                                                                                                                                                                                                                                                                                                                                                                                                           | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48                                                                                                                                 |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device         12.2.3 Multicast Data Frame.         12.3 Flow for CPU Control Frame.                                                                                                                                                                                                                                                                                                                                                                                  | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48                                                                                                                                 |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.2 Port Status.         11.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device         12.2.3 Multicast Data Frame.         12.3 Flow for CPU Control Frame.         12.3 Flow for CPU Control Frame.         12.3 CPU Transmitting Unicast CPU Frame                                                                                                                                                                                                                                                                                            | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50                                                                                 |

| 10.4.1 CPU Access. <b>11.0 The LED Interface</b> 11.1 LED interface.         11.1.1 Function Description         11.2 Port Status         11.3 LED Interface Time Diagram <b>12.0 Data Forwarding Protocol and Data Flow</b> 12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device         12.2.3 Multicast Data Frame.         12.3 Flow for CPU Control Frame.         12.3 Flow for CPU Control Frame         12.3.1 CPU Transmitting Unicast CPU Frame         12.3.2 CPU Transmitting Multicast CPU Frame                                                                                                                                                                                                                                        | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50                                                                 |

| 10.4.1 CPU Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50                                                         |

| 10.4.1 CPU Access.         11.0 The LED Interface         11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram         12.0 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.2 Unicast Data Frame to Local Device         12.2.3 Multicast Data Frame.         12.3.1 CPU Transmitting Unicast CPU Frame         12.3.2 CPU Transmitting Multicast Frame         12.3.3 CPU Receiving Multicast Frame         12.3.4 CPU Receiving Multicast Frame                                                                                                                                                                                                                                                                | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50<br>. 51                                                         |

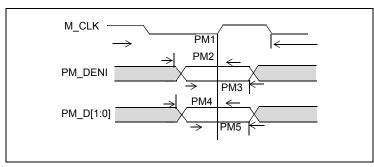

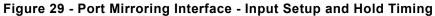

| 10.4.1 CPU Access         11.0 The LED Interface         11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram         12.0 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol and Data Flow         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding         12.1.3 Multicast Frame Forwarding         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device         12.3 Multicast Data Frame         12.3 Multicast Data Frame         12.3 Flow for CPU Control Frame         12.3.1 CPU Transmitting Unicast CPU Frame         12.3.2 CPU Transmitting Multicast CPU Frame         12.3.3 CPU Receiving Multicast Frame         12.3.4 CPU Receiving Multicast frame         12.3.5 CPU Receiving Multicast frame         12.3.4 CPU Receiving Multicast frame         13.0 Port Mirroring | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50<br>. 51<br>. 51                                                         |

| <ul> <li>10.4.1 CPU Access.</li> <li>11.0 The LED Interface .</li> <li>11.1 LED interface .</li> <li>11.1.1 Function Description .</li> <li>11.2 Port Status .</li> <li>11.3 LED Interface Time Diagram .</li> <li>12.0 Data Forwarding Protocol and Data Flow .</li> <li>12.1 Data Forwarding Protocol .</li> <li>12.1.1 Frame Reception .</li> <li>12.1.2 Unicast Frame Forwarding.</li> <li>12.3 Multicast Frame Forwarding.</li> <li>12.2 Flow for Data Frame to Local Device .</li> <li>12.2.1 Unicast Data Frame to Remote Device .</li> <li>12.2.2 Unicast Data Frame to Remote Device .</li> <li>12.3 Multicast Data Frame .</li> <li>12.3 Flow for CPU Control Frame .</li> <li>12.3 Flow for CPU Transmitting Unicast CPU Frame .</li> <li>12.3.1 CPU Transmitting Multicast CPU Frame .</li> <li>12.3.4 CPU Receiving Multicast frame .</li> <li>13.0 Port Mirroring .</li> <li>13.1 Features .</li> </ul>                                                                  | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50<br>. 51<br>. 51                                         |

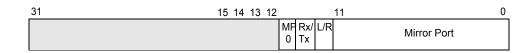

| 10.4.1 CPU Access.         11.0 The LED Interface         11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram         12.0 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2.4 Flow for Data Frame         12.2.2 Unicast Data Frame to Local Device         12.2.3 Multicast Data Frame.         12.3 Flow for CPU Control Frame.         12.3.1 CPU Transmitting Unicast CPU Frame         12.3.2 CPU Transmitting Multicast CPU Frame         12.3.3 CPU Receiving Multicast Frame         12.3.4 CPU Receiving Multicast frame         13.0 Port Mirroring.         13.1 Features         13.2 Physical Pins.                                                                              | 46<br>47<br>47<br>47<br>47<br>48<br>48<br>48<br>48<br>48<br>48<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>49<br>50<br>50<br>50<br>51<br>51<br>52                                                             |

| 10.4.1 CPU Access.         11.0 The LED Interface         11.1 LED interface         11.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram         12.0 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2 Flow for Data Frame         12.2.1 Unicast Data Frame to Local Device         12.2.2 Unicast Data Frame to Remote Device         12.3 Multicast Data Frame.         12.3 Flow for CPU Control Frame         12.3 CPU Transmitting Unicast CPU Frame         12.3.1 CPU Transmitting Multicast CPU Frame         12.3.2 CPU Transmitting Multicast CPU Frame         12.3.4 CPU Receiving Multicast frame         13.0 Port Mirroring         13.1 Features         13.2 Physical Pins.         13.2.1 Setting Register For Port Mirroring                                | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50<br>. 51<br>. 51<br>. 52<br>. 52<br>. 52 |

| 10.4.1 CPU Access.         11.0 The LED Interface         11.1 LED interface.         11.1.1 Function Description         11.1.2 Port Status         11.1.3 LED Interface Time Diagram         12.0 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol and Data Flow         12.1 Data Forwarding Protocol         12.1.1 Frame Reception         12.1.2 Unicast Frame Forwarding.         12.1.3 Multicast Frame Forwarding.         12.2.4 Flow for Data Frame         12.2.2 Unicast Data Frame to Local Device         12.2.3 Multicast Data Frame.         12.3 Flow for CPU Control Frame.         12.3.1 CPU Transmitting Unicast CPU Frame         12.3.2 CPU Transmitting Multicast CPU Frame         12.3.3 CPU Receiving Multicast Frame         12.3.4 CPU Receiving Multicast frame         13.0 Port Mirroring.         13.1 Features         13.2 Physical Pins.                                                                              | . 46<br>. 47<br>. 47<br>. 47<br>. 47<br>. 47<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 49<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 52<br>. 52                 |

| 14.1 Introduction                                             |    |

|---------------------------------------------------------------|----|

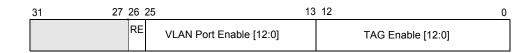

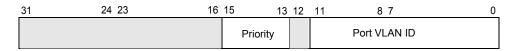

| 14.2 VLAN Implementation                                      |    |

| 14.2.1 Static Definitions of VLAN Membership                  |    |

| 14.2.2 Dynamic Learning of VLAN Membership.                   |    |

| 14.2.3 Dynamic Learning of Remote VLAN                        |    |

| 14.2.4 MDS213 Data Structures For VLAN Implementation.        |    |

| 14.2.4.1 VLAN ID Table                                        |    |

| 14.2.4.2 VLAN MAC Table                                       |    |

| 14.2.4.3 VLAN Port Mapping Table (VMAP)                       |    |

| 14.2.4.4 Port VLAN ID (PVID) Register                         |    |

| 15.0 IP Multicast                                             |    |

| 15.1 Introduction                                             |    |

| 15.2 IGMP and IP Multicast Filtering.                         |    |

| 15.3 Implementation in MDS213                                 |    |

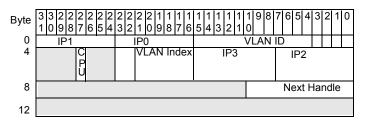

| 15.3.1 MCT Table                                              |    |

| 15.3.1.1 MCT Structure For Unicast Frame                      |    |

| 15.3.2 MCT structure for IP Multicast Packet                  |    |

| 16.0 Quality of Service (QOS)                                 |    |

| 16.1 Weighted Round Robin Transmission Strategy               |    |

| 16.2 Buffer Management Functions                              | 60 |

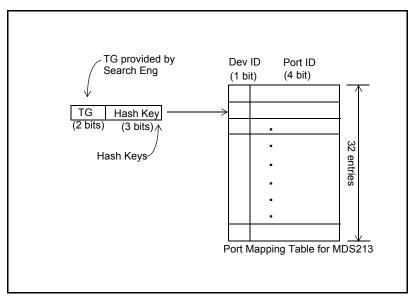

| 17.0 Port Trunking                                            | 61 |

| 17.1 Unicast Packet Forwarding.                               | 61 |

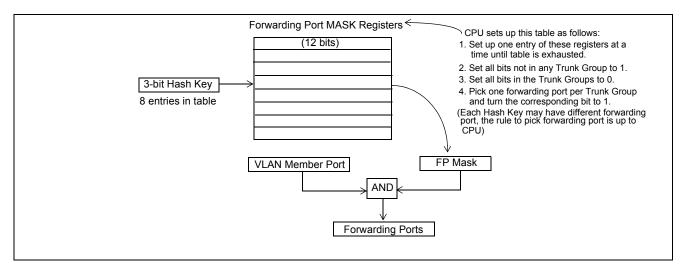

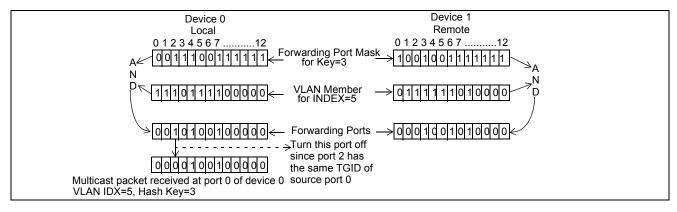

| 17.2 Multicast Packet Forwarding                              |    |

| 17.2.1 Select One Forwarding Port per Trunk Group             | 62 |

| 17.2.2 Blocking Multicast Packets Back to the Source Trunk    |    |

| 17.3 MAC Address Assignment.                                  |    |

| 18.0 Register Definitions                                     | 64 |

| 18.1 Register MAP                                             |    |

| 18.2 Register definitions                                     |    |

| 18.2.1 Device Configuration Register                          |    |

| 18.2.1.1 GCR - Global Control Register                        |    |

| 18.2.1.2 DCR0 - Device Status Register                        |    |

| 18.2.1.3 DCR1 - Signature, Revision & ID Register             |    |

| 18.2.1.4 DCR2 - Device Configuration Register                 |    |

| 18.2.1.5 DCR3 - Interfaces Status Register                    | 72 |

| 18.2.1.6 MEMP - Memory Packed Register                        | 72 |

| 18.2.2 Interrupt Control Registers                            |    |

| 18.2.3 Buffer Memory interface register                       | 74 |

| 18.2.3.1 MWARS - Memory Write Address Register - Single Cycle | 74 |

| 18.2.3.2 MRARS - Memory Read Address Register - Single Cycle  |    |

| 18.2.3.3 Address Registers For Burst Cycle                    | 75 |

| 18.2.3.4 Memory Read/Write Data Registers                     |    |

| 18.2.3.5 VTBP - VLAN ID Table Base Pointer                    |    |

| 18.2.3.6 MBCR - Multicast Buffer Control Register             | 77 |

| 18.2.3.7 AMA - RAM Counter Block Access Register              |    |

| 18.2.3.8 Reserve Register 1                                   |    |

| 18.2.3.9 Reserve Register 2                                   |    |

| 18.2.4 Frame Control Buffers Management Register              |    |

| 18.2.4.1 FCBSL - FCB Queue                                    | 78 |

| 18.2.4.2 FCBST - FCB QUEUE - Buffer Low Threshold             |    |

| 18.2.4.3 BCT - (FCB) Buffer Counter Threshold                 |    |

| 18.2.4.4 BCHL - Buffer Counter Hi-low Selection               | 79 |

|                                                               |    |

| 18.2.5 Queue Management Register                                     | . 79 |

|----------------------------------------------------------------------|------|

| 18.2.5.1 CINQ - CPU Input Queue                                      | . 79 |

| 18.2.5.2 COTQ - CPU Output Queue                                     |      |