## NRND – Not Recommend for New Designs

The MPC9446 is a 2.5 V and 3.3 V compatible 1:10 clock distribution buffer designed for low-voltage mid-range to high-performance telecom, networking and computing applications. Both 3.3 V, 2.5 V and dual supply voltages are supported for mixed-voltage applications. The MPC9446 offers 10 low-skew outputs and 2 selectable inputs for clock redundancy. The outputs are configurable and support 1:1 and 1:2 output to input frequency ratios. The MPC9446 is specified for the extended temperature range of -40°C to 85°C.

#### Features

IDT

- Configurable 10 outputs LVCMOS clock distribution buffer

- Compatible to single, dual and mixed 3.3 V/2.5 V voltage supply

- · Wide range output clock frequency up to 250 MHz

- Designed for mid-range to high-performance telecom, networking and computer applications

- Supports applications requiring clock redundancy

- Maximum output skew of 200 ps (150 ps within one bank)

- Selectable output configurations per output bank

- Tristable outputs

- 32-lead LQFP package, Pb-free

- Ambient operating temperature range of –40 to 85°C

#### **Functional Description**

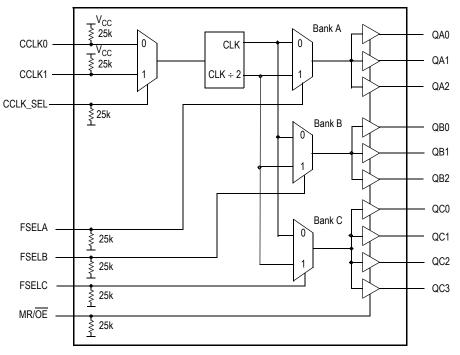

The MPC9446 is a full static fanout buffer design supporting clock frequencies up to 250 MHz. The signals are generated and retimed on-chip to ensure minimal skew between the three output banks. Two independent LVCMOS compatible clock inputs are available. This feature supports redundant clock sources or the addition of a test clock into the system design. Each of the three output banks can be

individually supplied by 2.5 V or 3.3 V supporting mixed voltage applications. The FSELx pins choose between division of the input reference frequency by one or two. The frequency divider can be set individually for each of the three output banks. The MPC9446 can be rese,t and the outputs are disabled by deasserting the MR/OE pin (logic high state). Asserting MR/OE will enable the outputs.

All inputs accept LVCMOS signals while the outputs provide LVCMOS compatible levels with the capability to drive terminated 50  $\Omega$  transmission lines. Please consult the MPC9456 specification for a 1:10 mixed voltage buffer with LVPECL compatible inputs. For series terminated transmission lines, each of the MPC9446 outputs can drive one or two traces giving the devices an effective fanout of 1:20. The device is packaged in a 7x7 mm<sup>2</sup> 32-lead LQFP package.

MPC9446 NRND DATASHEET

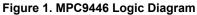

Figure 2. Pinout: 32-Lead Package Pinout (Top View)

| Pin                               | I/O    | Туре   | Function                                           |

|-----------------------------------|--------|--------|----------------------------------------------------|

| CCLK0,1                           | Input  | LVCMOS | LVCMOS clock inputs                                |

| FSELA, FSELB, FSELC               | Input  | LVCMOS | Output bank divide select input                    |

| MR/OE                             | Input  | LVCMOS | Internal reset and output (high impedance) control |

| GND                               |        | Supply | Negative voltage supply (GND)                      |

| $V_{CCA}, V_{CCB}^{(1)}, V_{CCC}$ |        | Supply | Positive voltage supply for output banks           |

| V <sub>CC</sub>                   |        | Supply | Positive voltage supply for core (VCC)             |

| QA0 – QA2                         | Output | LVCMOS | Bank A outputs                                     |

| QB0 – QB2                         | Output | LVCMOS | Bank B outputs                                     |

| QC0 – QC3                         | Output | LVCMOS | Bank C outputs                                     |

## Table 1. Pin Configuration

1.  $V_{CCB}$  is internally connected to  $V_{CC}$ .

#### Table 2. Supported Single and Dual Supply Configurations

| Supply Voltage Configuration | V <sub>CC</sub> <sup>(1)</sup> | V <sub>CCA</sub> <sup>(2)</sup> | V <sub>CCB</sub> <sup>(3)</sup> | V <sub>CCC</sub> <sup>(4)</sup> | GND |

|------------------------------|--------------------------------|---------------------------------|---------------------------------|---------------------------------|-----|

| 3.3 V                        | 3.3 V                          | 3.3 V                           | 3.3 V                           | 3.3 V                           | 0 V |

| Mixed Voltage Supply         | 3.3 V                          | 3.3 V or 2.5 V                  | 3.3 V                           | 3.3 V or 2.5 V                  | 0 V |

| 2.5 V                        | 2.5 V                          | 2.5 V                           | 2.5 V                           | 2.5 V                           | 0 V |

1. V<sub>CC</sub> is the positive power supply of the device core and input circuitry. V<sub>CC</sub> voltage defines the input threshold and levels.

2.  $V_{CCA}$  is the positive power supply of the bank A outputs.  $V_{CCA}$  voltage defines bank A output levels.

3.  $V_{CCB}$  is the positive power supply of the bank B outputs.  $V_{CCB}$  voltage defines bank B output levels.  $V_{CCB}$  is internally connected to  $V_{CC}$ . 4.  $V_{CCC}$  is the positive power supply of the bank C outputs.  $V_{CCC}$  voltage defines bank C output levels.

#### Table 3. Function Table (Controls)

| Control  | Default | 0                                     | 1                                          |

|----------|---------|---------------------------------------|--------------------------------------------|

| CCLK_SEL | 0       | CCLK0                                 | CCLK1                                      |

| FSELA    | 0       | f <sub>QA0:2</sub> = f <sub>REF</sub> | $f_{QA0:2} = f_{REF} \div 2$               |

| FSELB    | 0       | $f_{QB0:2} = f_{REF}$                 | $f_{QB0:2} = f_{REF} \div 2$               |

| FSELC    | 0       | $f_{QC0:3} = f_{REF}$                 | $f_{QC0:3} = f_{REF} \div 2$               |

| MR/OE    | 0       | Outputs enabled                       | Internal reset outputs disabled (tristate) |

## Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Characteristics     | Min  | Мах                  | Unit | Condition |

|------------------|---------------------|------|----------------------|------|-----------|

| V <sub>CC</sub>  | Supply Voltage      | -0.3 | 3.6                  | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>CC</sub> +0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |      | ±20                  | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |      | ±50                  | mA   |           |

| Τ <sub>S</sub>   | Storage Temperature | -65  | 125                  | °C   |           |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute-maximum-rated conditions is not implied.

#### **Table 5. General Specifications**

| Symbol          | Characteristics                   | Min  | Тур             | Max | Unit | Condition  |

|-----------------|-----------------------------------|------|-----------------|-----|------|------------|

| V <sub>TT</sub> | Output Termination Voltage        |      | $V_{CC} \div 2$ |     | V    |            |

| MM              | ESD Protection (Machine Model)    | 200  |                 |     | V    |            |

| HBM             | ESD Protection (Human Body Model) | 2000 |                 |     | V    |            |

| LU              | Latch-Up Immunity                 | 200  |                 |     | mA   |            |

| C <sub>PD</sub> | Power Dissipation Capacitance     |      | 10              |     | pF   | Per output |

| C <sub>IN</sub> | Input Capacitance                 |      | 4.0             |     | pF   |            |

Table 6. DC Characteristics ( $V_{CC} = V_{CCA} = V_{CCB} = V_{CCC} = 3.3 \text{ V} \pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to +85°C)

| Symbol                          | Characteristics                  | Min  | Тур     | Max                   | Unit   | Condition                                                  |

|---------------------------------|----------------------------------|------|---------|-----------------------|--------|------------------------------------------------------------|

| V <sub>IH</sub>                 | Input High Voltage               | 2.0  |         | V <sub>CC</sub> + 0.3 | V      | LVCMOS                                                     |

| V <sub>IL</sub>                 | Input Low Voltage                | -0.3 |         | 0.8                   | V      | LVCMOS                                                     |

| I <sub>IN</sub>                 | Input Current <sup>(1)</sup>     |      |         | 200                   | μA     | $V_{IN}$ = GND or $V_{IN}$ = VCC                           |

| V <sub>OH</sub>                 | Output High Voltage              | 2.4  |         |                       | V      | I <sub>OH</sub> = -24 mA <sup>(2)</sup>                    |

| V <sub>OL</sub>                 | Output Low Voltage               |      |         | 0.55<br>0.30          | V<br>V | $I_{OL} = 24 \text{ mA}^{(2)}$<br>$I_{OL} = 12 \text{ mA}$ |

| Z <sub>OUT</sub>                | Output Impedance                 |      | 14 – 17 |                       | Ω      |                                                            |

| I <sub>CCQ</sub> <sup>(3)</sup> | Maximum Quiescent Supply Current |      |         | 2.0                   | mA     | All V <sub>CC</sub> Pins                                   |

1. Input pull-up / pull-down resistors influence input current.

2. The MPC9446 is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated

transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up to two 50  $\Omega$  series terminated transmission lines.

3. I<sub>CCQ</sub> is the DC current consumption of the device with all outputs open and the input in its default state or open.

# Table 7. AC Characteristics (V<sub>CC</sub> = V<sub>CCA</sub> = V<sub>CCB</sub> = V<sub>CCC</sub> = 3.3 V ± 5%, T<sub>A</sub> = -40°C to +85°C)<sup>(1)</sup>

| Symbol                               | Characteristics                                                                                              | Min | Тур        | Мах                       | Unit           | Condition                                              |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|------------|---------------------------|----------------|--------------------------------------------------------|

| f <sub>ref</sub>                     | Input Frequency                                                                                              | 0   |            | 250 <sup>(2)</sup>        | MHz            |                                                        |

| f <sub>MAX</sub>                     | Maximum Output Frequency ÷1 outpu<br>÷2 outpu                                                                |     |            | 250 <sup>(2)</sup><br>125 | MHz<br>MHz     | FSELx = 0<br>FSELx = 1                                 |

| t <sub>P, REF</sub>                  | Reference Input Pulse Width                                                                                  | 1.4 |            |                           | ns             |                                                        |

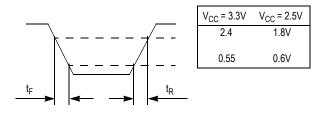

| t <sub>r</sub> , t <sub>f</sub>      | CCLK Input Rise/Fall Time                                                                                    |     |            | 1.0 <sup>(3)</sup>        | ns             | 0.8 to 2.0 V                                           |

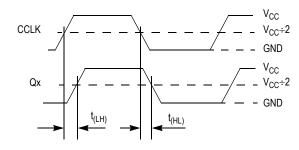

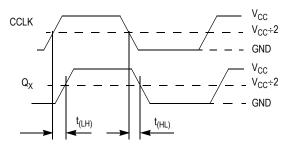

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CCLK0,1 to any C<br>CCLK0,1 to any C                                                       |     | 2.8<br>2.8 | 4.45<br>4.2               | ns<br>ns       |                                                        |

| t <sub>PLZ, HZ</sub>                 | Output Disable Time                                                                                          |     |            | 10                        | ns             |                                                        |

| t <sub>PZL, LZ</sub>                 | Output Enable Time                                                                                           |     |            | 10                        | ns             |                                                        |

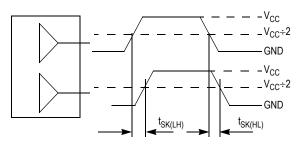

| t <sub>sk(O)</sub>                   | Output-to-Output Skew Within one ban<br>Any output bank, same output divide<br>Any output, Any output divide | r   |            | 150<br>200<br>350         | ps<br>ps<br>ps |                                                        |

| t <sub>sk(PP)</sub>                  | Device-to-Device Skew                                                                                        |     |            | 2.25                      | ns             |                                                        |

| t <sub>SK(P)</sub>                   | Output Pulse Skew <sup>(4)</sup>                                                                             |     |            | 200                       | ps             |                                                        |

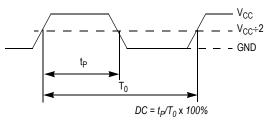

| DCQ                                  | Output Duty Cycle ÷1 outpu<br>÷2 outpu                                                                       |     | 50<br>50   | 53<br>55                  | %<br>%         | DC <sub>REF</sub> = 50%<br>DC <sub>REF</sub> = 25%–75% |

| t <sub>r</sub> , t <sub>f</sub>      | Output Rise/Fall Time                                                                                        | 0.1 |            | 1.0                       | ns             | 0.55 to 2.4 V                                          |

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V<sub>TT</sub>.

2. The MPC9446 is functional up to an input and output clock frequency of 350 MHz and is characterized up to 250 MHz.

3. Violation of the 1.0 ns maximum input rise and fall time limit will affect the device propagation delay, device-to-device skew, reference input pulse width, output duty cycle and maximum frequency specifications.

Output pulse skew t<sub>SK(P)</sub> is the absolute difference of the propagation delay times: | t<sub>PLH</sub> - t<sub>PHL</sub> |. Output duty cycle is frequency dependent: DC<sub>Q</sub> = (0.5 ± t<sub>SK(P)</sub> • f<sub>OUT</sub>). For example at f<sub>OUT</sub> = 125 MHz the output duty cycle limit is 50% ± 2.5%.

Table 8. DC Characteristics ( $V_{CC} = V_{CCA} = V_{CCB} = V_{CCC} = 2.5 \text{ V} \pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to +85°C)

| Symbol                          | Characteristics                  | Min  | Тур                    | Max                   | Unit | Condition                             |

|---------------------------------|----------------------------------|------|------------------------|-----------------------|------|---------------------------------------|

| V <sub>IH</sub>                 | Input High Voltage               | 1.7  |                        | V <sub>CC</sub> + 0.3 | V    | LVCMOS                                |

| V <sub>IL</sub>                 | Input Low Voltage                | -0.3 |                        | 0.7                   | V    | LVCMOS                                |

| V <sub>OH</sub>                 | Output High Voltage              | 1.8  |                        |                       | V    | $I_{OH} = -15 \text{ mA}^{(1)}$       |

| V <sub>OL</sub>                 | Output Low Voltage               |      |                        | 0.6                   | V    | I <sub>OL</sub> = 15 mA               |

| Z <sub>OUT</sub>                | Output Impedance                 |      | 17 – 20 <sup>(2)</sup> |                       | Ω    |                                       |

| I <sub>IN</sub>                 | Input Current <sup>(2)</sup>     |      |                        | ±200                  | μA   | $V_{IN}$ = GND or $V_{IN}$ = $V_{CC}$ |

| I <sub>CCQ</sub> <sup>(3)</sup> | Maximum Quiescent Supply Current |      |                        | 2.0                   | mA   | All V <sub>CC</sub> Pins              |

The MPC9446 is capable of driving 50 Ω transmission lines on the incident edge. Each output drives one 50 Ω parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up to two 50 Ω series terminated transmission lines per output.

2. Input pull-up / pull-down resistors influence input current.

3. I<sub>CCQ</sub> is the DC current consumption of the device with all outputs open and the input in its default state or open.

Table 9. AC Characteristics ( $V_{CC} = V_{CCA} = V_{CCB} = V_{CCC} = 2.5 \text{ V} \pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ )<sup>(1)</sup>

| Symbol                               | Characteristics                                                                                               | Min  | Тур | Мах                       | Unit           | Condition               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----|---------------------------|----------------|-------------------------|

| f <sub>ref</sub>                     | Input Frequency                                                                                               | 0    |     | 250 <sup>(2)</sup>        | MHz            |                         |

| f <sub>MAX</sub>                     | Maximum Output Frequency ÷1 output<br>÷2 output                                                               |      |     | 250 <sup>(2)</sup><br>125 | MHz<br>MHz     | FSELx = 0<br>FSELx = 1  |

| t <sub>P, REF</sub>                  | Reference Input Pulse Width                                                                                   | 1.4  |     |                           | ns             |                         |

| t <sub>r</sub> , t <sub>f</sub>      | CCLK Input Rise/Fall Time                                                                                     |      |     | 1.0 <sup>(3)</sup>        | ns             | 0.7 to 1.7 V            |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CCLK0,1 to any Q<br>CCLK0,1 to any Q                                                        |      |     | 5.6<br>5.5                | ns<br>ns       |                         |

| t <sub>PLZ, HZ</sub>                 | Output Disable Time                                                                                           |      |     | 10                        | ns             |                         |

| t <sub>PZL, LZ</sub>                 | Output Enable Time                                                                                            |      |     | 10                        | ns             |                         |

| t <sub>sk(O)</sub>                   | Output-to-Output Skew Within one bank<br>Any output bank, same output divide<br>Any output, Any output divide | r    |     | 150<br>200<br>350         | ps<br>ps<br>ps |                         |

| t <sub>sk(PP)</sub>                  | Device-to-Device Skew                                                                                         |      |     | 3.0                       | ns             |                         |

| t <sub>SK(P)</sub>                   | Output Pulse Skew <sup>(4)</sup>                                                                              |      |     | 200                       | ps             |                         |

| $DC_{Q}$                             | Output Duty Cycle ÷1 or ÷2 output                                                                             | t 45 | 50  | 55                        | %              | DC <sub>REF</sub> = 50% |

| t <sub>r</sub> , t <sub>f</sub>      | Output Rise/Fall Time                                                                                         | 0.1  |     | 1.0                       | ns             | 0.6 to 1.8 V            |

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V\_TT.

2. The MPC9446 is functional up to an input and output clock frequency of 350 MHz and is characterized up to 250 MHz.

3. Violation of the 1.0 ns maximum input rise and fall time limit will affect the device propagation delay, device-to-device skew, reference input pulse width, output duty cycle and maximum frequency specifications.

4. Output pulse skew  $t_{SK(P)}$  is the absolute difference of the propagation delay times:  $|t_{PLH} - t_{PHL}|$ . Output duty cycle is frequency dependent:  $DC_Q = (0.5 \pm t_{SK(P)} \cdot f_{OUT})$ . For example at  $f_{OUT} = 125$  MHz the output duty cycle limit is 50% ± 2.5%.

## Table 10. AC Characteristics ( $V_{CC}$ = 3.3 V + 5%, $V_{CCA}$ , $V_{CCB}$ , $V_{CCC}$ = 2.5 V + 5% or 3.3 V + 5%, $T_A$ = -40°C to +85°C)<sup>(1)</sup> (2)

| Symbol              | Characteristics                       | Min | Тур         | Max   | Unit | Condition               |

|---------------------|---------------------------------------|-----|-------------|-------|------|-------------------------|

| t <sub>sk(O)</sub>  | Output-to-Output Skew Within one bank |     |             | 150   | ps   |                         |

|                     | Any output bank, same output divider  |     |             | 250   | ps   |                         |

|                     | Any output, Any output divider        |     |             | 350   | ps   |                         |

| t <sub>sk(PP)</sub> | Device-to-Device Skew                 |     |             | 2.5   | ns   |                         |

| t <sub>PLH,HL</sub> | Propagation Delay CCLK0,1 to any Q    |     | See 3.3 V 7 | Fable |      |                         |

| t <sub>SK(P)</sub>  | Output Pulse Skew <sup>(3)</sup>      |     |             | 250   | ps   |                         |

| DCQ                 | Output Duty Cycle ÷1 or ÷2 output     | 45  | 50          | 55    | %    | DC <sub>REF</sub> = 50% |

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V<sub>TT</sub>.

2. For all other AC specifications, refer to 2.5 V or 3.3 V tables according to the supply voltage of the output bank.

Output pulse skew t<sub>SK(P)</sub> is the absolute difference of the propagation delay times: | t<sub>PLH</sub> - t<sub>PHL</sub> |. Output duty cycle is frequency dependent: DC<sub>Q</sub> = (0.5 ± t<sub>SK(P)</sub> • f<sub>OUT</sub>).

## **APPLICATIONS INFORMATION**

#### **Driving Transmission Lines**

The MPC9446 clock driver was designed to drive highspeed signals in a terminated transmission line environment. To provide the optimum flexibility to the user, the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of less than 20  $\Omega$ , the drivers can drive either parallel or series terminated transmission lines. For more information on transmission lines the reader is referred to Freescale application note AN1091. In most high performance clock networks, point-to-point distribution of signals is the method of choice. In a point-to-point scheme, either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a 50  $\Omega$  resistance to V<sub>CC</sub>÷2.

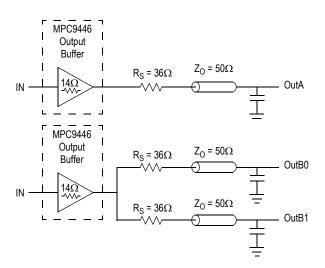

This technique draws a fairly high level of DC current, and thus, only a single terminated line can be driven by each output of the MPC9446 clock driver. For the series terminated case, however, there is no DC current draw; thus, the outputs can drive multiple series terminated lines. Figure 3 illustrates an output driving a single series terminated line versus two series terminated lines in parallel. When taken to its extreme, the fanout of the MPC9446 clock driver is effectively doubled due to its capability to drive multiple lines.

Figure 3. Single versus Dual Transmission Lines

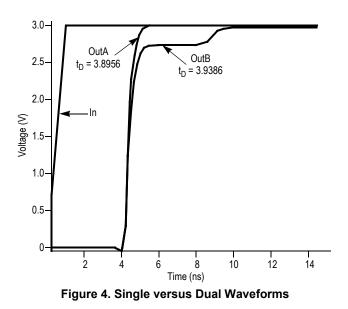

The waveform plots in Figure 4 show the simulation results of an output driving a single line versus two lines. In both cases, the drive capability of the MPC9446 output buffer is more than sufficient to drive 50  $\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations, a delta of only 43 ps exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output-to-output skew of the MPC9446. The output waveform in Figure 4 shows a step in the waveform. This step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the 36  $\Omega$  series resistor plus the output impedance does not match the parallel combination of

the line impedances. The voltage wave launched down the two lines will equal:

$$V_{L} = V_{S} (Z_{0} \div (R_{S} + R_{0} + Z_{0}))$$

$$Z_{0} = 50 \Omega \parallel 50 \Omega$$

$$R_{S} = 36 \Omega \parallel 36 \Omega$$

$$R_{0} = 14 \Omega$$

$$V_{L} = 3.0 (25 \div (18 + 14 + 25))$$

$$= 1.31 V$$

At the load end, the voltage will double, due to the near unity reflection coefficient, to 2.5 V. It will then increment towards the quiescent 3.0 V in steps separated by one round trip delay (in this case 4.0 ns).

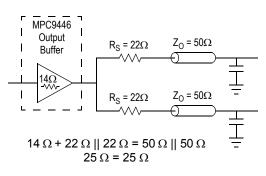

Since this step is well above the threshold region, it will not cause any false clock triggering; however, designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines, the situation in Figure 5 should be used. In this case, the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance, the line impedance is perfectly matched.

Figure 5. Optimized Dual Line Termination

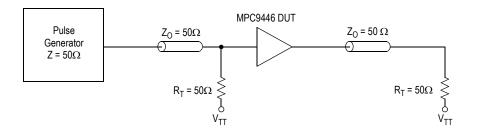

Figure 6. CCLK0, 1 MPC9446 AC Test Reference for V<sub>CC</sub> = 3.3 V and V<sub>CC</sub> = 2.5 V

Figure 7. Output Transition Time Test Reference

The pin-to-pin skew is defined as the worst case difference in propagation delay between any two similar delay paths within a single device.

The time from the PLL controlled edge to the non controlled edge, divided by the time between PLL controlled edges, expressed as a percentage.

Figure 11. Output Duty Cycle (DC)

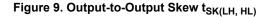

Figure 8. Propagation Delay (t<sub>PD</sub>) Test Reference

$t_{SK(P)}$  = |  $t_{PLH} - t_{PHL}$  |

## Figure 10. Output Pulse Skew (t<sub>SK(P)</sub>) Test Reference

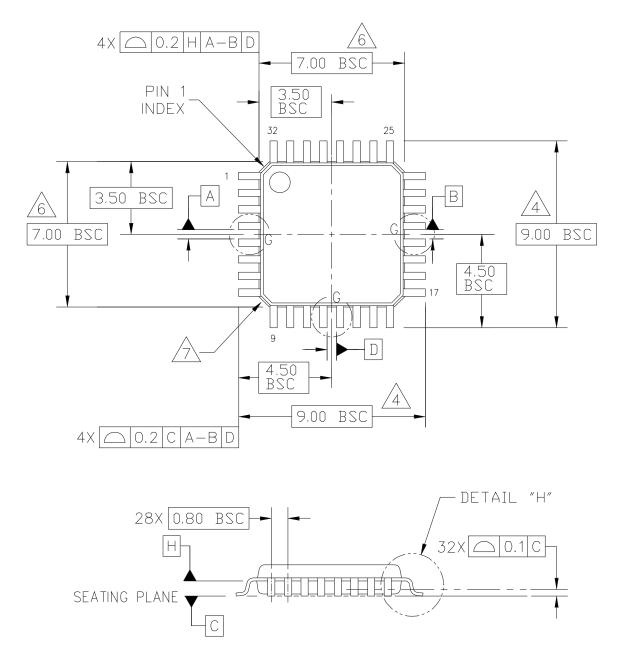

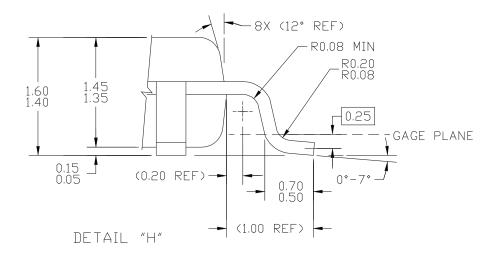

## PACKAGE DIMENSIONS

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | Mechanical outline |              | PRINT VERSION NE | IT TO SCALE |

|---------------------------------------------------------|--------------------|--------------|------------------|-------------|

| TITLE:                                                  |                    | DOCUMENT NO  | 1: 98ASH70029A   | RE∨: C      |

| LOW PROFILE QUAD FLAT PA                                | · · · · ·          | CASE NUMBER  | 2: 873A-04       | 01 APR 2005 |

| 32 LEAD, 0.8 PITCH (7 X                                 | 7 X 1.4)           | STANDARD: JE | DEC MS-026 BBA   |             |

PAGE 1 OF 3

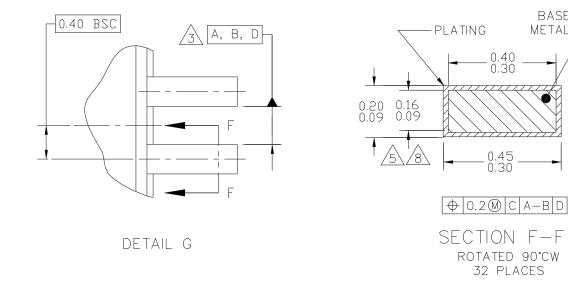

## CASE 873A-04 ISSUE C 32-LEAD LQFP PACKAGE

BASE

METAL

## **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                | PRINT VERSION NE | JT TO SCALE |

|---------------------------------------------------------|--------------------|----------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NO        | 1: 98ASH70029A | RE∨: C           |             |

| LOW PROFILE QUAD FLAT P.<br>32 LEAD, 0.8 PITCH (7 X     |                    | CASE NUMBER    | 2: 873A-04       | 01 APR 2005 |

| 52 LEAD, 0.8 THEIR (7 A                                 | ( / / 1.4)         | STANDARD: JE   | DEC MS-026 BBA   |             |

PAGE 2 OF 3

## CASE 873A-04 **ISSUE C** 32-LEAD LQFP PACKAGE

## PACKAGE DIMENSIONS

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

/3. DATUMS A, B, AND D TO BE DETERMINED AT DATUM PLANE H.

$\underline{/4.}$  dimensions to be determined at seating plane datum c.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THZ LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

- <u>/6.</u> DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

/7 exact shape of each corner is optional.

A. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 MM AND 0.25 MM FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE       |                | PRINT VERSION NOT TO SCALE |  |

|---------------------------------------------------------|--------------------------|----------------|----------------------------|--|

| TITLE:                                                  | DOCUMENT NO: 98ASH70029A |                | RE∨∶C                      |  |

| LOW PROFILE QUAD FLAT P.                                | CASE NUMBER: 873A-04     |                | 01 APR 2005                |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | STANDARD: JE             | DEC MS-026 BBA |                            |  |

PAGE 3 OF 3

## CASE 873A-04 ISSUE C 32-LEAD LQFP PACKAGE

# **Revision History Sheet**

| Rev | Table | Page | Description of Change                | Date     |

|-----|-------|------|--------------------------------------|----------|

| 5   |       | 1    | NRND – Not Recommend for New Designs | 12/21/12 |

|     |       |      |                                      |          |

# We've Got Your Timing Solution

6024 Silver Creek Valley Road San Jose, California 95138 Sales 800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT **Technical Support**

netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.