# Intel StrataFlash® Wireless Memory System (LV18 SCSP)

1024-Mbit LVX Family with LPSDRAM

## **Datasheet**

## **Product Features**

## **■** Device Memory Architecture

- -Flash die density: 128-, 256-Mbit

- —LPSDRAM die density: 128-, 256-Mbit

- —Top or Bottom parameter flash configuration

## Device Voltage

- —Core:  $V_{CC} = 1.8 \text{ V (typ.)}$

- $-I/O: V_{CCQ} = 1.8 \text{ V (typ.)}$

## Device Common Performance

- —Buffered EFP: 5μs / Byte (typ.) per die

- —Buffer Program: 7μs / Byte (typ.) per die

- -Concurrent Buffered EFP: 6.4-Mbps effective with 4 flash dies

# ■ Device Common Architecture Sheet4U.com Data Segment Flash Architecture

- —Asymmetrical blocking structure

- —16-KWord parameter blocks (Top or Bottom); 64-KWord main blocks

- —Zero-latency block locking

- —Absolute write protection with block lock down using F-VPP and F-WP#

## Device Packaging

- —103 active balls: 9 x 12 ball matrix

- —Area: 9 x 11 mm to 11 x 11 mm

- —Height: 1.4 mm

## SDRAM Architecture and Performance

- -Clock rate: 105 MHz

- —Four internal banks

- -Burst Length: 1, 2, 4, 8, or full page

## **■** Code Segment Flash Read Performance

- -85 ns initial access

- —25 ns Asynchronous Page read

- —14 ns Synchronous read (t<sub>CHOV</sub>)

- —54 MHz (max.) CLK

## ■ Data Segment Flash Performance

- —170 ns initial access

- —55 ns Asynchronous Page read

## ■ Code Segment Flash Architecture

- -Hardware Read-While-Write/Erase

- —Multiple 8-Mbit / 16-Mbit partition sizes

- -2-Kbit One-Time-Programmable **Protection Register**

- —Software Read-While-Write/Erase

- —Single partition size die

## Flash Software

- —Intel<sup>®</sup> FDI, Intel<sup>®</sup> PSM, and Intel<sup>®</sup> VFM

- —Common Flash Interface

- —Basic/Extended Command Set

## Quality and Reliability

- —Extended temperature: -25 °C to +85 °C

- -Minimum 100 K flash block erase cycle

- —0.13 μm ETOX™ VIII flash technology

Intel StrataFlash® Wireless Memory System (LV18 SCSP) with Low-Power SDRAM (LVX family) offers a variety of high performance code segment, large embedded data segment, and low-power SDRAM combinations in a common package on 0.13 μm ETOX<sup>TM</sup> VIII flash technology. The LVX family integrates up to two code segment flash dies, two data segment flash dies, and two low-power SDRAM dies or one SRAM die in a common x16D Performance ballout.

Notice: This document contains information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

> 300945-006 October 2004 WWW.DataSheet4U.com

DataSheet4U.com

t4U.com DataSho

## DataSheet4U.com

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The Intel StrataFlash® Wireless Memory System (LV18 SCSP) 1024-Mbit LVX Family with Low-Power SDRAM may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation.

DataSheet4U.com

DataSheet 4U.com

| 1.0 | Introduction                                                                    | 7              |

|-----|---------------------------------------------------------------------------------|----------------|

|     | <ul><li>1.1 Nomenclature</li><li>1.2 Acronyms</li><li>1.3 Conventions</li></ul> | 8              |

| 2.0 | Functional Overview                                                             | 11             |

|     | 2.1 Product Description                                                         | 13<br>13       |

| 3.0 | Package Information                                                             |                |

| 4.0 | Ballout and Signal Descriptions                                                 | 23             |

|     | 4.1 Signal Ballout                                                              | 23             |

| 5.0 | Maximum Ratings and Operating Conditions                                        | 27             |

|     | 5.1 Absolute Maximum Ratings                                                    |                |

| 6.0 | Electrical Specifications                                                       | 29             |

|     | 6.1 DC Voltage and Current Characteristics                                      | 29             |

| 7.0 | AC Characteristics                                                              |                |

|     | 7.1 Device AC Test Conditions                                                   | 31<br>31<br>32 |

| 3.0 | Power and Reset Specifications                                                  | 34             |

| 9.0 | Operations Overview                                                             | 34             |

|     | 9.1 Rus Operations                                                              | 3/             |

DataShe

DataSheet4U.com

et4U.com

**Datasheet**

www.DataSheet4U.com

| 10.0 Flash F                                                                              | Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 40                                                                             |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 11.0 Flash F                                                                              | Program Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .40                                                                              |

| 12.0 Flash E                                                                              | Erase Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .40                                                                              |

| 13.0 Flash \$                                                                             | Suspend and Resume Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .40                                                                              |

| 14.0 Flash E                                                                              | Block Locking and Unlocking Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 40                                                                             |

|                                                                                           | Protection Register Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 16.0 Flash (                                                                              | Configuration Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .40                                                                              |

|                                                                                           | Oual Operation Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 18.0 LPSDR                                                                                | AM Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .41                                                                              |

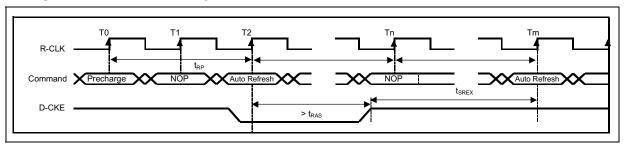

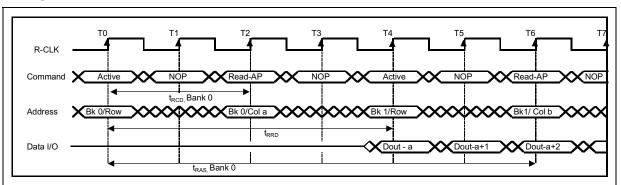

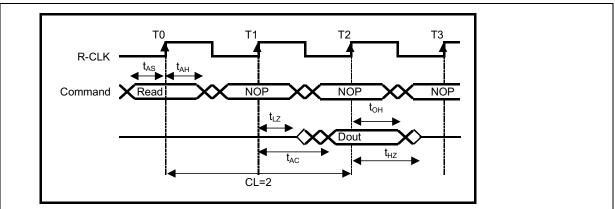

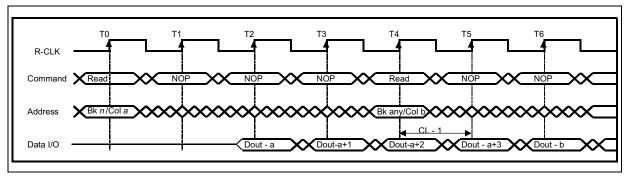

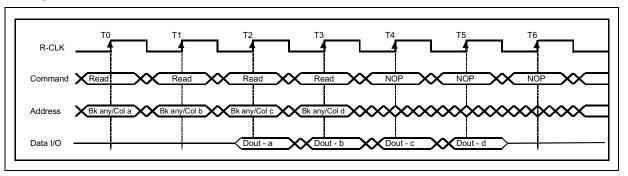

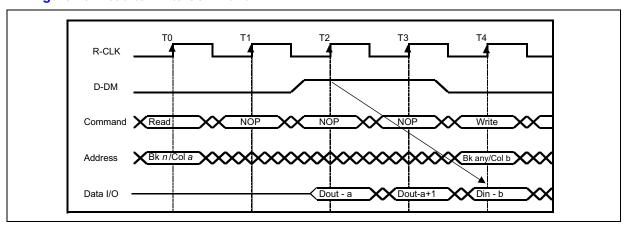

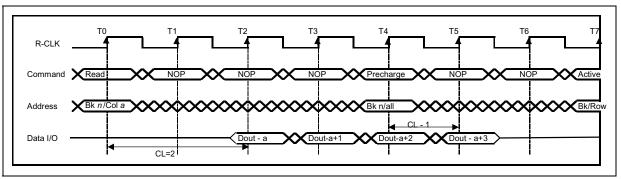

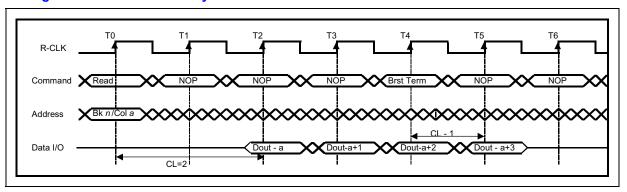

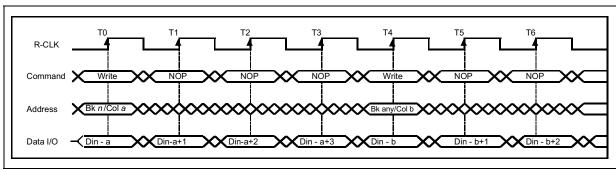

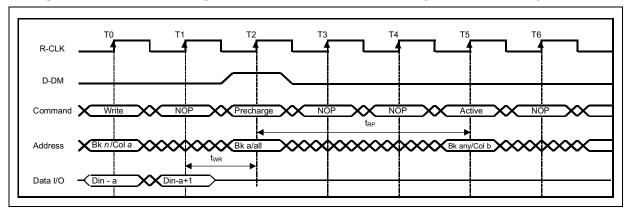

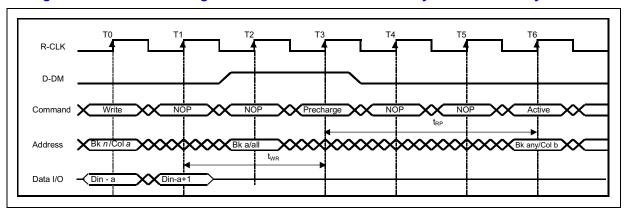

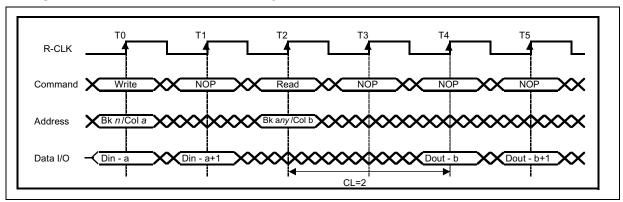

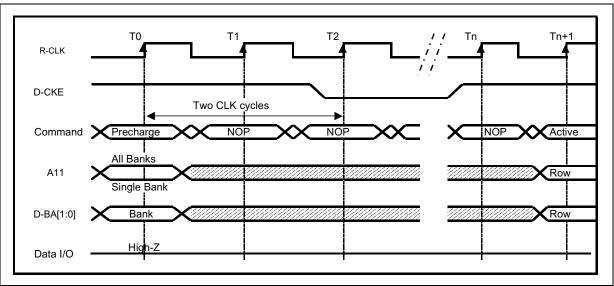

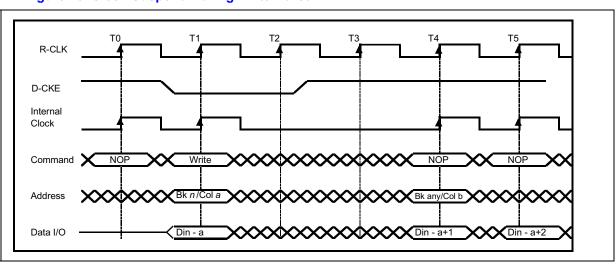

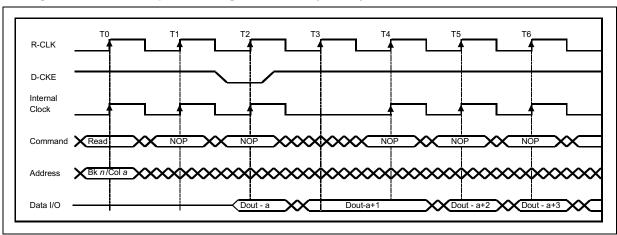

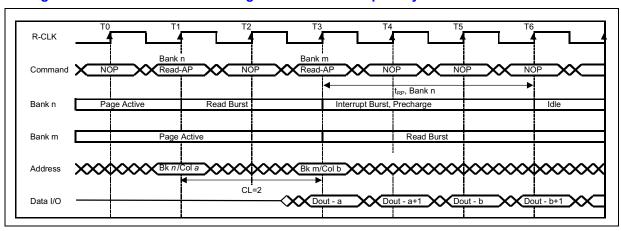

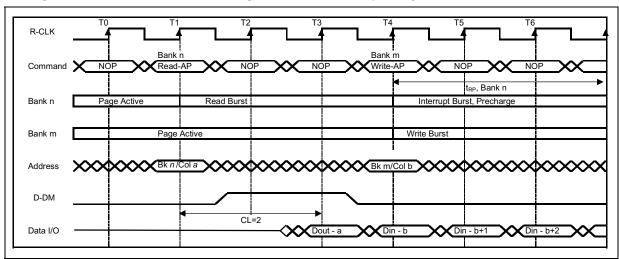

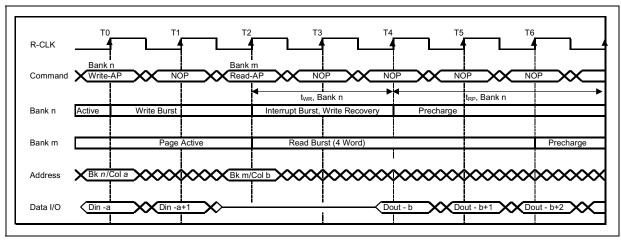

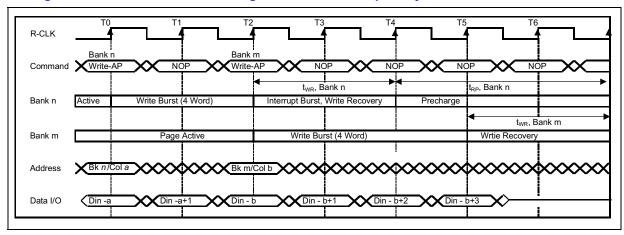

| 18.2 LF<br>18.3 Ex<br>18.4 LF<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18 | PSDRAM Power-up Sequence and Initialization PSDRAM Mode Register Extended Mode Register PSDRAM Commands and Operations B.4.1 LPSDRAM No Operation / Device Deselect 18.4.1.1 Device Deselect (NOP) 18.4.1.2 No Operation (NOP) B.4.2 LPSDRAM Active B.4.3 LPSDRAM Read B.4.4 LPSDRAM Write B.4.5 LPSDRAM Power-Downsta Sheet AU com B.4.6 LPSDRAM Deep Power-Down B.4.7 LPSDRAM Deep Power-Down B.4.7 LPSDRAM Precharge B.4.8 LPSDRAM Auto Precharge B.4.9 LPSDRAM Auto Precharge B.4.10 LPSDRAM Concurrent Auto Precharge B.4.11 LPSDRAM Burst Terminate B.4.12 LPSDRAM Auto Refresh B.4.13 LPSDRAM Self Refresh | .41<br>.42<br>.43<br>.43<br>.43<br>.43<br>.44<br>.45<br>.45<br>.46<br>.46<br>.54 |

| Appendix A                                                                                | Write State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 55                                                                             |

| Appendix B                                                                                | Common Flash Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 55                                                                             |

| Appendix C                                                                                | Flash Flowcharts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 55                                                                             |

| Appendix D                                                                                | Additional Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 56                                                                             |

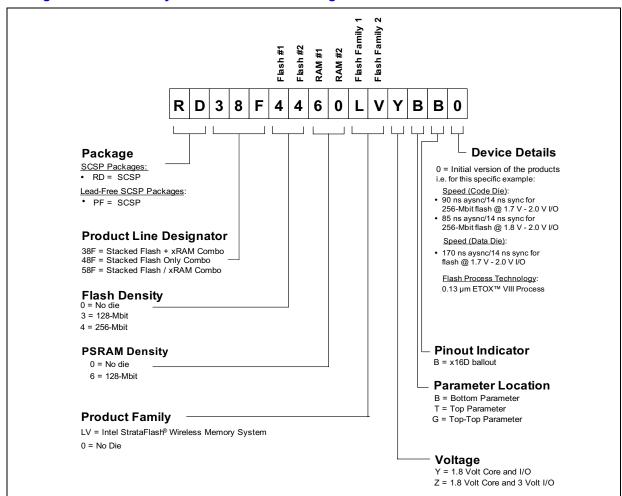

| Appendix E                                                                                | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 57                                                                             |

et4U.com

DataShe

# **Revision History**

| Date           | Revision | Description                                                                                                                                                                                                                                      |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February, 2004 | -001     | Initial release.                                                                                                                                                                                                                                 |

| February, 2004 | -002     | Corrected information in the Memory Map table, code and data segments, bottom parameter.                                                                                                                                                         |

| April, 2004    | -003     | Corrected errors in Table 1 and Table 26. The package dimension of part RD48F4444LVYBB0 RD48F4444LVYTB0 now reads 11x11x1.4 instead of 9x11x1.4.                                                                                                 |

| June, 2004     | -004     | Updated Table 1 and Table 26. Added line item RD38F4460LVYGB0. Added G as an option to Figure 29 - Ordering Information. Added Figure 6, a top-top memory map diagram. Added top/top configuration feature to the title page "Product Features". |

| July, 2004     | -005     | Added the mechanical specification diagram, Figure 5 for the 11x11x1.4 mm option.                                                                                                                                                                |

|                |          | Added line items 256L18/256V18/256SD, 256L18/256L18/ 256V18/256SD, and 256L18/256V18/256V18/256SD to the following tables:                                                                                                                       |

| October, 2004  | -006     | * Table 1 "Available Product Ordering Information for the LVX Family with LPSDRAM" on page 12                                                                                                                                                    |

|                |          | * Table 26 "LVX Family with LPSDRAM: Available Product Ordering Information" on page 57                                                                                                                                                          |

DataSheet4U.com

DataShe

et4U.com

DataSheet4U.com www.DataSheet4U.com

DataSheet4U.com

et4U.com DataShe

DataSheet4U.com

DataSheet4U.com

6

www.DataSheet4U.com

#### Introduction 1.0

This document provides preliminary information about the Intel StrataFlash® Wireless Memory System (LV18 SCSP) with Low-Power SDRAM (LVX family). This document describes the flash dies used in the code and large embedded data segments and the features, operations, and specifications within the subsystem. Also described in this document are the LPSDRAM characteristics and operations. The intent of this document is to provide information where these SCSP products differ from the Intel StrataFlash® Wireless Memory System (LV18) datasheet.

Refer to the latest revision of the Intel StrataFlash® Wireless Memory System Datasheet (order number 253854) for flash product details not included in this document.

#### 1.1 **Nomenclature**

1.8 V Core Voltage Range of 1.7 V − 1.95 V

1.8 V I/O Voltage Range of 1.7 V – 1.95 V

Asserted Signal with logical voltage level  $V_{II}$ , or enabled

Deasserted Signal with logical voltage level V<sub>IH</sub>, or disabled

High-Z Tri-stated or High Impedance

DrivertaSheet4U.com Low-Z

Non-Array Reads Flash reads which return flash Device Identifier, CFI Query, Protection

Register and Status Register information

**Program** An operation to Write data to the flash array

Bus cycle operation at the inputs of the flash die, in which a command Write

or data are sent to the flash array

Block Group of cells, bits, bytes or words within the flash memory array that

get erased with one erase instruction

Parameter block Any 16-Kword flash array block.

Main block Any 64-Kword flash array block.

Top parameter Previously referred to as a top-boot device, a device with flash

parameter partition located at the highest physical address of its

memory map for processor system boot up.

**Bottom parameter** Previously referred to as a bottom-boot device, a device with flash

parameter partition located at the lowest physical address of its memory

map for processor system boot up.

**Bottom-Top parameter** SCSP device configuration of two flash dies in the same segment

arranged with the parameter partitions located at the lowest and highest

physical address of its memory map.

DataSheet4U.com

www.DataSheet4U.com

7

DataSheet4U.com

Partition A group of flash blocks that shares common Status Register read state.

**Parameter partition** A flash partition containing parameter and main blocks.

**Main partition** A flash partition containing only main blocks.

**Die** Individual physical flash or RAM die used in a SCSP memory

subsystem device

**Segment** A section of the SCSP memory subsystem divided for different

operating characteristics. The SCSP memory subsystem has three segments: a code segment, a data segment, and an xRAM segment.

**Code segment** A segment that contains one or two flash memory dies optimized for

fast code or data reads. Each die features multi-partitions synchronous

read-while-write or burst read-while-erase capability.

**Data segment** A segment contains one or two flash memory dies optimized for large

embedded data. Each die feature single-partition asynchronous read,

write, and erase operations.

**xRAM segment** A segment contains one or two xRAM memory dies. The xRAM

combinations could include SRAM, PSRAM, or LPSDRAM.

**Subsystem** A stacked memory integration concept made up of multiple memory

dies arranged in code, data, and xRAM segments.

**Device** A specific stacked flash + xRAM memory density configuration

combination within the LVX product family.

## 1.2 Acronyms

**APS** Automatic Power Savings

**Buffered EFP** Buffered Enhanced Factory Programming

**CFI** Common Flash Interface

**CR** Configuration Register

CUI Command User Interface

**DU** Do Not Use

**ETOX** EPROM Tunnel Oxide

**OTP** One-Time Programmable

PLR Protection Lock Register

**PR** Protection Register

**RCR** Read Configuration Register

**RFU** Reserved for Future Use (all unused active signals in a package ballout)

www.DataSheet4U.com

**Datasheet**

DataSheet4U.com

8

**RWE** Read-While-Erase

**RWW** Read-While-Write

SCSP Stacked Chip Scale Package

SR Status Register

**SRD** Status Register Data

WSM Write State Machine

## 1.3 Conventions

0x Hexadecimal number prefix

**0b** Binary number prefix

A5 Denotes one element of a signal group membership, in this case address

bit 5.

**ADV**# A name without a prefix denotes a global signal of the device; for

example, Address Valid is global because there is no die specific

reference.

**bit** Binary unit, valid range [0, 1]

byte Eight bits, valid range [0x00 - 0xFF]

Clear Logical zero (0)

**DQ[15:0]** Denotes a group of similarly named signals, such as data bus.

F[3:1]-CE#, F[2:1]-OE# This is the method used to refer to more than one chip-enable or output

enable at the same time. When each die is refer to individually, the reference will be F1-CE# and F1-OE# (for die #1), F2-CE# and F2-OE#

(for die #2), and F3-CE# (for die #3), unless noted otherwise.

"F" denotes the flash specific signal and "CE#" is the root signal name of the flash die Chip-Enable. Other notation includes: "S" to denote SRAM, "P" to denote PSRAM, "D" to denote LPSDRAM, and "R" to

denote common RAM type signal names.

**k (noun)** 1000 (units)

**Kb** 1024 bits

**KB** 1024 bytes

**Kbit** 1024 bits

**KByte** 1024 bytes (8,192 bits)

**Kword** 1024 words (16,384 bits)

**Mbit** 1,048,576 bits

**MByte** 1,048,576 bytes (8,388,608 bits)

DataSheet4U.com www.DataSheet4U.com

Datasheet

9

**MWord** 1,048,576 words (16,777,216 bits)

M (noun) 1 million

Mb

1,048,576 bits

MB

1,048,576 bytes

Set Logical one (1)

SR[4] Denotes an individual flash Status Register bit, in this case bit 4 of

SR[7:0].

VCC Signal or voltage connection

$V_{CC}$  Signal or voltage level

**Word** Two bytes or sixteen bits, valid range [0x0000 - 0xFFFFF]

et4U.com

DataShe

DataSheet4U.com

DataSheet4U.com

www.DataSheet4U.com

10

#### **Functional Overview** 2.0

This section provides an overview of the features and capabilities of Intel StrataFlash® Wireless Memory System (LV18 SCSP) with Low-Power SDRAM LVX family; hereafter in this document, this device is called the LVX family with LPSDRAM device.

#### 2.1 **Product Description**

The LVX family with LPSDRAM device incorporates flash dies used as code segment flash die and large embedded data segment flash die, along with LPSDRAM for a high performance, costeffective high density solution. This stacked device utilizes the latest Intel StrataFlash® Wireless Memory System on 0.13 μm ETOX<sup>TM</sup> VIII process technology.

The code segment flash is a high performance, multi-partition, synchronous burst-mode Read-While-Write (RWW) or Read-While-Erase (RWE), while the large embedded data segment is a cost efficient, single partition, asynchronous memory die.

The package for this device is available in a x16D Performance ballout, supporting flash-only or flash with LPSDRAM stacked memory combinations. The Intel® SCSP package in a x16D performance ballout with a 0.8 mm ball pitch, 9 x 12 active ball matrix supports a memory subsystem up to 105 MHz on a x16-bit bus width. See Figure 1, "LVX Family with LPSDRAM Device Block Diagram" on page 11.

Figure 1. LVX Family with LPSDRAM Device Block Diagram

LVX Family Flash (Code/Data) Segment F1-CE# F2-CE# F-WP1# Flach Die #1 Flash Die #2 128- or 256-Mbit) (128- or 256-Mbit) F-RST# F-CLK -ADV# F-VCC F-WP2# WAIT -F-VPP OF# Flash Die #3 Flash Die #4 F3-CE# F4-CE# (128- or 256-Mbit) (128- or 256-Mbit) WE# VCCQ vss DQ[15:0] < xRAM Segment A[MAX:MIN] -R1-CS# LPSDRAM Die #1 R2-CS# D-DM1 / R-UB# -(128/256-Mbit) D-BA[1:0] D-DM0 / R-LB# SRAM Die #1 D-CAS# (8-Mbit) D-RAS# S-CS1# -LPSDRAM Die #2 R-CLK S-CS2 -(128/256-Mbit) - D-CKE S-VCC -R-VCC

11

www.DataSheet4U.com

NOTE: You can request the stacked Flash + xRAM combinations based on memory die options shown in Figure 1. For current available Flash + xRAM combinations, refer to Table 1.

The LVX family with LPSDRAM device consists of a 1.8 V flash core device (F-V<sub>CC</sub>) with 1.8 V and 3.0 V I/O options. The device is available with at least one flash die per code segment and/or one flash die per data segment. However, it has a maximum of two flash dies per code or data segments. See Table 2, "LV Flash Code and Data Die (F-CE#) Stacked Configuration" on page 15 for possible combinations.

Designed for low-voltage systems, the LVX supports read operations with F-V<sub>CC</sub> at 1.8 V, and erase and program operations with F-V<sub>PP</sub> at 1.8 V. Buffered Enhanced Factory Programming (Buffered EFP) provides the fastest flash array programming performance, with elevated F-V<sub>PP</sub> at 9.0 V to increase factory throughput. With F-V<sub>PP</sub> at 1.8 V, F-V<sub>CC</sub> and F-V<sub>CC</sub> can be tied together for a simple, ultra-low-power design. In addition to voltage flexibility, a dedicated F-V<sub>PP</sub> connection provides complete data protection when  $F-V_{PP} \leq V_{PPL,K}$ .

The Intel StrataFlash® Wireless Memory System provides data security through its individual zerolatency block lock capability. Each memory block can be unlocked, locked, or locked-down by hardware or software control.

Individualized F-CE# control allows the user to manage which flash die is asserted, furthering the flexibility of power management while controlling data integrity per segment with F-WP#. The F[2:1]-OE# in LVX products with a x16D Performance ballout ballout are common internally.

Table 1 lists the available LVX product family devices. If the product combinations you are seeking are not listed, the combination is not available at this time and you will need to contact your local Intel representative for details.

Available Product Ordering Information for the LVX Family with LPSDRAM Table 1.

**Package** I/O **RAM Density** Flash Density (Mbit) (Mbit) and RAM **Part Number Notes** Voltage and Family Size **Ballout** (V) Type **Ball Type** (mm) Name RD48F4444LVYBB0 256 L18 + 256 L18 + x16D SCSP 11x11x1.4 256 V18 + 256 V18 (103 Ball) Leaded RD48F4444LVYTB0 RD38F4460LVYBB0 SCSP 256 I 18 + x16D 128 SDRAM 9x11x1.4 RD38F4460LVYTB0 1 256 V18 (103 Ball) Leaded RD38F4460LVYGB0 1.8 RD58F0012LVYBB0 256 L18 + 256 L18 + x16D **SCSP** 9x11x1.4 2 128 SDRAM 256 V18 (103 Ball) Leaded RD58F0012LVYTB0 SCSP RD58F0016LVYBB0 256 L18 + x16D 128 SDRAM 9x11x1.4 256 V18 + 256 V18 (103 Ball) Leaded RD58F0016LVYTB0

### NOTES:

- 1. For the "custom" line item RD38F4460LVYGB0, the "G" designate the F-CE# parameter configuration where F1-CE# = Top parameter and F2-CE# = Top parameter. See Table 2 for details.

- 2. 58Fxxxx nomenclature is used when the stacked device has greater than three flash + RAM dies.

www.DataSheet4U.com

**Datasheet**

12

## 2.2 Unique Product Features

The code segment of the LVX includes the following enhanced features unless specifically noted otherwise:

- 64 unique (Intel pre-programmed) identifier bits and 2,112 user-programmable OTP bits for each code segment flash die.

- Traditional write, erase, and burst-mode read capabilities of Intel<sup>®</sup> Wireless Flash Memory (W18).

- Simultaneous RWW/RWE operations, enabling a burst read operation in one partition with simultaneous program or erase operations in other partitions.

- Burst-read across partition boundaries, but not across segment dies within the subsystem.

- User application code responsible for ensuring that burst-mode reads do not cross into a

partition that is in program or erase mode.

The embedded data segment includes the following features unless specifically noted otherwise:

- High density offerings of up to 512 Mbits are designated specifically for large embedded data.

- Single partition asynchronous page-mode read operation, allowing for a cost-effective ideal storage format.

- Read-while-write or read-while-erase operations can be accomplished with software through program suspend and erase suspend operations.

4U.com

DataSh

## 2.3 Product Configurations and Memory Partitioning

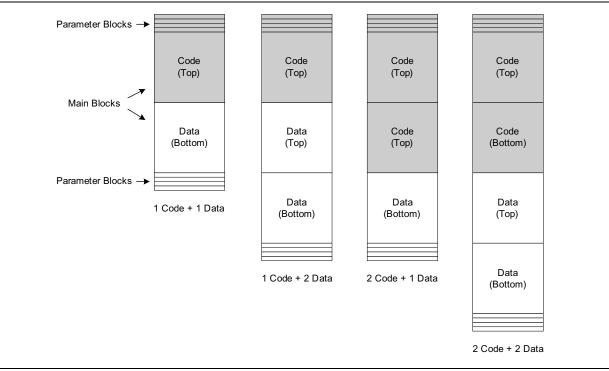

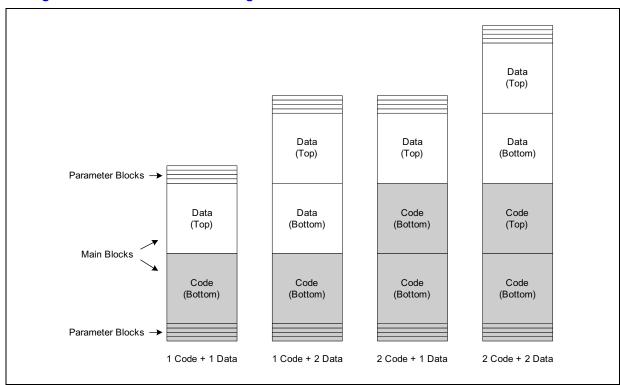

The first flash die, by default is the first code segment flash die, which is a fast, execute-in-place (XIP) solution that is ideally suited toward an instruction fetch application. This portion is the user selected parameter configuration option, where the density can be made up of 128-Mbit dies or 256-Mbit dies, each containing one parameter partition and several main partitions. The parameter partition contains four 16-Kword parameter blocks and seven 64-Kword main blocks; all main partitions consist of eight 64-Kword main blocks.

The large embedded data die segment is a single partition asynchronous page-mode read device that is available in variations of 128-Mbit dies or 256-Mbit dies. The single partition is made up of four 16-Kword parameter blocks and 64-Kword main blocks. The data segment flash die parameter configuration will always be the opposite of the code segment flash die parameter configuration. See Table 2, "LV Flash Code and Data Die (F-CE#) Stacked Configuration" on page 15 for examples of configuration options.

Users have the choice of selecting either a top or a bottom parameter configuration for the code die segment. Depending on the choice of configuration, the data die(s) in the LVX device will be parametrically opposed. For instance, if the user selects top parameter configuration for the code die, the data die in the package will be configured as bottom parameter configuration, and viceversa. This ensures the largest number of contiguous main block addresses for software efficiency.

The xRAM segment can consist of up to two low-power SDRAM (LPSDRAM) dies. The LPSDRAM can be either a 128-Mbit or a 256-Mbit die. For the code segment, partition configurations are as follows:

- 128-Mbit flash die partitions are 8 Mbits.

- 256-Mbit flash die partitions are 16 Mbits.

- Minimum code + data density combination is 384 Mbits.

DataSheet4U.com

www.DataSheet4U.com

**Datasheet**

13

Figure 2. Top Parameter Configurations

et4U.com

DataSheet4U.com

**Figure 3. Bottom Parameter Configurations**

DataSheet4U.com

14

www.DataSheet4U.com

DataShe

Datasheet

Data

Table 2. LV Flash Code and Data Die (F-CE#) Stacked Configuration

|                      |                           | Code S                                   | egment                | Data Se            | gment                 |  |

|----------------------|---------------------------|------------------------------------------|-----------------------|--------------------|-----------------------|--|

| Die                  | Stack Configuration       | 1st Flash<br>Code Die<br>(user selected) | 2nd Flash Code<br>Die | 1st Flash Data Die | 2nd Flash Data<br>Die |  |

|                      | Code + Data               | F1-CE# (Top)                             | F2-CE# (Bottom)       | _                  | _                     |  |

| Тор                  | Code + Data + Data        | F1-CE# (Top)                             | F2-CE# (Top)          | F3-CE# (Bottom)    | _                     |  |

| Parameter            | Code + Code + Data        | F1-CE# (Top)                             | F2-CE# (Top)          | F3-CE# (Bottom)    | _                     |  |

|                      | Code + Code + Data + Data | F1-CE# (Top)                             | F2-CE# (Bottom)       | F3-CE# (Top)       | F4-CE# (Bottom)       |  |

|                      | Code + Data               | F1-CE# (Bottom)                          | F2-CE# (Top)          | _                  | _                     |  |

| Bottom               | Code + Data + Data        | F1-CE# (Bottom)                          | F2-CE# (Bottom)       | F3-CE# (Top)       | _                     |  |

| Parameter            | Code + Code + Data        | F1-CE# (Bottom)                          | F2-CE# (Bottom)       | F3-CE# (Top)       | _                     |  |

|                      | Code + Code + Data + Data | F1-CE# (Bottom)                          | F2-CE# (Top)          | F3-CE# (Bottom)    | F4-CE# (Top)          |  |

|                      | Code + Data               | F1-CE# (Top)                             | F2-CE# (Top)          | _                  | _                     |  |

| Top-Top<br>Parameter | Code + Data + Data        | F1-CE# (Top)                             | F2-CE# (Top)          | F3-CE# (Top)       | _                     |  |

| (custom)             | Code + Code + Data        | F1-CE# (Top)                             | F2-CE# (Top)          | F3-CE# (Top)       | _                     |  |

|                      | Code + Code + Data + Data | F1-CE# (Top)                             | F2-CE# (Top)          | F3-CE# (Top)       | F4-CE# (Top)          |  |

Table 2 shows an example of the memory map and partitioning information for combinations with up to four flash dies in the LVX SCSP family with Synchronous LPSDRAM.

- Top parameter configuration. For two flash dies, flash die #1 (with F1-CE# as its Chip Enable) is configured as top parameter. Flash die #2 (with F2-CE# as its Chip Enable) is configured as bottom parameter.

- Bottom parameter configuration. For two flash dies, flash die #1 (with F1-CE# as its Chip Enable) is configured as bottom parameter. Flash die #2 (with F2-CE# as its Chip Enable) is configured as top parameter.

- Top-Top parameter configuration is a custom option, where all flash dies within the stacked device has the same parameter configuration. In this case, all dies are Top configured.

## 2.4 Memory Map

The LVX family with LPSDRAM device is available in several density and parameter configurations. The memory map is based on the stacking of individual 128- and 256-Mbit flash die density options. The memory map shows individual flash die configurations and block/partition allocations. See the following tables for further information:

- Table 3, "Code-Data (Top Parameter) SCSP Memory Map and Partitioning" on page 16

- Table 4, "Code-Data (Bottom Parameter) SCSP Memory Map and Partitioning" on page 17

- Table 5, "Code-Data (Top Top Parameter) SCSP Memory Map and Partitioning" on page 18

- Table 6, "Code-Code-Data (Top Parameter) SCSP Memory Map and Partitioning" on page 19

- Table 7, "Code-Code-Data (Bottom Parameter) SCSP Memory Map and Partitioning" on page 20

DataSheet4U.com www.DataSheet4U.com

Table 3. Code-Data (Top Parameter) SCSP Memory Map and Partitioning

| Flash | Die Stack          | Partitioning                            | Block Size | Partition<br>Size |      | 128-Mbit Flash | Partition<br>Size | 256-Mbit Flash |               |  |

|-------|--------------------|-----------------------------------------|------------|-------------------|------|----------------|-------------------|----------------|---------------|--|

| Die#  | Config.            | Faithoning                              | (KW)       | (Mbit)            | Blk# | Address Range  | (Mbit)            | Blk#           | Address Range |  |

|       |                    |                                         | 16         |                   | 130  | 7FC000-7FFFFF  |                   | 258            | FFC000-FFFFFF |  |

|       |                    | Parameter                               | ÷          |                   |      | :              |                   | :              | i             |  |

|       |                    | Parameter                               | 16         |                   | 127  | 7F0000-7F3FFF  |                   | 255            | FF0000-FF3FFF |  |

|       | Code               | (Partition 0)                           | 64         |                   | 126  | 7E0000-7EFFFF  |                   | 254            | FE0000-FEFFFF |  |

|       |                    | (                                       | :          |                   |      | :              |                   | :              | :             |  |

| 1     |                    |                                         | 64         | 8                 | 120  | 780000-78FFFF  | 16                | 240            | F00000-FFFFFF |  |

| •     | (Top<br>Parameter) | Main Partitions                         | 64         |                   | 119  | 770000-77FFFF  |                   | 239            | EF0000-EFFFFF |  |

|       |                    | (Partition 1 to 7)                      | :          |                   |      | :              |                   | :              | :             |  |

|       |                    | (* ==================================== | 64         |                   | 64   | 400000-4FFFFF  |                   | 128            | 800000-80FFFF |  |

|       |                    | Main Partitions<br>(Partition 8 to      | 64         |                   | 63   | 3F0000-3FFFFF  |                   | 127            | F70000-F7FFFF |  |

|       |                    |                                         | ÷          |                   |      | :              |                   | :              | :             |  |

|       |                    | 15)                                     | 64         |                   | 0    | 000000-00FFFF  |                   | 0              | 000000-00FFFF |  |

|       |                    |                                         | 64         |                   | 130  | 7F0000-7FFFF   | П                 | 258            | FF0000-FFFFF  |  |

|       |                    |                                         | 04         |                   | 130  | 7F0000-7FFFF   | 1                 |                | FF0000-FFFFF  |  |

|       |                    | Single Partition                        | 64         |                   | 67   | :              |                   | :              | :             |  |

|       |                    | 4x16 Kword                              |            |                   |      | 400000-40FFFF  |                   | 131            | 800000-80FFFF |  |

|       |                    | Parameter                               | 64         |                   | 66   | 3F0000-3FFFFF  |                   | 130            | 7F0000-7FFFF  |  |

|       | Data               | Blocks                                  | :          |                   | :    | :              |                   | :              | 100000 10555  |  |

| 2     | (Bottom            | 127x64 Kword                            | 64         | 128               | 11   | 080000-08FFFF  | 256               | 19             | 100000-10FFFF |  |

|       | Parameter)         | Main Blocks<br>(128 Mb)                 | 64         |                   | 10   | 070000-07FFF   |                   | 18             | 0F0000-0FFFFF |  |

|       |                    | 255x64 Kword                            | 64         | Dat               | aShe | 010000-01FFFF  | 4                 | :              | 040000 04555  |  |

|       |                    | Main Blocks                             |            |                   |      |                | 1                 | 4              | 010000-01FFFF |  |

|       |                    | (256 Mb)                                | 16         |                   | 3    | 00C000-00FFFF  | 4                 | 3              | 00C000-00FFFF |  |

|       |                    |                                         | :          |                   | :    | :              | 1                 | :              | :             |  |

|       |                    |                                         | 16         |                   | 0    | 000000-003FFF  | 11                | 0              | 000000-003FFF |  |

et4U.com

DataShe

DataSheet4U.com

16

www.DataSheet4U.com

Table 4. Code-Data (Bottom Parameter) SCSP Memory Map and Partitioning

| 1     | 1                  | ı                                          |           |                   |      |                  | П                 |                | 1             |  |

|-------|--------------------|--------------------------------------------|-----------|-------------------|------|------------------|-------------------|----------------|---------------|--|

| Flash | Die Stack          | Partitioning                               | Block     | Partition<br>Size |      | 128-Mbit Flash   | Partition<br>Size | 256-Mbit Flash |               |  |

| Die#  | Config.            | · and and                                  | Size (KW) | (Mbit)            | Blk# | Address Range    | (Mbit)            | Blk#           | Address Range |  |

|       |                    | Single Destition                           | 16        |                   | 130  | 7FC000-7FFFF     | İ                 | 258            | FFC000-FFFFFF |  |

|       |                    |                                            | ÷         |                   | :    | :                | 1                 |                | i             |  |

|       |                    | Single Partition                           | 16        |                   | 127  | 7F0000-7F3FFF    |                   | 255            | FF0000-FF3FFF |  |

|       |                    | 4x16 Kword<br>Parameter                    | 64        |                   | 126  | 7E0000-7EFFFF    |                   | 254            | FE0000-FEFFFF |  |

|       | Data               | Blocks                                     | :         |                   | :    | :                | 1                 | :              | :             |  |

| 2     | (Top<br>Parameter) | 127x64 Kword                               | 64        | 8                 | 120  | 780000-78FFFF    | 16                | 240            | F00000-FFFFFF |  |

| _     |                    | Main Blocks                                | 64        |                   | 119  | 770000-77FFFF    |                   | 239            | EF0000-EFFFFF |  |

|       |                    | (128 Mb)                                   | :         |                   | :    | :                |                   |                | :             |  |

|       |                    | 255x64 Kword<br>Main Blocks<br>(256 Mb)    | 64        |                   | 64   | 400000-4FFFFF    |                   | 128            | 800000-80FFFF |  |

|       |                    |                                            | 64        |                   | 63   | 3F0000-3FFFFF    |                   | 127            | F70000-F7FFF  |  |

|       |                    | (                                          | :         |                   | :    | :                |                   | :              | :             |  |

|       |                    |                                            | 64        |                   | 0    | 000000-00FFFF    |                   | 0              | 000000-00FFFF |  |

|       |                    |                                            |           |                   |      |                  |                   |                |               |  |

|       |                    | Main Partitions<br>(Partitions 8 to<br>15) | 64        |                   | 130  | 7F0000-7FFFFF    |                   | 258            | FF0000-FFFFFF |  |

|       |                    |                                            | ÷         |                   | :    | :                | ]                 | :              | :             |  |

|       |                    |                                            | 64        |                   | 67   | 400000-40FFFF    |                   | 131            | 800000-80FFFF |  |

|       |                    | Main Partitions                            | 64        |                   | 66   | 3F0000-3FFFFF    |                   | 130            | 7F0000-7FFFF  |  |

|       | Code               | (Partitions 1 to                           | :         |                   | :    | :                | ]                 | :              | :             |  |

| 1     | (Bottom            | 7)                                         | 64        | 128               | 11   | 080000-08FFFF    | 256               | 19             | 100000-10FFFF |  |

|       | Parameter)         |                                            | 64        |                   | 10   | 070000-07FFFF    |                   | 18             | 0F0000-0FFFF  |  |

|       | ,                  | Danamatan                                  | :         | D 1 0             |      | :                |                   |                | :             |  |

|       |                    | Parameter<br>Partition                     | 64        | DataS             |      | U. 010000-01FFFF | ]                 | 4              | 010000-01FFFF |  |

|       |                    | (Partition 0)                              | 16        |                   | 3    | 00C000-00FFFF    | ]                 | 3              | 00C000-00FFFF |  |

|       |                    |                                            | :         |                   | :    | :                | ]]                | :              | i             |  |

|       |                    |                                            | 16        |                   | 0    | 000000-00FFFF    |                   | 0              | 000000-00FFFF |  |

et4U.com

DataShe

17

DataSheet4U.com

DataSheet4U.com www.DataSheet4U.com

Table 5. Code-Data (Top - Top Parameter) SCSP Memory Map and Partitioning

| Flash | Die Stack          | Partitioning                       | Block Size | Partition<br>Size |            | 128-Mbit Flash     | Partition<br>Size | 256-Mbit Flash |                    |  |

|-------|--------------------|------------------------------------|------------|-------------------|------------|--------------------|-------------------|----------------|--------------------|--|

| Die#  | Config.            |                                    | (KW)       | (Mbit)            | Blk#       | Address Range      | (Mbit)            | Blk#           | Address Range      |  |

|       |                    |                                    | 16         |                   | 130        | 7FC000-7FFFFF      | i i               | 258            | FFC000-FFFFFF      |  |

|       |                    | Parameter                          | :          |                   |            | :                  |                   |                |                    |  |

|       |                    | Parameter                          | 16         |                   | 127        | 7F0000-7F3FFF      |                   | 255            | FF0000-FF3FFF      |  |

|       |                    | (Partition 0)                      | 64         |                   | 126        | 7E0000-7EFFFF      |                   | 254            | FE0000-FEFFFF      |  |

|       | Code               | (                                  | :          |                   |            | :                  |                   | :              | :                  |  |

| 1     |                    |                                    | 64         | 8                 | 120        | 780000-78FFFF      | 16                | 240            | F00000-FFFFFF      |  |

| •     | (Top<br>Parameter) | Main Partitions                    | 64         |                   | 119        | 770000-77FFFF      |                   | 239            | EF0000-EFFFFF      |  |

|       |                    | (Partition 1 to 7)                 |            |                   |            | :                  |                   |                | :                  |  |

|       |                    | ,                                  | 64         |                   | 64         | 400000-4FFFFF      | ]                 | 128            | 800000-80FFFF      |  |

|       |                    | Main Partitions<br>(Partition 8 to | 64         |                   | 63         | 3F0000-3FFFFF      |                   | 127            | F70000-F7FFF       |  |

|       |                    |                                    |            |                   |            | :                  |                   |                | ::                 |  |

|       |                    | 15)                                | 64         |                   | 0          | 000000-00FFFF      |                   | 0              | 000000-00FFFF      |  |

|       |                    |                                    | 16         |                   | 130        | 7FC000-7FFFFF      | П                 | 258            | FFC000-FFFFFF      |  |

|       |                    |                                    |            |                   |            | 7                  |                   |                |                    |  |

|       |                    | Single Partition                   | :<br>16    |                   | 127        | :<br>7F0000-7F3FFF | 4                 | 255            | FF0000-FF3FFF      |  |

|       |                    | 4x16 Kword                         | 64         |                   | 126        | 7E0000-7F5FFF      | 4                 | 254            | FE0000-FEFFF       |  |

|       |                    | Parameter                          |            |                   |            | 7 E0000-7 EFFFF    | 4                 |                |                    |  |

|       | Data               | Blocks                             | :<br>64    |                   | 120        | :<br>780000-78FFFF |                   | 240            | F00000-FFFFFF      |  |

| 2     | (Тор               | 127x64 Kword<br>Main Blocks        | 64         | 8                 | 119        | 770000-73FFFF      | 16                | 239            | EF0000-FFFFF       |  |

|       | Parameter)         | (128 Mb)                           | :          |                   |            |                    | 4                 | 200            |                    |  |

|       |                    | 255x64 Kword                       | 64         | Dat               | aShe<br>64 | 400000-4FFFF       | 1                 | 128            | :<br>800000-80FFFF |  |

|       |                    | Main Blocks                        | 64         |                   | 63         | 3F0000-3FFFFF      | 1                 | 127            | F70000-F7FFFF      |  |

|       |                    | (256 Mb)                           | :          |                   | :          | :                  | $\mathbf{H}$      | :              | :                  |  |

|       |                    |                                    | 64         |                   | 0          | :<br>000000-00FFFF | 1                 | 0              | :<br>000000-00FFFF |  |

|       |                    |                                    | ٠.         |                   | _          | 550000 001111      | 11                | Ü              | 330000 001111      |  |

et4U.com

DataShe

DataSheet4U.com

18

www.DataSheet4U.com

Table 6. Code-Code-Data (Top Parameter) SCSP Memory Map and Partitioning

| Flash | Die Stack                  | Partitioning                           | Block<br>Size | Partition<br>Size |       | 128-Mbit Flash     | Partition Size |      | 256-Mbit Flash     |

|-------|----------------------------|----------------------------------------|---------------|-------------------|-------|--------------------|----------------|------|--------------------|

| Die#  | Config.                    | rantioning                             | (KW)          | (Mbit)            | Blk#  | Address Range      | (Mbit)         | Blk# | Address Range      |

|       |                            |                                        | 16            |                   | 130   | 7FC000-7FFFFF      |                | 258  | FFC000-FFFFFF      |

|       |                            |                                        | :             |                   | :     | :                  | 1              | :    | :                  |

|       |                            | Parameter Partition                    | 16            |                   | 127   | 7F0000-7F3FFF      |                | 255  | FF0000-FF3FFF      |

|       |                            | (Partition 0)                          | 64            |                   | 126   | 7E0000-7EFFFF      |                | 254  | FE0000-FEFFFF      |

|       | Cada                       |                                        | ÷             |                   | ÷     | :                  | 1              | :    | ÷                  |

| 1     | Code                       |                                        | 64            | 8                 | 120   | 780000-78FFFF      | 16             | 240  | F00000-FFFFFF      |

| '     | (Top<br>Parameter)         | Main Dautitions                        | 64            | 0                 | 119   | 770000-77FFFF      |                | 239  | EF0000-EFFFFF      |

|       | l didiliotor,              | Main Partitions<br>(Partition 1 to 7)  | :             |                   | :     | :                  |                | :    | :                  |

|       |                            | (raraaari raari)                       | 64            |                   | 64    | 400000-4FFFF       | ]              | 128  | 800000-80FFFF      |

|       |                            | Main Dautitions                        | 64            |                   | 63    | 3F0000-3FFFFF      | ]              | 127  | F70000-F7FFFF      |

|       |                            | Main Partitions<br>(Partition 8 to 15) | ÷             |                   | ÷     | :                  |                | :    | i i                |

|       |                            | (1 attition 6 to 13)                   | 64            |                   | 0     | 000000-00FFFF      |                | 0    | 000000-00FFFF      |

|       |                            |                                        |               |                   | 400   |                    | 11             |      |                    |

|       | Code<br>(Top<br>Parameter) | Parameter Partition                    | 16            |                   | 130   | 7FC000-7FFFFF      |                | 258  | FFC000-FFFFFF      |

|       |                            |                                        | :             |                   | :     | :                  |                | :    | :                  |

|       |                            |                                        | 16            |                   | 127   | 7F0000-7F3FFF      |                | 255  | FF0000-FF3FFF      |

|       |                            | (Partition 0)                          | 64            |                   | 126   | 7E0000-7EFFFF      |                | 254  | FE0000-FEFFFF      |

|       |                            |                                        | :             |                   | :     | :                  |                | :    | :                  |

| 2     |                            |                                        | 64            | 8                 | 120   | 780000-78FFFF      | 16             | 240  | F00000-FFFFF       |

|       |                            | Main Partitions<br>(Partition 1 to 7)  | 64            |                   | 119   | 770000-77FFFF      |                | 239  | EF0000-EFFFFF      |

|       |                            |                                        | :             | DataS             | neet/ | IU.com             |                | :    | :                  |

|       |                            |                                        | 64            |                   | 64    | 400000-4FFFF       |                | 128  | 800000-80FFFF      |

|       |                            | Main Partitions                        | 64            |                   | 63    | 3F0000-3FFFFF      |                | 127  | F70000-F7FFF       |

|       |                            | (Partition 8 to 15)                    | :             |                   | :     | :                  |                | :    | :                  |

|       |                            | <u> </u>                               | 64            |                   | 0     | 000000-00FFFF      |                | 0    | 000000-00FFFF      |

|       |                            |                                        | 64            |                   | 130   | 7F0000-7FFFF       | П              | 258  | FF0000-FFFFFF      |

|       |                            |                                        | :             |                   | :     | :                  | -              | :    | :                  |

|       |                            |                                        | 64            |                   | 67    | :<br>400000-40FFFF |                | 131  | :<br>800000-80FFFF |

|       |                            | Single Partition                       | 64            |                   | 66    | 3F0000-3FFFFF      |                | 130  | 7F0000-7FFFF       |

|       |                            | 4x16 Kword                             | :             |                   | :     | :                  | -              | :    | :                  |

|       | Data                       | Parameter Blocks                       | 64            |                   | 11    | :<br>080000-08FFFF |                | 19   | :<br>100000-10FFFF |

| 3     | (Bottom                    | 127x64 Kword Main                      | 64            | 128               | 10    | 070000-03FFFF      | 256            | 18   | 0F0000-161111      |

|       | Parameter)                 | Blocks (128 Mb)                        | :             |                   | :     | :                  | -              | :    | :                  |

|       |                            | 255x64 Kword Main                      | 64            |                   | 4     | :<br>010000-01FFFF |                | 4    | :<br>010000-01FFFF |

|       |                            | Blocks (256 Mb)                        | 16            |                   | 3     | 00C000-00FFFF      |                | 3    | 00C000-00FFFF      |

|       |                            |                                        | :             |                   | :     | :                  |                | :    | :                  |

|       |                            |                                        | 16            |                   | 0     | 000000-003FFF      | <del> </del>   | 0    | :<br>000000-003FFF |

|       |                            |                                        | . •           | <u> </u>          | ,     | 2000000011         | П              | ,    | 200000 000111      |

*Note:* Other stacked memory combinations and parameter configurations can be created based on the memory map and partitions highlighted from Table 3 to Table 7.

DataSheet4U.com www.DataSheet4U.com

Datasheet 19

DataSheet4U.com

DataSheet4U.com

et4U.com

DataShe

Table 7. Code-Code-Data (Bottom Parameter) SCSP Memory Map and Partitioning

| Flash | Die Stack          | Partitioning                           | Block<br>Size | Partition<br>Size |                 | 128-Mbit Flash     | Partition<br>Size |         | 256-Mbit Flash     |

|-------|--------------------|----------------------------------------|---------------|-------------------|-----------------|--------------------|-------------------|---------|--------------------|

| Die#  | Config.            | Partitioning                           | (KW)          | (Mbit)            | Blk#            | Address Range      | (Mbit)            | Blk#    | Address Range      |

|       |                    |                                        | 16            |                   | 130             | 7FC000-7FFFFF      |                   | 258     | FFC000-FFFFFF      |

|       |                    |                                        | :             |                   | :               | :                  |                   | :       | :                  |

|       |                    |                                        | 16            |                   | 127             | 7F0000-7F3FFF      |                   | 255     | FF0000-FF3FFF      |

|       |                    | Single Partition                       | 64            |                   | 126             | 7E0000-7EFFFF      |                   | 254     | FE0000-FEFFFF      |

|       | Data               | 4x16 Kword Parameter Blocks            | :             |                   | :               | :                  |                   | :       | :                  |

| 3     |                    |                                        | 64            | 8                 | 120             | 780000-78FFFF      | 16                | 240     | F00000-FFFFFF      |

| J 3   | (Top<br>Parameter) | 127x64 Kword Main<br>Blocks (128 Mb)   | 64            | 0                 | 119             | 770000-77FFFF      | 10                | 239     | EF0000-EFFFFF      |

|       | · urumotor,        | 255x64 Kword Main                      | :             |                   | :               | :                  |                   | :       | :                  |

|       |                    | Blocks (256 Mb)                        | 64            |                   | 64              | 400000-4FFFF       |                   | 128     | 800000-80FFFF      |

|       |                    |                                        | 64            |                   | 63              | 3F0000-3FFFFF      |                   | 127     | F70000-F7FFFF      |

|       |                    |                                        | :             |                   | :               | :                  |                   | ÷       | :                  |

|       |                    |                                        | 64            |                   | 0               | 000000-00FFFF      |                   | 0       | 000000-00FFFF      |

|       |                    |                                        | 64            |                   | 130             | 7F0000-7FFFF       | T                 | 258     | FF0000-FFFFF       |

|       |                    | Main Partitions<br>(Partition 8 to 15) |               |                   |                 |                    |                   |         |                    |

|       |                    |                                        | :<br>64       |                   | .:<br>67        | :<br>400000-40FFFF |                   | 131     | :<br>800000-80FFFF |

|       |                    |                                        | 64            |                   | 66              | 3F0000-3FFFF       |                   | 130     | 7F0000-7FFFFF      |

|       |                    | Main Partitions                        |               |                   |                 | 350000-35555       |                   |         | 7F0000-7FFFF       |

|       | Code               | (Partition 1 to 7)                     | 64            |                   | 11              | :<br>080000-08FFFF |                   | :<br>19 | :<br>100000-10FFFF |

| 2     | (Bottom            |                                        | 64            |                   | 10              | 070000-07FFFF      |                   | 18      | 0F0000-10FFFF      |

|       | Parameter)         | Parameter Partition<br>(Partition 0)   |               |                   |                 |                    |                   |         |                    |

|       |                    |                                        | 64            | DataS             | ne <b>z</b> etz | 010000-01FFFF      |                   | :<br>4  | :<br>010000-01FFFF |

|       |                    |                                        | 16            |                   | 3               | 00C000-00FFFF      |                   | 3       | 00C000-00FFFF      |

|       |                    | (i dittion o)                          |               |                   |                 |                    |                   | :       |                    |

|       |                    |                                        | :<br>16       |                   | : 0             | :<br>000000-003FFF |                   | 0       | :<br>000000-003FFF |

|       |                    |                                        | 10            |                   | U               | 000000-003111      |                   |         | 000000-003111      |

|       |                    | Main Dertitions                        | 64            |                   | 130             | 7F0000-7FFFF       |                   | 258     | FF0000-FFFFFF      |

|       |                    | Main Partitions (Partition 8 to 15)    | :             |                   | :               | :                  |                   | :       | :                  |

|       |                    | (i didion o to ro)                     | 64            |                   | 67              | 400000-40FFFF      |                   | 131     | 800000-80FFFF      |

|       |                    | Main Dantitions                        | 64            |                   | 66              | 3F0000-3FFFFF      |                   | 130     | 7F0000-7FFFFF      |

|       | 0 - 4 -            | Main Partitions<br>(Partition 1 to 7)  | :             |                   | :               | :                  |                   | :       | :                  |

| 1     | Code               | (. αιααστι το τ)                       | 64            |                   | 11              | 080000-08FFFF      |                   | 19      | 100000-10FFFF      |

| '     | (Bottom Parameter) |                                        | 64            |                   | 10              | 070000-07FFFF      |                   | 18      | 0F0000-0FFFFF      |

|       | raiameter)         |                                        | ÷             |                   | :               |                    |                   | :       | :                  |

|       |                    | Parameter Partition                    | 64            |                   | 4               | 010000-01FFFF      |                   | 4       | 010000-01FFFF      |

|       |                    | (Partition 0)                          | 16            |                   | 3               | 00C000-00FFFF      |                   | 3       | 00C000-00FFFF      |

|       |                    |                                        | ÷             |                   | ÷               | :                  |                   | ÷       | <u> </u>           |

|       |                    |                                        | 16            |                   | 0               | 000000-003FFF      |                   | 0       | 000000-003FFF      |

Note: Other stacked memory combinations and parameter configurations can be created based on the memory map and partitions highlighted from Table 3 to Table 7.

DataSheet4U.com

20

et4U.com

**Datasheet**

DataSheet4U.com

www.DataSheet4U.com

DataShe

# **Package Information**

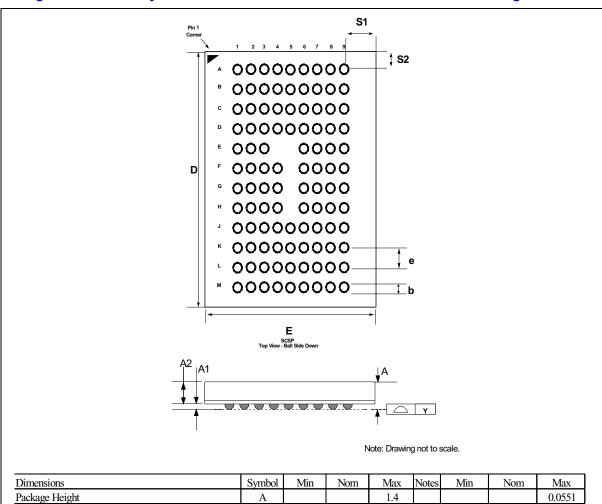

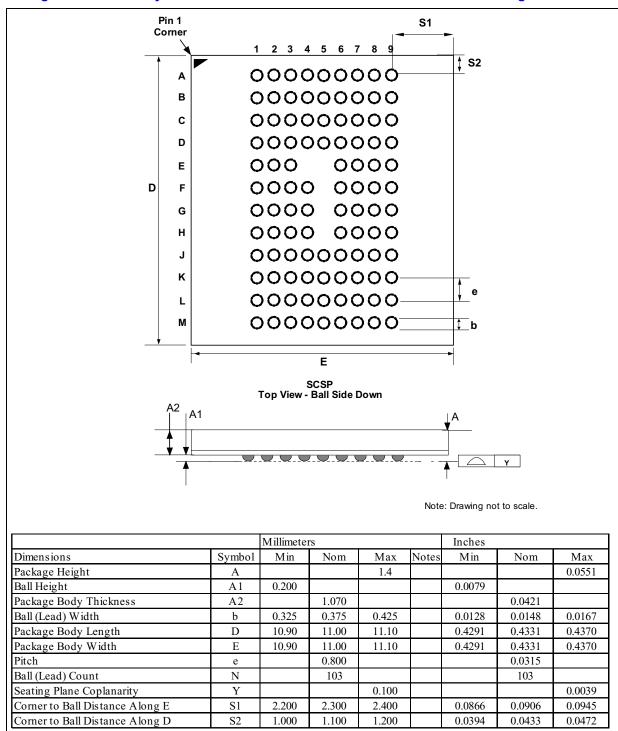

LVX family with LPSDRAM device is available in the following standard SCSP x 16D Performance ballout packages:

- Figure 4, "LVX Family with LPSDRAM Device SCSP x16D Performance Drawing 9x11x1.4 mm" on page 21

- Figure 5, "LVX Family with LPSDRAM Device SCSP x16D Performance Drawing 11x11x1.4 mm" on page 22

Figure 4. LVX Family with LPSDRAM Device SCSP x16D Performance Drawing 9x11x1.4 mm

| Dimensions                      | Symbol | Min   | Nom   | Max   | Notes | Min    | Nom    | Max    |

|---------------------------------|--------|-------|-------|-------|-------|--------|--------|--------|

| Package Height                  | A      |       |       | 1.4   |       |        |        | 0.0551 |

| Ball Height                     | A1     | 0.200 |       |       |       | 0.0079 |        |        |

| Package Body Thickness          | A2     |       | 1.070 |       |       |        | 0.0421 |        |

| Ball (Lead) Width               | b      | 0.325 | 0.375 | 0.425 |       | 0.0128 | 0.0148 | 0.0167 |

| Package Body Length             | D      | 10.90 | 11.00 | 11.10 |       | 0.4291 | 0.4331 | 0.4370 |

| Package Body Width              | Е      | 8.90  | 9.00  | 9.10  |       | 0.3504 | 0.3543 | 0.3583 |

| Pitch                           | e      |       | 0.800 |       |       |        | 0.0315 |        |

| Ball (Lead) Count               | N      |       | 103   |       |       |        | 103    |        |

| Seating Plane Coplanarity       | Y      |       |       | 0.100 |       |        |        | 0.0039 |

| Corner to Ball Distance Along E | S1     | 1.200 | 1.300 | 1.400 |       | 0.0472 | 0.0512 | 0.0551 |

| Corner to Ball Distance Along D | S2     | 1.000 | 1.100 | 1.200 |       | 0.0394 | 0.0433 | 0.0472 |

DataSheet4U.com www.DataSheet4U.com

Datasheet 21

DataSheet4U.com

et4U.com

Dataone

Figure 5. LVX Family with LPSDRAM Device SCSP x16D Performance Drawing 11x11x1.4 mm

et4U.com

DataSheet4U.com

DataSheet4U.com

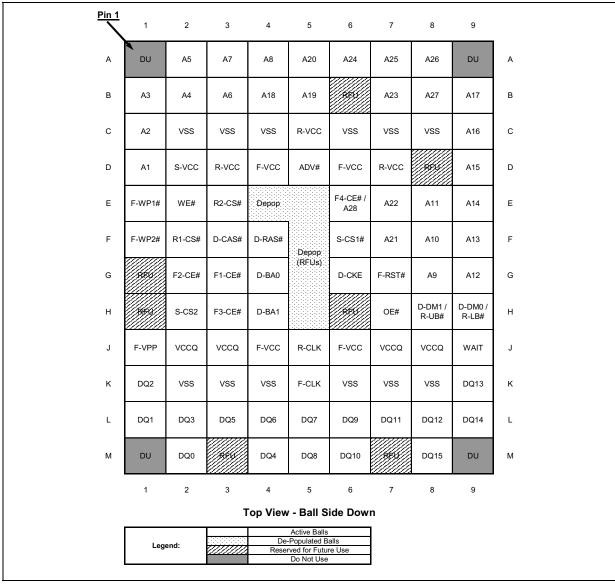

#### 4.0 **Ballout and Signal Descriptions**

#### **Signal Ballout** 4.1

Intel StrataFlash® Wireless Memory System family is available in a x16D Performance ballout, shown in Figure 6, "x16D (103 Ball) Performance Signal Ballout for LVX Device Family" The single package ballout is ideal for space-constrained board applications where density upgrades without PCB redesign is preferred. The user must adapt for density upgrade flexibility in the PCB design.

Figure 6. x16D (103 Ball) Performance Signal Ballout for LVX Device Family

et4U.com

www.DataSheet4U.com DataSheet4U.com

# 4.2 Signal Descriptions

Table 8 describes the active signals used on the LVX family with LPSDRAM device.

Table 8. Signal Descriptions (Sheet 1 of 3)