# LIN J2602 Transceiver

#### **Features**

- The MCP2003 and MCP2004 are compliant with LIN Bus Specifications 1.3, 2.0 and 2.1 and are compliant to SAE J2602

- Support Baud Rates up to 20 Kbaud with LIN-compatible output driver

- · 43V load dump protected

- Very low EMI meets stringent OEM requirements

- · Very high ESD immunity:

- >20kV on VBB (IEC 61000-4-2)

- >14kV on LBUS (IEC 61000-4-2)

- Very high immunity to RF disturbances meets stringent OEM requirements

- Wide supply voltage, 6.0V-27.0V continuous

- Extended Temperature Range: -40 to +125°C

- Interface to PIC<sup>®</sup> MCU EUSART and standard USARTs

- · Local Interconnect Network (LIN) bus pin:

- Internal pull-up resistor and diode

- Protected against battery shorts

- Protected against loss of ground

- High current drive

- · Automatic thermal shutdown

- Low-power mode:

- Receiver monitoring bus and transmitter off,  $(\cong 5 \mu A)$

## **Description**

This device provides a bidirectional, half-duplex communication physical interface to automotive and industrial LIN systems to meet the LIN bus specification Revision 2.1 and SAE J2602. The device is short circuit and overtemperature protected by internal circuitry. The device has been specifically designed to operate in the automotive operating environment and will survive all specified transient conditions while meeting all of the stringent quiescent current requirements.

MCP200X family members:

- 8-pin PDIP, DFN and SOIC packages:

- MCP2003, LIN-compatible driver, with WAKE pins

- MCP2004, LIN-compatible driver, with FAULT/TXE pins

# **Package Types**

| MCP2<br>PDIP, S         |                               | MCP2004<br>PDIP, SOIC                        |                           |  |  |

|-------------------------|-------------------------------|----------------------------------------------|---------------------------|--|--|

| RXD 1 CS 2 WAKE 3 TXD 4 | 8 VREN 7 VBB 6 LBUS FAU 5 VSS | RXD 1<br>CS 2<br>JLT/TXE 3<br>TXD 4          | 8 VREN 7 VBB 6 LBUS 5 VSS |  |  |

| MCP2<br>4x4 D           |                               | <b>MCP2004</b><br>4x4 DFN*                   |                           |  |  |

| WAKE 3 9                | VBB 6 LBUS FAU                | CS 2 EF  JIT/TXE 3 9  TxD 4 Pad (EP); see Ta | 7 VBB<br>6 LBUS<br>VSS    |  |  |

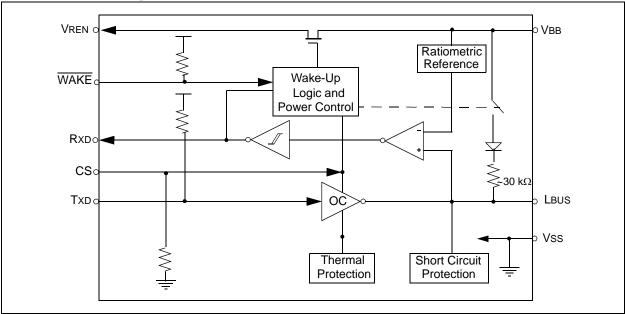

# MCP2003 Block Diagram

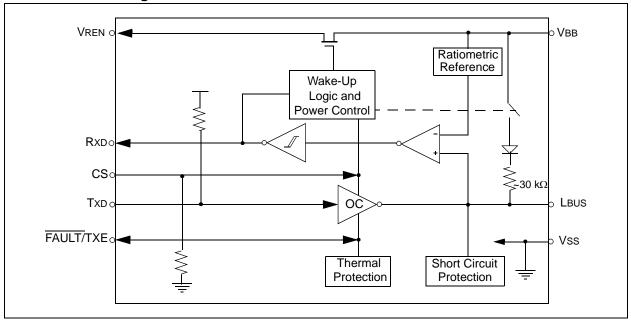

# MCP2004 Block Diagram

#### 1.0 DEVICE OVERVIEW

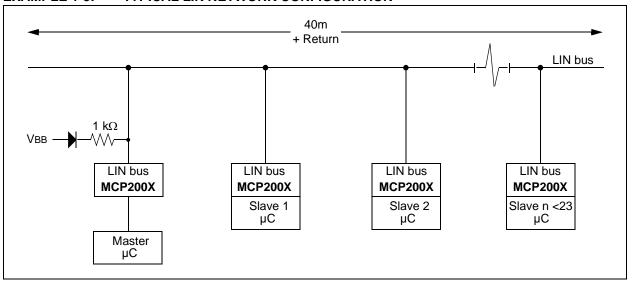

The MCP2003/4 provides a physical interface between a microcontroller and a LIN bus. This device will translate the CMOS/TTL logic levels to LIN logic level, and vice versa. It is intended for automotive and industrial applications with serial bus speeds up to 20 Kbaud.

LIN specification 2.1 requires that the transceiver of all nodes in the system is connected via the LIN pin, referenced to ground and with a maximum external termination resistance of  $510\Omega$  from LIN bus to battery supply. The  $510\Omega$  corresponds to 1 master and 15 slave nodes.

The VREN pin can be used to drive the logic input of an external voltage regulator. This pin is high in all modes except for Power-Down mode.

#### 1.1 External Protection

#### 1.1.1 REVERSE BATTERY PROTECTION

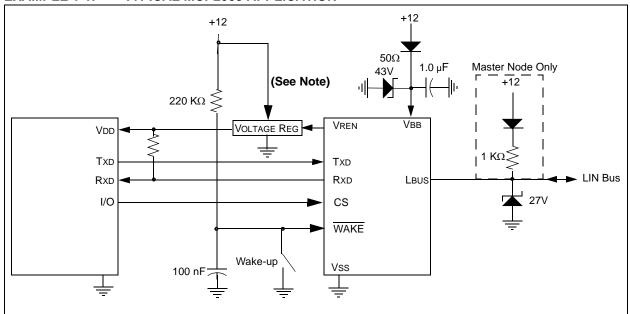

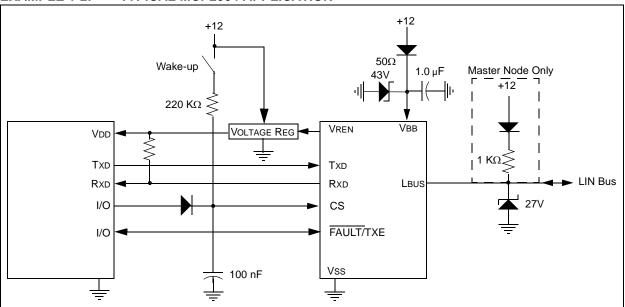

An external reverse-battery-blocking diode should be used to provide polarity protection (see Example 1-1).

# 1.1.2 TRANSIENT VOLTAGE PROTECTION (LOAD DUMP)

An external 43V transient suppressor (TVS) diode, between VBB and ground, with a  $50\Omega$  transient protection resistor (RTP) in series with the battery supply and the VBB pin serve to protect the device from power transients (see Example 1-1) and ESD events. While this protection is optional, it is considered good engineering practice.

## 1.2 Internal Protection

# 1.2.1 ESD PROTECTION

For component-level ESD ratings, please refer to the maximum operation specifications.

# 1.2.2 GROUND LOSS PROTECTION

The LIN Bus specification states that the LIN pin must transition to the recessive state when ground is disconnected. Therefore, a loss of ground effectively forces the LIN line to a high-impedance level.

#### 1.2.3 THERMAL PROTECTION

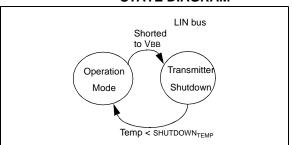

The thermal protection circuit monitors the die temperature and is able to shut down the LIN transmitter.

There are two causes for a thermal overload. A thermal shut down can be triggered by either, or both, of the following thermal overload conditions.

- · LIN bus output overload

- Increase in die temperature due to increase in environment temperature

Driving the TxD and checking the RxD pin makes it possible to determine whether there is a bus contention (Rx = low, Tx = high) or a thermal overload condition (Rx = high, Tx = low). After a thermal overload event, the device will automatically recover once the die temperature has fallen below the recovery temperature threshold. See Figure 1-1.

FIGURE 1-1: THERMAL SHUTDOWN STATE DIAGRAM

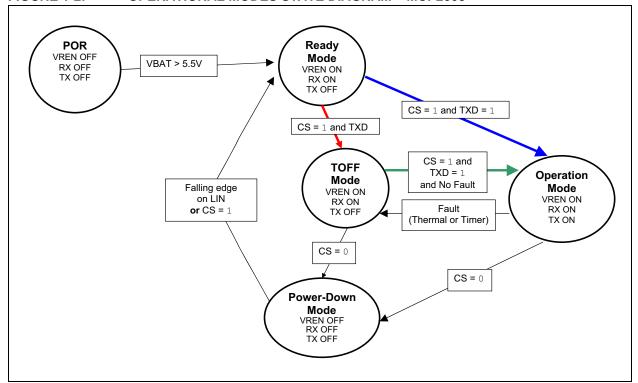

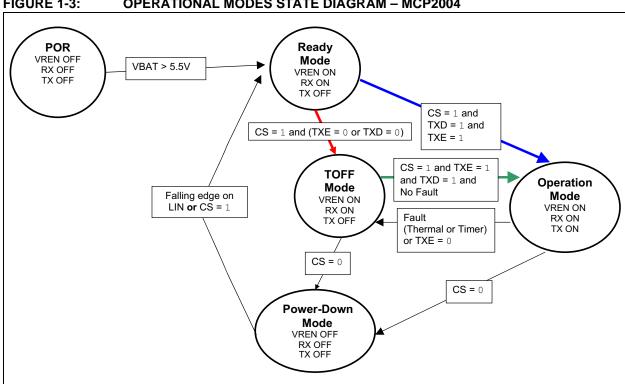

## 1.3 Modes of Operation

For an overview of all operational modes, refer to Table 1-1.

#### 1.3.1 POWER-DOWN MODE

In Power-Down mode, the transmitter and VREN are both off. Only the receiver section and the wake-up circuits are operational. This is the lowest power mode.

On bus activity (e.g. a BREAK character), CS going to a high level, or on a falling edge on WAKE, the device will immediately enter Ready mode. If CS is held high as the device transitions from Power-Down to Ready mode, the device will transition to Operation mode as soon as internal voltages stabilize.

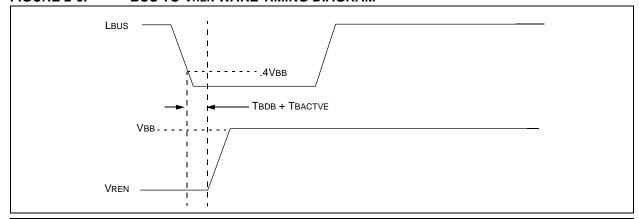

Note: Bus activity is defined as LBUS dropping below VIL(LBUS) for longer than the Bus Activity Debounce time (tBDB)

#### 1.3.2 READY MODE

Upon entering the Ready mode, VREN is enabled and the receiver detect circuit is powered up. The transmitter remains disabled and the device is ready to receive data but not to transmit.

Upon VBB supply pin power-on, the device will remain in Ready mode as long as CS is low. If CS transitions high, the device will enter Operation mode. However, if the TXD pin is held low when CS goes high, the device will transition to Transmitter Off mode instead of Operation mode.

#### 1.3.3 OPERATION MODE

In this mode, all internal modules are operational.

The MCP2003/4 will go into the Power-Down mode on the falling edge of CS. The MCP2003/4 will enter Transmitter Off mode in the event of a Fault condition. These include: thermal overload, bus contention and TXD timer expiration.

The MCP2004 device can also enter Transmitter Off mode if the  $\overline{\text{FAULT}/\text{TXE}}$  pin is pulled low

#### 1.3.4 TRANSMITTER OFF MODE

Transmitter Off mode is reached whenever the transmitter is disabled either due to a Fault condition or pulling the nFAULT/TXE pin low on the MCP2004. The fault conditions include: thermal overload, bus contention or TXD timer expiration.

The MCP2003/4 will go into Power-Down mode on falling edge of CS, or return to Operation mode if all faults are resolved and the FAULT/TXE pin on the MCP2004 is high.

FIGURE 1-3: **OPERATIONAL MODES STATE DIAGRAM - MCP2004**

While the MCP2003/4 is in thermal shutdown, TXD should not be actively driven high or it may power Note: internal logic through the ESD diodes and may damage the device.

**TABLE 1-1: OVERVIEW OF OPERATIONAL MODES**

| State           | Transmitter | Receiver           | Vren | Operation                                                                           | Comments                                  |

|-----------------|-------------|--------------------|------|-------------------------------------------------------------------------------------|-------------------------------------------|

| POR             | OFF         | OFF                | OFF  | Read CS, if low, then Ready; if high, Operational mode                              |                                           |

| Ready           | OFF         | ON                 | ON   | If CS high level, then Operation mode                                               | Bus Off state                             |

| Operation       | ON          | NO                 | ON   | If CS low level, then Power Down; If FAULT/TXE low level, then Transmitter Off mode | Normal Operation mode                     |

| Power Down      | OFF         | Activity<br>Detect | OFF  | On LIN bus falling, go to Ready mode. On CS high level, go to Operation mode        | Low Power mode                            |

| Transmitter Off | OFF         | ON                 | ON   | If CS low level, then Power Down; If FAULT/TXE and TXD high, then Operation mode    | FAULT/TXE only<br>available on<br>MCP2004 |

# 1.4 Typical Applications

# **EXAMPLE 1-1: TYPICAL MCP2003 APPLICATION**

**Note:** For applications with current requirements of less than 20 mA, the connection to +12V can be deleted, and voltage to the regulator supplied directly from the VREN pin.

# **EXAMPLE 1-2: TYPICAL MCP2004 APPLICATION**

# **EXAMPLE 1-3: TYPICAL LIN NETWORK CONFIGURATION**

## 1.5 Pin Descriptions

TABLE 1-1: PINOUT DESCRIPTIONS

|                                                    | 8-Pin 8-Pin   |     | MCP2003                                                            | MCP2004                                                            |  |

|----------------------------------------------------|---------------|-----|--------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Pin Name                                           | PDIP,<br>SOIC | DFN | Normal Operation                                                   | Normal Operation                                                   |  |

| RxD                                                | 1             | 1   | Receive Data Output (OD)                                           | Receive Data Output (OD)                                           |  |

| CS                                                 | 2             | 2   | Chip Select (TTL)                                                  | Chip Select/Local WAKE (TTL)                                       |  |

| WAKE (MCP2003 only)<br>FAULT/TXE (MCP2004<br>only) | 3             | 3   | Wake up, HV tolerant                                               | Fault Detect Output (OD) Transmitter Enable (TTL)                  |  |

| TXD                                                | 4             | 4   | Transmit Data Input (TTL)                                          | Transmit Data Input (TTL)                                          |  |

| Vss                                                | 5             | 5   | Ground                                                             | Ground                                                             |  |

| LBUS                                               | 6             | 6   | LIN bus (bidirectional)                                            | LIN bus (bidirectional)                                            |  |

| VBB                                                | 7             | 7   | Battery positive                                                   | Battery positive                                                   |  |

| VREN                                               | 8             | 8   | Voltage Regulator Enable Output                                    | Voltage Regulator Enable Output                                    |  |

| EP                                                 |               | 9   | Exposed Thermal Pad. Do not electrically connect or connect to Vss | Exposed Thermal Pad. Do not electrically connect or connect to Vss |  |

**Legend:** TTL = TTL Input Buffer; OD = Open-Drain Output

#### 1.5.1 RECEIVE DATA OUTPUT (RXD)

The Receive Data Output pin is a open drain (OD) output and follows the state of the LIN pin.

## 1.5.2 CS (CHIP SELECT)

Chip Select Input pin. An internal pull-down resistor will keep the CS pin low. This is done to ensure that no disruptive data will be present on the bus while the microcontroller is executing a Power-on Reset and an I/O initialization sequence. The pin must detect a high level to activate the transmitter.

If CS = 0 when the VBB supply is turned on, the device stays in Ready mode. In Ready mode, the receiver is on and the LIN transmitter driver is off.

If CS = 1 when the VBB supply is turned on, the device will proceed to the Operation mode as soon as internal voltages stabilize.

This pin may also be used as a local wake-up input (Refer to Example 1-1). In this implementation, the microcontroller I/O controlling the CS should be converted to a high-impedance input allowing the internal pull-down resistor will keep CS low. An external switch, or other source, can then wake-up both the transceiver and the microcontroller (if powered).

Note:

It is not recommended to tie CS high as this can result the MCP2003/4 entering Operation mode before the microcontroller is initialized and may result in unintentional LIN traffic.

# 1.5.3 WAKE UP INPUT (WAKE)

This pin is only available on the MCP2003.

The WAKE pin has an internal 800K pull up to VBB. A falling edge on the WAKE pin causes the device to wake from Power-Down mode. Upon waking, the MCP2003 will enter Ready mode

## 1.5.4 FAULT/TXE

This pin is only available on the MCP2004. This pin is bidirectional and allows disabling of the transmitter, as well as fault reporting related to disabling the transmitter. This pin is an open-drain output with states as defined in Table 1-2. The transmitter is disabled whenever this pin is low ('0'), either from an internal Fault condition or by an external drive. While the transmitter is disabled, the internal 30 k $\Omega$  pull-up resistor on the LBUS pin is also disconnected to reduce current.

Note:

The FAULT/TXE pin is true ('0') whenever the internal circuits have detected a short or thermal excursion and have disabled the LBUS output driver.

TABLE 1-2: FAULT/TXE TRUTH TABLE

| Txp | RXD LINBUS Thermal |     | LINBUS Thermal                        |   |   |                                                                                    |

|-----|--------------------|-----|---------------------------------------|---|---|------------------------------------------------------------------------------------|

| In  | Out                | I/O | Override External Driven Input Output |   |   | Definition                                                                         |

| L   | Н                  | Vвв | OFF                                   | Н | L | FAULT, TXD driven low, LINBUS shorted to VBB (Note 1)                              |

| Н   | Н                  | VBB | OFF                                   | Н | Н | OK                                                                                 |

| L   | L                  | GND | OFF                                   | Н | Н | OK                                                                                 |

| Н   | L                  | GND | OFF                                   | Н | Н | OK, data is being received from the LINBUS                                         |

| Х   | х                  | VBB | ON                                    | Н | L | FAULT, Transceiver in thermal shutdown                                             |

| Х   | Х                  | Vвв | Х                                     | L | Х | NO FAULT, the CPU is commanding the transceiver to turn off the transmitter driver |

**Legend:** x = don't care

**Note 1:** The FAULT/TXE is valid after approximately 25 μs after TXD falling edge. This is to eliminate false fault reporting during bus propagation delays.

# 1.5.5 TRANSMIT DATA INPUT (TXD)

The Transmit Data Input pin has an internal pull-up. The LIN pin is low (dominant) when TXD is low, and high (recessive) when TXD is high.

For extra bus security, TXD is internally forced to '1' whenever the transmitter is disabled regardless of external TXD voltage.

#### 1.5.5.1 Txp Dominant Timeout

If TXD is driven low longer than approximately 10ms, the LBUS pin is switched to recessive mode and the part enters TOFF Mode. This is to prevent the LIN node from permanently driving the LIN Bus dominant. The transmitter is re-enabled on TXD rising edge.

## 1.5.6 GROUND (Vss)

This is the Ground pin.

#### 1.5.7 LIN BUS (LBUS)

The bidirectional LIN Bus pin (LBUS) is controlled by the TXD input. LBUS has a current limited open collector output. To reduce EMI, the edges during the signal changes are slope controlled and include corner rounding control for both falling and rising edges.

The internal LIN receiver observes the activities on the LIN bus, and matches the output signal RXD to follow the state of the LBUS pin.

#### 1.5.7.1 Bus Dominant Timer

The Bus Dominant Timer is an internal timer that deactivates the LBUS transmitter after approximately 25 milliseconds of dominant state on the LBUS pin. The timer is reset on any recessive LBUS state.

The LIN bus transmitter will be re-enabled after a recessive state on the LBUS pin as long as CS is high. Disabling can be caused by the LIN bus being externally held dominant, or by TXD being driven low. Additionally, on the MCP2004, the FAULT pin will be driven low to indicate the Transmitter Off state.

#### 1.5.8 BATTERY (VBB)

This is the Battery Positive Supply Voltage pin.

# 1.5.9 VOLTAGE REGULATOR ENABLE OUTPUT (VREN)

This is the External Voltage Regulator Enable pin. Open source output is pulled high to VBB in all modes, except Power Down.

## 1.5.10 EXPOSED THERMAL PAD (EP)

Do not electrically connect, or connect to Vss.

**NOTES:**

## 2.0 ELECTRICAL CHARACTERISTICS

# 2.1 Absolute Maximum Ratings†

| VIN DC Voltage on RxD, TxD, FAULT/TXE                           | 0.3 to +30\   |

|-----------------------------------------------------------------|---------------|

| VIN DC Voltage on CS, WAKE and VREN                             | 0.3 to +30\   |

| VBB Battery Voltage, continuous, non-operating (Note 1)         | 0.3 to +40\   |

| VBB Battery Voltage, non-operating (LIN bus recessive) (Note 2) | 0.3 to +43\   |

| VBB Battery Voltage, transient ISO 7637 Test 1                  | 200V          |

| VBB Battery Voltage, transient ISO 7637 Test 2a                 | +150V         |

| VBB Battery Voltage, transient ISO 7637 Test 3a                 | 300V          |

| VBB Battery Voltage, transient ISO 7637 Test 3b                 | +200V         |

| VLBUS Bus Voltage, continuous                                   | 18 to +30\    |

| VLBUS Bus Voltage, transient (Note 3)                           | 27 to +43\    |

| ILBUS Bus Short Circuit Current Limit                           | 200 mA        |

| ESD protection on LIN, VBB, WAKE (IEC 61000-4-2) (Note 4)       | ±8 K\         |

| ESD protection on LIN, VBB (Human Body Model) (Note 5)          | ±8 K\         |

| ESD protection on all other pins (Human Body Model) (Note 5)    | ±4 KV         |

| ESD protection on all pins (Charge Device Model) (Note 6)       | ±2 KV         |

| ESD protection on all pins (Machine Model) (Note 7)             | ±200\         |

| Maximum Junction Temperature                                    | 150°C         |

| Storage Temperature                                             | -65 to +150°C |

- Note 1: LIN 2.x compliant specification.

- 2: SAE J2602 compliant specification.

- **3:** ISO 7637/1 load dump compliant (t < 500 ms).

- **4:** According to IEC 61000-4-2, 330 ohm, 150 pF and Tranceiver EMC Test Specifications [2] to [4]. For WAKE pin to meet the specification, series resistor must be in place (refer to Example 1-2).

- 5: According to AEC-Q100-002 / JESD22-A114.

- 6: According to AEC-Q100-011B.

- **7:** According to AEC-Q100-003 / JESD22-A115.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 2.2 Nomenclature used in this document

Some terms and names used in this data sheet deviate from those referred to in the LIN specifications. Equivalent values are shown below.

| LIN 2.1 Name         | Term used in the following tables | Definition                   |

|----------------------|-----------------------------------|------------------------------|

| $V_{BAT}$            | not used                          | ECU operating voltage        |

| V <sub>SUP</sub>     | VBB                               | Supply voltage at device pin |

| I <sub>BUS_LIM</sub> | Isc                               | Current Limit of Driver      |

| V <sub>BUSREC</sub>  | VIH(LBUS)                         | Recessive state              |

| V <sub>BUSDOM</sub>  | VIL(LBUS)                         | Dominant state               |

# 2.3 DC Specifications

| DC Specifications                         | Electrical Characteristics: Unless otherwise indicated, all limits are specified for: VBB = 6.0V to 27.0V TA = -40°C to +125°C |            |      |         |       |                                                    |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|-------|----------------------------------------------------|--|

| Parameter                                 | Sym                                                                                                                            | Min.       | Тур. | Max.    | Units | Conditions                                         |  |

| Power                                     |                                                                                                                                |            |      |         |       |                                                    |  |

| VBB Quiescent Operating Current           | IBBQ                                                                                                                           |            | 90   | 150     | μА    | Operating Mode,<br>bus recessive ( <b>Note 1</b> ) |  |

| VBB Transmitter-off Current               | Іввто                                                                                                                          | _          | 75   | 120     | μA    | Transmitter off, bus recessive ( <b>Note 1</b> )   |  |

| VBB Power Down Current                    | IBBPD                                                                                                                          | 1          | 5    | 15      | μA    | Transmitter off, bus recessive ( <b>Note 1</b> )   |  |

| VBB Current with Vss Floating             | IBBNOGND                                                                                                                       | -1         | -    | 1       | mA    | VBB = 12V, GND to VBB,<br>VLIN = 0-27V             |  |

| Microcontroller Interface                 |                                                                                                                                |            |      |         |       |                                                    |  |

| High Level Input Voltage (TxD, FAULT/TXE) | VIH                                                                                                                            | 2.0        | _    | 5.3     | V     |                                                    |  |

| Low Level Input Voltage (TxD, FAULT/TXE)  | VIL                                                                                                                            | -0.3       | _    | 0.8     | V     |                                                    |  |

| High Level Input Current (TXD, FAULT/TXE) | Іін                                                                                                                            | -2.5       | _    | _       | μA    | Input voltage = 4.0V                               |  |

| Low Level Input Current (TXD, FAULT/TXE)  | IIL                                                                                                                            | -10        | -    | 1       | μA    | Input voltage = 0.5V                               |  |

| High Level Voltage (VREN)                 | VHVREN                                                                                                                         | -0.3       | 1    | VBB+0.3 |       |                                                    |  |

| High Level Output Current (VREN)          | IHVREN                                                                                                                         | -20        | _    | -10     | mA    | Output voltage = VBB-<br>0.5V                      |  |

| High Level Input Voltage (CS)             | VIH                                                                                                                            | 2.0        | _    | VBB     | V     | Through a current limiting resistor                |  |

| Low Level Input Voltage (CS)              | VIL                                                                                                                            | -0.3       | _    | 0.8     | V     |                                                    |  |

| High Level Input Current (CS)             | Іін                                                                                                                            | -10.0      | _    | 10.0    | μA    | Input voltage = 4.0V                               |  |

| Low Level Input Current (CS)              | II∟                                                                                                                            | -5.0       | _    | 5.0     | μA    | Input voltage = 0.5V                               |  |

| Low Level Input Voltage (WAKE)            | VIL                                                                                                                            | VBB - 4.0V | _    | _       | V     |                                                    |  |

| Low Level Output Voltage (RxD)            | VOL                                                                                                                            | _          | _    | 0.4     | V     | IIN = 2 mA                                         |  |

| High Level Output Current (RXD)           | Іон                                                                                                                            | -1         | _    | -1      | μA    | VLIN - VBB, VRXD = 5.5V                            |  |

**Note 1:** Internal current limited. 2.0 ms maximum recovery time (RLBUS =  $0\Omega$ , TX = 0.4 VREG, VLBUS = VBB).

<sup>2:</sup> Node has to sustain the current that can flow under this condition; bus must be operational under this condition.

# 2.3 DC Specifications (Continued)

| DC Specifications                                                  | Electrical Characteristics: Unless otherwise indicated, all limits are specified for: VBB = 6.0V to 27.0V TA = -40°C to +125°C |           |            |           |       |                                                                |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----------|-------|----------------------------------------------------------------|--|

| Parameter                                                          | Sym                                                                                                                            | Min.      | Тур.       | Max.      | Units | Conditions                                                     |  |

| Bus Interface                                                      |                                                                                                                                |           |            |           |       |                                                                |  |

| High Level Input Voltage                                           | VIH(LBUS)                                                                                                                      | 0.6 VBB   | 1          | 1         | V     | Recessive state                                                |  |

| Low Level Input Voltage                                            | VIL(LBUS)                                                                                                                      | -8        |            | 0.4 Vвв   | V     | Dominant state                                                 |  |

| Input Hysteresis                                                   | VHYS                                                                                                                           |           |            | 0.175 VBB | V     | VIH(LBUS) - VIL(LBUS)                                          |  |

| Low Level Output Current                                           | IOL(LBUS)                                                                                                                      | 40        | l          | 200       | mA    | Output voltage = 0.1 VBB,<br>VBB = 12V                         |  |

| Pull-up Current on Input                                           | IPU(LBUS)                                                                                                                      | 5         | l          | 180       | μA    | ~30 kΩ internal pull-up @ VIH (LBUS) = 0.7 VBB                 |  |

| Short Circuit Current Limit                                        | Isc                                                                                                                            | 50        | 1          | 200       | mA    | (Note 1)                                                       |  |

| High Level Output Voltage                                          | Voh(LBUS)                                                                                                                      | 0.9 VBB   | 1          | VBB       | V     |                                                                |  |

| Driver Dominant Voltage                                            | V_LOSUP                                                                                                                        |           | 1          | 1.2       | V     | VBB = 7V, RLOAD = $500\Omega$                                  |  |

| Driver Dominant Voltage                                            | V_HISUP                                                                                                                        | _         | _          | 2.0       | V     | VBB = 18V, RLOAD = $500\Omega$                                 |  |

| Driver Dominant Voltage                                            | V_LOSUP-1K                                                                                                                     | 0.6       | _          | _         | V     | VBB = 7V, RLOAD = 1 k $\Omega$                                 |  |

| Driver Dominant Voltage                                            | V_HISUP-1K                                                                                                                     | 0.8       | _          | _         | V     | VBB = 18V, RLOAD = 1 k $\Omega$                                |  |

| Input Leakage Current (at the receiver during dominant bus level)  | IBUS_PAS_DOM                                                                                                                   | -1        | -0.4       | _         | mA    | Driver off,<br>VBUS = 0V,<br>VBB = 12V                         |  |

| Input Leakage Current (at the receiver during recessive bus level) | IBUS_PAS_REC                                                                                                                   | _         | 12         | 20        | μA    | Driver off,<br>8V < VBB < 18V<br>8V < VBUS < 18V<br>VBUS ≥ VBB |  |

| Leakage Current (disconnected from ground)                         | IBUS_NO_GND                                                                                                                    | -10       | 1.0        | +10       | μA    | GNDDEVICE = VBB,<br>0V < VBUS < 18V,<br>VBB = 12V              |  |

| Leakage Current (disconnected from VBB)                            | IBUS                                                                                                                           | 1         | ı          | 10        | μA    | VBB = GND,<br>0 < VBUS < 18V,<br>(Note 2)                      |  |

| Receiver Center Voltage                                            | VBUS_CNT                                                                                                                       | 0.475 VBB | 0.5<br>VBB | 0.525 VBB | V     | VBUS_CNT = (VIL (LBUS) + VIH (LBUS))/2                         |  |

| Slave Termination                                                  | RSLAVE                                                                                                                         | 20        | 30         | 47        | kΩ    |                                                                |  |

| Capacitance of Slave Node                                          | CSLAVE                                                                                                                         |           |            | 50        | pF    |                                                                |  |

**Note 1:** Internal current limited. 2.0 ms maximum recovery time (RLBUS =  $0\Omega$ , TX = 0.4 VREG, VLBUS = VBB).

<sup>2:</sup> Node has to sustain the current that can flow under this condition; bus must be operational under this condition.

# 2.4 AC Specifications

| AC CHARACTERISTICS                                                                 | VBB = 6.0V to 27.0V; TA = -40°C to +125°C |        |       |      |       |                                                                                                                                                                                                                           |  |

|------------------------------------------------------------------------------------|-------------------------------------------|--------|-------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                          | Sym                                       | Min.   | Тур.  | Max. | Units | Test Conditions                                                                                                                                                                                                           |  |

| Bus Interface – Constant SI                                                        | ope Time F                                | Paramo | eters |      |       |                                                                                                                                                                                                                           |  |

| Slope Rising and Falling Edges                                                     | tslope                                    | 3.5    | _     | 22.5 | μs    | 7.3V <= VBB <= 18V                                                                                                                                                                                                        |  |

| Propagation Delay of<br>Transmitter                                                | ttranspd                                  | _      | _     | 4.0  | μs    | ttranspd = max (ttranspdr or ttranspdf)                                                                                                                                                                                   |  |

| Propagation Delay of<br>Receiver                                                   | trecpd                                    | _      | _     | 6.0  | μs    | trecpd = max (trecpdr or trecpdf)                                                                                                                                                                                         |  |

| Symmetry of Propagation<br>Delay of Receiver Rising<br>Edge w.r.t. Falling Edge    | trecsym                                   | -2.0   |       | 2.0  | μs    | trecsym = max (trecpdf – trecpdr)<br>RRXD 2.4 $\Omega$ TO Vcc, CRXD 20 PF                                                                                                                                                 |  |

| Symmetry of Propagation<br>Delay of Transmitter Rising<br>Edge w.r.t. Falling Edge | ttrans-<br>sym                            | -2.0   | ı     | 2.0  | μs    | ttranssym = max (ttranspdf - ttranspdr)                                                                                                                                                                                   |  |

| Time to Sample of FAULT/<br>TXE for Bus Conflict Report-<br>ing                    | tfault                                    | _      | _     | 32.5 | μs    | tfault = max (ttranspd + tslope + trecpd)                                                                                                                                                                                 |  |

| Duty Cycle 1 @20.0 kbit/sec                                                        |                                           | .396   | _     | _    |       | Cbus; Rbus conditions:<br>1 nF; 1 k $\Omega$   6.8 nF; 660 $\Omega$   10 nF; 500 $\Omega$<br>THrec(max) = 0.744 x VBB,<br>THdom(max) = 0.581 x VBB,<br>VBB =7.0V - 18V; tbit = 50 $\mu$ s<br>D1 = tbus_rec(min)/2 x tbit) |  |

| Duty Cycle 2 @20.0 kbit/sec                                                        |                                           | _      | _     | .581 |       | Cbus; Rbus conditions:<br>1 nF; 1 k $\Omega$   6.8 nF; 660 $\Omega$   10 nF; 500 $\Omega$<br>THrec(max) = 0.284 x VBB,<br>THdom(max) = 0.422 x VBB,<br>VBB =7.6V - 18V; tbit = 50 $\mu$ s<br>D2 = tbus_rec(max)/2 x tbit) |  |

| Duty Cycle 3 @10.4 kbit/sec                                                        |                                           | .417   | _     | _    |       | Cbus; Rbus conditions:<br>1 nF; 1 k $\Omega$   6.8 nF; 660 $\Omega$   10 nF; 500 $\Omega$<br>THrec(max) = 0.778 x VBB,<br>THdom(max) = 0.616 x VBB,<br>VBB =7.0V - 18V; tbit = 96 $\mu$ s<br>D3 = tbus_rec(min)/2 x tbit) |  |

| Duty Cycle 4 @10.4 kbit/sec                                                        |                                           | _      | _     | .590 |       | Cbus; Rbus conditions:<br>1 nF; 1 k $\Omega$   6.8 nF; 660 $\Omega$   10 nF; 500 $\Omega$<br>THrec(max) = 0.251 x VBB,<br>THdom(max) = 0.389 x VBB,<br>VBB =7.6V - 18V; tbit = 96 $\mu$ s<br>D4 = tbus_rec(max)/2 x tbit) |  |

| Wake-up Timing                                                                     |                                           |        |       |      |       |                                                                                                                                                                                                                           |  |

| Bus Activity Debounce time                                                         | tBDB                                      | 5      |       | 20   | μs    | Bus debounce time, 10 µs typical                                                                                                                                                                                          |  |

| Bus Activity to Vren on                                                            | tBACTVE                                   | 35     |       | 150  | μs    | After Bus debounce time, 52 µs typical                                                                                                                                                                                    |  |

| WAKE to Vren on                                                                    | tWAKE                                     |        |       | 150  | μs    |                                                                                                                                                                                                                           |  |

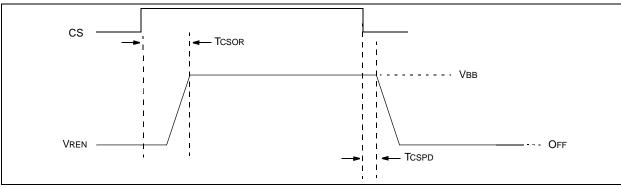

| Chip Select to Vren on                                                             | tCSOR                                     |        |       | 150  | μs    | Vren floating                                                                                                                                                                                                             |  |

| Chip Select to Vren off                                                            | tCSPD                                     | _      |       | 80   | μs    | Vren floating                                                                                                                                                                                                             |  |

# 2.5 Thermal Specifications

| THERMAL CHARACTERISTICS     |           |       |     |       |                 |  |  |

|-----------------------------|-----------|-------|-----|-------|-----------------|--|--|

| Parameter                   | Symbol    | Тур   | Max | Units | Test Conditions |  |  |

| Recovery Temperature        | θRECOVERY | +140  | _   | °C    |                 |  |  |

| Shutdown Temperature        | θSHUTDOWN | +150  | _   | °C    |                 |  |  |

| Short Circuit Recovery Time | ttherm    | 1.5   | 5.0 | ms    |                 |  |  |

| Thermal Package Resistances | •         |       | •   | •     |                 |  |  |

| Thermal Resistance, 8L-DFN  | θЈА       | 35.7  | _   | °C/W  |                 |  |  |

| Thermal Resistance, 8L-PDIP | θЈА       | 89.3  | _   | °C/W  |                 |  |  |

| Thermal Resistance, 8L-SOIC | θЈА       | 149.5 | _   | °C/W  |                 |  |  |

**Note 1:** The maximum power dissipation is a function of TJMAX,  $\Theta$ JA and ambient temperature  $T_A$ . The maximum allowable power dissipation at an ambient temperature is PD = (TJMAX - TA)  $\Theta$ JA. If this dissipation is exceeded, the die temperature will rise above 150°C and the MCP2003/4 will go into thermal shutdown.

# 2.6 Typical Performance Curves

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated, VBB = 6.0V to 18.0V, TA = -40°C to +125°C.

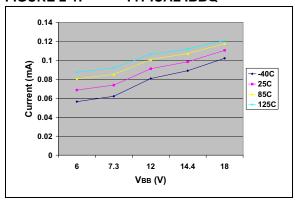

FIGURE 2-1: TYPICAL IBBQ

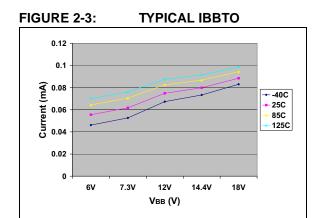

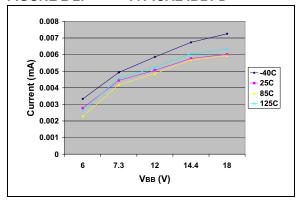

FIGURE 2-2: TYPICAL IBBPD

# 2.7 Timing Diagrams and Specifications

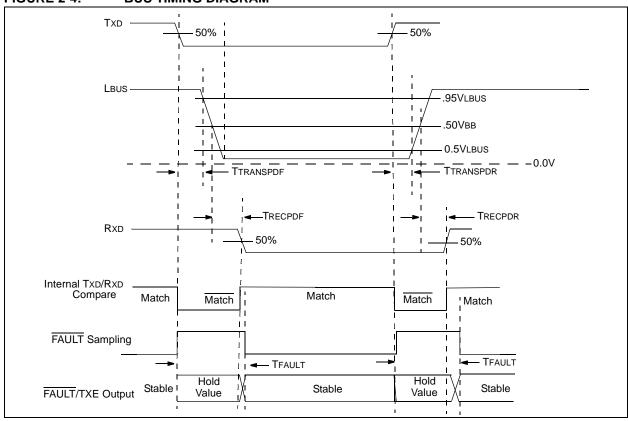

FIGURE 2-4: BUS TIMING DIAGRAM

FIGURE 2-5: CS TO VREN TIMING DIAGRAM

FIGURE 2-6: BUS TO VREN WAKE TIMING DIAGRAM

**NOTES:**

# 3.0 PACKAGING INFORMATION

# 3.1 Package Marking Information

8-Lead DFN (4x4)

8-Lead PDIP (300 mil)

8-Lead SOIC (150 mil)

Example:

Example:

Example:

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available

characters for customer-specific information.

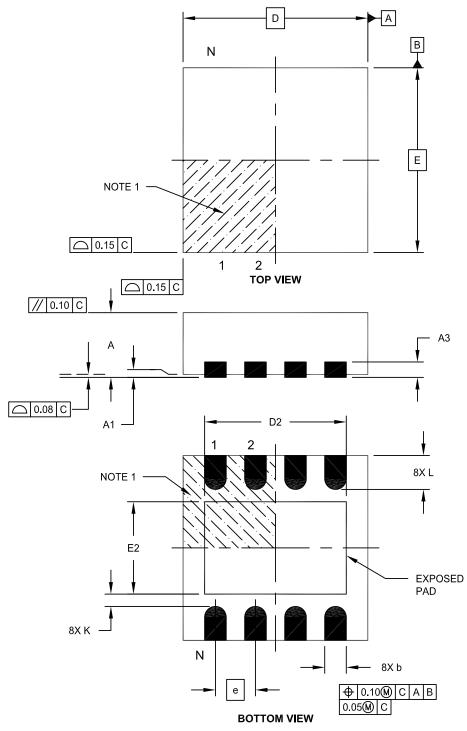

# 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-131E Sheet 1 of 2

# 8-Lead Plastic Dual Flat, No Lead Package (MD) - 4x4x0.9 mm Body [DFN]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  |          |          | S    |  |

|------------------------|--------|----------|----------|------|--|

| Dimension              | Limits | MIN      | NOM      | MAX  |  |

| Number of Pins         | N      |          | 8        |      |  |

| Pitch                  | е      |          | 0.80 BSC |      |  |

| Overall Height         | Α      | 0.80     | 0.90     | 1.00 |  |

| Standoff               | A1     | 0.00     | 0.02     | 0.05 |  |

| Contact Thickness      | A3     | 0.20 REF |          |      |  |

| Overall Length         | D      | 4.00 BSC |          |      |  |

| Exposed Pad Width      | E2     | 2.60     | 2.70     | 2.80 |  |

| Overall Width          | E      |          | 4.00 BSC |      |  |

| Exposed Pad Length     | D2     | 3.40     | 3.50     | 3.60 |  |

| Contact Width          | b      | 0.25     | 0.30     | 0.35 |  |

| Contact Length         | L      | 0.30     | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K      | 0.20     | -        | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131E Sheet 2 of 2

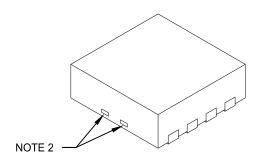

# 8-Lead Plastic Dual Flat, No Lead Package (MD) - 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS      |      |      |      |

|----------------------------|------------------|------|------|------|

| Dimension                  | Dimension Limits |      |      | MAX  |

| Contact Pitch              | E 0.80 BSC       |      |      |      |

| Optional Center Pad Width  | W2               |      |      | 3.60 |

| Optional Center Pad Length | T2               |      |      | 2.50 |

| Contact Pad Spacing        | C1               |      | 4.00 |      |

| Contact Pad Width (X8)     | X1               |      |      | 0.35 |

| Contact Pad Length (X8)    | Y1               |      |      | 0.75 |

| Distance Between Pads      | G                | 0.45 |      |      |

# Notes:

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2131C

<sup>1.</sup> Dimensioning and tolerancing per ASME Y14.5M

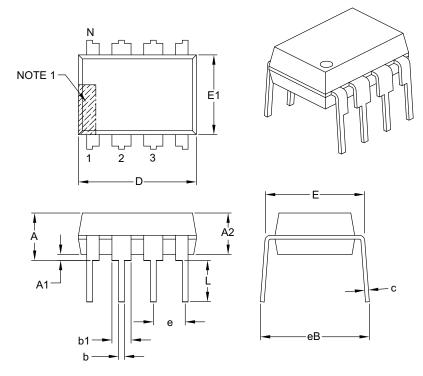

# 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |      | INCHES   |      |  |

|----------------------------|------------------|------|----------|------|--|

|                            | Dimension Limits | MIN  | NOM      | MAX  |  |

| Number of Pins             | N                |      | 8        |      |  |

| Pitch                      | е                |      | .100 BSC |      |  |

| Top to Seating Plane       | A                | -    | _        | .210 |  |

| Molded Package Thickness   | A2               | .115 | .130     | .195 |  |

| Base to Seating Plane      | A1               | .015 | _        | -    |  |

| Shoulder to Shoulder Width | E                | .290 | .310     | .325 |  |

| Molded Package Width       | E1               | .240 | .250     | .280 |  |

| Overall Length             | D                | .348 | .365     | .400 |  |

| Tip to Seating Plane       | L                | .115 | .130     | .150 |  |

| Lead Thickness             | С                | .008 | .010     | .015 |  |

| Upper Lead Width           | b1               | .040 | .060     | .070 |  |

| Lower Lead Width           | b                | .014 | .018     | .022 |  |

| Overall Row Spacing §      | eB               | _    | _        | .430 |  |

# Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

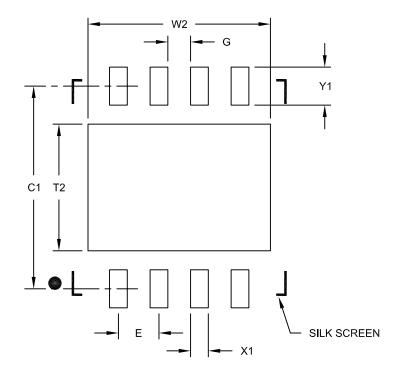

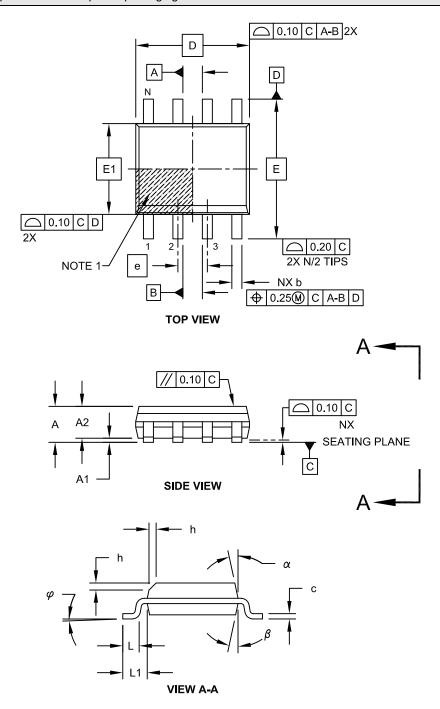

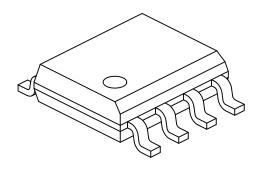

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057C Sheet 1 of 2

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**bte:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |        | MILLIMETERS |          |      |

|--------------------------|--------|-------------|----------|------|

| Dimension                | Limits | MIN         | NOM      | MAX  |

| Number of Pins           | N      |             | 8        |      |

| Pitch                    | е      |             | 1.27 BSC |      |

| Overall Height           | Α      | ı           | -        | 1.75 |

| Molded Package Thickness | A2     | 1.25        | -        | -    |

| Standoff §               | A1     | 0.10        | -        | 0.25 |

| Overall Width            | E      | 6.00 BSC    |          |      |

| Molded Package Width     | E1     | 3.90 BSC    |          |      |

| Overall Length           | D      | 4.90 BSC    |          |      |

| Chamfer (Optional)       | h      | 0.25        | - 0.50   |      |

| Foot Length              | L      | 0.40        | -        | 1.27 |

| Footprint                | L1     | 1.04 REF    |          |      |

| Foot Angle               | φ      | 0°          | -        | 8°   |

| Lead Thickness           | С      | 0.17        | -        | 0.25 |

| Lead Width               | b      | 0.31        | -        | 0.51 |

| Mold Draft Angle Top     | α      | 5°          | -        | 15°  |

| Mold Draft Angle Bottom  | β      | 5°          | -        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-057C Sheet 2 of 2

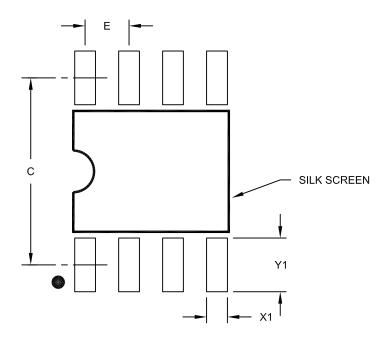

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                         | Units  | MILLIMETERS |          | S    |

|-------------------------|--------|-------------|----------|------|

| Dimension               | Limits | MIN         | NOM      | MAX  |

| Contact Pitch           | Е      |             | 1.27 BSC |      |

| Contact Pad Spacing     | С      |             | 5.40     |      |

| Contact Pad Width (X8)  | X1     |             |          | 0.60 |

| Contact Pad Length (X8) | Y1     |             |          | 1.55 |

## Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

# **APPENDIX A: REVISION HISTORY**

# Revision A (March 2010)

• Original Release of this Document.

# Revision B (July 2010)

Added Section 2.2 "Nomenclature used in this document", and added the "Capacitance of Slave Node" parameter to Table 2.3.

# **Revision C (August 2010)**

Updated all references of Sleep mode to Power-Down mode, and updated the Max. parameter for Duty Cycle 2 in Section 2.4 "AC Specifications".

**NOTES:**

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.            | <u>X</u>              | <u>/xx</u>                                                                                                                               | Exa | amples:        |                                                         |

|---------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|---------------------------------------------------------|

|                     | <br>nperature         | Package                                                                                                                                  | a)  | MCP2004-E/MD:  | Extended Temperature, 8L-DFN pkg.                       |

| Range               | Kange                 |                                                                                                                                          | b)  | MCP2004-E/P:   | Extended Temperature, 8L-PDIP pkg.                      |

| Device:             | MCP2004:<br>MCP2004T: | LIN Transceiver with Voltage Regulator<br>LIN Transceiver with Voltage Regulator                                                         | c)  | MCP2004-E/SN:  | Extended Temperature, 8L-SOIC pkg.                      |

| MCP2003:            | MCP2003:<br>MCP2003T: | (Tape and Reel) (DFN and SOIC) LIN Transceiver with Voltage Regulator LIN Transceiver with Voltage Regulator                             | d)  | MCP2004T-E/MD: | Tape and Reel,<br>Extended Temperature,<br>8L-DFN pkg.  |

| Temperature Range   | · F = -40°            | (Tape and Reel) (DFN and SOIC)  C to +125°C                                                                                              | e)  | MCP2004T-E/SN: | Tape and Reel,<br>Extended Temperature,<br>8L-SOIC pkg. |

| Tomporataro rtango. | 10                    | 0.10 1.120 0                                                                                                                             |     |                | or colo ping.                                           |

| Package:            |                       | MD = Plastic Micro Small Outline (4x4), 8-lead P = Plastic DIP (300 mil Body), 8-lead, 14-lead SN = Plastic SOIC, (150 mil Body), 8-lead | a)  | MCP2003-E/MD:  | Extended Temperature, 8L-DFN pkg.                       |

|                     |                       |                                                                                                                                          | b)  | MCP2003-E/P:   | Extended Temperature, 8L-PDIP pkg.                      |

|                     |                       |                                                                                                                                          | c)  | MCP2003-E/SN:  | Extended Temperature, 8L-SOIC pkg.                      |

|                     |                       |                                                                                                                                          | d)  | MCP2003T-E/MD: | . •                                                     |

|                     |                       |                                                                                                                                          | e)  | MCP2003T-E/SN: | Tape and Reel,<br>Extended Temperature,<br>8L-SOIC pkg. |

**NOTES:**

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN:978-1-60932-443-8

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

# WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### **ASIA/PACIFIC**

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-536-4818

Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 **UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10