SLAS646A – DECEMBER 2009 – REVISED FEBRUARY 2010

16-Bit, 625 MSPS, 2x Interpolating, Dual-Channel Digital-to-Analog Converter (DAC)

Check for Samples: DAC3282

#### **FEATURES**

- Dual, 16-Bit, 625 MSPS DACs

- 8-Bit Input LVDS Data Bus

- Byte-Wide Interleaved Data Load

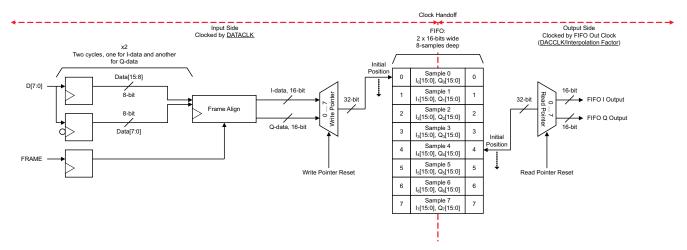

- 8 Sample Input FIFO

- Optional Data Pattern Checker

- Multi-DAC Synchronization

- Optional 2x Interpolation Filter

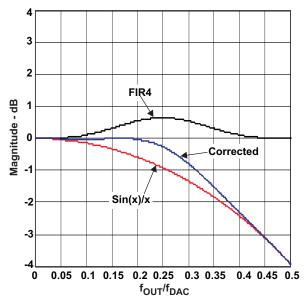

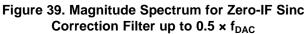

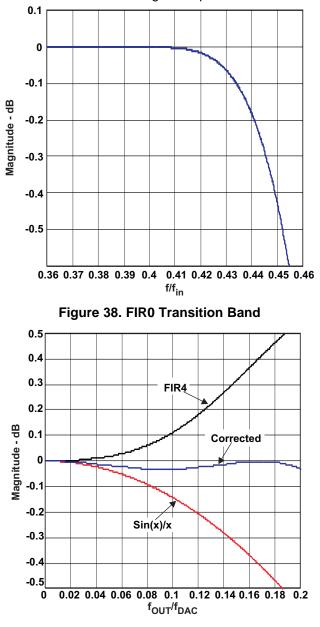

- Zero-IF Sinc Correction Filter

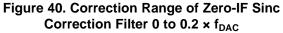

- Fs/2 and ± Fs/4 Coarse Mixer

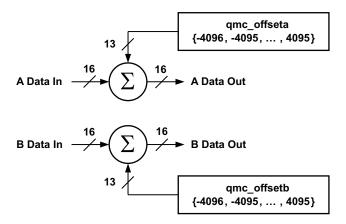

- Digital Offset Adjustment for LO Correction

- Temperature Sensor

- 3- or 4-Wire Serial Control Interface

- On Chip 1.2-V reference

- Differential Scalable Output: 2 to 20 mA

- Low Power: 950 mW at 625 MSPS, 845 mW at 500 MHz, Full Operating Conditions

- Space Saving Package: 48-pin 7×7mm QFN

### **APPLICATIONS**

- Cellular Base Stations

- Diversity Transmit

- Wideband Communications

- Digital Synthesis

## DESCRIPTION

The DAC3282 is a dual-channel 16-bit 625 MSPS digital-to-analog converter (DAC) with an 8-bit LVDS input data bus with on-chip termination, optional 2x interpolation filter, and internal voltage reference. The DAC3282 offers superior linearity, noise and crosstalk performance.

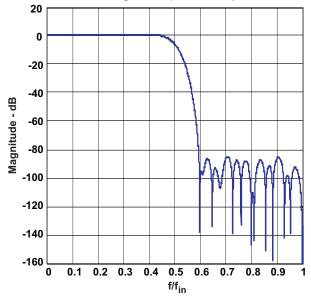

Input data can be interpolated by 2x through an on-chip interpolating FIR filter with over 85 dB of stop-band attenuation. Multiple DAC3282 devices can be fully synchronized.

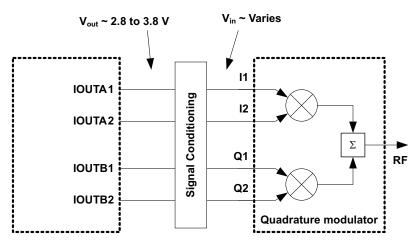

The DAC3282 allows either a complex or real output. An optional coarse mixer in complex mode provides frequency upconversion and the dual DAC output produces a complex Hilbert Transform pair. The digital offset correction feature allows optimization of LO feed-through of an external quadrature modulator performing the final single sideband RF up-conversion.

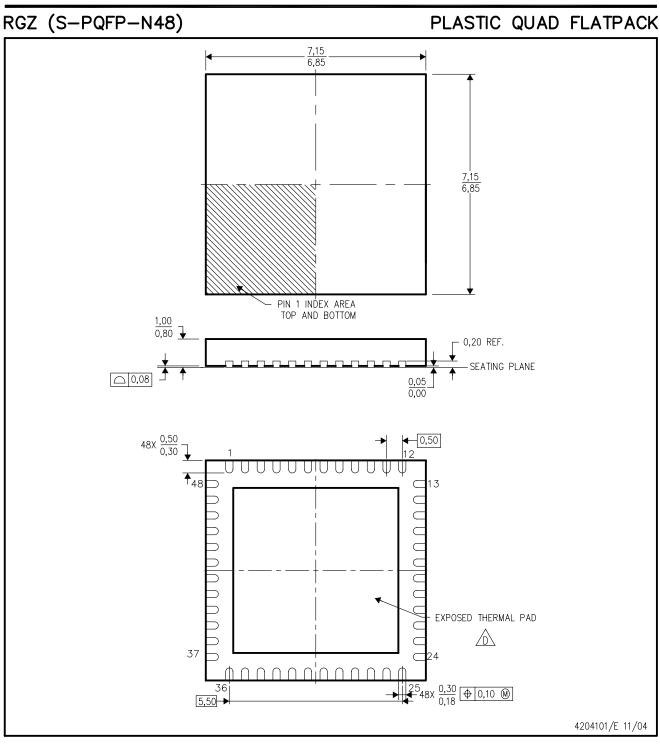

The DAC3282 is characterized for operation over the entire industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C and is available in a 48-pin 7×7mm QFN package.

#### **ORDERING INFORMATION**

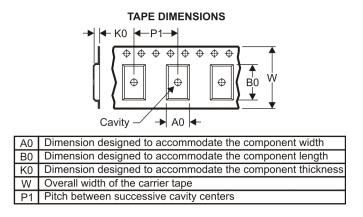

| T <sub>A</sub> | ORDER CODE PACKAGE<br>DRAWING/TYPE <sup>(1) (2)</sup> |                           | TRANSPORT<br>MEDIA | QUANTITY |

|----------------|-------------------------------------------------------|---------------------------|--------------------|----------|

| –40°C to 85°C  | DAC3282IRGZT                                          | RGZ / 48QFN Quad Flatpack |                    | 250      |

|                | DAC3282IRGZR                                          | No-Lead                   | Tape and Reel      | 2500     |

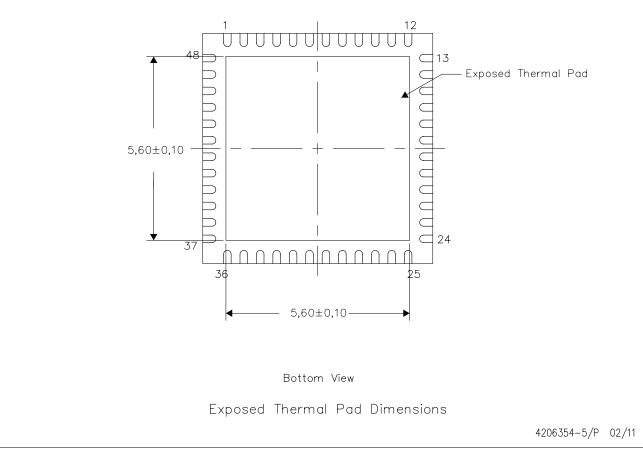

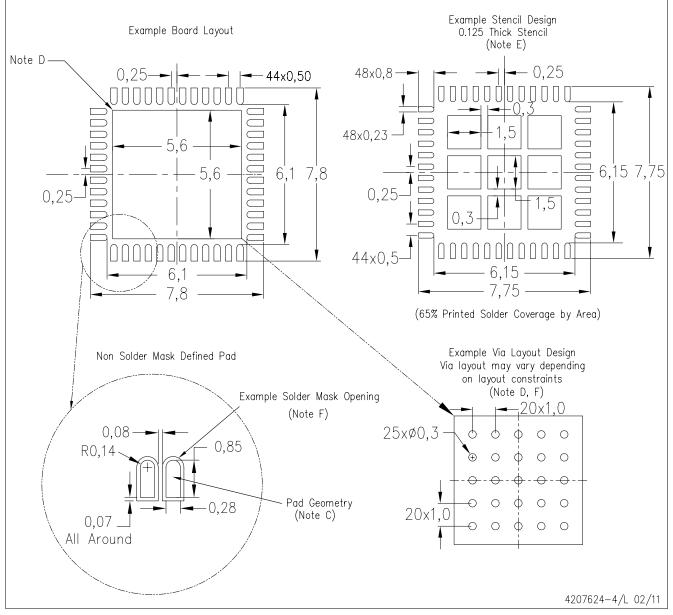

(1) Thermal Pad Size: 5,6 mm x 5,6 mm

(2) MSL Peak Temperature: Level-3-260C-168 HR

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## DAC3282

Alla S

#### SLAS646A - DECEMBER 2009-REVISED FEBRUARY 2010

Texas

INSTRUMENTS

www.ti.com

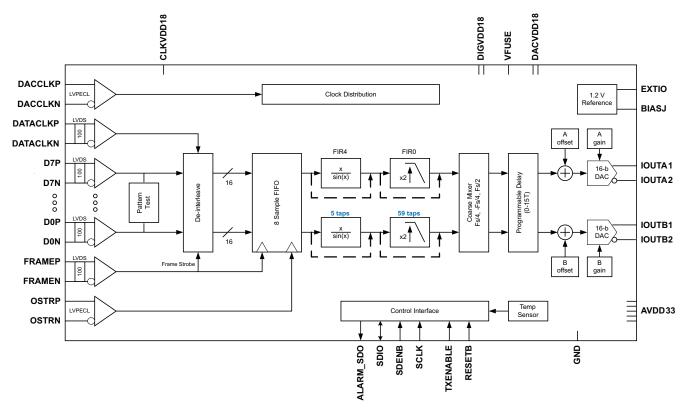

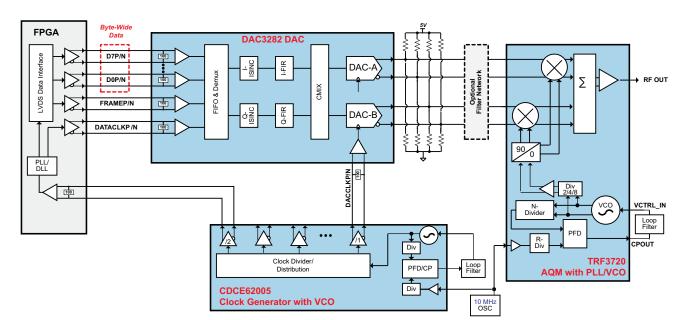

#### FUNCTIONAL BLOCK DIAGRAM

# www.ti.com

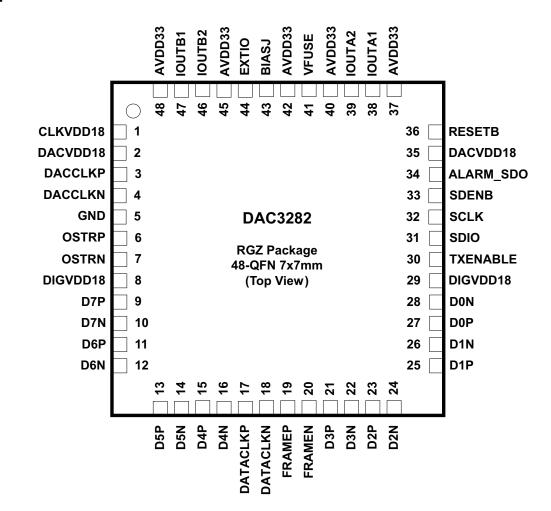

#### PIN FUNCTIONS

| PIN       |                           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------|---------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO.                       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| AVDD33    | 37, 40, 42,<br>45, 48     | Ι   | Analog supply voltage. (3.3 V)                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ALARM_SDO | 34                        | 0   | 1.8V CMOS output for ALARM condition. The ALARM output functionality is defined through the CONFIG6 register. Default polarity is active low, but can be changed to active high via CONFIG0 <b>alarm_pol</b> control bit. Optionally, it can be used as the uni-directional data output in 4-pin serial interface mode (CONFIG 23 <b>sif4_ena</b> = '1').                        |  |  |  |

| BIASJ     | 43                        | 0   | Full-scale output current bias. For 20mA full-scale output current, connect a 960 $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                      |  |  |  |

| CLKVDD18  | 1                         | Ι   | Internal clock buffer supply voltage. (1.8 V)<br>It is recommended to isolate this supply from DACVDD18 and DIGVDD18.                                                                                                                                                                                                                                                            |  |  |  |

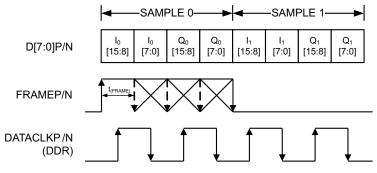

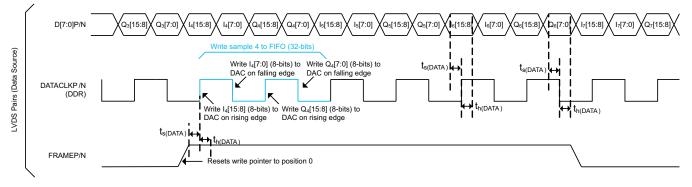

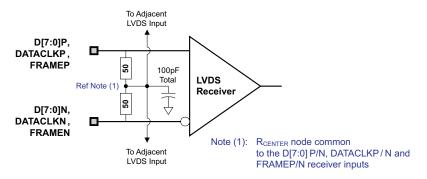

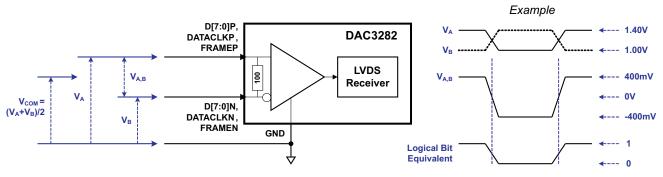

| D[70]P    | 9, 11, 13,<br>15, 21, 23, | I   | LVDS positive input data bits 0 through 7. Each positive/negative LVDS pair has an internal 100 $\Omega$ termination resistor. Data format relative to DATACLKP/N clock is Double Data Rate (DDR) with two data transfers per DATACKP/N clock cycle. Dual channel 16-bit data is transferred byte-wide on this single 8-bit data bus using FRAMEP/N as a frame strobe indicator. |  |  |  |

|           | 25, 27                    | 1   | D7P is most significant data bit (MSB) – pin 9                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|           |                           |     | D0P is least significant data bit (LSB) – pin 27                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|           |                           |     | The order of the bus can be reversed via CONFIG19 rev bit.                                                                                                                                                                                                                                                                                                                       |  |  |  |

|           | 10, 12, 14,               |     | LVDS negative input data bits 0 through 15. (See D[7:0]P description above)                                                                                                                                                                                                                                                                                                      |  |  |  |

| D[70]N    | 16, 22, 24, I             |     | D7N is most significant data bit (MSB) – pin 10                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|           | 26, 28                    |     | D0N is least significant data bit (LSB) – pin 28                                                                                                                                                                                                                                                                                                                                 |  |  |  |

Copyright © 2009–2010, Texas Instruments Incorporated

3

INSTRUMENTS www.ti.com

**Texas**

#### **PIN FUNCTIONS (continued)**

| PIN      |                   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO.               | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |  |  |

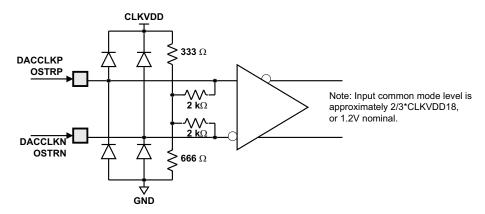

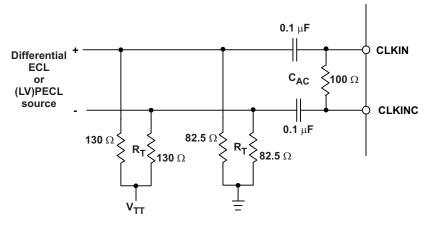

| DACCLKP  | 3                 | I   | Positive external LVPECL clock input for DAC core with a self-bias of approximately CLKVDD18/2.                                                                                                                                                                                                                                           |  |  |  |

| DACCLKN  | 4                 | I   | Complementary external LVPECL clock input for DAC core. (see the DACCLKP description)                                                                                                                                                                                                                                                     |  |  |  |

| DACVDD18 | 2, 35             | I   | DAC core supply voltage. (1.8 V)<br>It is recommended to isolate this supply from CLKVDD18 and DIGVDD18.                                                                                                                                                                                                                                  |  |  |  |

| DATACLKP | 17                | Ι   | LVDS positive input data clock. This positive/negative pair has an internal 100 $\Omega$ termination resistor.<br>Input data D[7:0]P/N is latched on both edges of DATACLKP/N (Double Data Rate) with two data transfers input per DATACLKP/N clock cycle.                                                                                |  |  |  |

| DATACLKN | 18                | Ι   | LVDS negative input data clock. (See DATACLKP description)                                                                                                                                                                                                                                                                                |  |  |  |

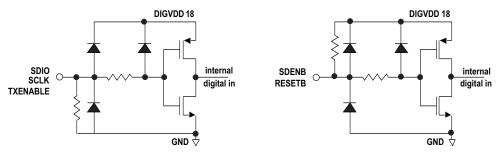

| DIGVDD18 | 8, 29             | Ι   | Digital supply voltage. (1.8V)<br>It is recommended to isolate this supply from CLKVDD18 and DACVDD18.                                                                                                                                                                                                                                    |  |  |  |

| EXTIO    | 44                | I/O | Used as external reference input when internal reference is disabled through CONFIG25 <b>extref_ena</b> = '1'. Used as internal reference output when CONFIG25 <b>extref_ena</b> = '0' (default). Requires a 0.1 $\mu$ F decoupling capacitor to AGND when used as reference output.                                                      |  |  |  |

| FRAMEP   | 19                | I   | LVDS frame indicator positive input. This positive/negative pair has an internal 100 $\Omega$ termination resistor. This signal is captured with the rising edge of DATACLKP/N and used to indicate the beginning of the frame. It is also used as a reset signal by the FIFO. The FRAMEP/N signal should be edge-aligned with D[7:0]P/N. |  |  |  |

| FRAMEN   | 20                | Ι   | LVDS frame indicator negative input. (See the FRAMEN description)                                                                                                                                                                                                                                                                         |  |  |  |

| GND      | 5, Thermal<br>Pad | Ι   | Pin 5 and the Thermal Pad located on the bottom of the QFN package is ground for all supplies.                                                                                                                                                                                                                                            |  |  |  |

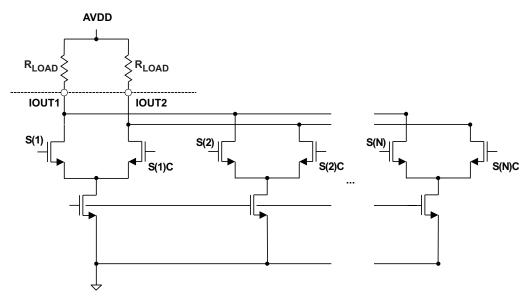

| IOUTA1   | 38                | 0   | A-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full scale current sink and the least positive voltage on the IOUTA1 pin. Similarly, a 0xFFFF data input results in a 0 mA current sink and the most positive voltage on the IOUTA1 pin.                                              |  |  |  |

| IOUTA2   | 39                | 0   | A-Channel DAC complementary current output. The IOUTA2 has the opposite behavior of the IOUTA1 described above. An input data value of 0x0000 results in a 0 mA sink and the most positive voltage on the IOUTA2 pin.                                                                                                                     |  |  |  |

| IOUTB1   | 47                | 0   | B-Channel DAC current output. Refer to IOUTA1 description above.                                                                                                                                                                                                                                                                          |  |  |  |

| IOUTB2   | 46                | 0   | B-Channel DAC complementary current output. Refer to IOUTA2 description above.                                                                                                                                                                                                                                                            |  |  |  |

| OSTRP    | 6                 | I   | LVPECL output strobe positive input. This positive/negative pair is captured with the rising edge of DACCLKP/N. It is used to reset the clock dividers and for multiple DAC synchronization. If unused it can be left floating.                                                                                                           |  |  |  |

| OSTRN    | 7                 | Ι   | LVPECL output strobe negative input. (See the OSTRP description)                                                                                                                                                                                                                                                                          |  |  |  |

| RESETB   | 36                | Ι   | 1.8V CMOS active low input for chip RESET. Internal pull-up.                                                                                                                                                                                                                                                                              |  |  |  |

| SCLK     | 32                | Ι   | 1.8V CMOS serial interface clock. Internal pull-down.                                                                                                                                                                                                                                                                                     |  |  |  |

| SDENB    | 33                | Ι   | 1.8V CMOS active low serial data enable, always an input to the DAC3282. Internal pull-up.                                                                                                                                                                                                                                                |  |  |  |

| SDIO     | 31                | I/O | 1.8V CMOS serial interface data. Bi-directional in 3-pin mode (default). In 4-pin interface mode, the SDIO pin is an input only. Internal pull-down.                                                                                                                                                                                      |  |  |  |

| TXENABLE | 30                | Ι   | 1.8V CMOS active high input. TXENABLE must be high for the DATA to the DAC to be enabled.<br>When TXENABLE is low, the digital logic section is forced to all 0, and any input data is ignored.<br>Internal pull-down.                                                                                                                    |  |  |  |

| VFUSE    | 41                | Ι   | Digital supply voltage. (1.8V) This supply pin is also used for factory fuse programming. <b>Connect to DACVDD18 pins for normal operation.</b>                                                                                                                                                                                           |  |  |  |

www.ti.com

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                  |                                                                  | VALUE                  | UNIT |

|----------------------------------|------------------------------------------------------------------|------------------------|------|

|                                  | DACVDD18 <sup>(2)</sup>                                          | -0.5 to 2.3            | V    |

|                                  | DIGVDD18 <sup>(2)</sup>                                          | -0.5 to 2.3            | V    |

| Supply voltage range             | CLKVDD18 <sup>(2)</sup>                                          | -0.5 to 2.3            | V    |

|                                  | VFUSE <sup>(2)</sup>                                             | -0.5 to 2.3            | V    |

|                                  | AVDD33 <sup>(2)</sup>                                            | –0.5 to 4              | V    |

| Terminal voltage range           | CLKVDD18 to DIGVDD18                                             | -0.5 to 0.5            | V    |

|                                  | DACVDD18 to DIGVDD18                                             | -0.5 to 0.5            | V    |

|                                  | D[70]P ,D[70]N, DATACLKP,DATACLKN, FRAMEP, FRAMEN <sup>(2)</sup> | -0.5 to DIGVDD18 + 0.5 | V    |

|                                  | DACCLKP, DACCLKN, OSTRP, OSTRN <sup>(2)</sup>                    | -0.5 to CLKVDD18 + 0.5 | V    |

|                                  | ALARM_SDO, SDIO, SCLK, SDENB, RESETB, TXENABLE <sup>(2)</sup>    | -0.5 to DIGVDD18 + 0.5 | V    |

|                                  | IOUTA1/B1, IOUTA2/B2 <sup>(2)</sup>                              | -1.0 to AVDD33 + 0.5   | V    |

|                                  | EXTIO, BIASJ <sup>(2)</sup>                                      | -0.5 to AVDD33 + 0.5   | V    |

| Peak input current (any input)   |                                                                  | 20                     | mA   |

| Peak total input current (all in | puts)                                                            | -30                    | mA   |

| Operating free-air temperature   | e range, T <sub>A</sub> : DAC3282                                | -40 to 85              | °C   |

| Storage temperature range        |                                                                  | -65 to 150             | °C   |

| Lead temperature 1,6 mm (1/      | 16 inch) from the case for 10 seconds                            | 260                    | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Measured with respect to GND.

#### THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|               | THERMAL CONDUCTIVITY                            | 48Id QFN | UNIT |

|---------------|-------------------------------------------------|----------|------|

| $T_{J}$       | Maximum Junction Temperature <sup>(1) (2)</sup> | 125      | °C   |

| 0             | Theta junction-to-ambient (still air)           | 30       | °C/W |

| $\theta_{JA}$ | Theta junction-to-ambient (150 lfm)             | 24       | °C/W |

| $\theta_{JB}$ | Theta junction-to-board                         | 8        | °C/W |

| $\theta_{JP}$ | Theta junction-to-pad                           | 1.3      | °C/W |

(1) Air flow or heat sinking reduces  $\theta_{JA}$  and may be required for sustained operation at 85° and maximum operating conditions.

(2) It is strongly recommended to solder the device thermal pad to the board ground plane.

www.ti.com

#### ELECTRICAL CHARACTERISTICS – DC SPECIFICATIONS<sup>(1)</sup>

over recommended operating free-air temperature range, nominal supplies, IOUT<sub>FS</sub> = 20 mA (unless otherwise noted)

| PARAMETER          |                                         | TEST CONDITIONS                              | MIN          | TYP   | MAX           | UNIT             |

|--------------------|-----------------------------------------|----------------------------------------------|--------------|-------|---------------|------------------|

| Resolutio          | n                                       |                                              | 16           |       |               | Bits             |

| DC ACCL            | JRACY                                   |                                              | ł            |       | L             |                  |

| DNL                | Differential nonlinearity               |                                              |              | ±2    |               | LSB              |

| INL                | Integral nonlinearity                   | -1 LSB = IOUT <sub>FS</sub> /2 <sup>16</sup> |              | ±4    |               | LSB              |

| ANALOG             | OUTPUT                                  |                                              | I            |       |               |                  |

|                    | Coarse gain linearity                   |                                              |              | ±0.04 |               | LSB              |

|                    | Offset error                            | Mid code offset                              |              | 0.01  |               | %FSR             |

|                    |                                         | With external reference                      |              | ±2    |               | %FSR             |

|                    | Gain error                              | With internal reference                      |              | ±2    |               | %FSR             |

|                    | Gain mismatch                           | With internal reference                      | -2           |       | 2             | %FSR             |

|                    | Minimum full scale output current       | Nominal full-scale current,                  |              | 2     |               |                  |

|                    | Maximum full scale output current       | $IOUT_{FS} = 16 \times IBIAS$ current.       |              | 20    |               | mA               |

|                    | Output compliance range <sup>(2)</sup>  | IOUT <sub>FS</sub> = 20 mA                   | AVDD<br>0.5V |       | AVDD<br>+0.5V | V                |

|                    | Output resistance                       |                                              |              | 300   |               | kΩ               |

|                    | Output capacitance                      |                                              |              | 5     |               | pF               |

| REFERE             | NCE OUTPUT                              |                                              |              |       |               |                  |

| $V_{REF}$          | Reference output voltage                |                                              | 1.14         | 1.2   | 1.26          | V                |

|                    | Reference output current <sup>(3)</sup> |                                              |              | 100   |               | nA               |

| REFERE             | NCE INPUT                               |                                              | ·            |       |               |                  |

| V <sub>EXTIO</sub> | Input voltage range                     | External Reference Mode                      | 0.1          | 1.2   | 1.25          | V                |

|                    | Input resistance                        |                                              |              | 1     |               | MΩ               |

|                    | Small signal bandwidth                  |                                              |              | 472   |               | kHz              |

|                    | Input capacitance                       |                                              |              | 100   |               | pF               |

| TEMPER             | ATURE COEFFICIENTS                      |                                              |              |       |               |                  |

|                    | Offset drift                            |                                              |              | ±1    |               | ppm of<br>FSR/°C |

|                    | Gain drift                              | With external reference                      |              | ±15   |               | ppm of           |

|                    | Gamunn                                  | With internal reference                      |              | ±30   |               | FSR/°C           |

|                    | Reference voltage drift                 |                                              |              | ±8    |               | ppm/°C           |

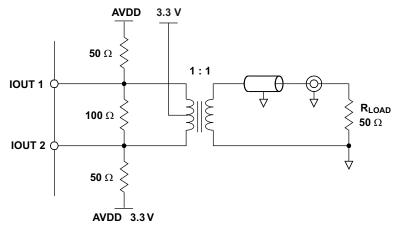

(1) Measured differential across IOUTA1 and IOUTA2 or IOUTB1 and IOUTB2 with 25  $\Omega$  each to AVDD.

(2) The lower limit of the output compliance is determined by the CMOS process. Exceeding this limit may result in transistor breakdown, resulting in reduced reliability of the DAC3282 device. The upper limit of the output compliance is determined by the load resistors and full-scale output current. Exceeding the upper limit adversely affects distortion performance and integral nonlinearity.

(3) Use an external buffer amplifier with high impedance input to drive any external load.

Copyright © 2009-2010, Texas Instruments Incorporated

Copyright © 2009–2010, Texas Instruments Incorporated

## ELECTRICAL CHARACTERISTICS – DC SPECIFICATIONS <sup>(1)</sup> (continued)

over recommended operating free-air temperature range, nominal supplies, IOUT<sub>FS</sub> = 20 mA (unless otherwise noted)

|                         | PARAMETER                                 | TEST CONDITIONS                                                                                                                                                                            | MIN  | TYP | MAX  | UNIT    |

|-------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|---------|

| POWER SU                | PPLY                                      |                                                                                                                                                                                            |      |     |      |         |

|                         | AVDD33                                    |                                                                                                                                                                                            | 3.0  | 3.3 | 3.6  | V       |

|                         | DACVDD18, DIGVDD18, CLKVDD18              |                                                                                                                                                                                            | 1.7  | 1.8 | 1.9  | V       |

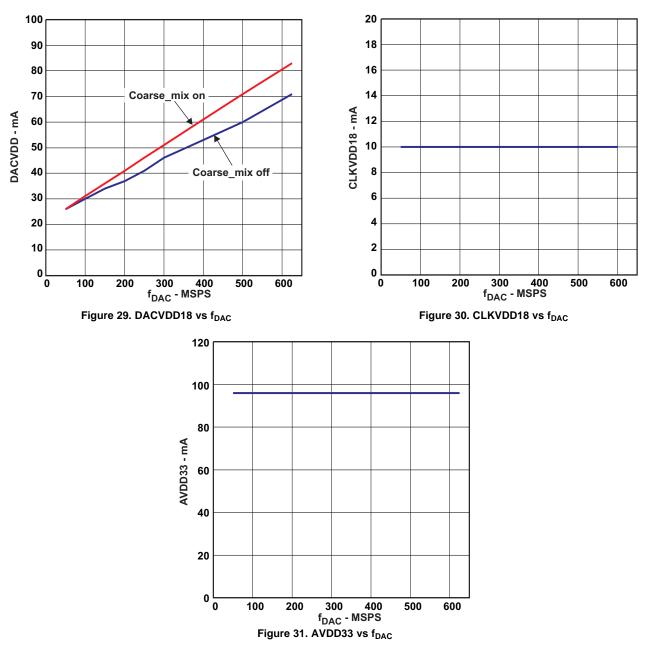

| I(AVDD33)               | Analog supply current                     |                                                                                                                                                                                            |      | 96  |      | mA      |

| I(DIGVDD18)             | Digital supply current                    | Mode 1(below)                                                                                                                                                                              |      | 268 |      | mA      |

| I(DACVDD18)             | DAC supply current                        | mode (below)                                                                                                                                                                               |      | 74  |      | mA      |

| I(CLKVDD18)             | Clock supply current                      |                                                                                                                                                                                            |      | 10  |      | mA      |

| I <sub>(AVDD33)</sub>   | Power down mode analog supply<br>current  |                                                                                                                                                                                            |      | 2   |      | mA      |

| I(DIGVDD18)             | Power down mode digital supply<br>current |                                                                                                                                                                                            |      | 3   |      | mA      |

| I(DACVDD18)             | Power down mode DAC supply<br>current     | Mode 4 (below)                                                                                                                                                                             |      | 0.5 |      | mA      |

| I <sub>(CLKVDD18)</sub> | Power down mode clock supply<br>current   |                                                                                                                                                                                            |      | 1   |      | mA      |

|                         | Power Dissipation                         | Mode 1: f <sub>DAC</sub> = 625MSPS, 2x interpolation, mixer on,<br>Digital Offset Control on                                                                                               |      | 950 | 1100 | mW      |

|                         |                                           | Mode 2: $f_{DAC}$ = 491.52MSPS, 2x interpolation, Zero-IF Correction Filter on, mixer off, Digital Offset Control on                                                                       |      | 845 |      | mW      |

| Ρ                       |                                           | Mode 3: Sleep Mode, f <sub>DAC</sub> = 625MSPS, 2X interpolation,<br>mixer on,<br>DAC in sleep mode:<br>CONFIG24 <b>sleepa, sleepb</b> set to 1                                            |      | 575 |      | mW      |

|                         |                                           | Mode 4: Power-Down mode, No clock, static data pattern,<br>DAC in power-down mode:<br>CONFIG23 clkpath_sleep_a, clkpath_sleepb set to 1<br>CONFIG24 clkrecv_sleep, sleepa, sleepb set to 1 |      | 15  |      | mW      |

| PSRR                    | Power Supply Rejection Ratio              | DC tested                                                                                                                                                                                  | -0.4 |     | 0.4  | %/FSR/V |

| Т                       | Operating Range                           |                                                                                                                                                                                            | -40  | 25  | 85   | °C      |

www.ti.com

NSTRUMENTS

XAS

#### **ELECTRICAL CHARACTERISTICS – AC SPECIFICATIONS**

over recommended operating free-air temperature range, nominal supplies, IOUTFS = 20 mA (unless otherwise noted)

| PARAMETER            |                                                                     | TEST CONDITIONS                                                                                                                                     | MIN      | TYP  | MAX | UNIT                |

|----------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-----|---------------------|

| ANALOG C             | DUTPUT <sup>(1)</sup>                                               |                                                                                                                                                     |          |      |     | L                   |

| 4                    |                                                                     | 1x Interpolation                                                                                                                                    | 312.5    |      |     | MODO                |

| f <sub>DAC</sub>     | Maximum output update rate                                          | 2x Interpolation                                                                                                                                    | 625      |      |     | MSPS                |

| t <sub>s(DAC)</sub>  | Output settling time to 0.1%                                        | Transition: Code 0x0000 to 0xFFFF                                                                                                                   |          | 10.4 |     | ns                  |

| t <sub>pd</sub>      | Output propagation delay                                            | DAC outputs are updated on the falling edge of DAC clock.<br>Does not include Digital Latency (see below).                                          |          | 2    |     | ns                  |

| t <sub>r(IOUT)</sub> | Output rise time 10% to 90%                                         |                                                                                                                                                     |          | 220  |     | ps                  |

| t <sub>f(IOUT)</sub> | Output fall time 90% to 10%                                         |                                                                                                                                                     |          | 220  |     | PS                  |

| Power up             | DAC Wake-up Time                                                    | IOUT current settling to 1% of IOUT <sub>FS</sub> . Measured from SDENB rising edge; Register CONFIG24, toggle <b>sleepa</b> from 1 to 0            |          | 90   |     | μs                  |

| Power-up<br>time     | DAC Sleep Time                                                      | IOUT current settling to less than 1% of IOUT <sub>FS</sub> . Measured from SDENB rising edge; Register CONFIG24, toggle <b>sleepa</b> from 0 to 1. |          | 90   |     | μS                  |

|                      |                                                                     | No interpolation, FIFO off, Offset off, Inverse sinc off                                                                                            |          | 38   |     |                     |

|                      |                                                                     | 2x Interpolation                                                                                                                                    | 59<br>16 |      |     | DAC clock<br>cycles |

|                      | Digital Latency                                                     | Zero-IF Sinc Correction Filter                                                                                                                      |          |      |     |                     |

|                      |                                                                     | FIFO                                                                                                                                                |          | 8    |     | -,                  |

|                      |                                                                     | Offset                                                                                                                                              |          | 4    |     |                     |

| AC PERFO             | RMANCE <sup>(2)</sup>                                               |                                                                                                                                                     |          |      |     |                     |

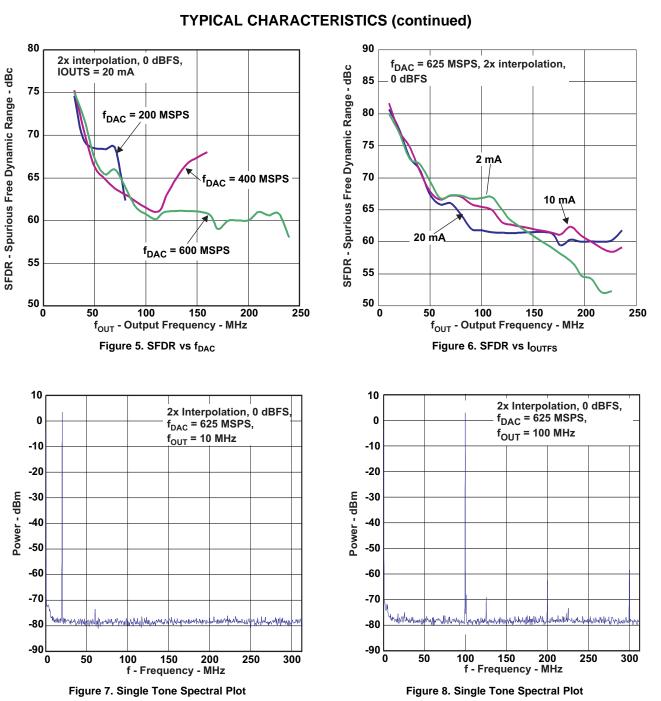

|                      |                                                                     | $f_{\text{DAC}}$ = 625 MSPS, $f_{\text{OUT}}$ = 10.1 MHz 2x Interp, DAC A+B on                                                                      | 83       |      |     |                     |

| SFDR                 | Spurious Free Dynamic Range SFDR (0 to $f_{DAC}/2$ ) Tone at 0 dBFS | $f_{\text{DAC}}$ = 625 MSPS, $f_{\text{OUT}}$ = 20.1 MHz 2x Interp, DAC A+B on                                                                      |          | 78   |     | dBc                 |

|                      |                                                                     | $f_{\text{DAC}}$ = 625 MSPS, $f_{\text{OUT}}$ = 70.1 MHz 2x Interp, DAC A+B on                                                                      |          | 64   |     |                     |

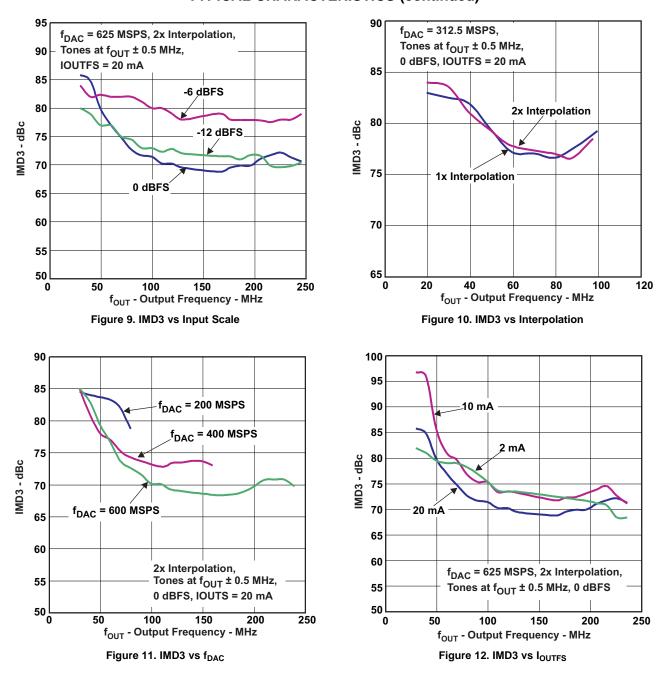

|                      |                                                                     | $f_{\text{DAC}}$ = 625 MSPS, $f_{\text{OUT}}$ = 30 $\pm$ 0.5 MHz 2x Interp, DAC A+B on                                                              |          | 82   |     |                     |

| IMD3                 | Third-order two-tone intermodulation                                | $f_{\text{DAC}}$ = 625 MSPS, $f_{\text{OUT}}$ = 50 $\pm$ 0.5 MHz 2x Interp, DAC A+B on                                                              |          | 80   |     | dBc                 |

|                      | distortion Each tone at –6 dBFS                                     | $f_{DAC}$ = 625 MSPS, $f_{OUT}$ = 150 $\pm$ 0.5 MHz 2x Interp, DAC A+B on,                                                                          |          | 69   |     |                     |

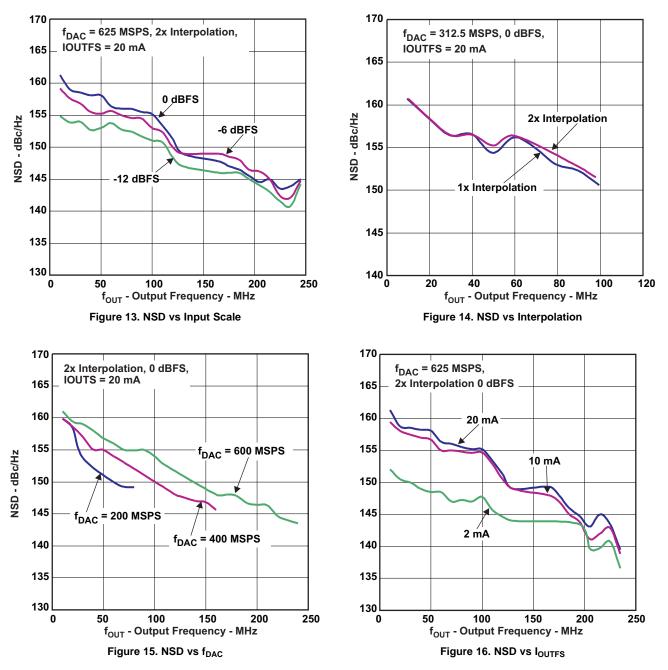

| NSD                  | Noise Spectral Density Single Tone at                               | $f_{DAC}$ = 625 MSPS, $f_{OUT}$ = 10.1 MHz 2x Interp, DAC A+B on                                                                                    |          | 161  |     | dDo/Ll=             |

| NSD                  | 0 dBm                                                               | $f_{DAC}$ = 625 MSPS, $f_{OUT}$ = 150.1 MHz 2x Interp, DAC A+B on                                                                                   |          | 150  |     | dBc/Hz              |

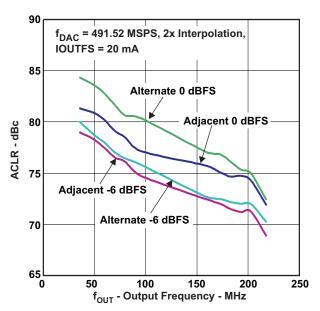

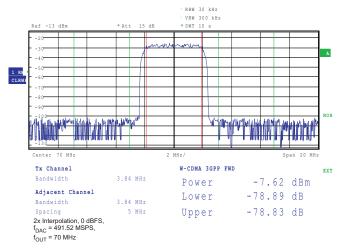

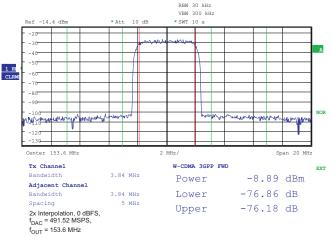

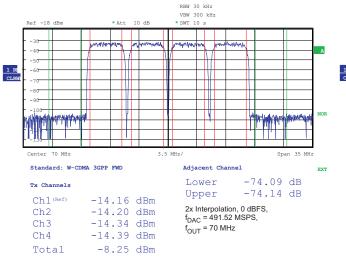

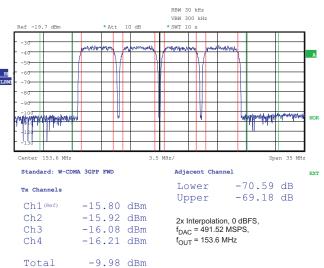

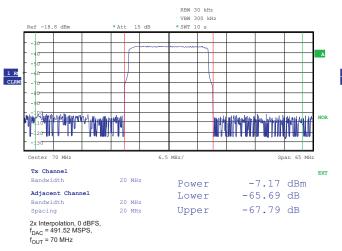

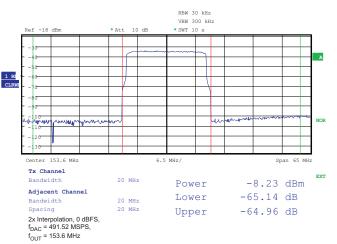

|                      | Adjacent Channel Leakage Ratio,                                     | $f_{DAC}$ = 491.52 MSPS, $f_{OUT}$ = 30.72 MHz 2x Interp, DAC A+B on                                                                                |          | 81   |     | dDo                 |

| WCDMA <sup>(3)</sup> | Single Carrier                                                      | $f_{\text{DAC}}$ = 491.52 MSPS, $f_{\text{OUT}}$ = 153.6 MHz 2x Interp, DAC A+B on                                                                  |          | 76   |     | dBc                 |

|                      | Alternate Channel Leakage Ratio,                                    | $f_{\text{DAC}}$ = 491.52 MSPS, $f_{\text{OUT}}$ = 30.72 MHz 2x Interp, DAC A+B on                                                                  |          | 84   |     | dBc                 |

|                      | Single Carrier                                                      | $f_{\text{DAC}}$ = 491.52 MSPS, $f_{\text{OUT}}$ = 153.6 MHz 2x Interp, DAC A+B on                                                                  |          | 77   |     | dBc                 |

|                      | Channel Isolation                                                   | $f_{DAC} = 625 \text{ MSPS}, f_{OUT} = 10 \text{ MHz}$                                                                                              |          | 84   |     | dBc                 |

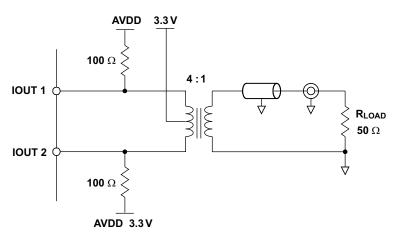

Measured single ended into 50  $\Omega$  load. (1)

(2) (3)

4:1 transformer output termination, 50  $\Omega$  doubly terminated load. Single carrier, W-CDMA with 3.84 MHz BW, 5-MHz spacing, centered at IF, PAR = 12dB. TESTMODEL 1, 10 ms

#### SLAS646A - DECEMBER 2009 - REVISED FEBRUARY 2010

## **ELECTRICAL CHARACTERISTICS – DIGITAL SPECIFICATIONS**

over recommended operating free-air temperature range, nominal supplies, IOUT<sub>FS</sub> = 20 mA (unless otherwise noted)

|                      | PARAMETER                                                                | TEST CONDITIONS                                                                                                              | MIN                     | TYP  | MAX                                   | UNIT   |

|----------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|---------------------------------------|--------|

| LVDS INT             | ERFACE: D[7:0]P/N, DATACLKP/N, FRAMEP/N <sup>(1)</sup>                   |                                                                                                                              |                         |      |                                       |        |

| f <sub>DATA</sub>    | Input data rate                                                          | Byte-wide DDR format<br>DATACLK frequency = 625 MHz                                                                          |                         |      | 312.5                                 | MSPS   |

| <i>c</i>             | Pute wide LV/DC date transfer rate                                       | 1x Interpolation                                                                                                             |                         |      | 1250                                  | MSPS   |

| f <sub>BUS</sub>     | Byte-wide LVDS data transfer rate                                        | 2x Interpolation                                                                                                             |                         |      | 1250                                  | 101343 |

| V <sub>A,B+</sub>    | Logic high differential input voltage threshold                          |                                                                                                                              | 175                     | 400  |                                       | mV     |

| V <sub>A,B-</sub>    | Logic low differential input voltage threshold                           |                                                                                                                              | -175                    | -400 |                                       | mV     |

| V <sub>COM</sub>     | Input Common Mode                                                        |                                                                                                                              | 1.0                     | 1.2  | 2.0                                   | V      |

| Z <sub>T</sub>       | Internal termination                                                     |                                                                                                                              | 85                      | 110  | 135                                   | Ω      |

| CL                   | LVDS Input capacitance                                                   |                                                                                                                              |                         | 2    |                                       | pF     |

| TIMING L             | VDS INPUTS: DATACLKP/N, double edge latching                             | g – See Figure 36                                                                                                            |                         |      |                                       |        |

| t <sub>s(DATA)</sub> | Setup time, D[7:0]P/N and FRAMEP/N, valid to either edge of DATACLKP/N   | FRAMEP/N latched on rising edge of<br>DATACLKP/N only                                                                        | 0                       |      |                                       | ps     |

| t <sub>h(DATA)</sub> | Hold time, D[7:0]P/N and FRAMEP/N, valid after either edge of DATACLKP/N | FRAMEP/N latched on rising edge of<br>DATACLKP/N only                                                                        | 400                     |      |                                       | ps     |

| t <sub>(FRAME)</sub> | FRAMEP/N pulse width                                                     | f <sub>DATACLK</sub> is DATACLK frequency in MHz                                                                             | 1/2f <sub>DATACLK</sub> |      |                                       | ns     |

| t_align              | Maximum offset between DATACLKP/N and<br>DACCLKP/N rising edges          | FIFO Bypass Mode only<br>f <sub>DACCLK</sub> is DACCLK frequency in MHz                                                      |                         |      | 1/2f <sub>DACCLK</sub><br>-0.55       | ns     |

| CLOCK IN             | IPUT (DACCLKP/N)                                                         | · · · · ·                                                                                                                    |                         |      | 1                                     |        |

|                      | Duty cycle                                                               |                                                                                                                              | 40%                     |      | 60%                                   |        |

|                      | Differential voltage <sup>(2)</sup>                                      |                                                                                                                              | 0.4                     | 1.0  |                                       | V      |

|                      | DACCLKP/N Input Frequency                                                |                                                                                                                              |                         |      | 625                                   | MHz    |

| OUTPUT               | STROBE (OSTRP/N)                                                         |                                                                                                                              |                         |      |                                       |        |

| f <sub>OSTR</sub>    | Frequency                                                                | $f_{OSTR} = f_{DACCLK} / (n \times 8 \times Interp)$ where n is any positive integer $f_{DACCLK}$ is DACCLK frequency in MHz |                         |      | f <sub>DACCLK</sub> /<br>(8 x interp) | MHz    |

|                      | Duty cycle                                                               |                                                                                                                              | 40%                     |      | 60%                                   |        |

|                      | Differential voltage                                                     |                                                                                                                              | 0.4                     | 1.0  |                                       | V      |

|                      | STRP/N Input: DACCLKP/N rising edge latching                             |                                                                                                                              |                         |      | ļ                                     |        |

| t <sub>s(OSTR)</sub> | Setup time, OSTRP/N valid to rising edge of<br>DACCLKP/N                 |                                                                                                                              |                         | 200  |                                       | ps     |

| t <sub>h(OSTR)</sub> | Hold time, OSTRP/N valid after rising edge of<br>DACCLKP/N               |                                                                                                                              |                         | 200  |                                       | ps     |

| CMOS INT             | TERFACE: ALARM_SDO, SDIO, SCLK, SDENB, RI                                | ESETB, TXENABLE                                                                                                              |                         |      | I                                     |        |

| VIH                  | High-level input voltage                                                 |                                                                                                                              | 1.25                    |      |                                       | V      |

| VIL                  | Low-level input voltage                                                  |                                                                                                                              |                         |      | 0.54                                  | V      |

| IIH                  | High-level input current                                                 |                                                                                                                              | -40                     |      | 40                                    | μA     |

| <br>I <sub>IL</sub>  | Low-level input current                                                  |                                                                                                                              | -40                     |      | 40                                    | μA     |

| CI                   | CMOS Input capacitance                                                   |                                                                                                                              |                         | 2    |                                       | pF     |

|                      | SDO, SDIO                                                                | lload = -100 μA                                                                                                              | DIGVDD18-0              | .2   |                                       | V      |

| V <sub>OH</sub>      | SDO, SDIO                                                                | Iload = -2 mA                                                                                                                | 0.8 x DIGVDD            |      |                                       | V      |

|                      | SDO, SDIO                                                                | $Iload = 100 \ \mu A$                                                                                                        |                         |      | 0.2                                   | V      |

| V <sub>OL</sub>      | SDO, SDIO                                                                | lload = 2 mA                                                                                                                 |                         |      | 0.5                                   | v      |

See LVDS INPUTS section for terminology.

Driving the clock input with a differential voltage lower than 1 V will result in degraded performance.

## ELECTRICAL CHARACTERISTICS – DIGITAL SPECIFICATIONS (continued)

over recommended operating free-air temperature range, nominal supplies,  $IOUT_{FS} = 20$  mA (unless otherwise noted)

|                       | PARAMETER                                     | TEST CONDITIONS                                 | MIN TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------|-------------------------------------------------|---------|-----|------|

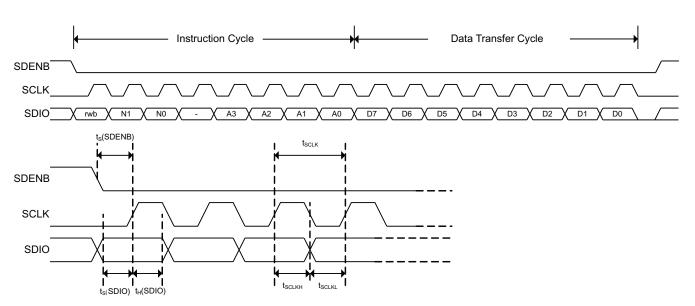

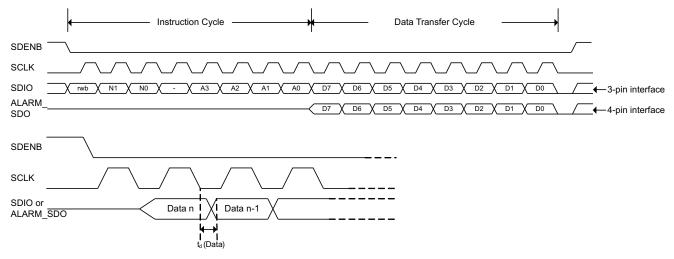

| SERIAL PO             | ORT TIMING – See Figure 32 and Figure 33      |                                                 | I       | I   |      |

| t <sub>s(SDENB)</sub> | Setup time, SDENB to rising edge of SCLK      |                                                 | 20      |     | ns   |

| t <sub>s(SDIO)</sub>  | Setup time, SDIO valid to rising edge of SCLK |                                                 | 10      |     | ns   |

| t <sub>h(SDIO)</sub>  | Hold time, SDIO valid to rising edge of SCLK  |                                                 | 5       |     | ns   |

| t <sub>(SCLK)</sub>   | Period of SCLK                                | Register CONFIG5 read (temperature sensor read) | 1       |     | μS   |

| (002.1)               |                                               | All other registers                             | 100     |     | ns   |

| t <sub>(SCLKH)</sub>  | High time of SCLK                             | Register CONFIG5 read (temperature sensor read) | 0.4     |     | μs   |

| (OOLINI)              | Ŭ                                             | All other registers                             | 40      |     | ns   |

| t <sub>(SCLKL)</sub>  | Low time of SCLK                              | Register CONFIG5 read (temperature sensor read) | 0.4     |     | μs   |

| (OOLINE)              |                                               | All other registers                             | 40      |     | ns   |

| t <sub>d(Data)</sub>  | Data output delay after falling edge of SCLK  |                                                 | 10      |     | ns   |

| t <sub>RESET</sub>    | Minimum RESETB pulsewidth                     |                                                 | 25      |     | ns   |

www.ti.com

#### SLAS646A – DECEMBER 2009 – REVISED FEBRUARY 2010

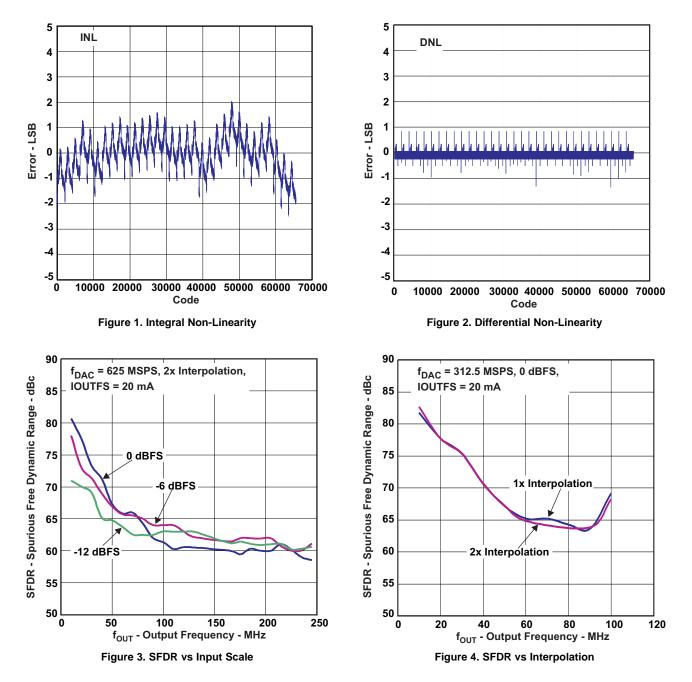

#### **TYPICAL CHARACTERISTICS**

Texas

INSTRUMENTS

www.ti.com

#### www.ti.com

TYPICAL CHARACTERISTICS (continued)

## **TYPICAL CHARACTERISTICS (continued)**

ÈXAS

**INSTRUMENTS**

www.ti.com

## DAC3282

#### SLAS646A – DECEMBER 2009 – REVISED FEBRUARY 2010

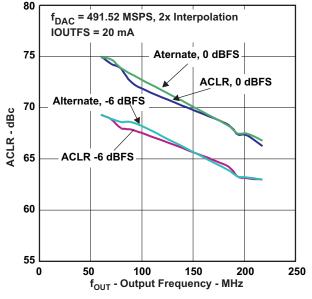

#### Figure 17. Single Carrier WCDMA ACLR vs Input Scale

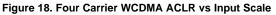

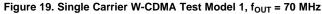

Figure 20. Single Carrier W-CDMA Test Model 1,  $f_{OUT} = 153.6 \text{ MHz}$

**TYPICAL CHARACTERISTICS (continued)**

TEXAS INSTRUMENTS

www.ti.com

#### SLAS646A-DECEMBER 2009-REVISED FEBRUARY 2010

**TYPICAL CHARACTERISTICS (continued)**

Figure 21. Four Carrier W-CDMA Test Model 1, f<sub>OUT</sub> = 70 MHz

Figure 22. Four Carrier W-CDMA Test Model 1, f<sub>OUT</sub> = 153.6 MHz

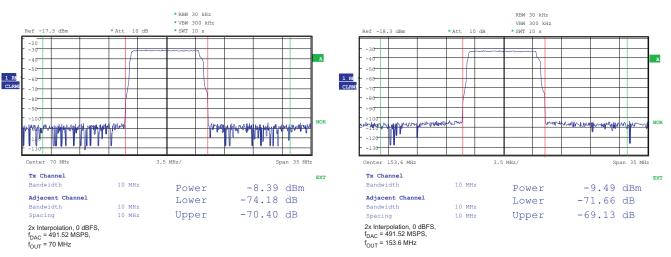

Figure 23. 10MHz Single Carrier LTE,  $f_{OUT}$  = 70 MHz

Figure 24. 10MHz Single Carrier LTE, f<sub>OUT</sub> = 153.6 MHz

#### www.ti.com

### **TYPICAL CHARACTERISTICS (continued)**

#### Figure 25. 20MHz Single Carrier LTE, f<sub>OUT</sub> = 70 MHz

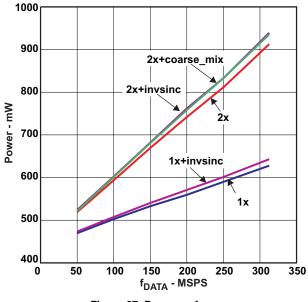

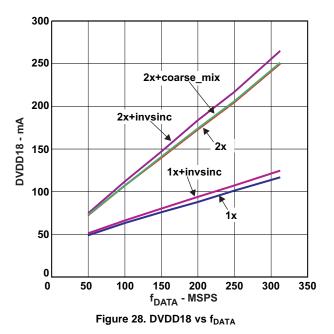

Figure 27. Power vs f<sub>DATA</sub>

Figure 26. 20MHz Single Carrier LTE, f<sub>OUT</sub> = 153.6 MHz

## **TYPICAL CHARACTERISTICS (continued)**

www.ti.com

#### **DEFINITION OF SPECIFICATIONS**

Adjacent Carrier Leakage Ratio (ACLR): Defined for a 3.84Mcps 3GPP W-CDMA input signal measured in a 3.84MHz bandwidth at a 5MHz offset from the carrier with a 12dB peak-to-average ratio.

Analog and Digital Power Supply Rejection Ratio (APSSR, DPSSR):Defined as the percentage error in the ratio of the delta IOUT and delta supply voltage normalized with respect to the ideal IOUT current.

**Differential Nonlinearity (DNL):** Defined as the variation in analog output associated with an ideal 1 LSB change in the digital input code.

**Gain Drift:** Defined as the maximum change in gain, in terms of ppm of full-scale range (FSR) per °C, from the value at ambient (25°C) to values over the full operating temperature range.

Gain Error: Defined as the percentage error (in FSR%) for the ratio between the measured full-scale output current and the ideal full-scale output current.

**Integral Nonlinearity (INL):** Defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero scale to full scale.

**Intermodulation Distortion (IMD3):** The two-tone IMD3 is defined as the ratio (in dBc) of the 3rd-order intermodulation distortion product to either fundamental output tone.

**Offset Drift:** Defined as the maximum change in DC offset, in terms of ppm of full-scale range (FSR) per °C, from the value at ambient (25°C) to values over the full operating temperature range.

**Offset Error:** Defined as the percentage error (in FSR%) for the ratio between the measured mid-scale output current and the ideal mid-scale output current.

**Output Compliance Range:** Defined as the minimum and maximum allowable voltage at the output of the current-output DAC. Exceeding this limit may result reduced reliability of the device or adversely affecting distortion performance.

**Reference Voltage Drift:** Defined as the maximum change of the reference voltage in ppm per °C from value at ambient (25°C) to values over the full operating temperature range.

**Spurious Free Dynamic Range (SFDR):** Defined as the difference (in dBc) between the peak amplitude of the output signal and the peak spurious signal.

**Signal to Noise Ratio (SNR):** Defined as the ratio of the RMS value of the fundamental output signal to the RMS sum of all other spectral components below the Nyquist frequency, including noise, but excluding the first six harmonics and dc.

www.ti.com

#### APPLICATION INFORMATION

#### SERIAL INTERFACE

The serial port of the DAC3282 is a flexible serial interface which communicates with industry standard microprocessors and microcontrollers. The interface provides read/write access to all registers used to define the operating modes of DAC3282. It is compatible with most synchronous transfer formats and can be configured as a 3 or 4 pin interface by **sif4\_ena** in register **CONFIG23**. In both configurations, SCLK is the serial interface input clock and SDENB is serial interface enable. For 3 pin configuration, SDIO is a bidirectional pin for both data in and data out. For 4 pin configuration, SDIO is data in only and ALARM\_SDO is data out only. Data is input into the device with the rising edge of SCLK.

Each read/write operation is framed by signal SDENB (Serial Data Enable Bar) asserted low for 2 to 5 bytes, depending on the data length to be transferred (1–4 bytes). The first frame byte is the instruction cycle which identifies the following data transfer cycle as read or write, how many bytes to transfer, and what address to transfer the data. Table 1 indicates the function of each bit in the instruction cycle and is followed by a detailed description of each bit. Frame bytes 2 to 5 comprise the data transfer cycle.

#### Table 1. Instruction Byte of the Serial Interface

|             | MSB |    |    |    |    |    |    | LSB |

|-------------|-----|----|----|----|----|----|----|-----|

| Bit         | 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0   |

| Description | R/W | N1 | N0 | A4 | A3 | A2 | A1 | A0  |

- **R/W** Identifies the following data transfer cycle as a read or write operation. A high indicates a read operation from DAC3282 and a low indicates a write operation to DAC3282.

- [N1 : N0] Identifies the number of data bytes to be transferred per Table 2. Data is transferred MSB first.

| N1 | N0 | Description      |

|----|----|------------------|

| 0  | 0  | Transfer 1 Byte  |

| 0  | 1  | Transfer 2 Bytes |

| 1  | 0  | Transfer 3 Bytes |

| 1  | 1  | Transfer 4 Bytes |

## Table 2. Number of Transferred Bytes Within One Communication Frame

[A4 : A0] Identifies the address of the register to be accessed during the read or write operation. For multi-byte transfers, this address is the starting address. Note that the address is written to the DAC3282 MSB first and counts down for each byte.

Figure 32 shows the serial interface timing diagram for a DAC3282 write operation. SCLK is the serial interface clock input to DAC3282. Serial data enable SDENB is an active low input to DAC3282. SDIO is serial data in. Input data to DAC3282 is clocked on the rising edges of SCLK.

SLAS646A – DECEMBER 2009 – REVISED FEBRUARY 2010

Figure 32. Serial Interface Write Timing Diagram

Figure 33 shows the serial interface timing diagram for a DAC3282 read operation. SCLK is the serial interface clock input to DAC3282. Serial data enable SDENB is an active low input to DAC3282. SDIO is serial data in during the instruction cycle. In 3 pin configuration, SDIO is data out from DAC3282 during the data transfer cycle(s), while ALARM\_SDO is in a high-impedance state. In 4 pin configuration, ALARM\_SDO is data out from DAC3282 during the data transfer cycle(s). At the end of the data transfer, ALARM\_SDO will output low on the final falling edge of SCLK until the rising edge of SDENB when it will 3-state.

Figure 33. Serial Interface Read Timing Diagram

www.ti.com

#### **REGISTER DESCRIPTIONS**

## **Register Map**

| Table 3. Register Map | Table | 3. | Register | Мар |

|-----------------------|-------|----|----------|-----|

|-----------------------|-------|----|----------|-----|

| Name      | Address | Default | (MSB)<br>Bit 7                                                      | Bit 6                                                | Bit 5                    | Bit 4           | Bit 3               | Bit 2               | Bit 1                | (LSB)<br>Bit 0       |  |

|-----------|---------|---------|---------------------------------------------------------------------|------------------------------------------------------|--------------------------|-----------------|---------------------|---------------------|----------------------|----------------------|--|

| CONFIG0   | 0x00    | 0x70    | qmc_offset_ena fifo_ena fifo_reset_ena multi_sync_ena alarm_out_ena |                                                      |                          |                 |                     | alarm_pol           | mixer_               | func(1:0)            |  |

| CONFIG1   | 0x01    | 0x11    | unused                                                              | unused                                               | unused                   | fir_ena         | fir4_ena            | iotest_ena          | unused               | twos                 |  |

| CONFIG2   | 0x02    | 0x00    | unused                                                              | unused                                               | unused                   | unused          |                     | output_de           | elay(3:0)            |                      |  |

| CONFIG3   | 0x03    | 0x10    | 64cnt_ena                                                           | 64cnt_ena unused unused fifo_offset(2:0) ala<br>2awa |                          |                 |                     |                     |                      | alarm_<br>1away_ena  |  |

| CONFIG4   | 0x04    | 0XFF    |                                                                     | coarse_daca(3:0) coarse_dacb(3:0)                    |                          |                 |                     |                     |                      |                      |  |

| CONFIG5   | 0x05    | N/A     |                                                                     | tempdata(7:0)                                        |                          |                 |                     |                     |                      |                      |  |

| CONFIG6   | 0x06    | 0x00    | unused                                                              | unused alarm_mask(6:0)                               |                          |                 |                     |                     |                      |                      |  |

| CONFIG7   | 0x07    | 0x00    | unused                                                              | alarm_from_<br>zerochk                               | alarm_fifo_<br>collision | reserved        | alarm_from_ iotest  | unused              | alarm_fifo_<br>2away | alarm_fifo_<br>1away |  |

| CONFIG8   | 0x08    | 0x00    |                                                                     | iotest_results(7:0)                                  |                          |                 |                     |                     |                      |                      |  |

| CONFIG9   | 0x09    | 0x7A    |                                                                     | iotest_pattern0(7:0)                                 |                          |                 |                     |                     |                      |                      |  |

| CONFIG10  | 0x0A    | 0xB6    |                                                                     | iotest_pattern1(7:0)                                 |                          |                 |                     |                     |                      |                      |  |

| CONFIG11  | 0x0B    | 0xEA    |                                                                     |                                                      |                          | iotest_pattern2 | 2(7:0)              |                     |                      |                      |  |

| CONFIG12  | 0x0C    | 0x45    |                                                                     | iotest_pattern3(7:0)                                 |                          |                 |                     |                     |                      |                      |  |

| CONFIG13  | 0x0D    | 0x1A    |                                                                     | iotest_pattern4(7:0)                                 |                          |                 |                     |                     |                      |                      |  |

| CONFIG14  | 0x0E    | 0x16    |                                                                     | iotest_pattern5(7:0)                                 |                          |                 |                     |                     |                      |                      |  |

| CONFIG15  | 0x0F    | 0xAA    |                                                                     | iotest_pattern6(7:0)                                 |                          |                 |                     |                     |                      |                      |  |

| CONFIG16  | 0x10    | 0xC6    |                                                                     |                                                      |                          | iotest_pattern  | 7(7:0)              |                     |                      |                      |  |

| CONFIG17  | 0x11    | 0x00    | rese                                                                | rved                                                 | reserved                 | reserved        |                     | reser               | ved                  |                      |  |

| CONFIG18  | 0x12    | 0x02    |                                                                     | reserved                                             |                          | reserved        | daca_<br>complement | dacb_<br>complement | clkdiv_<br>sync_ena  | unused               |  |

| CONFIG19  | 0x13    | 0x00    | bequalsa                                                            | aequalsb                                             | reserved                 | unused          | unused              | unused              | multi_<br>sync_sel   | rev                  |  |

| CONFIG20  | 0x14    | 0x00    |                                                                     |                                                      |                          | qmc_offseta(    | (7:0)               |                     |                      |                      |  |

| CONFIG21  | 0x15    | 0x00    |                                                                     |                                                      |                          | qmc_offsetb(    | (7:0)               |                     |                      |                      |  |

| CONFIG22  | 0x16    | 0x00    |                                                                     |                                                      | qmc_offseta(12:8         | )               |                     | unused              | unused               | unused               |  |

| CONFIG23  | 0x17    | 0x00    |                                                                     |                                                      | qmc_offsetb(12:8         | )               |                     | sif4_ena            | clkpath_<br>sleep_a  | clkpath_<br>sleep_b  |  |

| CONFIG24  | 0x18    | 0x83    | tsense_ena                                                          | clkrecv_sleep                                        | unused                   | reserved        | sleepb              | sleepa              | reserved             | reserved             |  |

| CONFIG25  | 0x19    | 0x00    |                                                                     |                                                      | reserved                 |                 |                     | extref_ena          | reserved             | reserved             |  |

| CONFIG26  | 0x1A    | 0x00    | unused                                                              | unused                                               | unused                   | unused          | unused              |                     | reserved             |                      |  |

| CONFIG27  | 0x1B    | 0x00    |                                                                     |                                                      |                          | reserved        |                     |                     |                      |                      |  |

| CONFIG28  | 0x1C    | 0x00    |                                                                     |                                                      |                          | reserved        |                     |                     |                      |                      |  |

| CONFIG29  | 0x1D    | 0x00    |                                                                     |                                                      |                          | reserved        |                     |                     |                      |                      |  |

| CONFIG30  | 0x1E    | 0x00    |                                                                     |                                                      |                          | reserved        |                     |                     |                      |                      |  |

| VERSION31 | 0x1F    | 0x43    | device                                                              | id(1:0)                                              |                          |                 | version(5:0)        |                     |                      |                      |  |

SLAS646A - DECEMBER 2009-REVISED FEBRUARY 2010

#### Register name: CONFIG0 – Address: 0x00, Default: 0x70

| Register<br>Name | Address | Bit        | Name                                                                                                                           | Function                                                                                                           |                                                                                                                     | Default<br>Value |             |        |           |                                                                 |

|------------------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|-------------|--------|-----------|-----------------------------------------------------------------|

| CONFIG0          | 0x00    | 7          | qmc_offset_ena                                                                                                                 | When asserted the DAC offset correction is enabled                                                                 |                                                                                                                     | 0                |             |        |           |                                                                 |

|                  | 6       | fifoin_ena | When asserted the FIFO is enabled. When the FIFO is bypassed DACCCLKP/N and DATACLKP/N must be aligned to within $t_{align}$ . |                                                                                                                    |                                                                                                                     |                  |             |        |           |                                                                 |

|                  |         | 5          | fifo_reset_ena                                                                                                                 | Allows the FRAME input to act as a FIFO write reset                                                                | when asserted                                                                                                       | 1                |             |        |           |                                                                 |