## **PRELIMINARY**

**UniClock CY22U1**

# Single Output, Low Power Programmable Clock Generator

## **Features**

- Small Footprint, 8-Pin QFN 1.7 x 1.7 x 0.6 mm<sup>3</sup> Package

- Low Power and Low Jitter Operation

- Multiple Operating Voltages:

- ☐ CY22U1S: 2.5V, 3.0V, or 3.3V

- □ CY22U1L: 1.8V

- Programmable Single Output Clock Generator Frequency Range:

- □ 1 to 200 MHz

- Crystal or External Reference Clock Input Frequency Range:

- □ Fundamental Tuned Crystal: 8 to 48 MHz

- □ External Reference Clock: 1 to 166 MHz

- Programmable Capacitor Tuning Array

- Programmable PD# or OE Control Pin

- Programmable Asynchronous or Synchronous OE and PD# Modes

### **Benefits**

- Services digital televisions and displays, set top boxes, multifunction printers, and a variety of consumer electronics applications.

- Saves PCB space due to small form factor.

- Enables quick turnaround and flexibility and adaptability to design changes through programmability.

- Enables synthesis of highly accurate and stable output clock frequencies with zero or low PPM error.

- Enables fine tuning of output clock frequency by adjusting the crystal load C<sub>Load</sub> using programmable internal capacitors.

- Lowers clock solution cost by pairing a high frequency PLL programmability with a low cost, low frequency crystal.

- Enables low power during the power down or output disable function.

- Provides flexibility for system applications through selectable asynchronous or synchronous output enable and disable.

Cypress Semiconductor Corporation

Document Number: 001-50320 Rev. \*C

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised August 10, 2009

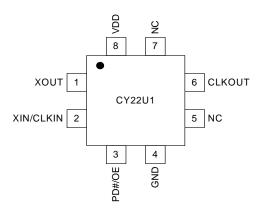

## **Pinouts**

Figure 1. Pin Diagram - CY22U1 8-Pin 1.7 x 1.7 mm<sup>2</sup> QFN

Table 1. Pin Definitions - CY22U1 8-Pin 1.7 x 1.7 mm<sup>2</sup> QFN

| Pin Number | Name      | Ю      | Description                                                                                           |

|------------|-----------|--------|-------------------------------------------------------------------------------------------------------|

| 1          | XOUT      | Output | Crystal output. Float for external clock input.                                                       |

| 2          | XIN/CLKIN | Input  | Crystal or external clock input.                                                                      |

| 3          | PD#/OE    | Input  | Multifunction pin. Active low power down or active high output enable pin. Has weak internal pull up. |

| 4          | GND       | Power  | Power supply ground.                                                                                  |

| 5          | NC        | -      | No connect. Pin has no internal connection.                                                           |

| 6          | CLKOUT    | Output | Programmable clock output. Output voltage depends on VDD. Has weak internal pull down.                |

| 7          | NC        | _      | No connect. Pin has no internal connection.                                                           |

| 8          | VDD       | Power  | Programmable power supply: CY22U1S: 2.5V, 3.0V, 3.3V (standard voltage) CY22U1L: 1.8V (low voltage)   |

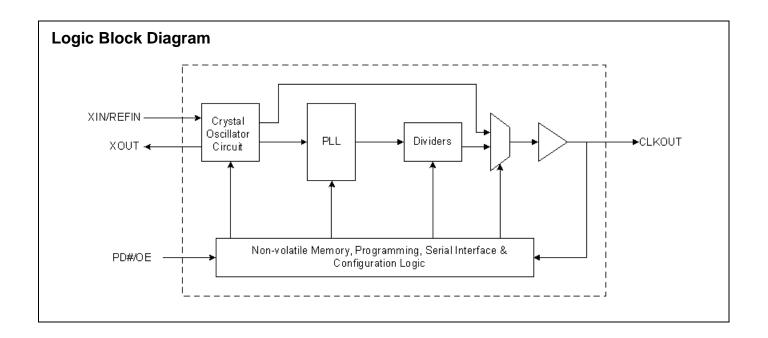

## **Functional Description**

The UniClock CY22U1 is a programmable, high accuracy, PLL-based clock generator device designed to replace crystals and crystal oscillators and save on cost and board space, while increasing reliability. The low jitter and accurate outputs makes this device suitable for use in digital televisions and displays, set top boxes, multifunction printers, and a variety of consumer electronics applications.

The device has several programmable options listed in the section Programmable Features on page 4. The entire configuration is one time programmable.

### Configurable PLL

The device uses a programmable PLL to generate output frequencies from 1 to 200 MHz. The high resolution of the PLL and flexible output dividers provide this flexibility.

### **Input Reference Clock Option**

There is an option of a crystal or clock signal for the input reference clock. The frequency range for crystal (XIN) is 8 MHz to 48 MHz, while the range for an external reference clock (CLKIN) is 1 MHz to 166 MHz. A PLL bypass mode enables this device to be used as a crystal oscillator.

## **Multiple VDD Power Supply Option**

The device has programmable power supply options. The operating supply voltages are 2.5V, 3.0V, or 3.3V for CY22U1S and 1.8V for CY22U1L.

## **Power Management Feature**

The UniClock CY22U1 offers PD# (active LOW) and OE (active HIGH) functions. When the power down mode is selected (PD# =0), the oscillator and PLL are placed in a low supply current standby mode and the output is tristated and weakly pulled LOW. The oscillator and PLL circuits must relock when the part exits the power down mode. If the output is disabled (OE=0), the output is tristated and weakly pulled LOW. In this mode, the oscillator and PLL circuits continue to operate, which enables a rapid return to normal operation when the output is enabled.

In addition, the PD# or OE mode can be programmed to occur asynchronously or synchronously with respect to the output signal. When the asynchronous setting is used, entering power down or disabling the output occurs immediately (enabling logic delays), regardless of the position in the clock cycle. Similarly, exiting power down or enabling the output occurs immediately with no guarantee of full output clock pulses. However, when the synchronous setting is used, the part waits for a falling edge at the output before entering power down or disabling the output. This prevents output glitches. The first output pulse is guaranteed to be a full clock pulse when enabling outputs with a synchronous OE pin. The first output pulse is not guaranteed to be a full clock when exiting power down in synchronous or asynchronous mode.

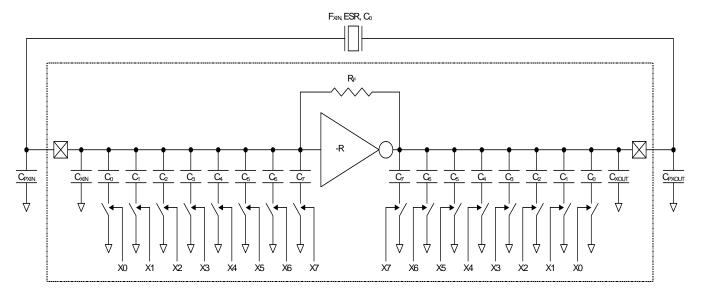

## **Output Frequency Tuning**

The UniClock CY22U1 contains an on-chip oscillator with a built in programmable capacitor array for fine tuning of the output frequency. The capacitive load seen by the crystal is adjusted by programming the memory bits. This feature can compensate for crystal variations or provide a more accurate synthesized frequency. Figure 2 shows the crystal oscillator tuning circuit block diagram.

## **Crystal Oscillator Tuning Circuit**

**Table 2. Crystal Oscillator Tuning Capacitor Values**

| Сар            | Value <sup>[1]</sup> | Unit |

|----------------|----------------------|------|

| C <sub>7</sub> | 5.000                | pF   |

| C <sub>6</sub> | 2.500                | pF   |

| C <sub>5</sub> | 1.250                | pF   |

| C <sub>4</sub> | 0.625                | pF   |

| C <sub>3</sub> | 0.313                | pF   |

| C <sub>2</sub> | 0.156                | pF   |

| C <sub>1</sub> | 0.078                | pF   |

| $C_0$          | 0.039                | pF   |

Figure 2. Crystal Oscillator Tuning Block Diagram

#### Note

<sup>1.</sup> The capacitor values are nominal.

**Programming Support**

The device is available in factory and field programmable

versions. The CyClockMaker Programming kit along with CyClockDesigner configuration software is used to field program

the device. For specific programming needs, contact your local

Cypress field application engineer (FAE) or sales representative.

## **Programmable Features**

The following list of features can be custom configured:

- PLL frequency and output divider value

- Oscillator tuning (crystal load) capacitance value

- Direct oscillator output (PLL bypass)

- High or low power supply voltage operation

- Power management mode (OE or PD#)

- Power management timing (synchronous or asynchronous)

## **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

Table 3. Absolute Maximum Ratings

| Parameter <sup>[2]</sup> | Description                              | Condition                   | Min         | Max                  | Unit  |

|--------------------------|------------------------------------------|-----------------------------|-------------|----------------------|-------|

| $V_{DD}$                 | Supply voltage, 2.5V/3.0V/3.3V range     |                             | -0.5        | 4.4                  | V     |

|                          | Supply voltage, 1.8V range               |                             | -0.5        | 2.8                  | V     |

| V <sub>IN</sub>          | Input voltage                            | Relative to V <sub>SS</sub> | -0.5        | V <sub>DD</sub> +0.5 | V     |

| T <sub>S</sub>           | Temperature, storage                     | Non functional              | <b>-</b> 55 | +125                 | °C    |

| T <sub>J</sub>           | Temperature, junction                    | Non functional              | -40         | +125                 | °C    |

| ESD <sub>HBM</sub>       | ESD protection (human body model)        | JEDEC EIA/JESD22-A114-E     | 2000        | _                    | Volts |

| D <sub>RET</sub>         | Data retention at T <sub>J</sub> = 125°C |                             | 10          | _                    | Yr.   |

| PR <sub>CYCLE</sub>      | Maximum programming cycle                |                             |             | 1                    | •     |

| UL-94                    | Flammability rating                      |                             | V           | /-0 at 1/8 in.       |       |

| MSL                      | Moisture sensitivity level               |                             |             | 3                    |       |

## **Recommended Operating Conditions**

| Parameter <sup>[2]</sup> | Description                                                                                         | Min | Тур | Max | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $V_{DD}$                 | Supply voltage, 1.8V operating range for CY22U1L                                                    | 1.6 | _   | 2.0 | V    |

|                          | Supply voltage, 2.5V operating range for CY22U1S                                                    | 2.2 | _   | 2.8 | V    |

|                          | Supply voltage, 3.0V operating range for CY22U1S                                                    | 2.7 | -   | 3.3 | V    |

|                          | Supply voltage, 3.3V operating range for CY22U1S                                                    | 3.0 | _   | 3.6 | V    |

| T <sub>AC</sub>          | Commercial ambient temperature                                                                      |     | -   | 70  | °C   |

| T <sub>AI</sub>          | Industrial ambient temperature                                                                      |     | _   | 85  | °C   |

| T <sub>PU</sub>          | Power up time for V <sub>DD</sub> to reach minimum specified voltage (power ramp must be monotonic) |     | -   | 500 | ms   |

| T <sub>PD</sub>          | Minimum pulse width of PD#/OE input                                                                 | 100 | _   | _   | ns   |

| C <sub>OUT</sub>         | Output load capacitance                                                                             | _   | _   | 15  | pF   |

#### Note

Document Number: 001-50320 Rev. \*C Page 4 of 11

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation

of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum

Rated Conditions for extended periods may affect device reliability or cause permanent device damage.

## **DC Electrical Specifications**

| Parameter <sup>[3]</sup> | Description                      | Test Conditions                                    | Min                   | Тур    | Max                                 | Unit     |

|--------------------------|----------------------------------|----------------------------------------------------|-----------------------|--------|-------------------------------------|----------|

| V <sub>IL1</sub>         | Input low voltage of PD#/OE      |                                                    | _                     | _      | 0.2*V <sub>DD</sub>                 | V        |

| V <sub>IH1</sub>         | Input high voltage of PD#/OE     |                                                    | 0.8*V <sub>DD</sub>   | _      | -                                   | V        |

| $V_{IL2}$                | Input low voltage of REFIN       | CY22U1S                                            | -0.2                  | _      | 0.4                                 | V        |

|                          |                                  | CY22U1L                                            | -0.2                  | _      | 0.4                                 | V        |

| V <sub>IH2</sub>         | Input high voltage of REFIN      | CY22U1S                                            | 1.2                   | _      | 2.1                                 | V        |

|                          |                                  | CY22U1L                                            | 1.2                   | _      | V <sub>DD</sub> +0.3 <sup>[4]</sup> | V        |

| V <sub>OL1</sub>         | Output low voltage               | I <sub>OL</sub> = 8 mA, V <sub>DD</sub> = 3.0/3.3V | _                     | _      | 0.4                                 | V        |

| V <sub>OH1</sub>         | Output high voltage              | I <sub>OH</sub> = 8 mA, V <sub>DD</sub> = 3.0/3.3V | V <sub>DD</sub> – 0.4 | _      | _                                   | V        |

| $V_{OL2}$                | Output low voltage               | I <sub>OL</sub> = 4 mA, V <sub>DD</sub> = 1.8/2.5V | _                     | _      | 0.1*V <sub>DD</sub>                 | V        |

| $V_{OH2}$                | Output high voltage              | I <sub>OH</sub> = 4 mA, V <sub>DD</sub> = 1.8/2.5V | 0.9*V <sub>DD</sub>   | _      | _                                   | V        |

| I <sub>IL</sub>          | Input low current                | Input = V <sub>SS</sub>                            | _                     | <1     | 10                                  | μА       |

| I <sub>IH</sub>          | Input high current               | Input = V <sub>DD</sub>                            | _                     | <1     | 10                                  | μА       |

| I <sub>OZL</sub>         | Output leakage current           | Output = V <sub>SS</sub> , Tj = 85°C               | _                     | <1     | 5                                   | μА       |

| I <sub>OZH</sub>         | Output leakage current           | Output = V <sub>DD</sub>                           | _                     | _      | 50                                  | μА       |

| $I_{DD}$                 | Power supply current for CY22U1L | F <sub>OUT</sub> = 50 MHz, 15 pF load              | _                     | _      | 7.5                                 | mA       |

|                          |                                  | F <sub>OUT</sub> = 200MHz, 15 pF load              | _                     | _      | 15                                  | mA       |

|                          | Power supply current for CY22U1S | F <sub>OUT</sub> = 50 MHz, 15 pF load              | _                     | _      | 10                                  | mA       |

|                          |                                  | F <sub>OUT</sub> = 200 MHz, 15 pF load             | _                     | _      | 25                                  | mA       |

| I <sub>PD</sub>          | Power down current               | Tj = 85°C                                          | _                     | 25     | 50                                  | μА       |

| R <sub>UP</sub>          | Input pull up resistors          | PD#/OE = low<br>PD#/OE = high                      | 1<br>100              | _<br>_ | 6<br>250                            | MΩ<br>kΩ |

| R <sub>DN</sub>          | Output pull down resistors       |                                                    | 500                   | _      | 1500                                | kΩ       |

| C <sub>IN</sub>          | Input capacitance of PD#/OE pin  |                                                    | _                     | _      | 7                                   | pF       |

Note

3. Parameters are guaranteed by design and characterization. Not 100% tested in production.

4.  $V_{IH2}$  absolute maximum value is 2.1V. For  $V_{DD}$  = 1.6V to 1.8V, the maximum  $V_{IH2}$  is  $V_{DD}$  + 0.3V.

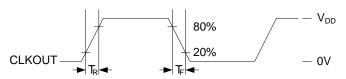

## **AC Electrical Specifications**

| Parameter <sup>[6]</sup>  | Description                                                         | Test Conditions                                                                                                 | Min         | Тур            | Max             | Unit                                         |

|---------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------|----------------|-----------------|----------------------------------------------|

| F <sub>IN</sub> (Crystal) | Crystal frequency range (XIN)                                       |                                                                                                                 | 8           | _              | 48              | MHz                                          |

| F <sub>IN</sub> (Clock)   | Clock frequency range (REFIN)                                       |                                                                                                                 | 1           | _              | 166             | MHz                                          |

| F <sub>CLK</sub>          | Output frequency                                                    |                                                                                                                 | 1           | _              | 200             | MHz                                          |

| T <sub>R</sub>            | Output rise time                                                    | Measured from 20% to 80% $V_{DD,}$ $C_{OUT}$ = 15 pF                                                            | _           | _              | 1.5             | ns                                           |

| T <sub>F</sub>            | Output fall time                                                    | Measured from 80% to 20% $V_{DD,}$ $C_{OUT}$ = 15 pF                                                            | _           | _              | 1.5             | ns                                           |

| DC                        | Output clock duty cycle                                             | Using PLL as a source                                                                                           | 45          | 50             | 55              | %                                            |

| T <sub>CCJ</sub>          | Cycle-to-cycle jitter of CLKOUT using PLL                           | $F_{OUT} \ge 100 \text{ MHz}$<br>$100 \text{ MHz} \ge F_{OUT} \ge 50 \text{ MHz}$<br>$F_{OUT} < 50 \text{ MHz}$ | -<br>-<br>- | 75<br>150<br>– | 125<br>200<br>1 | ps<br>ps<br>%T <sub>OUT</sub> <sup>[5]</sup> |

| T <sub>P</sub>            | Period jitter of CLKOUT using PLL                                   | $F_{OUT} \ge 100 \text{ MHz}$<br>$100 \text{ MHz} \ge F_{OUT} \ge 50 \text{ MHz}$<br>$F_{OUT} < 50 \text{ MHz}$ |             | 75<br>150<br>– | 125<br>200<br>1 | ps<br>ps<br>%T <sub>OUT</sub> <sup>[5]</sup> |

| T <sub>PO,CLK</sub>       | Power on time for output clock                                      |                                                                                                                 | -           | _              | 5               | ms                                           |

| T <sub>PU,CLK</sub>       | Power up time from power down for output clock                      |                                                                                                                 | _           | _              | 5               | ms                                           |

| T <sub>PD,ASYNC</sub>     | Time from falling edge of PD# to stopped outputs, asynchronous mode |                                                                                                                 | _           | _              | 100             | ns                                           |

| T <sub>PD,SYNC</sub>      | Time from falling edge of PD# to stopped outputs, synchronous mode  |                                                                                                                 | _           | _              | 1.5T + 100      | ns                                           |

| T <sub>OD,ASYNC</sub>     | Time from falling edge of OE to stopped outputs, asynchronous mode  |                                                                                                                 | -           | _              | 100             | ns                                           |

| T <sub>OD,SYNC</sub>      | Time from falling edge of OE to stopped outputs, synchronous mode   |                                                                                                                 | -           | _              | 1.5T + 100      | ns                                           |

| T <sub>OE,ASYNC</sub>     | Time from rising edge of OE to running outputs, asynchronous mode   |                                                                                                                 | Ι           | _              | 100             | ns                                           |

## **Recommended Crystal Specifications for SMD Package**

| Parameter        | Description                       | Range 1 | Range 2 | Range 3 | Unit |

|------------------|-----------------------------------|---------|---------|---------|------|

| F <sub>MIN</sub> | Minimum frequency                 | 8       | 14      | 28      | MHz  |

| F <sub>MAX</sub> | Maximum frequency                 | 14      | 28      | 48      | MHz  |

| R <sub>1</sub>   | Maximum motional resistance (ESR) | 135     | 50      | 30      | Ω    |

| C <sub>0</sub>   | Nominal shunt capacitance         | 4       | 4       | 2       | pF   |

| C <sub>L</sub>   | Nominal load capacitance          |         | 14      | 12      | pF   |

| $D_L$            | Maximum crystal drive level       | 300     | 300     | 300     | μW   |

Document Number: 001-50320 Rev. \*C

<sup>5. %</sup>T<sub>OUT</sub> is the percentage of the output clock period.

6. Parameters are guaranteed by design and characterization. Not 100% tested in production.

## **Switching Waveforms**

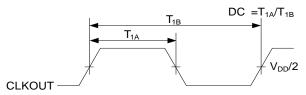

Figure 3. CLKOUT Rise and Fall Time

Figure 4. Duty Cycle Timing (DC)

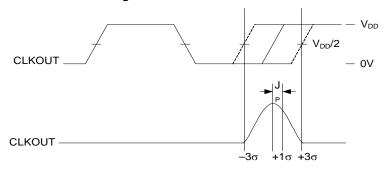

Figure 5. Period Jitter

Figure 6. Cycle to Cycle Jitter

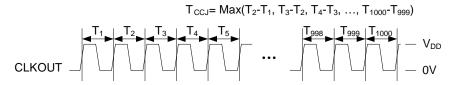

Figure 7. Power On Timing

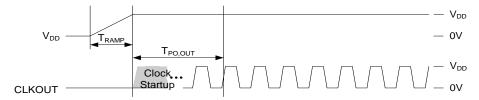

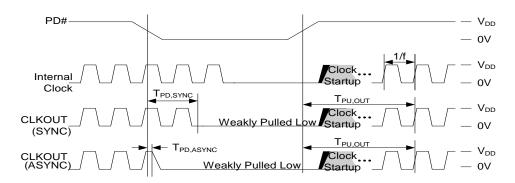

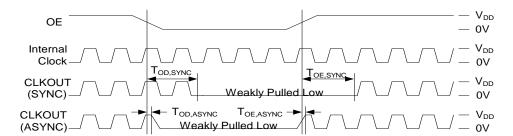

Figure 8. Power Down Timing (Synchronous and Asynchronous Modes) and Power Up Timing

Figure 9. CLKOUT Enable (Synchronous and Asynchronous Modes) and CLKOUT DisableTiming

## **Ordering Information**

| Part Number <sup>[7, 8]</sup> | Туре                                          | VDD(V)                             | Production Flow            |

|-------------------------------|-----------------------------------------------|------------------------------------|----------------------------|

| Pb-Free                       |                                               |                                    |                            |

| CY22U1SCALGXC-00              | 8-pin QFN, Field Programmable                 | Supply voltage: 2.5V, 3.0V or 3.3V | Commercial, 0°C to 70°C    |

| CY22U1SCALGXC-00T             | 8-pin QFN, Field Programmable - tape and reel | Supply voltage: 2.5V, 3.0V or 3.3V | Commercial, 0°C to 70°C    |

| CY22U1LCALGXC-00              | 8-pin QFN, Field Programmable                 | Supply voltage: 1.8V               | Commercial, 0°C to 70°C    |

| CY22U1LCALGXC-00T             | 8-pin QFN, Field Programmable - tape and reel | Supply voltage: 1.8V               | Commercial, 0°C to 70°C    |

| CY22U1SCALGXI-00              | 8-pin QFN, Field Programmable                 | Supply voltage: 2.5V, 3.0V or 3.3V | Industrial, -40°C to +85°C |

| CY22U1SCALGXI-00T             | 8-pin QFN, Field Programmable - tape and reel | Supply voltage: 2.5V, 3.0V or 3.3V | Industrial, -40°C to +85°C |

| CY22U1LCALGXI-00              | 8-pin QFN, Field Programmable                 | Supply voltage: 1.8V               | Industrial, -40°C to +85°C |

| CY22U1LCALGXI-00T             | 8-pin QFN, Field Programmable - tape and reel | Supply voltage: 1.8V               | Industrial, -40°C to +85°C |

| CY22U1SCxLGXC-yy              | 8-pin QFN                                     | Supply voltage: 2.5V, 3.0V or 3.3V | Commercial, 0°C to 70°C    |

| CY22U1SCxLGXC-yyT             | 8-pin QFN - tape and reel                     | Supply voltage: 2.5V, 3.0V or 3.3V | Commercial, 0°C to 70°C    |

| CY22U1LCxLGXC-yy              | 8-pin QFN                                     | Supply voltage: 1.8V               | Commercial, 0°C to 70°C    |

| CY22U1LCxLGXC-yyT             | 8-pin QFN - tape and reel                     | Supply voltage: 1.8V               | Commercial, 0°C to 70°C    |

| CY22U1SCxLGXI-yy              | 8-pin QFN                                     | Supply voltage: 2.5V, 3.0V or 3.3V | Industrial, -40°C to +85°C |

| CY22U1SCxLGXI-yyT             | 8-pin QFN - tape and reel                     | Supply voltage: 2.5V, 3.0V or 3.3V | Industrial, -40°C to +85°C |

| CY22U1LCxLGXI-yy              | 8-pin QFN                                     | Supply voltage: 1.8V               | Industrial, -40°C to +85°C |

| CY22U1LCxLGXI-yyT             | 8-pin QFN - tape and reel                     | Supply voltage: 1.8V               | Industrial, -40°C to +85°C |

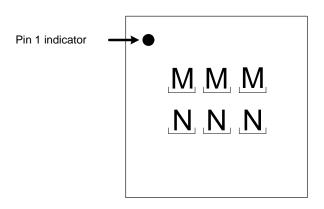

Figure 1. Actual Marking

(MMM) = 7<sup>th</sup>, 8<sup>th</sup> and 9<sup>th</sup> characters of marketing part number (NNN) = Last 3 digits of assembly lot number

## Notes

- x indicates a part marking placeholder to distinguish different configurations for the same customer, beginning alphabetically from "A".

yy indicates "Factory Programmable" and are factory programmed configurations. For more details, contact your local Cypress FAE or Cypress Sales Representative.

Page 9 of 11

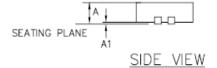

## **Package Drawing and Dimensions**

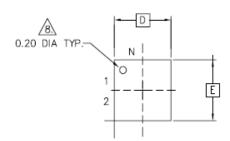

Figure 10. CY22U1 8-Pin 1.7 x 1.7 x 0.6 mm<sup>3</sup> QFN

TOP VIEW

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING CONFORME TO ASME Y14.5M 1994. 2. ALL DIMENSIONS ARE IN MILLIMETERS,  $\theta$  IS IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED

BETWEEN 0.15 AND 0.30mm FROM TERMINAL TIP. IF THE TERMINAL HAS

THE OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE

DIMENSION 6 SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

5. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E

- SIDE RESPECTIVELY.

- 6. MAX. PACKAGE WARPAGE IS 0.05 mm.

- 7. MAXIMUM ALLOWABLE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- 8. PIN #1 ID ON TOP WILL BE LASER MARKED.

| S + M B O L | СОММС | COMMON DIMENSIONS |      |       |  |  |

|-------------|-------|-------------------|------|-------|--|--|

| ို          | MIN.  | NOM.              | MAX. | NO TE |  |  |

| Α           | 0.50  | 0.55              | 0.60 |       |  |  |

| A1          | 0.00  | 0.02              | 0.05 |       |  |  |

| 0           | 0     |                   | 12   | 2     |  |  |

| K           |       | 0.20 MIN.         |      |       |  |  |

| D           |       | 1.7 BSC           |      |       |  |  |

| Ε           |       | 1.7 BSC           |      |       |  |  |

| [e]         |       | 0.40 BSC          |      |       |  |  |

| N           |       | 8<br>2            |      | 5     |  |  |

| ND          |       | 2 2               |      |       |  |  |

| ΝE          |       | 5                 |      |       |  |  |

| L           | 0.35  | 0.40              | 0.45 |       |  |  |

| b           | 0.15  | 0.20              | 0.25 | ▲     |  |  |

001-49591 \*\*

**BOTTOM VIEW**

## **Document History Page**

|     | cument Title: UniClock CY22U1 Single Output, Low Power Programmable Clock Generator cument Number: 001-50320 |                 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rev | ECN                                                                                                          | Orig. of Change | Submission Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| **  | 2612925                                                                                                      | CXQ/AESA        | 11/26/2008      | New Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| *A  | 2636981                                                                                                      | CXQ/PYRS        | 01/15/09        | Updated part numbers in Ordering Information Removed section on programmable output drive strength Changed input range min from 8 MHz to 1 MHz Changed input range from 200MHz max to 166MHz max Replaced CyberClocksOnline and CY3672 programmer reference with CyClockMaker and CyClockDesigner reference Updated VIH/VIL specs for REFIN Added typical I <sub>PD</sub> of 25uA Added period jitter spec Added marking format information Updated package drawing to spec 001-49591 |  |  |  |

| *B  | 2673516                                                                                                      | CXQ/PYRS        | 03/13/09        | Changed from Advanced to Preliminary datasheet Deleted "1.8V" when referring to external reference Fixed error in device name for V <sub>IL2</sub> and V <sub>IH2</sub> Updated V <sub>IH2</sub> maximum for CY22M1L and added note 4 Added IDD values to DC Electrical Specifications table                                                                                                                                                                                          |  |  |  |

| *C  | 2748211                                                                                                      | TSAI            | 08/10/09        | Posting to external web.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

## Sales, Solutions, and Legal Information

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

#### **Products**

PSoC psoc.cypress.com

Clocks & Buffers clocks.cypress.com

Wireless wireless.cypress.com

Memories memory.cypress.com

Image Sensors image.cypress.com

© Cypress Semiconductor Corporation, 2008-2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-50320 Rev. \*C

Revised August 10, 2009

Page 11 of 11

MoBL is a registered trademark, and More Battery Life is a trademark, of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.