#

DATASHEET

## DIFFERENTIAL SPREAD SPECTRUM CLOCK DRIVER

## MK1493-05

## Description

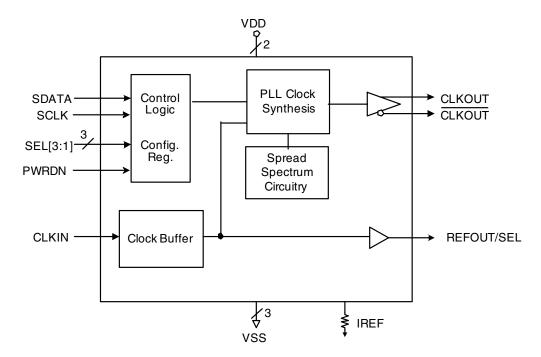

The MK1493-05 is a spread-spectrum clock generator used as a companion chip with a CK410 system clock. The device is used in a PC or embedded system to substantially reduce electro-magnetic interference (EMI). The device provides a differential spread-spectrum high frequency output and a reference output clock. An SMBus is connected to the CK410 for command and control of the MK1493-05. The input reference clock to the MK1493-05 comes directly from the CK410. No external, expensive crystal or crystal oscillator is required.

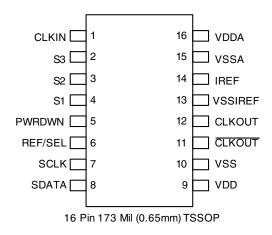

A 16-pin TSSOP package is employed to maximize board space utilization.

#### **Features**

- Packaged in 16-pin TSSOP package

- Available in Pb (lead) free package

- Single differential spread spectrum clock

- Spread spectrum for EMI control

- Supports SMBUS index read/write and blocks read/write operations

- Uses external 14.31818 MHz clock from CK410

- Low output jitter design

- Power down mode lowers Idd

- Spread selection via hardware pins (down and center)

## Block Diagram

1

## **Pin Assignment**

## **Spread Spectrum Selection Table**

| S3 | S2 | S1 | S0 | Spread %      | Spread Type |

|----|----|----|----|---------------|-------------|

| 0  | 0  | 0  | 0  | 0.8           | Down        |

| 0  | 0  | 0  | 1  | 1.0           | Down        |

| 0  | 0  | 1  | 0  | 1.25          | Down        |

| 0  | 0  | 1  | 1  | 1.5           | Down        |

| 0  | 1  | 0  | 0  | 1.75          | Down        |

| 0  | 1  | 0  | 1  | 2.0           | Down        |

| 0  | 1  | 1  | 0  | 2.5           | Down        |

| 0  | 1  | 1  | 1  | 3.0           | Down        |

| 1  | 0  | 0  | 0  | ±0.3          | Center      |

| 1  | 0  | 0  | 1  | <u>+</u> 0.4  | Center      |

| 1  | 0  | 1  | 0  | <u>+</u> 0.5  | Center      |

| 1  | 0  | 1  | 1  | <u>+</u> 0.6  | Center      |

| 1  | 1  | 0  | 0  | <u>+</u> 0.8  | Center      |

| 1  | 1  | 0  | 1  | <u>+</u> 1.0  | Center      |

| 1  | 1  | 1  | 0  | <u>+</u> 1.25 | Center      |

| 1  | 1  | 1  | 1  | <u>+</u> 1.5  | Center      |

The spread enable and spread select[3:0] SMBus register bits control spread modulation and enable/disable. The CLKIN clock input and REF clock output will not have or be spread. At device power-up the spread-spectrum is enabled and hardware control is enabled. The S0 configuration bit is hard-coded to zero when hardware control mode is selected.

## **Pin Descriptions**

| Pin | Pin<br>Name | Pin<br>Type | Pin Description                                                                         |

|-----|-------------|-------------|-----------------------------------------------------------------------------------------|

| 1   | CLKIN       | Input       | 14.31818 MHz single-ended clock input.                                                  |

| 2   | S3          | Input       | Spread spectrum select pin #3. See table above. Internal pull-down.                     |

| 3   | S2          | Input       | Spread spectrum select pin #2. See table above. Internal pull-down.                     |

| 4   | S1          | Input       | Spread spectrum select pin #1. See table above. Internal pull-down.                     |

| 5   | PWRDN       | Input       | Power down pin. Active high. Internal pulldown.                                         |

| 6   | REF/SEL     | I/O         | Strap input for selecting CLKOUT frequency and 14.31818 MHz reference clock.            |

| 7   | SCLK        | Input       | SMBus compatible clock.                                                                 |

| 8   | SDATA       | I/O         | SMBus compatible data.                                                                  |

| 9   | VDD         | Power       | +3.3 V power supply for logic and outputs.                                              |

| 10  | VSS         | Power       | Ground for logic and outputs.                                                           |

| 11  | CLKOUT      | Output      | Selectable 96/100 MHz spread spectrum differential clock output.                        |

| 12  | CLKOUT      | Output      | Selectable 96/100 MHz spread spectrum differential clock output.                        |

| 13  | VSSIREF     | Power       | Ground for current reference.                                                           |

| 14  | IREF        | Input       | Precision resistor attached to this pin is connected to the internal current reference. |

| 15  | VSSA        | Power       | Ground for PLL.                                                                         |

| 16  | VDDA        | Power       | +3.3 V power supply for PLL.                                                            |

3

## **General SMBus Serial Interface**

## How to Write:

- Controller (host) sends a start bit

- Controller (host) sends the write address D4(H)

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location =N

- IDT clock will acknowledge

- Controller (host) sends the data byte count = X

- IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X 1 (see Note 2)

- IDT clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

## How to Read:

- Controller (host) sends a start bit

- Controller (host) sends the write address D4(H)

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location =N

- IDT clock will acknowledge

- Controller (host) will send a separate start bit

- Controller (host) sends the read address D5(H)

- IDT clock will acknowledge

- Controller (host) sends the data byte count = X

- IDT clock sends Byte N + X 1

- IDT clock sends *Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8)*

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

| Ind       | Index Block Write Operation |                     |     |  |  |  |  |

|-----------|-----------------------------|---------------------|-----|--|--|--|--|

| Control   | ler (Host)                  | IDT(Slave/Receiver) |     |  |  |  |  |

| Т         | starTbit                    |                     |     |  |  |  |  |

| Slave Ad  | dress D4 <sub>H)</sub>      |                     |     |  |  |  |  |

| WR        | WRite                       |                     |     |  |  |  |  |

|           |                             |                     | ACK |  |  |  |  |

| Beginnin  | ig Byte = N                 |                     |     |  |  |  |  |

|           |                             |                     | ACK |  |  |  |  |

| Data Byte | e Count = X                 |                     |     |  |  |  |  |

|           |                             |                     | ACK |  |  |  |  |

| Beginnin  | ig Byte = N                 |                     |     |  |  |  |  |

|           |                             | - x                 | ACK |  |  |  |  |

|           | 0                           | B                   |     |  |  |  |  |

|           | 0                           | Ý                   | 0   |  |  |  |  |

|           | 0                           | Т                   | 0   |  |  |  |  |

|           |                             | E                   | 0   |  |  |  |  |

| Byte N    | N + X - 1                   |                     |     |  |  |  |  |

|           |                             |                     | ACK |  |  |  |  |

| Р         | stoP bit                    |                     |     |  |  |  |  |

|      | Index Block Rea             | d C | Operation           |

|------|-----------------------------|-----|---------------------|

| Co   | ntroller (Host)             |     | IDT(Slave/Receiver) |

| Т    | starTbit                    |     |                     |

| Slav | e Address D4 <sub>(H)</sub> |     |                     |

| WR   | WRite                       |     |                     |

|      |                             |     | ACK                 |

| Beg  | jinning Byte = N            |     |                     |

|      |                             |     | ACK                 |

| RT   | Repeat starT                |     |                     |

| Slav | e Address D5 <sub>(H)</sub> |     |                     |

| RD   | ReaD                        |     |                     |

|      |                             |     | ACK                 |

|      |                             |     |                     |

|      |                             |     | Data Bye Count = X  |

|      | ACK                         |     |                     |

|      |                             |     | Beginning Byte N    |

|      | ACK                         | x   |                     |

|      |                             | B   | 0                   |

|      | 0                           | Y   | 0                   |

|      | 0                           | Т   | 0                   |

|      | 0                           | E   |                     |

|      | Γ                           |     | Byte N + X - 1      |

| Ν    | Not acknowledge             |     |                     |

| Р    | stoP bit                    |     |                     |

## **SMBus Address**

The MK1493-05 is a slave-only device that supports block read and block write protocol using a single 7 bit address and read/write bit. A block write (D4h) or block read (D5h) is made up of seven (7) bits and one (1) read/write bit.

| A6 | A5 | <b>A</b> 4 | A3 | A2 | A1 | <b>A</b> 0 | R/W# |

|----|----|------------|----|----|----|------------|------|

| 1  | 1  | 0          | 1  | 0  | 1  | 0          | Х    |

The applications where the indexed block write and block are used, the dummy byte (bit 11-18) functions as a register-offset (8 bits) pointer.

## **Byte 0: Control Register**

| Bit | Description                                                                                                       | Туре | Power Up<br>Condition | Output(s) Affected    | Notes |

|-----|-------------------------------------------------------------------------------------------------------------------|------|-----------------------|-----------------------|-------|

| 7   | Spread Select 0                                                                                                   | RW   | 0                     | CLKOUT, <u>CLKOUT</u> | 1,2,3 |

| 6   | Spread Select 1                                                                                                   | RW   | S1                    | CLKOUT, CLKOUT        | 1,2,3 |

| 5   | Spread Select 2                                                                                                   | RW   | S2                    | CLKOUT, CLKOUT        | 1,2,3 |

| 4   | Spread Select 3                                                                                                   | RW   | S3                    | CLKOUT, CLKOUT        | 1,2,3 |

| 3   | Select Output Frequency,<br>1=100 MHz, 0=96 MHz                                                                   | RW   | SEL 100/96            | CLKOUT, CLKOUT        | 1,2   |

| 2   | Reserved, must be written as 0                                                                                    | RW   | 0                     | Not applicable        | 1     |

| 1   | Spread spectrum enable,<br>0=spread OFF, 1=spread ON                                                              | RW   | 1=spread ON           | CLKOUT, CLKOUT        | 1     |

| 0   | Hardware/Software control of<br>spread enable , S[3:0], and<br>output frequency.<br>0=h.w cinttrol, 1=s/w control | RW   | 0=h/w control         | Not applicable        |       |

## Byte 1: Control Register

| Bit | Description                            | Туре | Power Up<br>Condition | Output(s) Affected | Notes |

|-----|----------------------------------------|------|-----------------------|--------------------|-------|

| 7   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

| 6   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

| 5   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

| 4   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

| 3   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

| 2   | CLKOUT enable, 0=disable,<br>1=enabled | RW   | 1=enabled             | Not applicable     |       |

| 1   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

| 0   | Reserved, must be written as 0         | R    | Undefined             | Not applicable     |       |

## Byte 2 through 5: Control

| Bit    | Description                    | Туре | Power Up<br>Condition | Output(s) Affected | Notes |

|--------|--------------------------------|------|-----------------------|--------------------|-------|

| 7 to 0 | Reserved, must be written as 0 | R    | Undefined             | Not applicable     |       |

## Byte 6: Control Register

| Bit | Description       | Туре | Power Up | Output(s) Affected | Notes |

|-----|-------------------|------|----------|--------------------|-------|

| 7   | Revision ID bit 3 | R    |          | Not applicable     |       |

| 6   | Revision ID bit 2 | R    |          | Not applicable     |       |

| 5   | Revision ID bit 1 | R    |          | Not applicable     |       |

| 4   | Revision ID bit 0 | R    |          | Not applicable     |       |

| 3   | Vendor ID bit 3   | R    |          | Not applicable     | 4     |

| 2   | Vendor ID bit 2   | R    |          | Not applicable     | 4     |

| 1   | Vendor ID bit 1   | R    |          | Not applicable     |       |

| 0   | Vendor ID bit 0   | R    |          | Not applicable     | 4     |

#### Notes:

1. These bits are read-only when the hardware/software bit is set to hardware control.

2. When the hardware/software bit is set to hardware control these bits reflect the state of the S[3:1] and SEL100/96# pins and the SO bit is set to zero. When the hardware/software bit is set to software control the S[3:1] and SEL100/96# pins are overridden by these bits.

- 3. See Spread Spectrum Selection Table on page 2 for spread selection options.

- 4. Use the same vendor ID as is used for the CK408 clock chip.

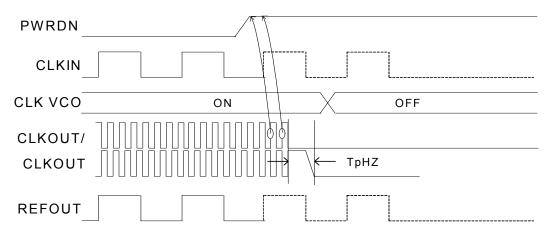

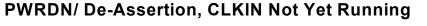

#### **Power Down Mode Operation**

The Power Down pin is used to shut off the clock cleanly prior to shutting off power to the device. The power down pin is an active high asynchronous input. When PWRDWN is sampled low for two output clock periods then all clocks need to be stopped prior to turning off the VCO. ALL clocks need to be stopped in a predictable manner.

CLKOUT is driven differentially when PWRDWN# is de-asserted unless the CLKOUT is disabled through the SMBus register bit.

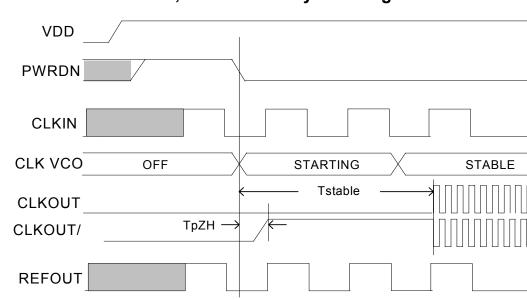

PWRDN/ De-Assertion, CLKIN Already Running

CLKIN must have a stable clock input when PWRDN is de-asserted. If CLKIN starts after PWRDN is de-asserted then Tstable specification applies to when CLKIN is ON. If CLKIN is full ON before PWRDN is de-asserted then the Tstable specification applies.

8

## **Application Information**

#### **Series Termination Resistor**

Clock output traces should use series termination. To series terminate a  $50\Omega$  trace (a commonly used trace impedance), place a  $33\Omega$  resistor in series with the clock line, as close to the clock output pin as possible. The nominal impedance of the clock output is  $20\Omega$ .

#### **Decoupling Capacitors**

As with any high-performance mixed-signal IC, the MK1493-05 must be isolated from system power supply noise to perform optimally.

Decoupling capacitors of  $0.01\mu$ F must be connected between each VDD and the PCB ground plane.

#### **PCB Layout Recommendations**

For optimum device performance and lowest output phase noise, the following guidelines should be observed.

1) Each  $0.01\mu$ F decoupling capacitor should be mounted on

## **Absolute Maximum Ratings**

the component side of the board as close to the VDD pin as possible. No vias should be used between decoupling capacitor and VDD pin. The PCB trace to VDD pin should be kept as short as possible, as should the PCB trace to the ground via. Distance of the ferrite bead and bulk decoupling from the device is less critical.

2) To minimize EMI, and obtain the best signal integrity, the  $33\Omega$  series termination resistor should be placed close to the clock output.

3) An optimum layout is one with all components on the same side of the board, minimizing vias through other signal layers (the ferrite bead and bulk decoupling capacitor can be mounted on the back). Other signal traces should be routed away from the MK1493-05.

This includes signal traces just underneath the device, or on layers adjacent to the ground plane layer used by the device.

Stresses above the ratings listed below can cause permanent damage to the MK1493-05. These ratings are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                          | Rating              |

|-------------------------------|---------------------|

| Supply Voltage, VDD, VDDA     | 5.5 V               |

| All Inputs and Outputs        | -0.5 V to VDD+0.5 V |

| Ambient Operating Temperature | 0 to +70°C          |

| Storage Temperature           | -65 to +150°C       |

| Junction Temperature          | 125°C               |

| Soldering Temperature         | 260°C               |

| ESD Protection (Input)        | 2000 V min. (HBM)   |

## **Electrical Characteristics - DC**

| Parameter                          | Symbol            | Conditions                        | Min.    | Тур. | Max.     | Units |

|------------------------------------|-------------------|-----------------------------------|---------|------|----------|-------|

| Supply Voltage                     | V                 |                                   | 3.135   |      | 3.465    |       |

| Input High Voltage <sup>2</sup>    | V <sub>IH</sub>   |                                   | 2.0     |      | VDD +0.3 | V     |

| Input Low Voltage <sup>2</sup>     | V <sub>IL</sub>   |                                   | VSS-0.3 |      | 0.8      | V     |

| Input Leakage Current <sup>3</sup> | ۱ <sub>IL</sub>   | 0 < Vin < VDD                     | -5      |      | 5        | μA    |

| Output High Voltage <sup>2</sup>   | V <sub>OH</sub>   | I <sub>OH</sub> = -1 mA           | 2.4     |      |          | V     |

| Output Low Voltage <sup>2</sup>    | V <sub>OH</sub>   | I <sub>OH</sub> = 1 mA            |         |      | 0.4      | V     |

| Output Current <sup>5</sup>        | IoH               | CLKOUT, Voh@Z=0.7 V@50<br>ohms    | 6*Iref  |      | +12% x I |       |

| Operating Supply Current           | I <sub>DD</sub>   | No load                           |         |      | 55       | mA    |

|                                    | I <sub>DDPD</sub> | No load, input low                |         |      | 400      | μA    |

| Input Capacitance                  | CIN               | Input pin capacitance             |         |      | 7        | pF    |

| Output Capacitance                 | C <sub>OUT</sub>  | Output pin capacitance            |         |      | 6        | pF    |

| Pin Inductance                     | L <sub>PIN</sub>  |                                   |         |      | 5        | nH    |

| Output Resistance                  | Rout              | CLKOUT                            | 3.0     |      |          | kΩ    |

| Pull-up Resistor <sup>1,4</sup>    | Rpu               | Real time, asynchronous assertion |         | 120  |          | kΩ    |

| Pull-down Resistor <sup>1,4</sup>  | Rpd               | Real time, asynchronous assertion |         | 120  |          | kΩ    |

Unless stated otherwise, VDD = 3.3 V ±5%, Ambient Temperature 0 to +70°C

<sup>1</sup>Includes ±50K ohm internal.

<sup>2</sup>Single edge is monotonic when transitioning through region.

<sup>3</sup>Inputs with pull-ups/-downs are not included.

<sup>4</sup>Internal leakage to ground is less than equal to 5 uA to ensure high level if input is floating.

<sup>5</sup>Configuration is Rr=475 ohms at 1%. Iref=2.32 mA. Iref=VDD/(3 x Rr).

## **Electrical Characteristics - CLKIN/REFOUT**

Unless stated otherwise, VDD = 3.3 V ±5%, Ambient Temperature 0 to +70°C

| Parameter                           | Symbol            | Conditions          | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------|---------------------|------|------|------|-------|

| Rise Time                           | t <sub>RISE</sub> | from 0.8 V to 2.0 V | 600  |      | 1200 | ps    |

| Fall Time                           | t <sub>FALL</sub> | from 2.0 V to 0.8 V | 600  |      | 1200 | ps    |

| Edge Rate                           |                   | Rising Edge         | 1.0  |      | 4.0  | V/ns  |

| Edge Rate                           |                   | Falling Edge        | 1.0  |      | 4.0  | V/ns  |

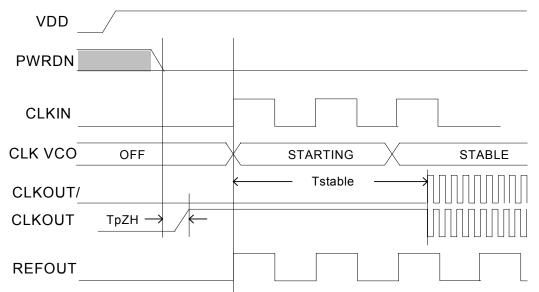

| Duty Cycle <sup>1</sup>             |                   |                     | 40   |      | 60   | %     |

| Jitter, Cycle-to-Cycle <sup>1</sup> |                   |                     |      |      | 1000 | ps    |

| Accuracy                            |                   | Long Term Accuracy  |      |      | 300  | ppm   |

<sup>1</sup>Measured from VDD/2.

## **Electrical Characteristics - CLKOUT**

Unless stated otherwise, VDD=3.3 V ±5%, Ambient Temperature 0 to +70°C

| Parameter                                  | Symbol            | Conditions                                                            | Min. | Тур. | Max.          | Units |

|--------------------------------------------|-------------------|-----------------------------------------------------------------------|------|------|---------------|-------|

| High Voltage <sup>1,2</sup>                | V <sub>H</sub>    |                                                                       | 660  | 700  | 850           | mV    |

| Low Voltage <sup>1,2</sup>                 | VL                |                                                                       | -150 | 0    |               | mV    |

| Crossing Point<br>Voltage <sup>1,2</sup>   |                   | absolute                                                              | 250  |      | 550           | mV    |

| Crossing Point<br>Voltage <sup>1,2,4</sup> |                   | variation over all edges                                              |      |      | 140           | mV    |

| Jitter, Cycle-to-Cycle <sup>1,3</sup>      |                   |                                                                       |      | 80   |               | ps    |

| Modulation Frequency                       |                   | spread spectrum                                                       |      | 32.5 |               | kHz   |

| Rise Time <sup>1,2</sup>                   | t <sub>RISE</sub> | from 0.175 V to 0.525 V. Rising edge CLKOUT and falling edge CLKOUT/. | 175  |      | 700           | ps    |

| Fall Time <sup>1,2</sup>                   | t <sub>FALL</sub> | from 2.0 V to 0.8 V                                                   | 175  |      | 700           | ps    |

| Rise/Fall Time<br>Variation <sup>1,2</sup> |                   |                                                                       |      |      | 125           | ps    |

| Rise/Fall Time<br>Matching <sup>1,2</sup>  |                   |                                                                       |      |      | 20            | %     |

| Duty Cycle <sup>1,3</sup>                  |                   |                                                                       | 45   |      | 55            | %     |

| Output Voltage<br>Variation <sup>1,2</sup> |                   | undershoot, overshoot                                                 | -0.3 |      | Vhigh+0.<br>3 | V     |

<sup>1</sup>Test setup is Rs=33.2 ohms, Rp=49.9 ohms with 2 pF.

<sup>2</sup>Measurement taken from a single-ended waveform.

<sup>3</sup>Measurement taken from a differential waveform

<sup>4</sup>Measured at the crossing point where instantaneous voltages of both CLKOUT and CLKOUT/ are equal

## **Electrical Characteristics - AC**

| Parameter                        | Symbol    | Conditions                          | Min. | Тур. | Max. | Units |

|----------------------------------|-----------|-------------------------------------|------|------|------|-------|

| Output Enable Time <sup>1</sup>  | TpZL,TpZH | All outputs                         |      |      | 10   | us    |

| Output Disable Time <sup>1</sup> | TpLZ,TpHZ | All outputs                         | 600  |      | 1200 | ps    |

| Stabilization Time <sup>2</sup>  | Tstable   | from power-up                       |      | 3.0  |      | ms    |

| Spread Change Time               | Tspread   | Settling period after spread change |      | 3.0  |      | ms    |

Unless stated otherwise, VDD = 3.3 V ±5%, Ambient Temperature 0 to +70°C, C<sub>I</sub> = 15 pF

<sup>1</sup>CLKOUT and SMBus pins are tri-stated when PWRDN/ is asserted. CLKOUT is driven differential when PWRDN/ is de-asserted unless its already disabled.

<sup>2</sup>The period is when VDD equals its typical VDD condition.

## **Measurement Diagrams**

Measurement diagram for duty cycle and jitter.

## **Current Reference Source (Iref)**

If board target trace impedance (Z) is 50 $\Omega$ , then Rr = 475 $\Omega$  (1%), providing IREF of 2.32 mA, output current (I<sub>OH</sub>) is equal to 6\*IREF.

#### **Thermal Characteristics**

| Parameter                           | Symbol        | Conditions     | Min. | Тур. | Max. | Units |

|-------------------------------------|---------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to      | $\theta_{JA}$ | Still air      |      | 78   |      | °C/W  |

| Ambient                             | $\theta_{JA}$ | 1 m/s air flow |      | 70   |      | °C/W  |

|                                     | $\theta_{JA}$ | 3 m/s air flow |      | 68   |      | °C/W  |

| Thermal Resistance Junction to Case | $\theta_{JC}$ |                |      | 37   |      | °C/W  |

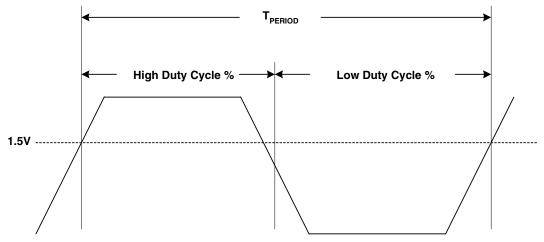

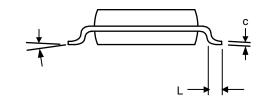

## Package Outline and Package Dimensions (16-pin TSSOP, 4.40 mm Body, 0.65 mm Pitch)

Package dimensions are kept current with JEDEC Publication No. 95, MO-153

|        | Millimeters |            | Inches      |             |  |  |

|--------|-------------|------------|-------------|-------------|--|--|

| Symbol | Min         | Max        | Min         | Max         |  |  |

| A      |             | 1.20       |             | 0.047       |  |  |

| A1     | 0.05        | 0.15       | 0.002       | 0.006       |  |  |

| A2     | 0.80        | 1.05       | 0.032       | 0.041       |  |  |

| b      | 0.19        | 0.30       | 0.007       | 0.012       |  |  |

| С      | 0.09        | 0.20       | 0.0035      | 0.008       |  |  |

| D      | 4.90        | 5.1        | 0.193       | 0.201       |  |  |

| E      | 6.40 BASIC  |            | 0.252 BASIC |             |  |  |

| E1     | 4.30        | 4.50       | 0.169       | 0.177       |  |  |

| е      | 0.65        | Basic      | 0.0256      | .0256 Basic |  |  |

| L      | 0.45        | 0.75       | 0.018       | 0.030       |  |  |

| α      | 0°          | <b>8</b> ° | 0°          | 8°          |  |  |

| aaa    |             | 0.10       |             | 0.004       |  |  |

## **Ordering Information**

| Part / Order Number | Marking  | Shipping<br>packaging | Package      | Temperature |  |

|---------------------|----------|-----------------------|--------------|-------------|--|

| MK1493-05G          | 149305G  | Tubes                 | 16-pin TSSOP | 0 to +70°C  |  |

| MK1493-05GTR        | 149305G  | Tape and Reel         | 16-pin TSSOP | 0 to +70°C  |  |

| MK1493-05GLF        | 149305GL | Tubes                 | 16-pin TSSOP | 0 to +70°C  |  |

| MK1493-05GLFTR      | 149305GL | Tape and Reel         | 16-pin TSSOP | 0 to +70°C  |  |

| MK1493-05GLN        | 149305GN | Tubes                 | 16-pin TSSOP | 0 to +70°C  |  |

| MK1493-05GLNTR      | 149305GN | Tape and Reel         | 16-pin TSSOP | 0 to +70°C  |  |

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

## Innovate with IDT and accelerate your future networks. Contact:

## www.IDT.com

#### **For Sales**

800-345-7015 408-284-8200 Fax: 408-284-2775

## For Tech Support 408-284-4522

clockhelp@idt.com

## Corporate Headquarters

Integrated Device Technology, Inc. www.idt.com

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA