semiconductor, inc.

11403 West Bernado Court, Suite 100, San Diego, CA 92127. Tel No: (619) 674 2233, Fax No: (619) 674 2230

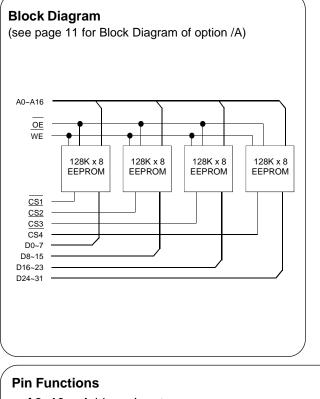

## Description

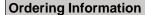

The PUMA 68E4001/A is a 4Mbit CMOS EEPROM module in a JEDEC 68 pin surface mount PLCC. The plastic device is screened to ensure high reliability. Access times of 120, 150 and 200ns are available. The output width is user configurable as 8, 16, or 32 bits wide using CS1-4 and is available in two pinout options, single WE or WE1-4 (version /A). Page write (128 bytes) is performed in 5 ms (typical). The device also features both hardware and software data protection with DATA polling and Toggle bit indication of end of write . Write cycle endurance is 10,000 Erase/Write cycles with a data retention time of 10 years.

# 128K x 32 EEPROM Module

# PUMA 68E4001/A-12/15/20

Issue 4.2 : November 1998

## 4,194,304 bit CMOS EEPROM Module

## Features

- Access Times of 120/150/200 ns.

- User Configurable as 8 / 16 / 32 bit wide output.

- · Commercial, Industrial, or Military grades.

- 490/913/1760 mW (max). Operating Power

- JEDEC 68 pin surface mount PLCC, available in two pinouts : Single  $\overline{WE}$ ,  $\overline{WE1-4}$  is version A.

- High reliability plastic design

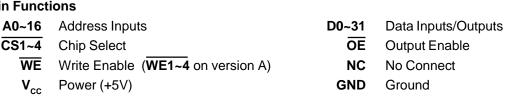

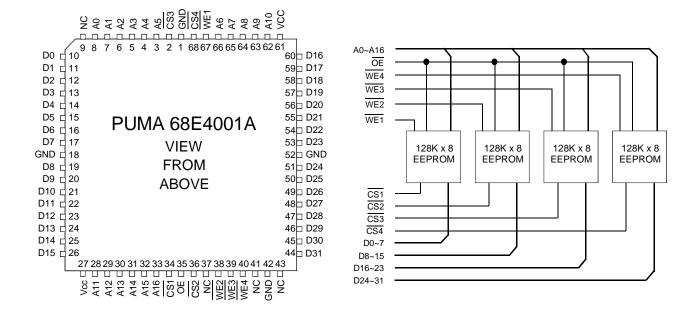

**Pin Definition**

D0 🗆 10

D1 🗆 11

D2 🗆 12

D3 [ 13 D4 🗆

D5

**D7** [ 17

D8 🗆 19

D9 🗆

D10 🗆

D11 22

D12 23

D13 24

D14 25

D15 26

GND [ 18

14 □ 15

16 D6 🗆

20

21

· Hardware and Software Data Protection.

(see page 11 for option /A Pinout)

Endurance of 10<sup>4</sup> Erase/Write Cycles and Data Retention Time of 10 years.

> 9 8 7 6 5 4 3 2 1 6867666564636261

> > PUMA 68E4001

VIEW

FROM

ABOVE

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

60 D16

59 D17

58 D18

57 D19

56 D20

55 D21

54 D22

53 D23

52 GND

51 D24

50 D25

49🗆 D26

48 D27

47 D28

46 D29

45 D30

44 🗆 D31

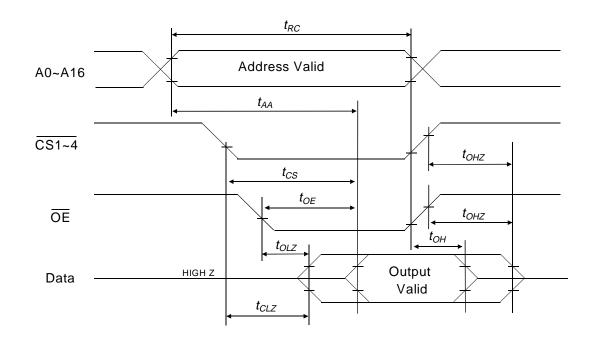

#### **DC OPERATING CONDITIONS**

| Absolute Maximum Ratings (1)                             |                  |                              |    |

|----------------------------------------------------------|------------------|------------------------------|----|

| Operating Temperature                                    | T <sub>opr</sub> | -55 to +125                  | °C |

| Storage Temperature                                      | T <sub>stg</sub> | -65 to +150                  | °C |

| Input voltages (including N.C. pins) with Respect to GND | V <sub>IN</sub>  | -0.6 to +6.25                | V  |

| Output voltages with respect to GND                      | V <sub>out</sub> | -0.6 to V <sub>cc</sub> +0.6 | V  |

Notes : (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Recommended Operating Conditions |                 |      |     |                    |                       |  |  |  |

|----------------------------------|-----------------|------|-----|--------------------|-----------------------|--|--|--|

|                                  |                 | min  | typ | max                |                       |  |  |  |

| DC Power Supply Voltage          | V <sub>cc</sub> | 4.5  | 5.0 | 5.5                | V                     |  |  |  |

| Input Low Voltage                | V <sub>IL</sub> | -1.0 | -   | 0.8                | V                     |  |  |  |

| Input High Voltage               | V <sub>IH</sub> | 2.0  | -   | V <sub>cc</sub> +1 | V                     |  |  |  |

| Operating Temp Range             | T <sub>A</sub>  | 0    | -   | 70                 | C                     |  |  |  |

|                                  | T <sub>AI</sub> | -40  | -   | 85                 | °C (I Suffix)         |  |  |  |

|                                  | T <sub>AM</sub> | -55  | -   | 125                | °C ( <b>M</b> Suffix) |  |  |  |

| <b>DC Electrical Characteristics</b> ( $T_A$ =-55°C to +125°C, $V_{CC}$ =5V ± 10%) |        |                          |                                                                                                                         |     |      |      |  |  |

|------------------------------------------------------------------------------------|--------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|------|--|--|

| Parameter                                                                          |        | Symt                     | ool Test Condition                                                                                                      | min | max  | Unit |  |  |

| Input Leakage Current                                                              |        | <b>I</b>                 | $V_{IN} = GND$ to $V_{CC}$ +1                                                                                           | -   | 40   | μA   |  |  |

| Output Leakage Current                                                             | 32 bit | $\mathbf{I}_{\text{LO}}$ | $V_{I/O} = GND \text{ to } V_{CC}, \overline{CS}^{(1)} = V_{IH}$                                                        | -   | 40   | μA   |  |  |

| Operating Supply Current                                                           | 32 bit | I <sub>CC32</sub>        | $\overline{CS}^{(1)} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}, I_{OUT} = 0 \text{ mA}, f = 5 \text{ MHz}^{(2)}$ | -   | 320  | mA   |  |  |

|                                                                                    | 16 bit |                          | As above                                                                                                                | -   | 166  | mA   |  |  |

|                                                                                    | 8 bit  |                          | As above                                                                                                                | -   | 89   | mA   |  |  |

| Standby Supply Current TTL                                                         | levels | I <sub>SB1</sub>         | $\overline{CS}^{(1)}$ = 2.0V to V <sub>cc</sub> +1V                                                                     | -   | 12   | mA   |  |  |

| CMOS                                                                               | levels | $I_{SB2}$                | $\overline{\text{CS}}^{(1)}$ = V <sub>cc</sub> -0.3V to V <sub>cc</sub> +1V                                             | -   | 1.2  | mA   |  |  |

| Output Low Voltage                                                                 |        | V <sub>ol</sub>          | I <sub>oL</sub> = 2.1mA.                                                                                                | -   | 0.45 | V    |  |  |

| Output High Voltage                                                                |        | $V_{OH}$                 | I <sub>OH</sub> = -400μA.                                                                                               | 2.4 | -    | V    |  |  |

Notes (1) CS above are accessed through CS1-4. These inputs must be operated simultaneously for 32 bit operation, in pairs in 16 bit mode and singly for 8 bit mode.

(2) Also for WE1~4 on the PUMA 68E4001A version. Additionally, WE1~4 are accessed as in note (1) above.

| <b>Capacitance</b> ( $T_A = 25^{\circ}C, f = 1$ MHz) Note: These parameters are calculated, not measured. |                                                         |                  |                      |     |     |      |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|----------------------|-----|-----|------|--|

| Parameter                                                                                                 |                                                         | Symbol           | Test Condition       | typ | max | Unit |  |

| Input Capacitance                                                                                         | $\overline{CS1}$ -4, $\overline{WE1}$ -4 <sup>(1)</sup> | C <sub>IN1</sub> | V <sub>IN</sub> =0V  | -   | 20  | pF   |  |

|                                                                                                           | Other Inputs                                            | C <sub>IN2</sub> | V <sub>IN</sub> =0V  | -   | 22  | pF   |  |

| Output Capacitance                                                                                        | e                                                       | C <sub>OUT</sub> | V <sub>OUT</sub> =0V | -   | 22  | pF   |  |

Notes: (1) On the PUMA 68E4001A version only.

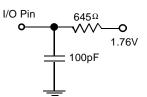

### **AC OPERATING CONDITIONS**

# Read Cycle

| Read Cycle                             |                     |     |     |     |     |     |     |      |

|----------------------------------------|---------------------|-----|-----|-----|-----|-----|-----|------|

|                                        |                     | 12  |     | 15  |     | 20  |     |      |

| Parameter                              | Symnbol             | min | max | min | max | min | max | Unit |

| Read Cycle Time                        | t <sub>RC</sub>     | 120 | -   | 150 | -   | 200 | -   | ns   |

| Address Access Time                    | t <sub>AA</sub>     | -   | 120 | -   | 150 | -   | 200 | ns   |

| Chip Select Access Time                | t <sub>cs</sub>     | -   | 120 | -   | 150 | -   | 200 | ns   |

| Output Enable Access Time              | t <sub>oe</sub>     | 0   | 60  | 0   | 70  | 0   | 80  | ns   |

| Chip Select High to High Z Output (1)  | t <sub>HZ</sub>     | 0   | 50  | 0   | 50  | 0   | 50  | ns   |

| Output Enable High to High Z Output (  | 1) t <sub>oHz</sub> | 0   | 50  | 0   | 50  | 0   | 50  | ns   |

| Chip Select Low to Active Output (1)   | t <sub>LZ</sub>     | 0   | -   | 0   | -   | 0   | -   | ns   |

| Output Enable Low to Active Output (1) | ) t <sub>olz</sub>  | 0   | -   | 0   | -   | 0   | -   | ns   |

| Output Hold from Address Change        | t <sub>oH</sub>     | 0   | -   | 0   | -   | 0   | -   | ns   |

|                                        |                     |     |     |     |     |     |     |      |

Notes: (1)  $t_{HZ}$  max. and  $t_{OLZ}$  max. are measured with CL = 5pF, from the point when Chip Select or Output Enable return high (whichever occurs first) to the time when the outputs are no longer driven.  $t_{HZ}$  and  $t_{OHZ}$  are shown for reference only: they are characterized and not tested.

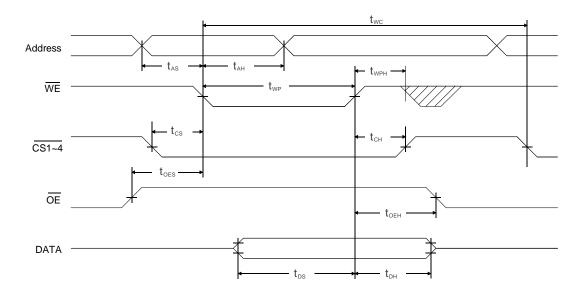

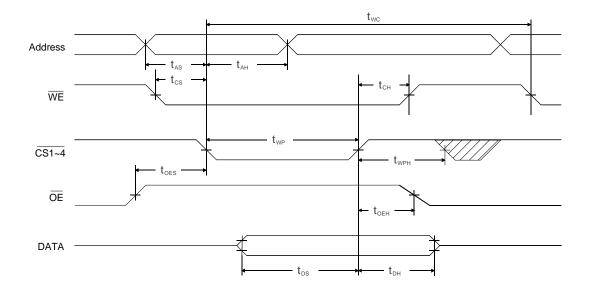

| Write Cycle                |                  |     |     |     |      |

|----------------------------|------------------|-----|-----|-----|------|

| Parameter                  | Symbol           | min | typ | max | Unit |

| Write Cycle Time           | t <sub>wc</sub>  | -   | -   | 10  | ms   |

| Address Set-up Time        | t <sub>AS</sub>  | 0   | -   | -   | ns   |

| Address Hold Time          | t <sub>AH</sub>  | 50  | -   | -   | ns   |

| Output Enable Set-up Time  | t <sub>oes</sub> | 0   | -   | -   | ns   |

| Output Enable Hold Time    | t <sub>oeh</sub> | 0   | -   | -   | ns   |

| Chip Select Set-up Time    | t <sub>cs</sub>  | 0   | -   | -   | ns   |

| Chip Select Hold Time      | t <sub>сн</sub>  | 0   | -   | -   | ns   |

| Write Pulse Width          | t <sub>wP</sub>  | 100 | -   | -   | ns   |

| Write Enable High Recovery | t <sub>wPH</sub> | 50  | -   | -   | ns   |

| Data Set-up Time           | t <sub>DS</sub>  | 50  | -   | -   | ns   |

| Data Hold Time             | t <sub>DH</sub>  | 0   | -   | -   | ns   |

| Delay to Next Write        | t <sub>DW</sub>  | 10  | -   | -   | μs   |

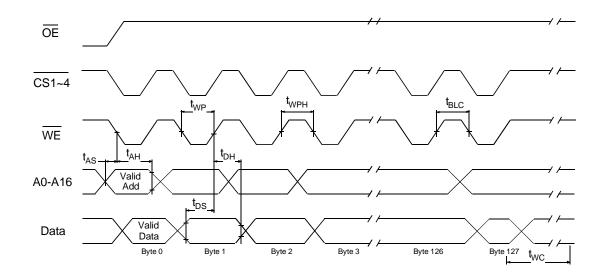

| Byte Load Cycle            | t <sub>BLC</sub> | -   | -   | 150 | μs   |

#### AC Test Conditions

# **Output Test Load**

- \* Input pulse levels: 0V to 3.0V

- \* Input rise and fall times: 10ns

- \* Input and Output timing reference levels: 1.5V

- \* Output load: 1 TTL gate + 100pF

- \* V<sub>cc</sub>=5V±10%

# Read Cycle Timing Waveform

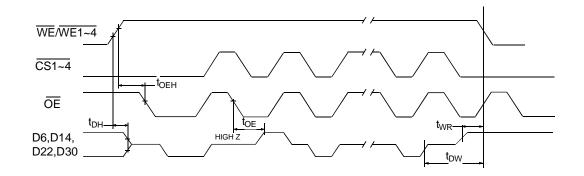

# AC Write Waveform - WE Controlled

## AC Write Waveform - CS Controlled

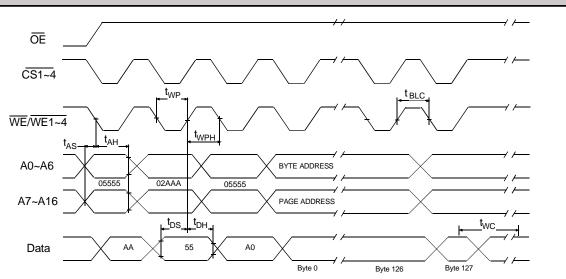

# Page Mode Write Waveform

#### Note: A8 through A16 must specify the page address during each high to low transition of Write Enable (or Chip select). Output Enable must be high only when Write Enable and Chip Select are both low.

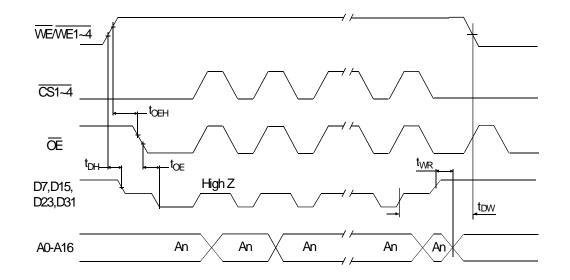

# DATA Polling Waveform

# **Toggle Bit Waveform**

## **Software Protected Write Waveform**

#### **Device Operation**

The following description deals with the PUMA 68E4001 device, with the references to  $\overline{\text{WE}}$  meaning  $\overline{\text{WE1}}$  on the PUMA 68E4001A part.

#### Read

The PUMA 68E4001 read operations are initiated by both Output Enable and Chip Select LOW. The read operation is terminated by either Chip Select or Output Enable returning HIGH. This 2-line control architecture eliminates bus contention in a system environment. The data bus will be in a high impendence state when either Output Enable or Chip Select is HIGH.

#### Write

Write operations are initiated when both Chip Select and Write Enable are LOW and Output Enable is HIGH. The PUMA 68E4001 supports both a Chip Select and Write Enable controlled write cycle. That is, the address is latched by the falling edge of either Chip Select or Write Enable, whichever occurs last. Similarly, the data is latched internally by the rising edge of either Chip Select or Write Enable, whichever occurs first. A byte write operation, once initiated, will automatically continue to completion, typically within 5 ms.

#### Page Mode Write

The page write feature of the PUMA 68E4001 allows the entire memory to be written in 5 seconds. Page Write allows 128 bytes of data to be written prior to the internal programming cycle. The host can fetch data from another location within the system during a page write operation (change the source address), but the page address (A8 through A16) for each subsequent valid write cycle to the part during this operation must be the same as the initial page address.

The page write mode can be initiated during any write operation. Following the initial byte write cycle, the host can write up to 128 bytes in the same manner as the first byte written. Each successive byte load cycle, started by the Write Enable HIGH to LOW transition, must begin within 150  $\mu$ s of the falling edge of the preceding Write Enable. If a subsequent Write Enable HIGH to LOW transition is not detected within 150  $\mu$ s, the internal automatic programming cycle will commence.

#### DATA Polling

The PUMA 68E4001 features DATA Polling to indicate if the write cycle is completed. During the internal programming cycle, any attempt to read the last byte written will produce the compliment of that data on D7. Once the programming is complete, D7 will reflect the true data. Note: If the the PUMA 68E4001 is in a protected state and an illegal write operation is attempted DATA Polling will not operate.

#### **TOGGLE** bit

In addition to DATA polling, another method is provided to determine the end of a Write Cycle. During a write operation successive attempts to read data will result in D6 toggling between 1 and 0. Once a write is complete, this toggling will stop and valid data will be read.

#### Hardware Data Protection

The PUMA 68E4001 provides three hardware features to protect non-volalitile data from inadvertent writes.

- Noise Protection A Write Enable pulse less than 15 ns will not initiate a write cycle.

- Default  $V_{cc}$  Sence All functions are inhibited when  $V_{cc}$  < 3.6 V.

- Write Inhibit Holding either Output Enable LOW, Write Enable HIGH or Chip Select HIGH will prevent an inadvertent write cycle during power on or power off, maintaining data integrity.

#### Software Data Protection

The PUMA 68E4001 can be automatically protected during power-up and power-down without the need for external circuits by employing the software data protect feature. The internal software data protection circuit is enabled after the first write operation utilizing the software algorithm. This circuit is nonvolatile and will remain set for the life of the device unless the reset command is issued.

Once the software protection is enabled, the PUMA 68E4001 is also protected against inadvertent and accidental writes in that, the software algorithm must be issued prior to writing additional data to the device.

#### **Operating Modes**

The table below shows the logic inputs required to control the operation of the PUMA 68E4001.

| MODE          | CS1~4 | OE | WE | OUTPUTS  |

|---------------|-------|----|----|----------|

| Read          | 0     | 0  | 1  | Data Out |

| Write         | 0     | Ι  | 0  | Data in  |

| Standby       | 1     | Х  | Х  | Floating |

| Write Inhibit | Х     | Х  | 1  |          |

|               | Х     | 0  | Х  |          |

$0 = V_{IL}$  :  $1 = V_{IH}$  :  $X = V_{IH}$  or  $V_{IL}$

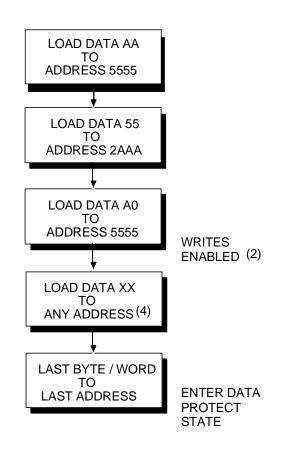

#### Software Algorithms

Selecting the software data protection mode requires the host system to precede datawrite operations by a series of three write operations to three specific addresses. The three byte sequence opens the page write window enabling the host to write from from 1 to 128 bytes of data. Once the page load cycle has been completed, the device will automatically be returned to the data protected state

#### Software Data Protection Algorithm

Regardless of wheather the device has been protected or not, once the software data protected aglorithm is used and the data is written, the PUMA 68E4001 will automatically disable further writes unless another command is issued to cancel it. If no further commands are issued the PUMA 68E4001 will be write protected during powerdown and any subsequent power-up.

Notes:

(1) Data Format I/O7-I/O0 (Hex);

### Once initiated, this sequence of write operations should not be interrupted.

- (2) Enable Write Protect state will be initiated at end of write even if no other data is loaded.

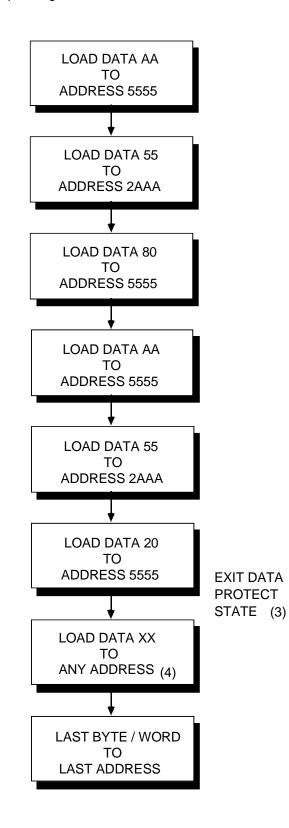

- (3) Disable Write Protect state will be initiated at end of write period even if no other data is loaded.

- (4) 1 to 128 bytes of data may be loaded.

#### Software Data Protect Disable

In the event the user wants to deactivate the software data protection feature for testing or reprogramming in an  $E^2$ PROM programmer. The following six step algorithm will reset the internal protection circuit. After t<sub>wc</sub>, the PUMA 68E4001 will be in standard operating mode.

#### Pin Definifion 'A' version

#### **Block Diagram 'A' version**

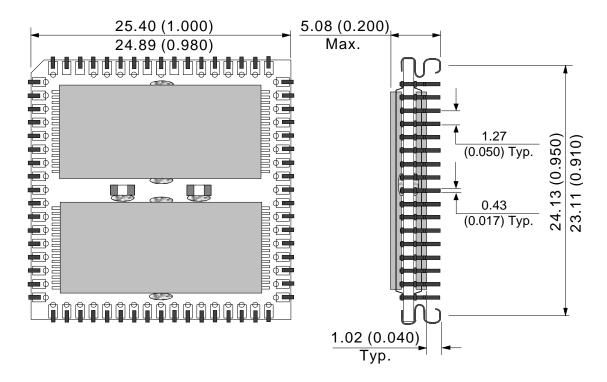

**Package Information** Dimensions in mm(inches)

## Plastic 68 Pin JEDEC Surface mount PLCC

#### Soldering Recommendations

#### Bake

As specified on product packaging If not specified HMPLtd recommend a minimum bake of 6 hours duration @ 125C if parts have been exposed to the atmosphere for 24hrs or more

Soldering Must not exceed VPR 215 - 219C, 60 secs

IR / Convection Ramp rate 6C/sec max Temp maintained at 125C, 120secs max Temp exceeding 183C, 120-180secs Time at max temp 10-40secs Max temp 220 +5/-0 C Ramp down -6C/sec max

Although this data is believed to be accurate the information contained herein is not intended to and does not create any warranty of merchantability or fitness for a particular purpose. Products are subject to a constant process of development. Data may be changed at any time without notice. Products are not authorised for use as critical components in life support devices or systems without the express written approval of a company director