# International TOR Rectifier

# µPFC ONE CYCLE CONTROL PFC IC

#### **Features**

- PFC with IR proprietary "One Cycle Control"

- Continuous conduction mode (CCM) boost type PFC

- No line voltage sense required

- Programmable switching frequency (50kHz-200kHz)

- Programmable output overvoltage protection

- Brownout and output undervoltage protection

- · Cycle-by-cycle peak current limit

- · Soft start

- User initiated micropower "Sleep Mode"

- Open loop protection

- Maximum duty cycle limit of 98%

- User programmable fixed frequency operation

- Min. off time of 150-350ns over freq range

- · VCC under voltage lockout

- · Internally clamped 13V gate drive

- Fast 1.5A peak gate drive

- Micropower startup (<200 μA)</li>

- Latch immunity and ESD protection

- · Parts also available Lead-Free

### **Description**

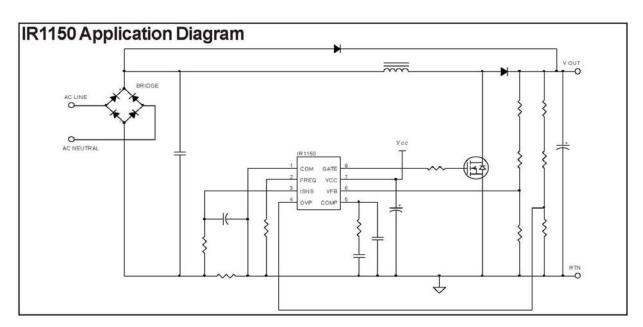

The  $\mu$ PFC IR1150 is a power factor correction (PFC) control IC designed to operate in continuous conduction mode (CCM) over a wide range input line voltages. The IR1150 is based on IR's proprietary "One Cycle Control" (OCC) technique providing a cost effective solution for PFC.

The proprietary control method allows major reductions in component count, PCB area and design time while delivering the same high system performance as traditional solutions.

The IC is fully protected and eliminates the often noise sensitive line voltage sensing requirements of existing solutions.

The IR1150 features include programmable switching frequency, programmable dedicated over voltage protection, soft start, cycle-by-cycle peak current limit, brownout, open loop, UVLO and micropower startup current. In addition, for low standby power requirements (Energy Star, 1W Standby, Blue Angel, etc.), the IC can be driven into sleep mode with total current consumption below 200 $\mu$ A, by pulling the OVP pin below 0.62V.

#### **Packages**

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltages are absolute voltages referenced to COM. Thermal resistance and power dissipation are measured under board mounted and still air conditions.

| Parameters                 | Symbols             | Min. | Max. | Units    | Remarks                         |

|----------------------------|---------------------|------|------|----------|---------------------------------|

| VCC voltage                | $V_{CC}$            | -0.3 | 22   | V        | Not internally clamped          |

| Freq. voltage              | $V_{FREQ}$ .        | -0.3 | 10.5 | ٧        |                                 |

| ISNS voltage               | V <sub>ISNS</sub>   | -10  | 3    | ٧        |                                 |

| OVP/EN voltage             | $V_{\text{OVP/EN}}$ | -0.3 | 9    | V        |                                 |

| VFB voltage                | $V_{FB}$            | -0.3 | 10.5 | ٧        |                                 |

| COMP voltage               | $V_{COMP}$          | -0.3 | 10   | ٧        |                                 |

| Gate voltage               | $V_{GATE}$          | -0.3 | 18   | <b>V</b> |                                 |

| Continuous gate current    | I <sub>GATE</sub>   | -5   | 5    | mA       |                                 |

| Max peak gate current      | $I_{GATEPK}$        | -1.5 | 1.5  | Α        |                                 |

| Junction temperature       | $T_J$               | -40  | 150  | °C       |                                 |

| Storage temperature        | Ts                  | -55  | 150  | °C       |                                 |

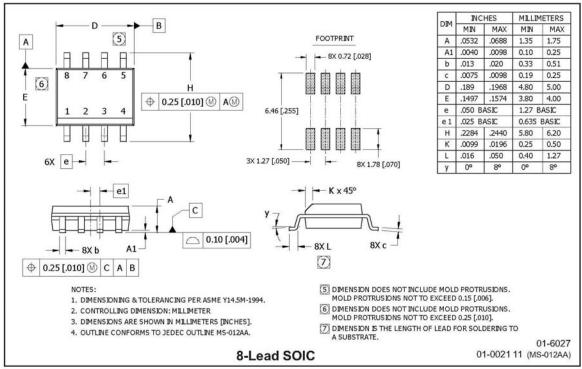

| Thermal resistance         | R <sub>0 JA</sub>   | _    | 128  | °C/W     | SOIC-8                          |

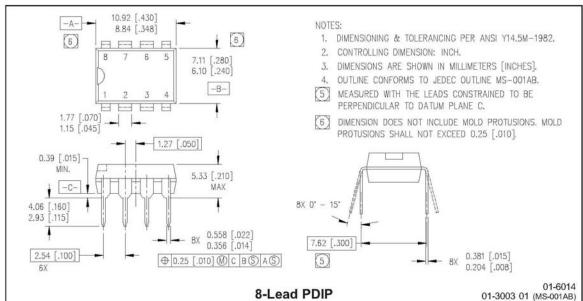

| Thermal resistance         | <b>™</b> θ JA       | _    | 84   | °C/W     | PDIP-8                          |

| Package power dissipation  | $P_{D}$             | _    | 675  | mW       | SOIC-8 T <sub>AMB</sub> = 25 °C |

| i ackage power dissipation | ı D                 | _    | 1000 | mW       | PDIP-8 T <sub>AMB</sub> = 25 °C |

| ESD protection             | $V_{ESD}$           | _    | 2    | kV       | Human body model*               |

### **Recommended Operating Conditions**

Recommended operating conditions for reliable operation with margin

| ·                    |         |      |      |      |       |            |  |  |

|----------------------|---------|------|------|------|-------|------------|--|--|

| Parameters           | Symbols | Min. | Тур. | Max. | Units | Remarks    |  |  |

| Supply voltage       | VCC     | 15   | 18   | 20   | V     |            |  |  |

| Junction temperature | TJ      | -25  | _    | 125  | °C    |            |  |  |

| Ambient temperature  | TA      | 0    | _    | 70   | °C    | IR1150(S)  |  |  |

| Ambient temperature  | TA      | -25  | _    | 85   | °C    | IR1150I(S) |  |  |

| Switching frequency  | FSW     | 50   | _    | 200  | kHz   |            |  |  |

### **Electrical Characteristics**

The electrical characteristics involve the spread of values guaranteed within the specified supply voltage and junction temperature range  $T_J$  from  $-25^{\circ}$ C to  $125^{\circ}$ C. Typical values represent the median values, which are related to  $25^{\circ}$ C. If not otherwise stated, a supply voltage of  $V_{CC}$  =15V is assumed for test condition

### **Supply Section**

| Parameters                                      | Symbols  | Min. | Тур. | Max. | Units | Remarks |

|-------------------------------------------------|----------|------|------|------|-------|---------|

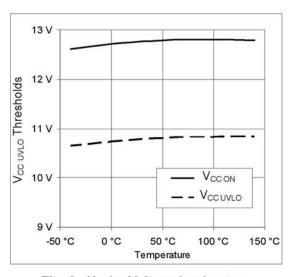

| VCC turn-on threshold                           | VCC ON   | 12.2 | 12.7 | 13.2 | V     |         |

| VCC turn-off threshold (under voltage lock out) | VCC UVLO | 10.2 | 10.7 | 11.2 | V     |         |

<sup>\*</sup>Per EIA/JESD22-A114-B (discharging a 100pF capacitor through a 1.5K $\Omega$  series resistor)

#### **Electrical Characteristics cont.**

The electrical characteristics involve the spread of values guaranteed within the specified supply voltage and junction temperature range  $T_J$  from  $-25^{\circ}$ C to  $125^{\circ}$ C. Typical values represent the median values, which are related to  $25^{\circ}$ C. If not otherwise stated, a supply voltage of  $V_{CC}$  =15V is assumed for test condition.

| 7 11 7 0 00             |                      |      |      |      |       |                                                             |  |  |

|-------------------------|----------------------|------|------|------|-------|-------------------------------------------------------------|--|--|

| Parameters              | Symbols              | Min. | Тур. | Max. | Units | Remarks                                                     |  |  |

| VCC turn-off hysteresis | V <sub>CC</sub> HYST | 1.8  | _    | 2.2  | V     |                                                             |  |  |

|                         |                      | _    | 18   | 22   | mA    | C <sub>LOAD</sub> =1nF f <sub>SW</sub> =200kHZ              |  |  |

| Operating current       | I <sub>CC</sub>      | _    | 36   | 40   | mA    | C <sub>LOAD</sub> =10nF f <sub>SW</sub> =200kHZ             |  |  |

| operating content       | icc                  |      | 8    | 10   | mA    | Standby mode - inactive gate<br>Internal oscillator running |  |  |

| Startup current         | ICCSTART             | _    | _    | 175  | uA    | V <sub>CC</sub> =V <sub>CC ON</sub> - 0.1V                  |  |  |

| Sleep current           | I <sub>SLEEP</sub>   |      | 125  | 200  | uA    | V <sub>OVP</sub> <0.5V, V <sub>CC</sub> =15V                |  |  |

| Sleep threshold         | V <sub>SLEEP</sub>   | 0.56 | 0.62 | 0.68 | V     |                                                             |  |  |

### **Oscillator Section**

| Parameters            | Symbols             | Min. | Тур. | Max. | Units | Remarks                           |

|-----------------------|---------------------|------|------|------|-------|-----------------------------------|

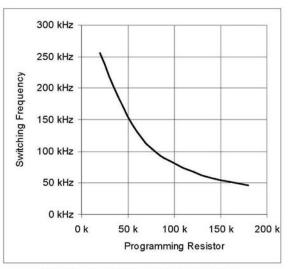

| Switching frequency   | f <sub>SW</sub>     | 50   | _    | 200  | kHz   | $R_{SET}$ = 165kΩ-37kΩ approx.    |

| Initial accuracy      | f <sub>SW ACC</sub> |      | _    | 5    | %     | T <sub>A</sub> = 25°C             |

| Voltage stability     | $V_{STAB}$          | _    | 0.2  | 3    | %     | 13V <vcc <20v<="" td=""></vcc>    |

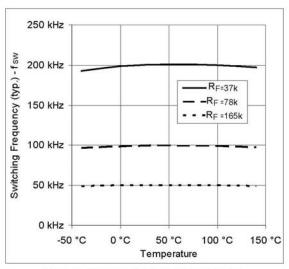

| Temperature stability | T <sub>STAB</sub>   | _    | 2    | _    | %     | -25°C ≤ TJ≤ 125°C                 |

| Total variation       | f <sub>VT</sub>     | _    | 10   | _    | %     | Line & temperature                |

| Long term stability   | F <sub>STABLT</sub> | _    | 0.1  | 0.5  | %     | T <sub>AMB</sub> = 125°C, 1000Hrs |

| Maximum duty cycle    | $D_{MAX}$           | 93   | _    | 98   | %     | f <sub>SW</sub> =200kHz           |

| Minimum duty cycle    | D <sub>MIN</sub>    | _    | _    | 0    | %     |                                   |

| Minimum off time      | T <sub>offmin</sub> | 200  | 300  | 400  | Ns    | f <sub>SW</sub> = 50kHz to 200kHz |

#### **Protection Section**

| Parameters                                                                             | Symbols           | Min.  | Тур.  | Max.  | Units | Remarks              |

|----------------------------------------------------------------------------------------|-------------------|-------|-------|-------|-------|----------------------|

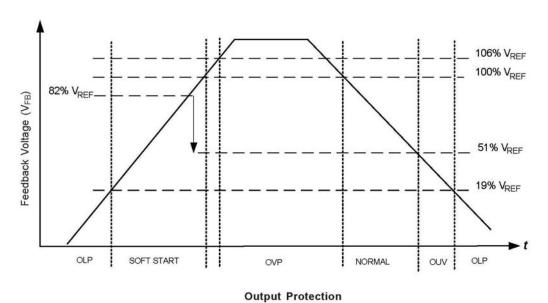

| Open loop protection(OLP) Vfb threshold                                                | $V_{OLP}$         | 17    | 19    | 21    | %VREF |                      |

| Output under voltage protection (OUV)                                                  | V <sub>OUV</sub>  | 49    | 51    | 53    | %VREF | Brown out protection |

| Output over voltage protection (OVP)                                                   | V <sub>OVP</sub>  | 104   | 105.5 | 107   | %VREF |                      |

| OVP hysteresis                                                                         | _                 | 350   | 450   | 550   | mV    |                      |

| Peak current limit protection (I <sub>PKLMT</sub> ) I <sub>SNS</sub> voltage threshold | V <sub>ISNS</sub> | -1.11 | -1.04 | -0.96 | V     |                      |

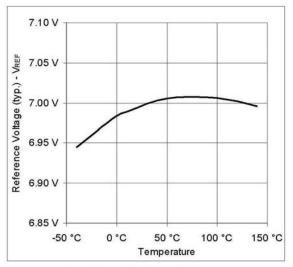

### **Internal Voltage Reference Section**

| Parameters        | Symbols           | Min. | Тур. | Max. | Units | Remarks                                        |

|-------------------|-------------------|------|------|------|-------|------------------------------------------------|

| Reference voltage | $V_{REF}$         | 6.9  | 7.0  | 7.1  | V     | T <sub>A</sub> = 25°C                          |

| Line regulation   | R <sub>REG</sub>  | _    | 12   | 25   | mV    | 13.5V <v<sub>CC &lt; 20V</v<sub>               |

| Temp stability    | T <sub>STAB</sub> | _    | 0.4  | _    | %     | -25°C ≤T <sub>AMB</sub> ≤ 125°C                |

| Total variation   | $\Delta V_{TOT}$  | 6.8  | _    | 7.1  | V     | Over V <sub>CC</sub> and T <sub>i</sub> ranges |

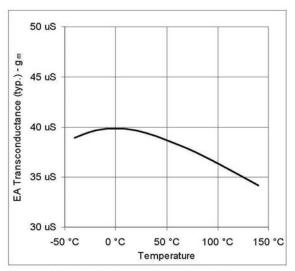

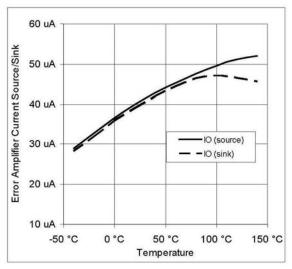

**Voltage Error Amplifier Section**

| Parameters                            | Symbols                 | Min.     | Тур.     | Max.       | Units | Remarks                                                                               |

|---------------------------------------|-------------------------|----------|----------|------------|-------|---------------------------------------------------------------------------------------|

| Transconductance                      | g <sub>m</sub>          | 30       | 40       | 55         | μS    | -25°C ≤T <sub>AMB</sub> ≤ 125°C                                                       |

| Source/sink current                   | I <sub>OVEA</sub>       | 30<br>20 | 40<br>45 | 65<br>90   | μA    | T <sub>AMB</sub> = 25°C<br>-25°C ≤T <sub>AMB</sub> ≤ 125°C                            |

| Soft start delay time (calculated)    | t <sub>ss</sub>         | _        | 40       | _          | ms    | $R_{GAIN}$ =1k $\Omega$ , $C_{ZERO}$ =0.33 $\mu$ F $C_{POLE}$ =0.01 $\mu$ F, fXO=28Hz |

| VCOMP voltage (fault)                 | V <sub>COMP</sub> FLT   | _        | 1.2      | 1.5<br>0.2 | V     | @ 1mA (max) initial<br>@ 25μA steady state                                            |

| Effective VCOMP voltage               | V <sub>COMP</sub> EFF   |          | 6.05     |            | V     |                                                                                       |

| Input bias current                    | I <sub>IB</sub>         | _        | -0.2     | -0.5       | μA    | $V_{FB}=0V$ $-25^{\circ}C \le T_{AMB} \le 125^{\circ}C$                               |

| Open loop bandwidth                   | BW                      | _        | 1        | _          | MHz   |                                                                                       |

| Input offset voltage temp coefficient | TC <sub>IOV</sub>       | _        | _        | 10         | μV/°C | Note 1                                                                                |

| Common mode rejection ratio           | CMRR                    | _        | 100      | _          | dB    |                                                                                       |

| Output low voltage                    | V <sub>OL</sub>         | _        | _        | 0.5        | V     |                                                                                       |

| Output high voltage                   | $V_{OH}$                | 5.71     | 6.15     | 6.8        | V     |                                                                                       |

| VCOMP start voltage                   | V <sub>COMP START</sub> | 300      | 500      | 700        | mV    |                                                                                       |

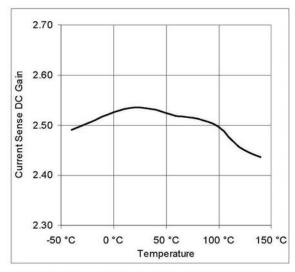

### **Current Amplifier Section**

| Parameters                            | Symbols            | Min. | Тур. | Max. | Units | Remarks                                              |

|---------------------------------------|--------------------|------|------|------|-------|------------------------------------------------------|

| DC gain                               | <b>g</b> dc        | _    | 2.5  | _    | V/V   |                                                      |

| Corner frequency                      | f <sub>C</sub>     | 200  | _    | 280  | kHz   | Note 1                                               |

| Input offset voltage                  | $V_{IO}$           | _    | 1    | 4    | mV    | Note 1                                               |

| ISNS bias current                     | I <sub>IB</sub>    | _    | 200  | 300  | μΑ    | V <sub>FB</sub> =0V,-25°C ≤ T <sub>AMB</sub> ≤ 125°C |

| Input offset voltage temp coefficient | TC <sub>IOV</sub>  | _    | _    | 10   | μV/°C | Note 1                                               |

| Common mode rejection ratio           | CMRR               | _    | 100  | _    | dB    |                                                      |

| Blanking time                         | T <sub>BLANK</sub> | 230  | 350  | 450  | ns    | T <sub>AMB</sub> = 25°C                              |

| Dianking time                         | IBLANK             | 150  |      | 600  | ns    | -25°C ≤T <sub>AMB</sub> ≤ 125°C                      |

### **Gate Driver Section**

| Parameters           | Symbols             | Min. | Тур. | Max. | Units | Remarks                                       |

|----------------------|---------------------|------|------|------|-------|-----------------------------------------------|

| Gate low voltage     | $V_{GLO}$           | _    | 1.2  | 1.5  | V     | I <sub>GATE</sub> =200mA                      |

| Gate high voltage    | $V_{GTH}$           | _    | 13   | 18   | V     | V <sub>CC</sub> =20V                          |

| Gate high voltage    | $V_{GTH}$           | 9.5  | ı    | _    | ٧     | V <sub>CC</sub> =11.5V                        |

| Rise time            | tr                  | _    | 20   | _    | ns    | $C_{LOAD} = 1nF, V_{CC} = 16V$                |

| Nise time            | u                   | _    | 70   | _    | ns    | $C_{LOAD} = 10nF, V_{CC} = 16V$               |

| Fall time            | tf                  | _    | 20   | _    | ns    | C <sub>LOAD</sub> = 1nF, V <sub>CC</sub> =16V |

| raii tiirie          | u                   | _    | 70   | _    | ns    | $C_{LOAD} = 10nF, V_{CC} = 16V$               |

| Out peak current     | I <sub>OPK</sub>    | 1.5  | _    | _    | Α     | $C_{LOAD} = 10nF, V_{CC} = 16V$               |

| Gate voltage @ fault | VG <sub>fault</sub> | _    | _    | 1.8  | V     | I <sub>GATE</sub> =20mA                       |

Note 1: Guaranteed by design, but not tested in production.

# International **IOR** Rectifier

# IR1150(S)/IR1150I(S)(PbF)

### **Lead Assignments & Definitions**

| Lead A   | Assignme | nt                | Pin# | Symbol           | Description                       |

|----------|----------|-------------------|------|------------------|-----------------------------------|

|          |          |                   | 1    | СОМ              | Ground                            |

| IF       | R1150    |                   | 2    | FREQ             | Frequency Set                     |

| сом 1    |          | 8 GATE            | 3    | I <sub>SNS</sub> | Current Sense                     |

| FREQ 2   |          | 7 V <sub>cc</sub> | 4    | OVP/EN           | Overvoltage Fault Detect / Enable |

| sns 3    |          | 6 V <sub>FB</sub> | 5    | COMP             | Voltage Loop Compensation         |

| OVP/EN 4 |          | 5 COMP            | 6    | $V_{FB}$         | Output Voltage Sense              |

| 3.7.7.1  |          | 33                | 7    | $V_{CC}$         | IC Supply Voltage                 |

|          |          |                   | 8    | GATE             | Gate Drive Output                 |

### **General Description**

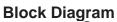

The  $\mu$ PFC IR1150 is intended for boost converters for power factor correction operating at a fixed frequency in continuous conduction mode. The IC operates with two loops; an inner current loop and an outer voltage loop. The inner current loop is fast, reliable and does not require sensing of the input voltage in order to create a current reference.

This inner current loop sustains the sinusoidal profile of the average input current based on the dependency of the pulse width modulator duty cycle on the input line voltage in order to determine the analogous input line current. Thus, the current loop uses the embedded input voltage signal to control the average input current to follow the input voltage.

The IR1150 enables excellent THD performance. In light load conditions, a small distortion occurs at zero-crossing due to the finite boost inductance but this is negligible and well within EN61000-3-2 Class D specifications.

The outer voltage loop controls the DC bus voltage. This voltage is fed into the voltage error amplifier to control the slope of the integrator ramp and sets the amplitude of the average input current.

The two loops combine to control the amplitude, phase and shape of the input current, with respect to the input voltage, giving near-unity power factor.

The IC is designed for robust operation and provides protection from system level over current, over voltage, under voltage, and brownout conditions.

#### **IC Supply**

The UVLO circuit monitors the VCC pin and maintains the gate drive signal inactive until the VCC pin voltage reaches the UVLO turn on threshold, (V<sub>CC ON</sub>). As soon as the VCC voltage exceeds this threshold, provided that the V<sub>FB</sub> pin voltage is greater than 20%VREF, the gate drive will begin switching (under Soft Start) and increase the pulse width to its maximum value as demanded by the output voltage error amplifier. If the voltage on the VCC pin falls below the UVLO turn off threshold, (V<sub>CC UVLO</sub>), the IC turns off, gate drive is terminated, and the turn on threshold must again be exceeded in order to re-start the process and move into Soft Start mode.

#### **Soft Start**

Soft Start controls the rate of rise of the output voltage error amplifier in order to obtain a linear control of the increasing duty cycle as a function of time. The Soft Start time is controlled by voltage error amplifier compensation components selected, and is user programmable based on desired loop crossover frequency.

#### **Frequency Select**

The switching frequency of the IC is programmable by an external resistor at the FREQ pin. The design incorporates min/max restrictions such that the minimum and maximum operating frequency fall within the range of 50-200kHz.

#### **Gate Drive**

The gate drive is a totem pole driver with 1.5A capability. If higher currents are required, additional external drivers can be used.

### **Detailed Pin Description**

#### **COM: Ground**

This is the ground potential pin of the integrated control circuit. All internal devices are referenced to this point.

#### **V<sub>FB</sub>**: Output Voltage Feedback

The output voltage of the boost converter is sensed via a resistive divider and fed into this pin, which is the inverting input of the output voltage error amplifier. The impedance of the divider string must be low enough so as to not introduce substantial error due to the input bias currents of the amplifier, yet high enough so as to minimize power dissipation. A typical value of external divider impedance is 1MO.

The error amplifier is a transconductance type which yields high output impedance, thus increasing the noise immunity of the error amplifier output. This also eliminates input divider string interaction with compensation feedback capacitors and reducing the loading of divider string due to a low impedance output of the amplifier.

#### **COMP: Voltage Loop Compensation**

External circuitry from this pin to ground compensates the system voltage loop and soft start time. This is the output of the voltage error amplifier. This pin will be discharged via internal resistance when a fault mode occurs.

#### **GATE: Gate Drive Output**

This is the gate drive output of the IC. Drive voltage is internally limited and provides ±1.5A peak with matched rise and fall times.

#### **FREQ: Frequency Set**

This is the user programmable frequency pin. An external resistor from this pin to the COM pin programs the frequency. The operational switching frequency range for the device is 50kHz – 200kHz.

#### **ISNS: Current Sense input**

This pin is the inverting Current Sense Input & Peak Current Limit. The voltage at this pin is the negative voltage drop, sensed across the system current sense resistor, representing the inductor current.

This voltage is fed into the Peak Current Limit protection comparator with threshold around -1V. This protection circuit incorporates a leading edge blanking circuit following the comparator to improve noise immunity of the protection process.

The current sense signal is also fed into the current sense amplifier. The signal is amplified, filtered of high frequency noise and then injected into a summing node where it is subtracted from the compensation voltage  $V_{\text{COMP}}$ .

The signal on this pin must be previously filtered with an RC cell to provide additional noise immunity. The input impedance of this pin is  $5k\Omega$ .

#### V<sub>cc</sub>: Supply Voltage

This is the supply voltage pin of the IC and it is monitored by the under voltage lockout circuit. It is possible to turn off the IC by pulling this pin below the minimum turn off threshold voltage, without damage to the IC.

To prevent noise problems, a bypass ceramic capacitor connected to VCC and COM should be placed as close as possible to the IR1150.

This pin is not internally clamped, therefore damage will occur if the maximum voltage is exceeded.

#### **OVP/EN: Over Voltage Protection / Enable**

This pin is the input to the over voltage protection comparator the threshold of which is internally programmed to 105.5% of VREF.

A resistive divider feeds this pin from the output volt-age to COM and inhibits the gate drive whenever the threshold is exceeded. Normal operation resumes when the voltage level on this pin decreases to below the pin threshold.

This pin is also used to activate "sleep" mode by pulling the voltage level below 0.62V (typ).

### **Operating States**

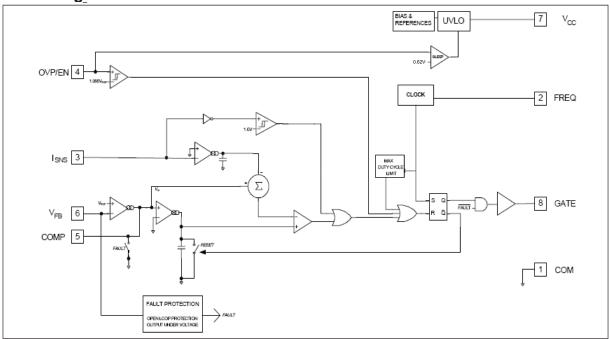

#### **UVLO Mode**

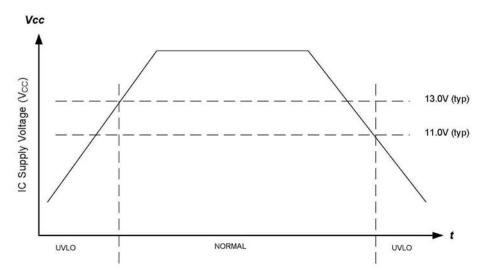

The IC remains in the UVLO condition until the voltage on the  $V_{\text{CC}}$  pin exceeds the VCC turn on threshold voltage, VCC ON

During the time the IC remains in the UVLO state, the gate drive circuit is inactive and the IC draws a

quiescent current of ICC START. The UVLO mode is accessible from any other state of operation whenever the IC supply voltage condition of  $V_{\rm CC} < V_{\rm CC~UVLO}$  occurs.

#### **Standby Mode**

The IC is in this state if the supply voltage has exceeded  $V_{\text{CC ON}}$  and the VFB pin voltage is less than 20% of VREF . The oscillator is running and all internal circuitry is biased in this state but the gate is inactive. This state is accessible from any other state of operation except OVP. The IC enters this state whenever the VFB pin voltage has decreased to 50% of VREF when operating in normal mode or during a peak current limit fault condition, or 20% VREF when operating in soft start mode.

#### **Soft Start Mode**

This state is activated once the  $V_{\text{CC}}$  voltage has exceeded  $V_{\text{CCON}}$  and the VFB pin voltage has exceeded 20% of VREF.

The soft start time, which is defined as the time required for the duty cycle to linearly increase from zero to maximum, is dependent upon the values selected for compensation of the voltage loop pin COMP to pin COM. Throughout the soft start cycle, the output of the voltage error amplifier (pin COMP) charges through the compensation network. This forces a linear rise of the voltage at this node which in turn forces a linear increase in the gate drive duty cycle from 0. This controlled duty cycle reduces system component stress during start up conditions as the input current amplitude is increasing linearly.

#### **Normal Mode**

The IC enters normal operating mode once the soft start transition has been completed. At this point the gate drive is switching and the IC draws a maximum of ICC from the supply voltage source. The device will initiate another soft start sequence in the event of a shutdown due to a fault, which activates the protection circuitry, or if the supply voltage drops below the UVLO turn off threshold of  $V_{\rm CC}$  UVLO.

#### **Fault Protection Mode**

The fault mode will be activated when any of the protection circuits are activated. The IC protection circuits include Supply Voltage Under Voltage Lockout (UVLO), Output Over Voltage Protection (OVP), Open Loop Protection (OLP), Output Undervoltage Protection (OUV), and Peak Current Limit Protection (IPK LIMIT).

#### Sleep Mode

The sleep mode is initiated by pulling the OVP pin below 0.62V (typ). In this mode the IC draws a very low quiescent supply current.

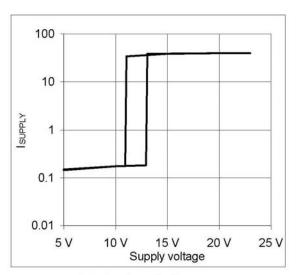

Fig.1 - Supply Current

Fig. 2 - Under Voltage Lockout vs.

Temperature

Fig. 3 - Oscillator Frequency vs. Programming Resistor

Fig. 4 - Oscillator Frequency vs.

Temperature

Fig. 5 - Reference Voltage

Fig. 6 - Voltage Error Amplifier Transconductance

Fig.7 - Voltage Error Amplifier Source/Sink Current

Fig. 8 - Current Sense Amplifier DC Gain

### **IR1150 Timing Diagrams**

### V<sub>cc</sub> Under Voltage Lockout

#### Case outline

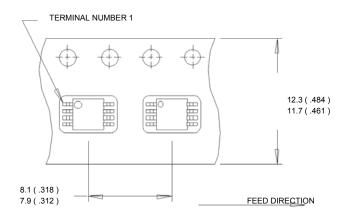

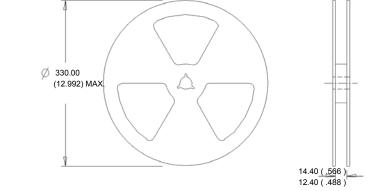

# Tape & Reel Information (SOIC 8-Lead only)

Dimensions are shown in millimeters (inches)

#### NOTES:

- 1. OUTLINE CONFORMS TO EIA-481 & EIA-541.

- 2. CONTROLLING DIMENSION : MILLIMETER.

NOTES:

1.CONTROLLING DIMENSION : MILLIMETER. 2.OUTLINE CONFORMS TO EIA-481 & EIA-541.

International IOR Rectifier

## IR1150(S)/IR1150I(S)(PbF)

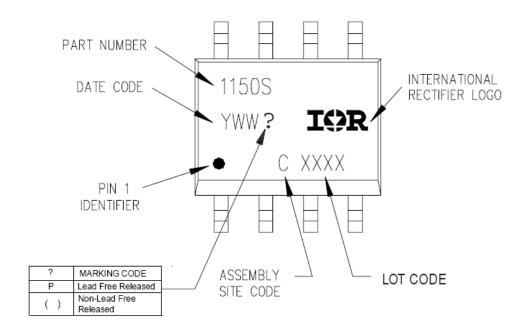

#### PART MARKING INFORMATION

TOP MARKING (LASER)

#### ORDER INFORMATION

**Basic Part** 8-Lead SOIC IR1150STR order IR1150STR

Lead-free Part 8-Lead SOIC IR1150S order IR1150STRPbF 8-Lead SOIC IR1150ISTR order IR1150ISTR 8-Lead SOIC IR1150ISTR order IR1150ISTRPbF 8-Lead PDIP IR1150 order IR1150PbF 8-Lead PDIP IR1150I order IR1150IPbF

# International

The IR1150(S)(PbF) has been designed and qualified for the Consumer Market The IR1150I(S)(PbF) has been designed and qualified for the Industrial Market Qualification Standards can be found on IR's Web site.

WORLD HEADQUARTERS: 233 Kansas Street, El Segundo, California 90245 Tel: (310) 252-7105 http://www.irf.com/ Data and specifications subject to change without notice. 2/5/2007