# 128Mbit GDDR-II SDRAM

1M x 32Bit x 4 Banks

GDDR-II SDRAM

with Differential Data Strobe and DLL

Revision 1.5

December 2002

Samsung Electronics reserves the right to change products or specification without notice.

# 1M x 32Bit x 4 Banks GDDR-II Synchronous DRAM with Differential Data Strobe

#### **FEATURES**

- 2.5V + 0.1V power supply for device operation

- 1.8V + 0.1V power supply for I/O interface

- On-Die Termination for all inputs except CKE,ZQ

- · Output Driver Strength adjustment by EMRS

- SSTL\_18 compatible inputs/outputs

- 4 banks operation

- · MRS cycle with address key programs

- CAS latency : 5, 6, 7 (clock)

- Burst length: 4 only

- Burst type : sequential only

- Additive latency (AL): 0,1(clock)

- Read latency(RL): CL+AL

- Write latency(WL): AL+1

- Differential Data Strobes for Data-in, Date out;

- 4 DQS and /DQS(one differential strobe per byte)

- Single Data Strobes by EMRS.

- · Edge aligned data & data strobe output

- · Center aligned data & data strobe input

- · DM for write masking only

- · Auto & Self refresh

- 32ms refresh period (4K cycle)

(16ms is under consideration)

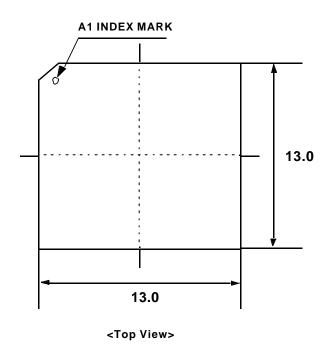

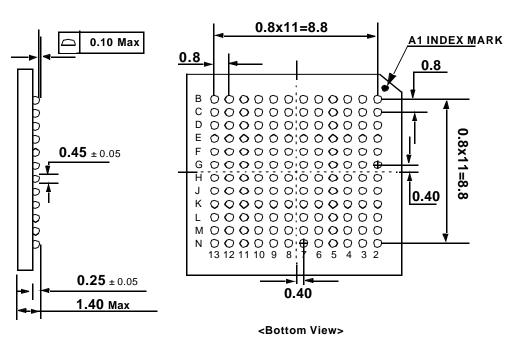

- 144 Ball FBGA

- Maximum clock frequency up to 500MHz

- Maximum data rate up to 1Gbps/pin

- DLL for Address, CMD and outputs

#### ORDERING INFORMATION

| Part NO.        | Max Freq. | Max Data Rate | Interface | Package       |

|-----------------|-----------|---------------|-----------|---------------|

| K4N26323AE-GC20 | 500MHz    | 1000Mbps/pin  |           |               |

| K4N26323AE-GC22 | 450MHz    | 900Mbps/pin   | SSTL_18   | 144 Ball FBGA |

| K4N26323AE-GC25 | 400MHz    | 800Mbps/pin   |           |               |

## **GENERAL DESCRIPTION**

#### FOR 1M x 32Bit x 4 Bank GDDR-II SDRAM

The 4Mx32 GDDR-II is 134,217,728 bits of hyper synchronous data rate Dynamic RAM organized as 4 x 1,048,976 words by 32 bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 4GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of operating frequencies, and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

# **K4N26323AE-GC**

## **PIN CONFIGURATION**

Normal Package (Top View)

|   | 2    | 3     | 4    | 5    | 6                | 7          | 8          | 9                | 10   | 11    | 12    | 13   |

|---|------|-------|------|------|------------------|------------|------------|------------------|------|-------|-------|------|

| В | DQS0 | /DQS0 | VSSQ | DQ3  | DQ2              | DQ0        | DQ31       | DQ29             | DQ28 | VSSQ  | /DQS3 | DQS3 |

| С | DQ4  | DM0   | VDDQ | VDDQ | DQ1              | VDDQ       | VDDQ       | DQ30             | VDDQ | VDDQ  | DM3   | DQ27 |

| D | DQ6  | DQ5   | VSSQ | VSSQ | VSSQ             | VDD        | VDD        | VSSQ             | VSSQ | VSSQ  | DQ26  | DQ25 |

| E | DQ7  | VDDQ  | VDD  | VSS  | VSSQ             | VSS        | VSS        | VSSQ             | VSS  | VDD   | VDDQ  | DQ24 |

| F | DQ17 | DQ16  | VDDQ | VSSQ | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ | VDDQ  | DQ15  | DQ14 |

| G | DQ19 | DQ18  | VDDQ | VSSQ | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ | VDDQ  | DQ13  | DQ12 |

| н | DQS2 | /DQS2 | NC   | VSSQ | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ | NC    | /DQS1 | DQS1 |

| J | DQ20 | DM2   | VDDQ | VSSQ | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ | VDDQ  | DM1   | DQ11 |

| К | DQ21 | DQ22  | VDDQ | VSSQ | VSS              | VSS        | VSS        | VSS              | VSSQ | VDDQ  | DQ9   | DQ10 |

| L | DQ23 | А3    | VDD  | VSS  | RFU <sub>2</sub> | VDD        | VDD        | RFU <sub>1</sub> | VSS  | VDD   | A4    | DQ8  |

| М | VREF | A2    | A10  | /RAS | NC               | CKE        | NC         | ZQ               | /CS  | A9    | A5    | VREF |

| N | A0   | A1    | A11  | BA0  | /CAS             | СК         | /CK        | /WE              | BA1  | A8/AP | A6    | A7   |

#### NOTE:

- 1. RFU1 is reserved for A12

- 2. RFU2 is reserved for BA2

- 3. (M,13) VREF for CMD and ADDRESS

- 4. (M,2) VREF for Data input

# PIN CONFIGURATION Mirror Package (Top View)

|          | <u>2</u> | <u>3</u> | <u>4</u> | <u>5</u> | <u>6</u>         | <u>7</u>   | <u>8</u>   | 9                | <u>10</u> | <u>11</u> | <u>12</u> | <u>13</u> |

|----------|----------|----------|----------|----------|------------------|------------|------------|------------------|-----------|-----------|-----------|-----------|

| <u>B</u> | DQS3     | /DQS3    | VSSQ     | DQ28     | DQ29             | DQ31       | DQ0        | DQ2              | DQ3       | VSSQ      | /DQS0     | DQS0      |

| <u>C</u> | DQ27     | DM3      | VDDQ     | VDDQ     | DQ30             | VDDQ       | VDDQ       | DQ1              | VDDQ      | VDDQ      | DM0       | DQ4       |

| <u>D</u> | DQ25     | DQ26     | VSSQ     | VSSQ     | VSSQ             | VDD        | VDD        | VSSQ             | VSSQ      | VSSQ      | DQ5       | DQ6       |

| <u>E</u> | DQ24     | VDDQ     | VDD      | VSS      | VSSQ             | VSS        | VSS        | VSSQ             | VSS       | VDD       | VDDQ      | DQ7       |

| <u>E</u> | DQ14     | DQ15     | VDDQ     | VSSQ     | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ      | VDDQ      | DQ16      | DQ17      |

| <u>G</u> | DQ12     | DQ13     | VDDQ     | VSSQ     | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ      | VDDQ      | DQ18      | DQ19      |

| <u>H</u> | DQS1     | /DQS1    | NC       | VSSQ     | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ      | NC        | /DQS2     | DQS2      |

| <u>J</u> | DQ11     | DM1      | VDDQ     | VSSQ     | NC,<br>VSS       | NC,<br>VSS | NC,<br>VSS | NC,<br>VSS       | VSSQ      | VDDQ      | DM2       | DQ20      |

| <u>K</u> | DQ10     | DQ9      | VDDQ     | VSSQ     | VSS              | VSS        | VSS        | VSS              | VSSQ      | VDDQ      | DQ22      | DQ21      |

| L        | DQ8      | A4       | VDD      | VSS      | RFU <sub>1</sub> | VDD        | VDD        | RFU <sub>2</sub> | VSS       | VDD       | А3        | DQ23      |

| <u>M</u> | VREF     | A5       | A9       | /CS      | ZQ               | NC         | CKE        | NC               | /RAS      | A10       | A2        | VREF      |

| <u>N</u> | A7       | A6       | A8/AP    | BA1      | /WE              | /CK        | CK         | /CAS             | BA0       | A11       | A1        | A0        |

<sup>\*</sup> Under consideration

# INPUT/OUTPUT FUNCTIONAL DESCRIPTION

| Symbol             | Туре             |                                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK             | Input            |                                                                            | e differenti <u>al cl</u> ock inputs. CMD, ADD inputs are sampled on the crossin <u>g of</u> the positive<br>we edge of CK. Output (read) data is referenced to the crossings of CK and CK (both direc-                                                                                                                                                                                                                                                                 |

| CKE                | Input            | and output drivers. Tak<br>or Active Power-Down<br>refresh entry. CKE is a | IGH activates, and CKE Low deactivates, internal clock signals and device input buffers ting CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), (row Active in any bank). CKE is synchronous for power down entry and exit, and for self synchronous for self refresh exit. CKE must be maintained high throughout read and write s, excluding CK, CK and CKE are disabled during power-down. Input buffers, excluding ng self refresh. |

| CS                 | Input            |                                                                            | ands <u>are masked when CS</u> is registered HIGH. CS provides for external bank selection on panks. CS is considered part of the command code.                                                                                                                                                                                                                                                                                                                         |

| RAS,<br>CAS,<br>WE | Input            | Command Inputs: RA                                                         | S, CAS and WE (along with CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                         |

| DM0<br>~DM3        | Input            | coincident with that inp                                                   | is an input mask signal for write data. Input data is masked when DM is sampled HIGH but data during a Write access. DM is sampled on both edges of clock. Although DM pins loading matches the DQ and DQS loading.                                                                                                                                                                                                                                                     |

| BA0,<br>BA1        | Input            |                                                                            | a: BAO and BA1 define to which bank an Active, Read, Write or Precharge command is to determines if the mode register or extended mode register is to be accessed during a                                                                                                                                                                                                                                                                                              |

| A0 -<br>A11        | Input            | for Read/Write comma<br>during a Precharge cor<br>HIGH). If only one ban   | ded the row address for Active commands and the column address and Auto Precharge bit nds to select one location out of the memory array in the respective bank. A8 is sampled mmand to determine whether the Precharge applies to one bank (A8 LOW) or all banks (A8 k is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide de Register Set commands.                                                                                |

| DQ                 | Input/<br>Output | Data Input/ Output: B                                                      | i-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    |                  | Data Strobe: output wiread data, centered in                               | ith read data, input with write data for source synchronous operation.Edge-aligned with write data.                                                                                                                                                                                                                                                                                                                                                                     |

| DQS0~              |                  | DQS Scheme                                                                 | Differential DQS per byte                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DQS3               | Input/           | DQS0, DQS0                                                                 | DQS0 for DQ0-DQ7                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DQS0~<br>DQS3      | Output           | DQS1, DQS1                                                                 | DQS1 for DQ8-DQ15                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DQSS               |                  | DQS2, DQS2                                                                 | DQS2 for DQ16-DQ23                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |                  | DQS3, DQS3                                                                 | DQS3 for DQ24-DQ31                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC/<br>RFU         |                  | No Connect: No intern                                                      | nal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{DDQ}$          | Supply           | DQ Power Supply: 1.8                                                       | 3V ± 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{SSQ}$          | Supply           | DQ Ground                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{DD}$           | Supply           | Power Supply: 2.5V ±                                                       | 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>SS</sub>    | Supply           | Ground                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>REF</sub>   | Supply           | Reference voltage: ha<br>2 Pins : (M,2) for Data                           | alf Vddq ,<br>input , (M,13) for CMD and ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ZQ                 | input            |                                                                            | n for On-die termination.<br>- 2 X (target value (Rterm) of termination resistance of DQ pin of each chip)                                                                                                                                                                                                                                                                                                                                                              |

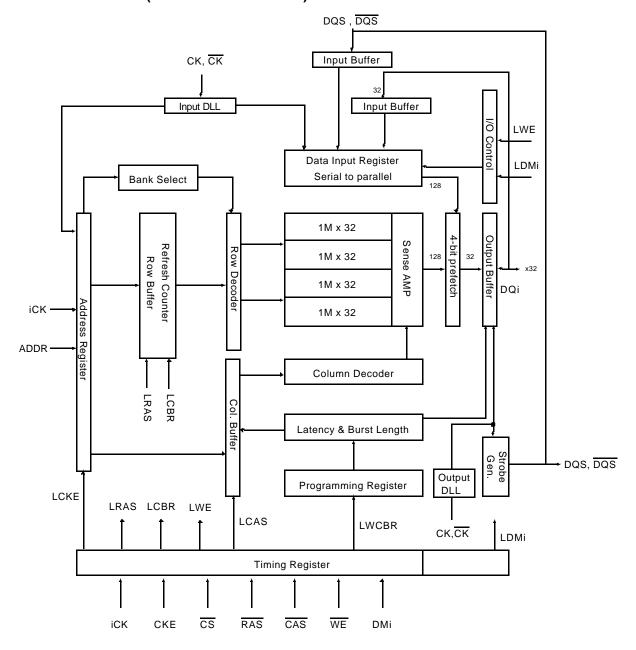

## BLOCK DIAGRAM (1Mbit x 32I/O x 4 Bank)

\* iCK : internal clock

## **FUNTIONAL DESCRIPTION**

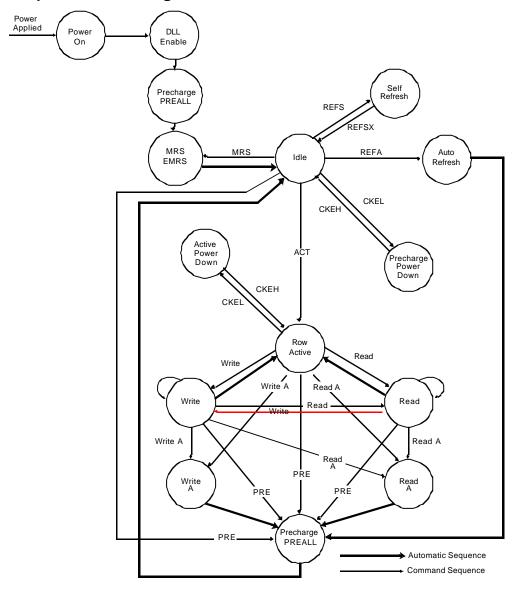

## **Simplified State Diagram**

PREALL = Precharge All Banks MRS = Mode Register Set EMRS = Extended Mode Register Set REFS = Enter Self Refresh REFSX = Exit Self Refresh REFA = Auto Refresh CKEL = Enter Power Down

CKEH = Exit Power Down

ACT = Active

Write A = Write with Autoprecharge

Read A = Read with Autoprecharge

PRE = Precharge

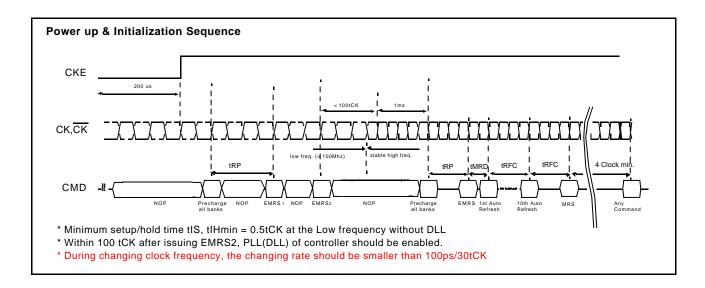

#### **Power-Up Sequence**

GDDR-II SDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations.

- 1. Power Up Sequence

- Apply Power and Keep CKE at low state. (All other inputs may be undefined)

- Apply VDD before VDDQ.

- Apply VDDQ before VREF.

- Start low frequency clock (100MHz) and maintain stable condition for minimum 200us.

- The minimum of 200us after stable power and clock (CK, /CK), apply NOP and take CKE to be high.

- Issue precharge command for all banks of the device (tS/tH =0.5tCK).

- Issue EMRS command to initialize DRAM with DLL OFF and On-die Termination OFF( tS/tH=0.5tCK) .

| BA1 | BA <sub>0</sub> | A11 | A10 | <b>A</b> 9 | A8 | <b>A</b> 7 | A6 | <b>A</b> 5 | A4 | Аз | A2 | A1 | A <sub>0</sub> | Address Bus               |

|-----|-----------------|-----|-----|------------|----|------------|----|------------|----|----|----|----|----------------|---------------------------|

| Ţ   | Ţ               | Ţ   | Ţ   | Ţ          | Ţ  | 1          | Ţ  | Į          | Į  | Ţ  | ļ  | Ţ  | ļ              |                           |

| 0   | 1               | 0   | Х   |            | Х  | •          | 0  | )          | X  | 0  | 0  | >  | <              | Extended Mode<br>Register |

- Issue EMRS command to control DLL and decide on-die termination state.

Within 100 clocks after issuing EMRS command for DLL on, stable high frequency clock should be supplied to DRAM.

| Ī | BA1 | BA <sub>0</sub> | A11 | A10 | <b>A</b> 9 | A8 | A7 | A6 | <b>A</b> 5 | A4 | Аз | A2 | A1  | Ao | Address Bus   |

|---|-----|-----------------|-----|-----|------------|----|----|----|------------|----|----|----|-----|----|---------------|

| _ | ļ   |                 | ļ   | Į   | ļ          | Ų  | ļ  | Į  | ļ          | ļ  | ļ  | ļ  | ļ   | Ÿ  | Extended Mode |

| Ī | 0   | 1               | 0   | V   | ,          | V  |    | 1  | \          | /  | V  | V  | , , | /  | Register      |

(V=Valid value)

- The additional 1ms clock cycles are required to lock the DLL and determine value of on-die termination after issuing EMRS command or supplying stable clock from a controller.

Apply NOP during Locking DLL to protect invalid command.

- Issue precharge command for all banks of the device.

- Issue EMRS command

- Issue at least 10 or more Auto refresh command to update the value of on-die termination.

- Issue a MRS command to initialize the mode register.

- Issue any command.

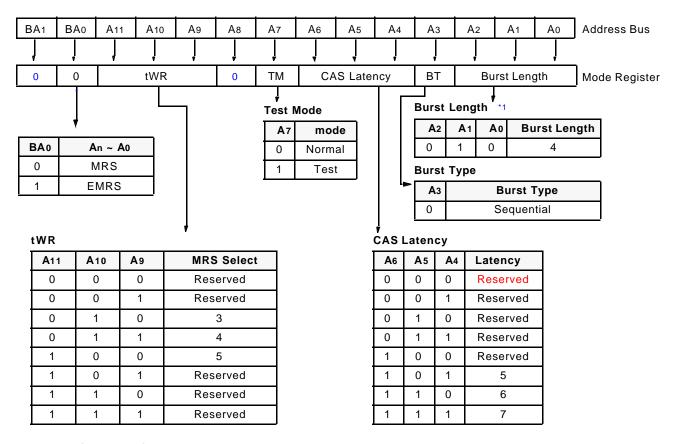

## MODE REGISTER SET(MRS)

The mode register stores the data for controlling the various operating modes of GDDR-II SDRAM. It programs CAS latency, addressing mode, test mode and various vendor specific options to make GDDR-II SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for proper operation. The mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  (The GDDR-II SDRAM should be in active mode with CKE already high prior to writing into the mode register). The state of address pins A0 ~ A11 and BA0, BA1 in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  going low is written in the mode register. Minimum four clock cycles are requested to complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A0 ~ A2, addressing mode uses A3, CAS latency (read latency from column address) uses A4 ~ A6. A7 is used for test mode. A9 ~ A11 are used for tWR. Refer to the table for specific codes for various addressing modes and CAS latencies.

\*1. BL 4, Sequential Only

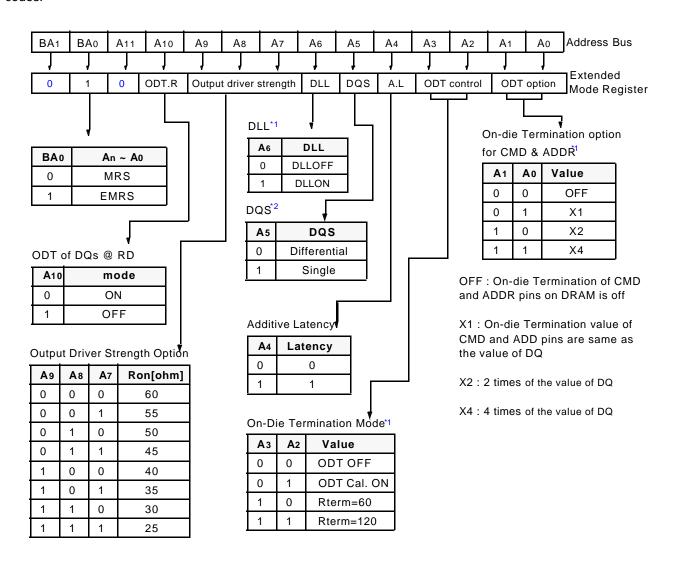

## **EXTENDED MODE REGISTER SET(EMRS)**

The extended mode register stores the data output <u>driver strength</u> and on-die termination options. The extended mode register is written by asserting low on <u>CS</u>, <u>RAS</u>, <u>CAS</u>, <u>WE</u> and high on BA0(The GDDR-II SDRAM should be in all bank precharge with CKE already high prior to <u>writing into the extended</u> mode register). The state of address pins A0 ~ A11 and BA0 in the same cycle as <u>CS</u>, <u>RAS</u>, <u>CAS</u> and <u>WE</u> going low are written in the extended mode register. Four clock cycles are required to complete the write operation in the extended mode register. 8 kinds of the output driver strength are supported by EMRS (A9, A8, A7) code. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. "High" on BA0 is used for EMRS. Refer to the table for specific codes.

<sup>\*1.</sup> DLL control, ODT control, and ODT option command should be issued at low frequency clock(<100Mhz) with tIS/tIH=0.5tCK

<sup>\*2.</sup> When single DQS is selected, 4 /DQS pins should be connected to VREF.

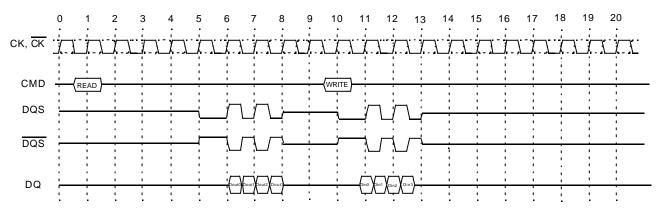

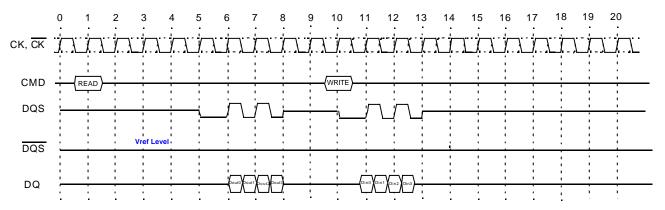

## **DQS**

| 500MHz           | 450MHZ           | 400MHz                         |

|------------------|------------------|--------------------------------|

| Differential DQS | Differential DQS | Differential DQS<br>Single DQS |

<sup>\*</sup> To support existing DDR-I user , single DQS is supported under 400MHz by EMRS option, When single DQS is selected, 4 /DQS pins should be connected to VREF.

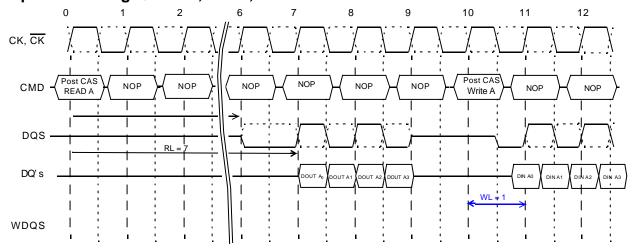

# Differntial DQS Timing (CL5, BL4)

## Single DQS Timing (CL5, BL4)

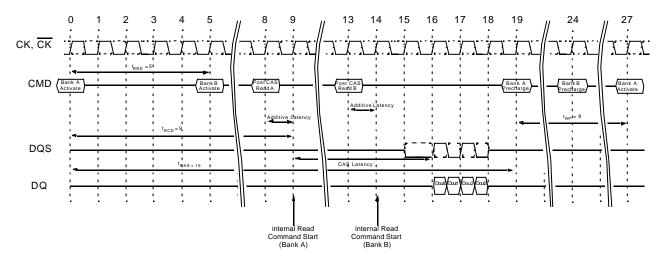

#### **Bank Activate Command**

The Bank Activate command is issued by holding  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  high with  $\overline{\text{CS}}$  and  $\overline{\text{RAS}}$  low at the rising edge of the clock. The bank addresses BA0 and BA1 are used to select the desired bank. The row address A0 through A11 is used to determine which row to activate in the selected bank. The Bank Activate command must be applied before any Read or Write operation can be executed. Immediately after the bank active command, the GDDR-II SDRAM can accept a read or write command on the following clock cycle. If a R/W command is issued to a bank that has not satisfied the tRCDmin specification, then additive latency must be programmed into the device to delay when the R/W command is internally issued to the device. The additive latency value must be chosen to assure tRCDmin is satisfied.

Additive latencies of (0,1) are supported. Once a bank has been activated it must be precharged before another Bank Activate command can be applied to the same bank. The bank active and precharge times are defined as tRAS and tRP, respectively. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device  $(t_{RC})$ , which is equal to tRAS + tRP. The minimum time interval between Bank Activate commands, Bank 0,1, 2, 3 (in any order), is the Bank to Bank delay time  $(t_{RRD})$ .

#### Bank Activate Command Cycle : CL=7, $t_{RCD}$ =9, AL=1, $t_{RP}$ =8, $t_{RRD}$ =5, $t_{CCD}$ =2, $t_{RAS}$ =19

#### **Read and Write Access Modes**

After a bank has been activated, a read or write cycle can be executed. This is accomplished by setting  $\overline{RAS}$  high,  $\overline{CS}$  and  $\overline{CAS}$  low at the clock's rising edge. The  $\overline{WE}$  must also be defined at this time to determine whether the access cycle is a read operation ( $\overline{WE}$  high) or a write operation ( $\overline{WE}$  low).

A new burst access must not interrupt the previous 4 bit burst operation. The minimum CAS to CAS delay is defined by tCCD, and is a minimum of 2 clocks for read or write cycles.

#### Write Latency

The Write Latency(WL) is always defined as AL(Additive Latency)+1 where Read Latency is defined as the sum of additive latency plus CAS latency (RL=AL+CL).

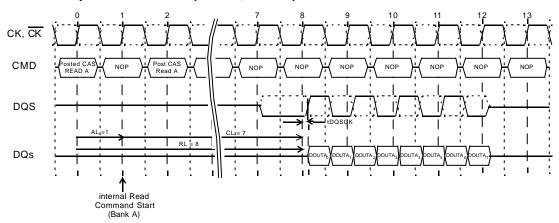

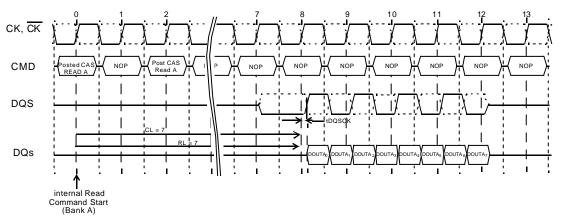

#### Posted CAS

Posted  $\overline{\text{CAS}}$  operation is supported to make command and data bus efficient for sustainable bandwidths in GDDR-II SDRAM. In this operation, the GDDR-II SDRAM allows a  $\overline{\text{CAS}}$  read or write command to be issued tRCDmin or 1 tCK earlier than tRCDmin after the  $\overline{\text{RAS}}$  bank activate command. The command is held for the time of the Additive Latency (AL) before it is issued inside the device. The Read Latency (RL) is controlled by the sum of AL and the  $\overline{\text{CAS}}$  latency (CL). Therefore if a user chooses to issue a R/W command before the tRCDmin, then AL (greater than 0) must be written into the FMRS.

## Examples of posted CAS operation

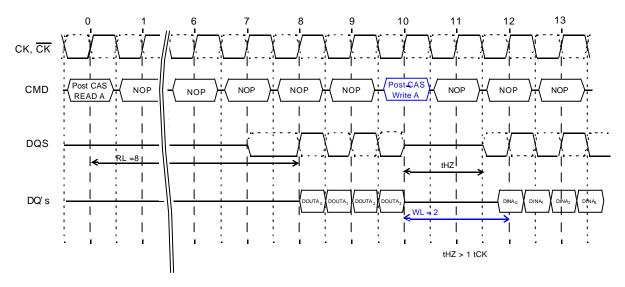

<u>Example 1</u> Read followed by a write to the same bank

$[AL = 1, t_{RCD} = 9, CL = 7, RL = (AL + CL) = 8, WL = (AL + 1) = 2]$

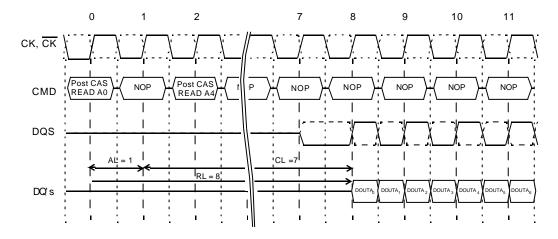

Example 2 Read followed by a write to the same bank

$[AL = 0, t_{RCD} = 9, CL = 7, RL = (AL + CL) = 7, WL = (AL + 1) = 1]$

#### **Burst Read Command**

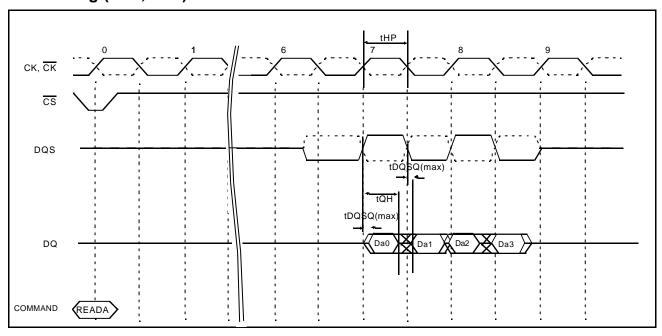

The Burst Read command is initiated by having  $\overline{CS}$  and  $\overline{CAS}$  low while holding  $\overline{RAS}$  and  $\overline{WE}$  high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The delay from the start of the command to when the data from the first cell appears on the outputs is equal to the value of the read latency (RL). The data strobe output (DQS) is driven low 1 clock before valid data (DQ) is driven onto the data bus. The first bit of the burst is synchronized with the rising edge of the data strobe (DQS). Each subsequent data-out appears on the DQ pin in phase with the DQS signal in a source synchronous manner. The RL is equal to an additive latency (AL) plus  $\overline{CAS}$  latency (CL). The CL is defined by the Mode Register Set (MRS), similar to the existing SDR and DDR-I SDRAMs. The AL is defined by the Extended Mode Register Set (EMRS).

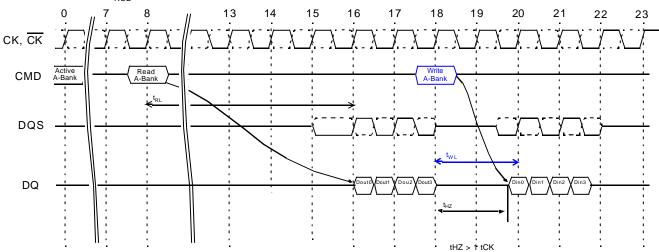

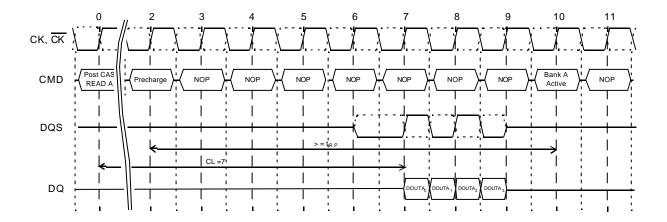

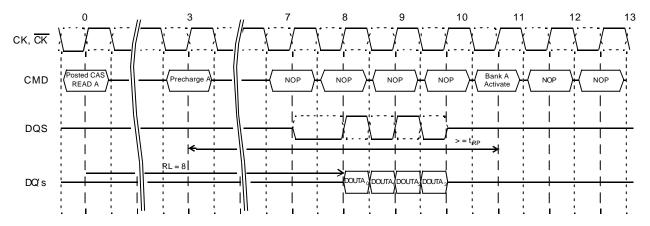

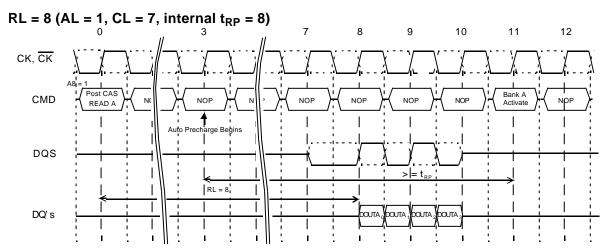

#### Burst Read Operation: RL = 8 (AL = 1, CL = 7)

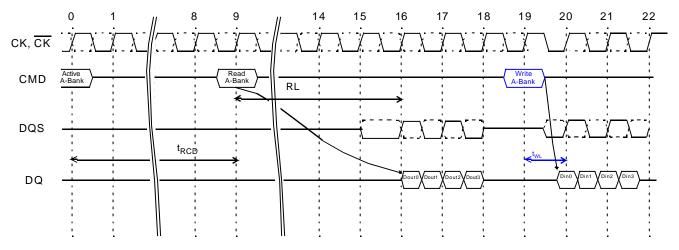

## Burst Read Operation: RL = 7 (AL = 0 and CL = 7)

## Burst Read followed by Burst Write: AL = 1, CL = 7, RL = 8, WL = (AL+1) = 2

## Seamless Burst Read Operation: CL = 7, AL = 1, RL = 8

The seamless burst read operation is supported by enabling a read command at every other clock. This operation is allowed regardless of same or different banks as long as the banks are activated.

#### **Burst Write Operation**

The Burst Write command is initiated by having  $\overline{CS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  low while holding  $\overline{RAS}$  high at the rising edge of the clock. The address inputs determine the starting column address. Write latency (WL) is defined by an Additive Latency(AL) plus one and is equal to (AL + 1). The first data bit of the burst cycle must be applied to the DQ pins at the first rising edge of the clock and at the first falling edge of the clock. The tDQSS specification must be satisfied for write cycles. The subsequent burst bit data are issued on successive edges of the clock until the burst length of 4 is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored. The DQ Signal is ignored after the burst write operation is complete. The time from the completion of the burst write to bank precharge is the write recovery time (tWR).

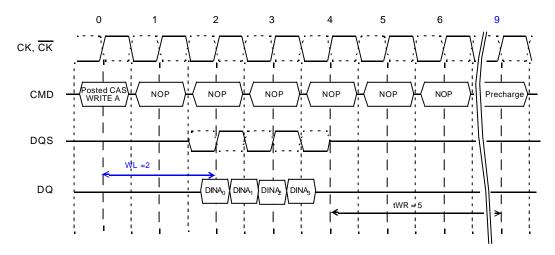

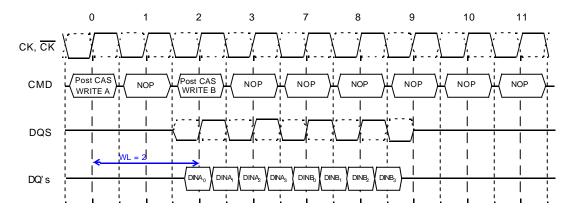

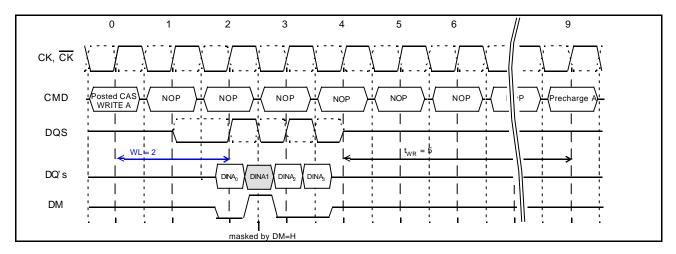

Burst Write Operation : AL= 1, CL = 7, WL = 2, t<sub>WR</sub> = 5

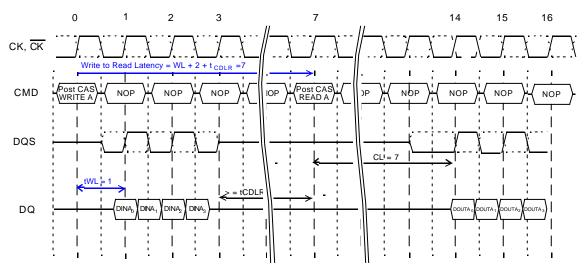

#### Burst Write followed by Burst Read : RL = 7 (AL=0, CL=7), WL = 1, tCDLR = 4

The minimum number of clock from the burst write command to the burst read command is WL+2+a write-to-read-turn-around-time(tCDLR).

## Seamless Burst Write Operation : AL = 1, CL = 7, WL = AL + 1 = 2

The seamless burst write operation is supported by enabling a write command every other clock. This operation is allowed regardless of same or different banks as long as the banks are activated

#### **Precharge Command**

The Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is triggered when  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{WE}$  are low and  $\overline{CAS}$  is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank independently or all banks simultaneously. Three address bits A8, BA0 and BA1 are used to define which bank to precharge when the command is issued.

|      | _           |             | -                  |

|------|-------------|-------------|--------------------|

| A8   | BA1         | BA0         | Precharged Bank(s) |

| LOW  | LOW         | LOW         | Bank 0 only        |

| LOW  | LOW         | HIGH        | Bank 1 only        |

| LOW  | HIGH        | LOW         | Bank 2 only        |

| LOW  | HIGH        | HIGH        | Bank 3 only        |

| HIGH | DON' T CARE | DON' T CARE | All Banks 0 ~ 3    |

**Bank Selection for Precharge by Address Bits**

#### **Burst Read Operation Followed by Precharge**

For the earliest possible precharge, the precharge command may be issued on the rising edge which is CAS latency (CL) clock cycles before the end of the read burst. A new bank active (command) may be issued to the same bank after the RAS precharge time ( $t_{RP}$ ). A precharge command cannot be issued until  $t_{RAS}$  is satisfied.

## Burst Read Operation Followed by Precharge: RL = 7 (AL=0, CL=7), t<sub>RP</sub>= 8

## Burst Read Operation Followed by Precharge: RL = 8 (AL=1, CL=7, t<sub>RP</sub> =8)

## **Burst Write followed by Precharge**

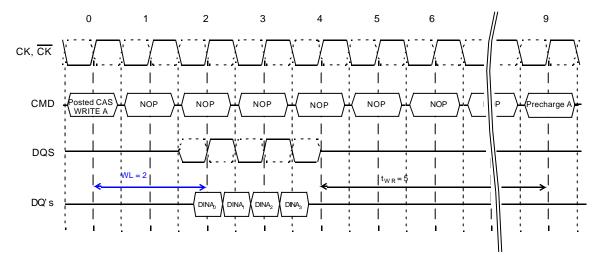

For write cycles, a delay must be satisfied from the completion of the last burst write cycle until the Precharge Command can be issued. This delay is known as a write recovery time  $(t_{WR})$  referenced from the completion of the burst write to the precharge command. No Precharge command should be issued prior to the tWR delay, as GDDR-II SDRAM does not support any burst interrupt operation.

## Burst Write followed by Precharge: AL = 1, CL = 7, WL = AL + 1 = 2, $t_{WR} = 5$

#### **DM FUNCTION**

The DDR SDRAM has a Data mask function that can be used in conjunction with data Write cycle only, not Read cycle. When the Data Mask is activated (DM high) during write operation the write data is masked immediately (DM to Data-mask Latency is zero).

DM must be issued at the rising edge or the falling edge of Data Strobe instead of a clock edge.

#### **Auto-Precharge Operation**

Before a new row in an active bank can be opened, the active bank must be precharged using either the Precharge Command or the auto-precharge function. When a Read or a Write Command is given to the GDDR-II SDRAM, the CAS timing accepts one extra address, column address A8, to allow the active bank to automatically begin precharge at the earliest possible moment during the burst read or write cycle. If A8 is low when the READ or WRITE Command is issued, then normal Read or Write burst operation is executed and the bank remains active at the completion of the burst sequence. If A8 is high when the Read or Write Command is issued, then the auto-precharge function is engaged.

This feature allows the precharge operation to be partially or completely hidden during burst read cycles (dependent upon  $\overline{\text{CAS}}$  latency) thus improving system performance for random data access. The RAS lockout circuit internally delays the Precharge operation until the array restore operation has been completed so that the auto precharge command may be issued with any read or write command.

Auto-precharge also be implemented during Write commands. The precharge operation engaged by the Auto precharge command will not begin until the last data of the burst write sequence is properly stored in the memory array.

#### **Burst Read with Auto Precharge**

If A8 is high when a Read Command is issued, the Read with Auto-Precharge function is engaged. The GDDR-II SDRAM starts an Auto Precharge operation on the rising edge which is (AL + BL/2)cycles later from the read with Auto Precharge command, when tRAS(min) is satisfied. If tRAS(min) is not satisfied at the edge, the start point of Auto Precharge operation will be delayed until tRAS(min) is satisfied. A new bank active command may be issued to the same bank if the following two conditions are satisfied simultaneously.

- (1) The RAS precharge time (tRP) has been satisfied from the clock at which the auto precharge begins.

- (2) The RAS cycle time (tRC) from the previous bank activation has been satisfied.

When the Read with Auto-Precharge command is issued, new command (Read, Read with Auto Precharge or precharge) of same bank can be asserted tCCD=2 clock cycles later.

#### Burst Read with Auto Precharge Followed by Same Bank Activation :

#### Burst Read with Auto Precharge (AL=0)

| Asserted                 |         | For sar | ne bank |         | For different bank |       |       |       |  |

|--------------------------|---------|---------|---------|---------|--------------------|-------|-------|-------|--|

| command                  | 1       | 2       | 3       | 4       | 1                  | 2     | 3     | 4     |  |

| READ                     | Illegal | Legal   | Illegal | Illegal | Illegal            | Legal | Legal | Legal |  |

| READ with Auto Precharge | Illegal | Legal   | Illegal | Illegal | Illegal            | Legal | Legal | Legal |  |

| Active                   | Illegal | Illegal | Illegal | Illegal | Legal              | Legal | Legal | Legal |  |

| Precharge                | Illegal | Legal   | Illegal | Illegal | Legal              | Legal | Legal | Legal |  |

\*When AL(Additive Latency) is 1, a precharge command for same bank can be issued at 3th cycle only and others are same with AL=0.

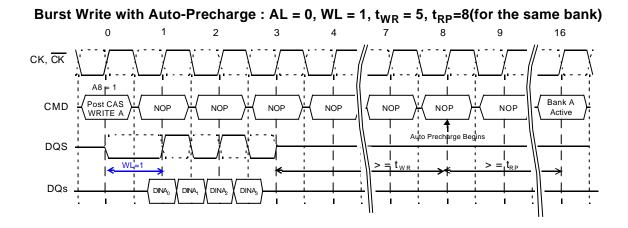

#### **Burst Write with Auto-Precharge**

If A8 is high when a Write Command is issued, the Write with Auto-Precharge function is engaged. The GDDR-II SDRAM automatically begins precharge operation after the completion of the burst write plus write recovery time (tWR). Interruption of the Write with Auto-Precharge function is prohibited. Active command of same bank can be issued WL+tWR+tRP+BL/2 cycles later from the Write with Auto-Precharge command. The bank undergoing Auto-Precharge from the completion of the write burst may be reactivated if the following two conditions are satisfied.

- (1) The data-in to bank activate delay time (tWR + tRP) has been satisfied.

- (2) The RAS cycle time (tRC) from the previous bank activation has been satisfied.

#### **Burst Write with Auto-Precharge (AL=0)**

| Asserted                  |         | For sa  | me bank | _       |         | For different bank |       |  |  |

|---------------------------|---------|---------|---------|---------|---------|--------------------|-------|--|--|

| command                   | 1 ~ 7   | 8       | 9 ~ 15  | 16      | 1       | 2 ~ 6              | 7     |  |  |

| WRITE                     | Illegal | Illegal | Illegal | Illegal | Illegal | Legal              | Legal |  |  |

| WRITE with Auto Precharge | Illegal | Illegal | Illegal | Illegal | Illegal | Legal              | Legal |  |  |

| READ                      | Illegal | Illegal | Illegal | Illegal | Illegal | Illegal            | Legal |  |  |

| READ with Auto Precharge  | Illegal | Illegal | Illegal | Illegal | Illegal | Illegal            | Legal |  |  |

| Active                    | Illegal | Illegal | Illegal | Legal   | Legal   | Legal              | Legal |  |  |

| Precharge                 | Illegal | Illegal | Illegal | Illegal | Legal   | Legal              | Legal |  |  |

| All Bank Precharge        | Illegal | Legal   | Legal   | Legal   |         | -                  |       |  |  |

<sup>\*</sup>When AL(Additive Latency) is 1, a active command for same bank can be issued from 17th cycle, a READ or READ with Auto Precharge command for different bank can be issued from 8th cycle and others are same with AL=0.

<sup>\*</sup> All Bank Precharge command can be issued from 8th cycle.

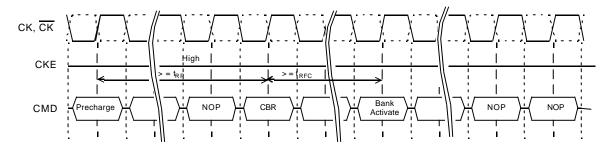

## Automatic Refresh Command (CAS Before RAS Refresh)

When  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  are held low and  $\overline{\text{WE}}$  high at the rising edge of the clock, the chip enters the Automatic Refresh mode (CBR). All banks of the GDDR-II SDRAM must be precharged and idle for a minimum of the Precharge time ( $t_{\text{RP}}$ ) before the Auto Refresh Command (CBR) can be applied. An address counter, internal to the device, supplies the bank address during the refresh cycle. No control of the external address bus is required once this cycle has started.

When the refresh cycle has completed, all banks of the GDDR-II SDRAM will be in the precharged (idle) state. A delay between the Auto Refresh Command (CBR) and the next Activate Command or subsequent Auto Refresh Command must be greater than or equal to the Auto Refresh cycle time ( $t_{RFC}$ ).

#### **Self Refresh Command**

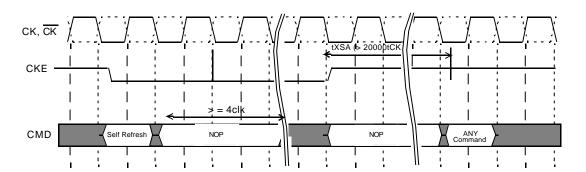

The GDDR-II SDRAM device has a built-in timer to accommodate Self Refresh operation. The Self Refresh Command is defined by having  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and CKE held low with  $\overline{WE}$  high at the rising edge of the clock. Once the Self Refresh Command is registered, CKE must be held low to keep the device in Self Refresh mode and NOP command should be issued or  $\overline{CS}$  should be held high to ensure stable self refresh operation for next four cycles after the Self Refresh Command. When the GDDR-II SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The user may halt the external clock while the device is in Self Refresh mode, however, the clock must be restarted before the device can exit Self Refresh operation. After CKE is brought high, an internal timer is started to insure CKE is held high for approximately 10ns before registering the Self Refresh exit command. The purpose of this circuit is to filter out noise glitches on the CKE input which may cause the GDDR-II SDRAM to erroneously exit Self Refresh operation. Once the Self Refresh exit command is registered, a delay equal or longer than the tXSA (>20000 tck) must be satisfied before any command can be issued to the device. CKE must remain high for the entire Self Refresh exit period (tXSA > 20000tCK) and commands must be gated off with  $\overline{CS}$  held high. Alternatively, NOP commands may be registered on each positive clock edge during the Self Refresh exit interval. (See Figure.)

\*After self refresh entry, NOP or chip deselect command should be issued during more than 4 cycles and chip deselet command should be issued for tXSA after self refresh exit.

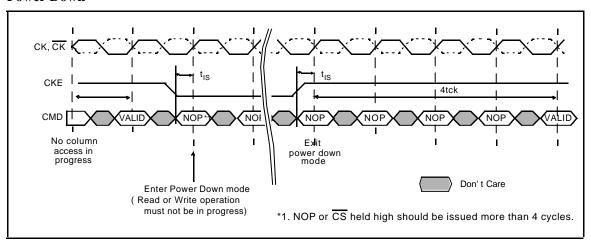

#### Power-Down

Power-down is entered when CKE is registered LOW (no accesses can be in progress). If power-down occurs when all banks are idle, this mode is referred to as precharge power-down; if power-down occurs when there is a row active in any bank, this mode is referred to as active power-down. Entering power-down deactivates the input and output buffers, excluding CK, CK and CKE. During 4 cycles after power down mode issued, NOP should be issued or CS must be held high. In Power Down mode, CKE Low and a stable clock signal must be maintained at the inputs of the GDDR-II SDRAM, and all other input signals are "Don' t Care" except first 4 cycles after power down mode issued. Power-down duration is limited by the refresh requirements of the device.

The power-down state is synchronously exited when CKE is registered HIGH (along with a NOP or  $\overline{\text{CS}}$  hold high). A valid, executable command may be applied four clock cycles later.

#### **Power Down**

\*CL + 2tCK after read or CL after last data in, a power-down command can be issued.

#### **Burst Interruption**

Interruption of a burst read or write cycle is prohibited.

#### **No Operation Command**

The No Operation Command should be used in cases when the GDDR-II SDRAM is in an idle or a wait state. The purpose of the No Operation Command is to prevent the GDDR-II SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle. The Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when CS is brought high at the rising edge of the clock, the RAS, CAS, and WE signals become don't cares

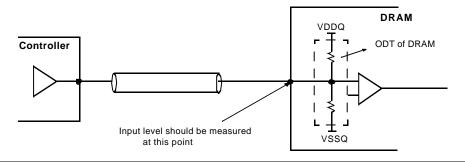

#### **On-Die Termination**

All pins except ZQ, CKE Pins adopt on-die termination to improve signal integrity of channel. The On-Die Termination should be controlled by EMRS command at low frequency clock (<100Mhz). The On-Die Termination control command should be issued before issuing DLLON command by EMRS or simultaneously to guarantee stable channel condition of /CK and CK pins. If A3, A2 = 0, 0, the On-Die Termination of all pins will be deactivated. If A3, A2 = 0, 1, the On-Die Termination will be self-calibrated by detecting the external Resistor on ZQ pin. If A3, A2 = 1, 0, the value of the On-Die Termination of CK, /CK, 32 DQ' s, 4 DM' s, 4 /DQS' s and 4DQS pins will be the fixed value, 600hm. If A3, A2 = 1, 1, the value of the On-Die Termination of CK, /CK, 32 DQ' s, 4 DM' s, 4 /DQS' s and 4DQS pins will be the fixed value, 1200hm.

If A3, A2 = 0, 1 is issued by EMRS, the value of the on-die termination of each pin is determined by monitoring the value of a external resistor which is connected between ZQ pin and VSSQ, and updated every CBR refresh cycle to compensate variation of voltage and temperature.

The value of On-Die Termination of CMD and ADD (/RAS, /CAS, /WE, /CS, BA0, BA1 and A0  $\sim$  A11) pins of each DRAM depend on EMRS code (A1, A0). If A1, A0 = 0, 0, the On-die Termination of CMD and ADD pins will be deactivated. If A1, A0 = 0, 1, the value of the On-die Termination of CMD and ADD pins will be same value as the value of DQ pins. If A1, A0 = 1, 0, the value of the On-Die Termination of CMD and ADD pins will be two times of the value of DQ pins. If A1, A0 = 1, 1, the value of the On-Die Termination of CMD and ADD pins will be four times of the value of DQ pins.

#### The On-Die Termination for one bank system with self-calibration code (A3, A2 = 0, 1)

The value of external resistor (Rref) at external one bank system is 2 times of target termination value of DQ's on channel (Rterm). Then the value of On-Die Termination of CK, /CK, 32 DQ's, 4 DM's, 4 /DQS's and 4DQS pins is half value of the external resistor. The value of On-Die Termination of CMD and ADD (/RAS, /CAS, /WE, /CS, BA0, BA1 and A0 ~ A11) pins of each DRAM depend on EMRS code (A2, A0).

The following figure shows the typical external one bank system having on-die termination.

#### Front Side DRAMs ak/ak CK./CK ADD ADD /RAS./CAS./WE./CS RAS/CAS/ME/CS DMs,DQS, DM's DO'S DOG s/DOG s DQS' s/DQS' s CK/CK CK./CK ZC 4DD 2XRterm RAS/CAS/WE/C DM' s, DQ' S DQS' s/DQS' s DMsD0'S DQS s/DQS s CK,/CK ak/ak ADD /CS 2XRterm /RAS./CAS./WE RAS/CAS/ME/CS DMsDQS DM' s, DQ' S DQS' s/DQS' s DQS s/DQS s CK/CK 70 CK /CK ADD RAS/CAS/WE/CS DMsDQS

DQSs/DQSs

## **Block Diagram of 1 Bank System**

re Rterm is the termination value on charnnel

The On-die Termination on/off status on DRAM is in accompany with DRAM operation mode.

Power consumption by On-die termination can be reduced by issuing power down mode.

# On-Die Termination (ODT) Status of 1 Bank System

| Mode         |           | Pin                           | ODT of DRAM |

|--------------|-----------|-------------------------------|-------------|

| Self_refres  | sh        | All                           | OFF         |

| Power Dov    | vn.       | CK, /CK                       | ON          |

| Power Dov    | VII       | Other pins                    | OFF         |

| Active       |           | All                           | ON          |

| All banks i  | llo.      | CK, /CK, ADD's, CMD           | ON          |

| All banks in | ile .     | DQ' s, DQS' s, /DQS' s, DM' s | ON          |

|              | A10=1     | CK, /CK, ADD's, CMD, DM,s     | ON          |

| READ         | A I U = I | DQ's, DQS's, /DQS's           | OFF         |

| READ         | A10=0     | CK, /CK, ADD's, CMD, DM,s     | ON          |

|              | A 10=0    | DQ' s, DQS' s, /DQS' s        | ON          |

<sup>\*</sup> A10 in EMRS code is used for On-Die Termination of DQ's off when Read data comes out

#### The On-die Termination for external two bank system with self-calibration code (A3, A2 = 0, 1)

The external resistor (Rref) is equal to 2X the number of shared DRAM's on one channel X target termination value of DQ channel. The following figure is represented the typical two bank system having on-die termination. 4 DRAM's share one channel for CMD and ADD pins and 2 DRAM's share one channel for DQ's and CLK pins. The external resistor (Rref) is 4 times of target termination value on channel. The On-die Termination value of CK, /CK, 32 DQ's, 4 DM's, 4 /DQS's and 4DQS pins on channel is half value of the external resistor (Rref).

#### Front Side DRAM's Back Side DRAM's CK,/CK CK,/CK ADD /RAS,/CAS, /WE, /CS ADD /RAS, /CAS, /WE, /CS DM's, DQ's, DQS's, IDQS's DM's, DQ's, DQS's, /DQS's DM's, DQ's, DQS's, IDQS' CK./CK CK./CK ADD /RAS,/CAS, /WE, /CS DM's, DQ's, DQS's, /DQS's /WE. /CS DM's, DQ's, DQS's, /DQS's DM's, DQ's, DQS's, /DQS's CK,/CK CK./CK CK /CK zq /RAS, /CAS, /WE, /CS DM's, DQ's, DQS's, IDQS's CK,/CK zq zq ADD RAS./CAS. DM's, DQ's, DM's, DQ's, DQS's, /DQS DQS's, /DQS's

## **Block Diagram of 2 Banks System**

Self-refresh and power down mode in two bank system should be issued for all DRAM's at the same time to keep suitable On-die termination condition on channel.

| Mo             | de         |        | Di-                           | DR  | AM         | D l     |     |    |

|----------------|------------|--------|-------------------------------|-----|------------|---------|-----|----|

| M1             | N          | 12     | Pin                           | M1  | M2         | Remarks |     |    |

| Self_refresh   | Self_r     | efresh | All                           | OFF | OFF        | *1      |     |    |

| Self_refresh   | Other      | States | All                           |     |            | Illegal |     |    |

| Power down     | Dawe       |        | CK,/CK                        | ON  | ON         |         |     |    |

| Power down     | Power down |        | Power down                    |     | Other pins | OFF     | OFF | *1 |

| Power down     | Other      | States |                               |     |            | Illegal |     |    |

|                | Active     |        | CK, /CK, ADD' s, CMD          | ON  | ON         |         |     |    |

|                | AC         | tive   | DQ' s, DQS' s, /DQS' s, DM' s | ON  | ON         |         |     |    |

| All Banks idle |            | 440.4  | CK, /CK, ADD' s, CMD          | ON  | ON         |         |     |    |

| All Banks Idle | Dand       | A10=1  | DQ' s, DQS' s, /DQS' s, DM' s | ON  | OFF        |         |     |    |

|                | Read       | 440.0  | CK, /CK, ADD's, CMD           | ON  | ON         |         |     |    |

|                |            | A10=0  | DQ' s, DQS' s, /DQS' s, DM' s | ON  | ON         |         |     |    |

|                |            | 440.4  | CK, /CK, ADD' s, CMD          | ON  | ON         |         |     |    |

| Active         | A10=1      |        | DQ' s, DQS' s, /DQS' s, DM' s | ON  | OFF        |         |     |    |

| Active         | Read       | 440.0  | CK, /CK, ADD's, CMD           | ON  | ON         |         |     |    |

|                |            | A10=0  | DQ' s, DQS' s, /DQS' s, DM' s | ON  | ON         |         |     |    |

<sup>1.</sup> With these case, the system couldn't have suitable Rterm.

Because the On-Die termination value on channel is two times than the target value.

#### 4. Command Truth Table.

|                            | Cł                | ΚE               |    |     |     |    |    |         |             |             |         |        |

|----------------------------|-------------------|------------------|----|-----|-----|----|----|---------|-------------|-------------|---------|--------|

| Function                   | Previous<br>Cycle | Current<br>Cycle | cs | RAS | CAS | WE | DM | BA0/BA1 | A11 - A9    | A8          | A7 - A0 | Notes  |

| Mode Register Set          | Н                 | Х                | L  | L   | L   | L  | Х  | BA0     | = 0 and MR  | SOP         | Code    | 1      |

| Extended Mode Register Set | Н                 | X                | L  | L   | L   | L  | Х  | BA0 =   | = 1 and EMF | RS OP       | Code    | 1      |

| Auto (CBR) Refresh         | Н                 | Н                | L  | L   | L   | Η  | Х  | Х       | Х           | Х           | Х       | 1      |

| Entry Self Refresh         | Н                 | L                | L  | L   | L   | Н  | Х  | х       | Х           | Х           | Х       | 1      |

| Fuit Oalf Dafaaah          | L                 | Н                | Н  | Х   | Х   | Х  | Х  | Х       | Х           | Х           | Х       | 1      |

| Exit Self Refresh          | L                 | Н                | L  | Н   | Н   | Η  | Х  | Х       | Х           | Х           | Х       |        |

| Single Bank Precharge      | Н                 | Х                | L  | L   | Н   | L  | Х  | ВА      | Х           | L           | Х       | 1,2    |

| Precharge all Banks        | Н                 | Х                | L  | L   | Н   | L  | Х  | Х       | Х           | Н           | Х       | 1      |

| Bank Activate              | Н                 | X                | L  | L   | Н   | Η  | Х  | BA      | Rov         | Row Address |         | 1,2    |

| Write                      | Н                 | Х                | L  | Н   | L   | L  | Х  | BA      | Х           | L           | Column  | 1,2,3, |

| Write with Auto Precharge  | Н                 | Х                | L  | Н   | L   | L  | Х  | ВА      | Х           | Н           | Column  | 1,2,3, |

| Read                       | Н                 | Х                | L  | Н   | L   | Н  | Х  | BA      | Х           | L           | Column  | 1,2,3  |

| Read with Auto-Precharge   | Н                 | Х                | L  | Н   | L   | Η  | Х  | BA      | Х           | Н           | Column  | 1,2,3  |

| DM                         | Н                 | Х                | Х  | Х   | Х   | Х  | DM | х       | Х           | Х           | Х       | 6      |

| No One section             | Н                 | Х                | L  | Н   | Н   | Н  | Х  | Х       | Х           | Х           | Х       | 1      |

| No Operation               | Н                 | Х                | Н  | Х   | Х   | Х  | Х  | х       | Х           | Х           | Х       | 1      |

| Dawer Dawe Made Enter      | Н                 | L                | Н  | Х   | Х   | Х  | Х  | Х       | Х           | Х           | Х       | 1,4,5  |

| Power Down Mode Entry      | Н                 | L                | L  | Н   | Н   | Н  | Х  | Х       | Х           | Х           | Х       |        |

| Davida Davida Maria Erri   | L                 | Н                | Н  | Х   | Х   | Х  | Х  | Х       | Х           | Х           | Х       | 1,4,5  |

| Power Down Mode Exit       | L                 | Н                | L  | Н   | Н   | Н  | Х  | Х       | Х           | Х           | Х       |        |

- 1. All of the GDDR-II SDRAM operations are defined by states of  $\overline{CS}$ ,  $\overline{WE}$ ,  $\overline{RAS}$ , and  $\overline{CAS}$  at the positive rising edge of the clock.

- 2. Bank Select (BA0,1), determine which bank is to be operated upon.

- 3. Burst read or write cycle may not be terminated.

- 4. The Power Down Mode does not perform any refresh operations, therefore the device can't remain in this mode longer than the Refr esh period (t<sub>REF</sub>) of the device. Four clock delay is required for mode entry and exit.

- 5. If  $\overline{\text{CS}}$  is low, then when CKE returns high, no command is registered into the chip for one clock cycle.

- 6. DM sampled at the rising and falling edges of the DQS and Data-in are masked at the both edges (Write DM latency is 0).

(V=Valid, X=Don' t Care, H=Logic High, L=Logic Low)

## 5. Clock Enable (CKE) Truth Table

|                             | Ch                | KE               |    | _   | Con                 | nmand |                       |                                                         |       |

|-----------------------------|-------------------|------------------|----|-----|---------------------|-------|-----------------------|---------------------------------------------------------|-------|

| Current State               | Previous<br>Cycle | Current<br>Cycle | cs | RAS | CAS                 | WE    | BA1, BA0,<br>A11 - A0 | Action                                                  | Notes |

|                             | Н                 | Х                | Х  | Х   | Х                   | Х     | Х                     | INVALID                                                 | 1     |

|                             | L                 | Н                | Н  | Х   | Х                   | Х     | Х                     | Exit Self Refresh with Device Deselect                  | 2     |

| Self Refresh                | L                 | Н                | L  | Н   | Н                   | Н     | Х                     | Exit Self Refresh with No Operation                     | 2     |

|                             | L                 | Н                | L  | C   | Command             | b     | Address               | ILLEGAL                                                 | 2     |

|                             | L                 | L                | Х  | Х   | Х                   | Х     | Х                     | Maintain Self Refresh                                   |       |

|                             | Н                 | Х                | Х  | Х   | Х                   | Х     | Х                     | INVALID                                                 | 1     |

|                             | L                 | Н                | Н  | Х   | Х                   | Х     | Х                     | Power Down mode exit, all banks idle                    | 2     |

| Power Down                  | L                 | Н                | L  | Н   | Η                   | Н     | Х                     | Exit Power Down mode with No Operation                  | 2     |

|                             | L                 | Н                | L  | C   | Command             | t     | Address               | ILLEGAL                                                 | 2     |

|                             | L                 | L                | Х  | Х   | Х                   | Х     | Х                     | Maintain Power Down Mode                                |       |

|                             | Н                 | Н                | Н  | Х   | Х                   | Х     |                       | Device Deselect                                         | 3     |

|                             | Н                 | Н                | L  | C   | Command             | t     | Address               | Refer to the Current State Truth Table                  | 3     |

| All Banks Idle              | Н                 | L                | Н  | Х   | Х                   | Х     |                       | Power Down                                              |       |

|                             | Н                 | L                | L  |     | and exce<br>sh comm |       | Х                     | ILLEGAL                                                 |       |

|                             | Н                 | L                | L  | L   | L                   | Н     | Х                     | Entry Self Refresh                                      | 4     |

|                             | Н                 | Н                | Х  | Х   | Х                   | Х     | Х                     | Refer to operations in the Current State<br>Truth Table |       |

| Any State other than listed | Н                 | L                | Х  | Х   | Х                   | Х     | Х                     | Power Down                                              | 5     |

| above                       | L                 | Н                | Х  | Х   | Х                   | Х     | Х                     | Power Down                                              |       |

|                             | L                 | L                | Х  | Х   | Х                   | Х     | Х                     | Power Down                                              |       |

- 1. For the given Current State CKE must be low in the previous cycle.

- 2. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. The minimum setup time for CKE (t<sub>CES</sub>) must be satisfied before any command other than self refresh exit.

- 3. The inputs (BA1, BA0, A11 A0) depend on the command that is issued. See the Current State Truth Table for more information.

- 4. The Auto Refresh, Self Refresh Mode, and the Mode Register Set modes can only be entered from the all banks idle state.

- 5. Must be a legal command as defined in the Current State Truth Table.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                             | Symbol    | Value      | Unit |

|---------------------------------------|-----------|------------|------|

| Voltage on any pin relative to Vss    | VIN, VOUT | -0.5 ~ 3.6 | V    |

| Voltage on VDD supply relative to Vss | VDD       | -1.0 ~ 3.6 | V    |

| Voltage on VDD supply relative to Vss | VDDQ      | -0.5 ~ 3.6 | V    |

| Storage temperature                   | Tstg      | -55 ~ +150 | °C   |

| Power dissipation                     | PD        | 4.5        | W    |

| Short circuit current                 | los       | 50         | mA   |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

## POWER & DC OPERATING CONDITIONS(SSTL\_18 In/Out)

Recommended operating conditions (Voltage referenced to Vss=0V, Tj=0 to 100°C)

| Parameter                   | Symbol   | Min        | Тур | Max        | Unit | Note |

|-----------------------------|----------|------------|-----|------------|------|------|

| Device Supply voltage       | VDD      | 2.4        | 2.5 | 2.6        | V    | 1    |

| Output Supply voltage       | VDDQ     | 1.7        | 1.8 | 1.9        | V    | 1    |

| Reference voltage           | VREF     | 0.49*V DDQ | -   | 0.51*V DDQ | V    | 2    |

| DC Input logic high voltage | VIH (DC) | VREF+0.125 | -   | VDDQ+0.30  | V    | 4    |

| DC Input logic low voltage  | VIL (DC) | -0.30      | -   | VREF-0.125 | V    | 5    |

| AC Input logic high voltage | VIH(AC)  | VREF+0.25  | -   | -          | V    |      |

| AC Input logic low voltage  | VIL(AC)  | -          | -   | VREF-0.25  | V    |      |

| Output logic high voltage   | Voн      | Vtt+0.4    | -   | -          | V    | 6    |

| Output logic low voltage    | Vol      | -          | -   | Vtt-0.4    | V    | 6    |

| Input leakage current       | lı∟      | -5         | -   | 5          | uA   | 7    |

| Output leakage current      | loL      | -5         | -   | 5          | uA   | 7    |

Note: 1. Under all conditions VDDQ must be less than or equal to VDD.

- 2. VREF is expected to equal 0.50\*VDDQ of the transmitting device and to track variations in the DC level of the same. Peak to peak noise on the VREF may not exceed + 2% of the DC value. Thus, from 0.50\*VDDQ, VREF is allowed + 25mV for DC error and an additional + 25mV for AC noise.

- 3. Vtt of the transmitting device must track VREF of the receiving device.

- 4. VIH(max.) = VDDQ +1.5V for a pulse and it which can not be greater than 1/3 of the cycle rate.

- 5. VIL(mim.) = -1.5V for a pulse width and it can not be greater than 1/3 of the cycle rate.

- 6. Output logic high voltage and low voltage is depend on channel condition.(Ract, Ron)

- 7. For any pin under test input of  $0V \le VIN \le VDD$  is acceptable. For all other pins that are not under test VIN=0V

#### DC CHARACTERISTICS

Recommended operating conditions Unless Otherwise Noted, Tj=0 to 100°C)

| Parameter Svm                                    |        | Took Comdition                                                                                             |      | Version |      | Unit | Nata |

|--------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------|------|---------|------|------|------|

| Parameter                                        | Symbol | Test Condition                                                                                             | -20  | -22     | -25  | Unit | Note |

| Operating Current<br>(One Bank Active)           | ICC1   | Burst Lenth=4 tRC ≥ tRC(min) IoL=0mA, tcc= tcc(min)                                                        | 590  | 540     | 500  | mA   | 1    |

| Precharge Standby Current in Power-down mode     | ICC2P  | CKE ≤ VIL(max), tcc= tcc(min)                                                                              | 110  | 100     | 95   | mA   |      |

| Precharge Standby Current in Non Power-down mode | Icc2N  | CKE $\geq$ VIH(min), CS $\geq$ VIH(min), tcc= tcc(min) 230 210 190 n                                       |      | mA      |      |      |      |

| Active Standby Current power-down mode           | ІссзР  | CKE ≤ VIL(max), tcc= tcc(min) 110 100 95                                                                   |      | 95      | mA   |      |      |

| Active Standby Current in in Non Power-down mode | Icc3N  | $\label{eq:cke} \begin{split} CKE & \geq VIH(min), \; CS \geq VIH(min), \\ tcc= & \; tcc(min) \end{split}$ | 510  | 470     | 430  | mA   |      |

| Operating Current<br>( Burst Mode)               | ICC4   | IOL=0mA ,tcc= tcc(min), Page Burst, All Banks activated.                                                   | 1200 | 1100    | 990  | mA   |      |

| Refresh Current                                  | ICC5   | trc≥ trfc                                                                                                  | 370  | 350     | 330  | mA   | 2    |

| Self Refresh Current                             | ICC6   | CKE ≤ 0.2V 7                                                                                               |      | mA      |      |      |      |

| Operating Current<br>(4Bank interleaving)        | ICC7   | Burst Lenth=4 tRC ≥ tRC(min) IoL=0mA, tCC= tCC(min)                                                        | 1400 | 1300    | 1180 | mA   |      |

Note: 1. Measured with outputs open & On-Die termination off.

2. Refresh period is 16ms.

#### **AC INPUT OPERATING CONDITIONS**

Recommended operating conditions (Voltage referenced to Vss=0V, VpD=2.5V  $\pm$  0.1V, VpDq=1.8V  $\pm$  0.1V, Tj=0 to 100 °C)

| Parameter                                                          | Symbol | Min          | Тур | Max          | Unit | Note |

|--------------------------------------------------------------------|--------|--------------|-----|--------------|------|------|

| Input High (Logic 1) Voltage; DQ                                   | VIH    | VREF+0.25    | -   | -            | V    | 1    |

| Input Low (Logic 0) Voltage; DQ                                    | VIL    | -            | -   | VREF-0.25    | V    | 2    |

| Clock Input Differential Voltage ; CK and CK                       | VID    | 0.5          | -   | VDDQ+0.6     | V    | 3    |

| Clock Input Crossing Point Voltage ; CK and $\overline{\text{CK}}$ | Vıx    | 0.5*VDDQ-0.2 | -   | 0.5*VDDQ+0.2 | V    | 4    |

**Note :** 1. VIH(Max) = 4.2V. The overshoot voltage duration is < 3ns at VDD. VIH level should be met at the pin of DRAM when ODT=ON.

- 2. VIL(Min) = -1.5V. The undershoot voltage duration is < 3ns at VSS. VIL level should be met at the pin of DRAM when ODT=ON.

- 3. VID is the magnitude of the difference between the input level on CK and the input level on CK

- 4. The value of Vix is expected to equal 0.5\*VDDQ of the transmitting device and must track variations in the DC level of the same

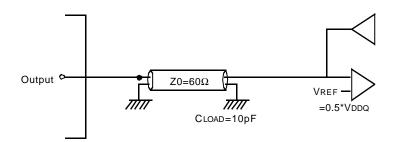

# AC OPERATING TEST CONDITIONS (VDD=2.5V±0.1V, Tj= 0 to 100 °C)

| Parameter                                  | Value               | Unit | Note |

|--------------------------------------------|---------------------|------|------|

| Input reference voltage for CK(for single) | 0.50*VDDQ           | V    |      |

| CK and CK signal maximum peak swing        | 1.5                 | V    |      |

| CK signal minimum slew rate                | 1.0                 | V/ns |      |

| Input Levels(VIH/VIL)                      | VREF+0.25/VREF-0.25 | V    |      |

| Input timing measurement reference level   | VREF                | V    |      |

| Output timing measurement reference level  | 1/2 VDDQ            | V    |      |

| Output load condition                      | See Fig.1           |      |      |

(Fig. 1) Output Load Circuit

# **CAPACITANCE** (VDD=2.5V, TA= 25°C, f=1MHz)

| Parameter                                      | Symbol | Min | Max | Unit |

|------------------------------------------------|--------|-----|-----|------|

| Input capacitance ( CK, CK )                   | CIN1   | 3.0 | 5   | pF   |

| Input capacitance (A0~A10, BA0~BA1)            | CIN2   | 3.0 | 5   | pF   |

| Input capacitance ( CKE, CS, RAS, CAS, WE )    | CIN3   | 3.0 | 5   | pF   |

| Data & DQS input/output capacitance(DQ 0~DQ31) | Соит   | 3.0 | 5   | pF   |

| Input capacitance(DM0 ~ DM3)                   | CIN4   | 3.0 | 5   | pF   |

## **AC CHARACTERISTICS**

| D                                          |           | Sumb al | -20 (G    | F1000)    | -22 (G    | F900)     | -25 (G    | F800)     | Unit |

|--------------------------------------------|-----------|---------|-----------|-----------|-----------|-----------|-----------|-----------|------|

| Paramet                                    | er        | Symbol  | Min       | Max       | Min       | Max       | Min       | Max       | Unit |

|                                            | CL=7      |         | 2.0       | 4.0       | -         | -         | -         | -         | ns   |

| CK cycle time                              | CL=6      | tCK     | -         | -         | 2.22      | 4.0       | -         | -         | ns   |

|                                            | CL=5      |         | -         | -         | -         | -         | 2.5       | 4.0       | ns   |

| CK high width                              | •         | tCH     | 0.45      | 0.55      | 0.45      | 0.55      | 0.45      | 0.55      | tCK  |

| CK low width                               |           | tCL     | 0.45      | 0.55      | 0.45      | 0.55      | 0.45      | 0.55      | tCK  |

| DQS out access time from                   | om CK     | tDQSCK  | -0.35     | 0.35      | -0.45     | 0.45      | -0.45     | 0.45      | ns   |

| Data strobe edge to Do                     | ut edge   | tDQSQ   | -0.225    | 0.225     | -0.25     | 0.25      | -0.28     | 0.28      | ns   |

| Read preamble                              |           | tRPRE   | 0.85      | 1.15      | 0.88      | 1.12      | 0.9       | 1.1       | tCK  |

| Read postamble                             |           | tRPST   | 0.35      | 0.65      | 0.38      | 0.62      | 0.4       | 0.6       | tCK  |

| DQS in/out high level                      |           | tDQSH   | 0.45      | 0.55      | 0.45      | 0.55      | 0.45      | 0.55      | tCK  |

| DQS in/out low level                       |           | tDQSL   | 0.45      | 0.55      | 0.45      | 0.55      | 0.45      | 0.55      | tCK  |

| Address and Control inp                    | out setup | tIS     | 0.5       | -         | 0.55      | -         | 0.6       | -         | ns   |

| Address and Control inp                    | out hold  | tIH     | 0.5       | -         | 0.55      | -         | 0.6       | -         | ns   |

| Write command to first latching transition | DQS       | tDQSS   | WL - 0.15 | WL + 0.15 | WL - 0.15 | WL + 0.15 | WL - 0.15 | WL + 0.15 | tCK  |

| Write preamble setup ti                    | me        | tWPRES  | 0         | -         | 0         | -         | 0         | -         | ps   |

| Write postamble                            |           | tWPST   | 0.4       | 0.6       | 0.4       | 0.6       | 0.4       | 0.6       | tCK  |

| Write preamble                             |           | tWPRE   | 0.35      | -         | 0.35      | -         | 0.35      | -         | tCK  |

| DQ_in and DM setup tir                     | ne to DQS | tDS     | 0.25      | -         | 0.27      | -         | 0.3       | -         | ns   |

| DQ_in and DM hold tim                      | e to DQS  | tDH     | 0.25      | -         | 0.27      | -         | 0.3       | -         | ns   |

| Clock half period                          |           | tHP     | tCL/H min | -         | tCL/H min | -         | tCL/H min | -         | ns   |

| Data output hold time fr                   | om DQS    | tQH     | tHP-0.225 | -         | tHP-0.25  | -         | tHP-0.28  | -         | ns   |

| Jitter over 1-6 clock cyc                  | les of CK | tJ *1   | -         | 50        | -         | 55        | -         | 65        | ps   |

| Cycle to Cycle duty cyc                    | le error  | tDC,ERR | -         | 50        | -         | 55        | -         | 65        | ps   |

| Rise and fall times of C                   | K         | tR, tF  | -         | 400       | -         | 450       | -         | 500       | ps   |

<sup>1.</sup> The cycle to cycle jitter and 2~6 cycle short term jitter.

# Simplified Timing @ BL=4, CL=7, AL=0

# **K4N26323AE-GC**

#### Note 1:

- The JEDEC DDR-II specification currently defines the output data valid window(tDV) as the time period when the data strobe and all data associated with that data strobe are coincidentally valid.

- The previously used definition of tDV(=0.35tCK) artificially penalizes system timing budgets by assuming the worst case output valid window even then the clock duty cycle applied to the device is better than 45/55%

- A new AC timing term, tQH which stands for data output hold time from DQS is defined to account for clock duty cycle variation and replaces tDV

- tQHmin = tHP-X where

- . tHP=Minimum half clock period for any given cycle and is defined by clock high or clock low time(tCH,tCL)

- . X=A frequency dependent timing allowance account for tDQSQmax

## tQH Timing (CL7, BL4)

# K4N26323AE-GC

# **AC CHARACTERISTICS (I)**

| Parameter                                    | Symbol | -20 (GI   | F1000) | -22 (G   | F900) | -25 (G   | Unit |          |

|----------------------------------------------|--------|-----------|--------|----------|-------|----------|------|----------|

| Parameter                                    | Symbol | Min       | Max    | Min      | Max   | Min      | Max  | Unit     |

| Row cycle time                               | tRC    | 27 (54.0) | -      | 26       | -     | 24       | -    | tCK (ns) |

| Refresh row cycle time                       | tRFC   | 33 (66.0) | -      | 30       | -     | 27       | -    | tCK (ns) |

| Row active time                              | tRAS   | 19 (38.0) | 100K   | 18       | 100K  | 17       | 100K | tCK (ns) |

| RAS to CAS delay for Read                    | tRCDR  | 9 (18.0)  | -      | 9        | -     | 8        | -    | tCK (ns) |

| RAS to CAS delay for Write                   | tRCDW  | 6 (12.0)  | -      | 6        | -     | 5        | -    | tCK (ns) |

| Row precharge time                           | tRP    | 8 (16.0)  | -      | 8        | -     | 7        | -    | tCK (ns) |

| Row active to Row active                     | tRRD   | 5         | -      | 5        | -     | 4        | -    | tCK      |

| Last data in to Row precharge                | tWR    | 5 (10.0)  | -      | 5        | -     | 4        | -    | tCK (ns) |

| Last data in to Read command                 | tCDLR  | 4         | -      | 4        | -     | 4        | -    | tCK      |

| Col. address to Col. address                 | tCCD   | 2         | -      | 2        | -     | 2        | -    | tCK      |