# **User's Manual**

# **V850E/PH2**<sup>TM</sup>

32-Bit Single-Chip Microcontroller

**Hardware**

μPD70F3187

#### NOTES FOR CMOS DEVICES —

# 1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③ PRECAUTION AGAINST ESD**

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

# **4** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

# (5) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

All (other) product, brand, or trade names used in this pamphlet are the trademarks or registered trademarks of their respective owners.

Product specifications are subject to change without notice. To ensure that you have the latest product data, please contact your local NEC Electronics sales office.

- The information in this document is current as of June, 2006. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all

products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

For further information, please contact:

#### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan

Tel: 044-435-5111 http://www.necel.com/

#### [America]

#### **NEC Electronics America, Inc.**

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 http://www.am.necel.com/

#### [Europe]

#### **NEC Electronics (Europe) GmbH**

Arcadiastrasse 10 40472 Düsseldorf, Germany Tel: 0211-65030 http://www.eu.necel.com/

#### **Hanover Office**

Podbielski Strasse 166 B 30177 Hanover Tel: 0 511 33 40 2-0

#### **Munich Office**

Werner-Eckert-Strasse 9 81829 München Tel: 0 89 92 10 03-0

#### Stuttgart Office

Industriestrasse 3 70565 Stuttgart Tel: 0 711 99 01 0-0

#### **United Kingdom Branch**

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908-691-133

#### Succursale Française

9, rue Paul Dautier, B.P. 52180 78142 Velizy-Villacoublay Cédex France

Tel: 01-3067-5800

# Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

# Tyskland Filial

Täby Centrum Entrance S (7th floor) 18322 Täby, Sweden Tel: 08 638 72 00

# Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02-667541

#### **Branch The Netherlands**

Steijgerweg 6 5616 HS Eindhoven The Netherlands Tel: 040 265 40 10

#### [Asia & Oceania]

#### NEC Electronics (China) Co., Ltd

7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China TEL: 010-8235-1155 http://www.cn.necel.com/

#### NEC Electronics Shanghai Ltd.

Room 2509-2510, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai P.R. China P.C:200120 Tel: 021-5888-5400 http://www.cn.necel.com/

#### **NEC Electronics Hong Kong Ltd.**

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318 http://www.hk.necel.com/

#### Seoul Branch

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737

#### **NEC Electronics Taiwan Ltd.**

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-8175-9600

# NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311 http://www.sg.necel.com/

G06.6-1A

# **Preface**

Readers This manual is intended for users who want to understand the functions of the

V850E/PH2 (PHOENIX-F).

**Purpose** This manual presents the hardware manual of V850E/PH2.

**Organization** This system specification describes the following sections:

• Pin function

CPU function

• Internal peripheral function

Flash memory

**Legend** Symbols and notation are used as follows:

Weight in data notation: Left is high-order column, right is low order column

Active low notation :  $\overline{xxx}$  (pin or signal name is over-scored) or

/xxx (slash before signal name)

Memory map address: : High order at high stage and low order at low stage

Note : Explanation of (Note) in the text

Caution : Item deserving extra attention

**Remark** : Supplementary explanation to the text

Numeric notation : Binary... xxxx or xxxB

Decimal... xxxx

Hexadecimal... xxxxH or 0x xxxx

Prefixes representing powers of 2 (address space, memory capacity)

K (kilo):  $2^{10} = 1024$

M (mega):  $2^{20} = 1024^2 = 1,048,576$ G (giga):  $2^{30} = 1024^3 = 1,073,741,824$

# **Table of Contents**

|            |     | Prefac   | ce                                                 | 5   |

|------------|-----|----------|----------------------------------------------------|-----|

| Chapte     | r 1 | Introd   | luction                                            | 33  |

| 1.1        |     | Outline  |                                                    | 33  |

| 1.2        |     |          | Features                                           |     |

| 1.3        |     |          | tions                                              |     |

| 1.4        | -   |          | g Information                                      |     |

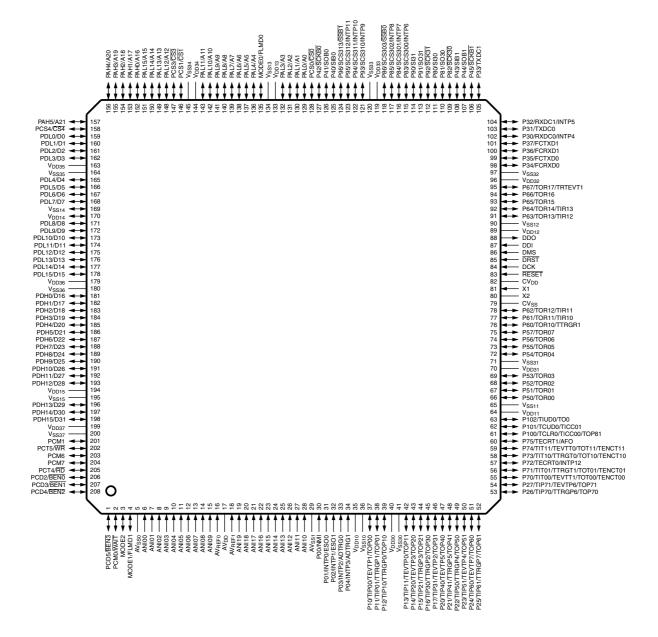

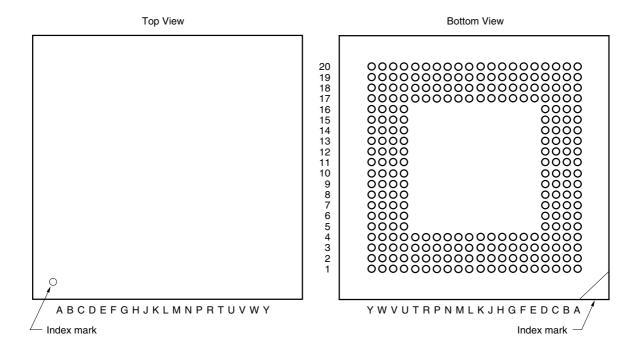

| 1.9        |     |          | ofiguration (Top View)                             |     |

| 1.0        | -   |          | n Blocks                                           |     |

|            | -   | 6.1      | Internal block diagram                             |     |

|            |     |          | On-chip units.                                     |     |

|            | •   | 0.2      |                                                    |     |

| Chapte     | r 2 | Pin Fı   | unctions                                           | 45  |

| 2          |     |          | Pin Functions                                      |     |

| 2.2        |     | Pin Stat |                                                    |     |

| 2.3        |     |          | tion of Pin Functions                              |     |

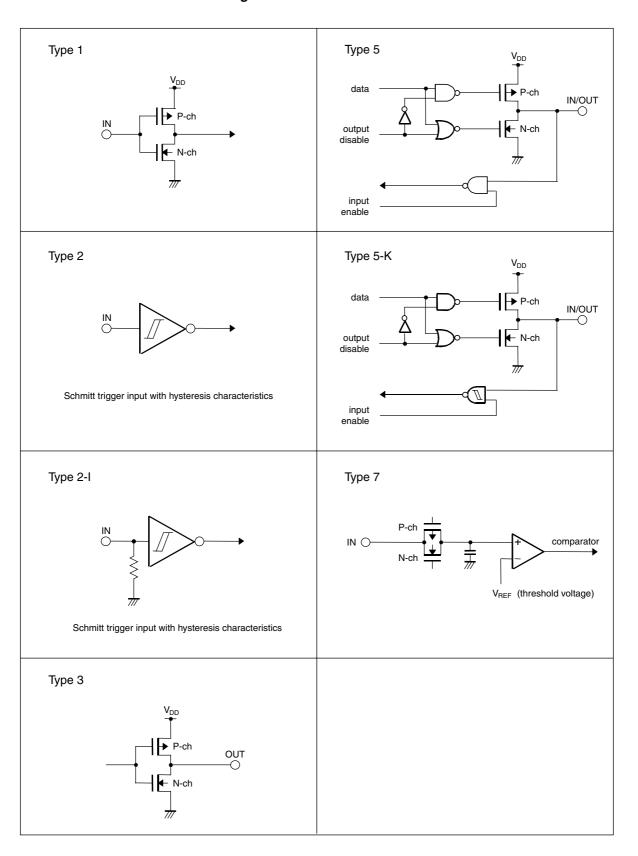

| 2.4        |     |          | Circuits and Recommended Connection of Unused Pins |     |

| 2.         |     |          | Suppression                                        |     |

| ۷.,        | ,   | 140136 3 | uppression                                         | / ¬ |

| Chapte     | r 3 | CDITE    | -<br>-unctions                                     | 77  |

| 3.         |     |          | S                                                  |     |

| 3.2<br>3.2 |     |          | egister Set                                        |     |

| J.2        |     | 2.1      | Program register set                               |     |

|            |     |          | System register set                                |     |

|            | _   |          | Floating point arithmetic unit register set        |     |

| 3.3        | _   |          | ng Modes                                           |     |

| 3.         |     | •        |                                                    |     |

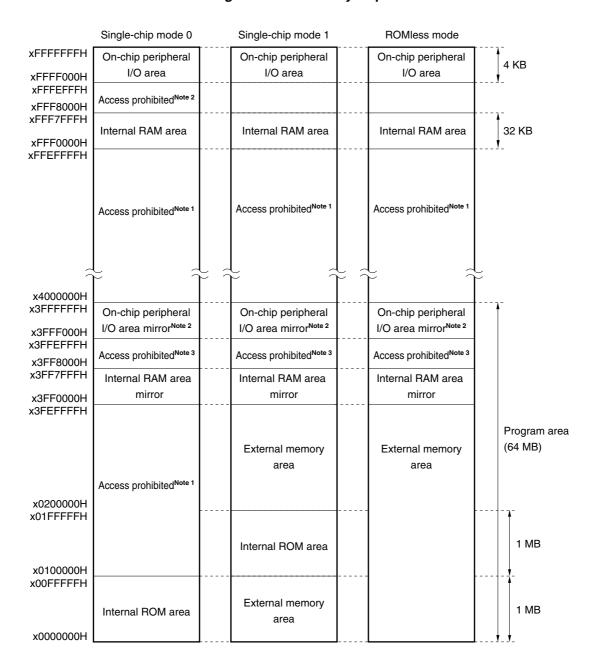

|            | _   |          | Operating modes outline                            |     |

| 2          | _   |          | Operation mode specification                       |     |

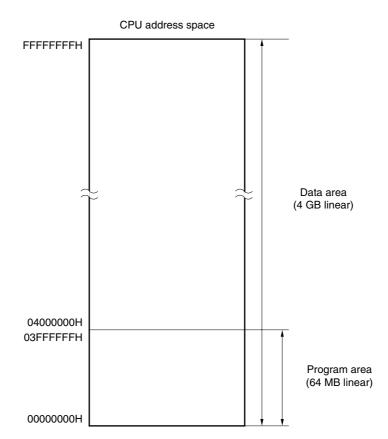

| 3.4        |     |          | s Space                                            |     |

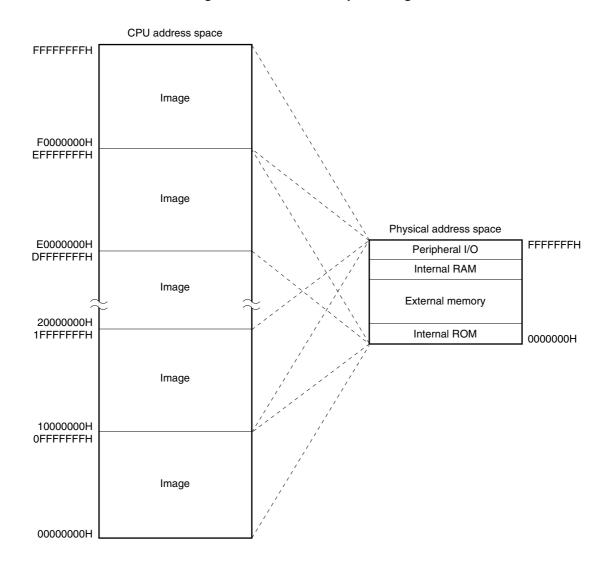

|            | _   |          | CPU address space                                  |     |

|            | _   |          | Images                                             |     |

|            |     |          | Wrap-around of CPU address space                   |     |

|            | _   |          | Memory map                                         |     |

|            | _   |          | Areas                                              |     |

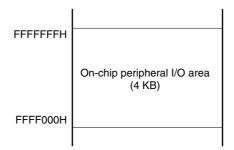

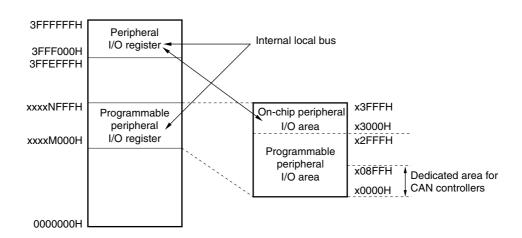

|            |     |          | Peripheral I/O registers list                      |     |

|            | _   |          | Programmable peripheral I/O area                   |     |

|            |     | 4.8      | Specific registers                                 |     |

|            |     |          | System wait control register (VSWC)                |     |

|            |     |          | Cautions                                           |     |

|            | 3.  | 4.11     | Cautions                                           | 131 |

| Observator | 4   | D 0      | Nametral Franctica                                 | 400 |

| Chapte     |     |          | Control Function                                   |     |

| 4.         |     |          | S                                                  |     |

| 4.2        |     |          | ntrol Pins                                         |     |

| 4.3        |     |          | / Block Function                                   |     |

| _          |     |          | Chip select control function.                      |     |

| 4.4        |     | •        | cle Type Control Function                          |     |

|            |     |          | Bus cycle type configuration                       |     |

| 4.         |     |          | cess                                               |     |

|            |     |          | Number of access clocks                            |     |

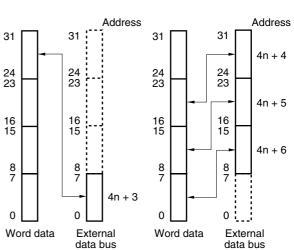

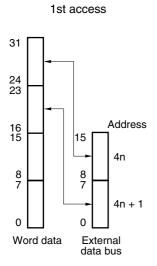

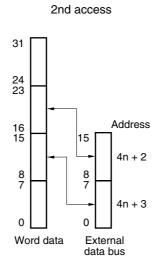

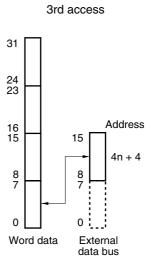

|            |     |          | Bus sizing function                                |     |

|            |     | 5.3      | Endian control function                            |     |

|            |     | 5.4      | Bus width                                          |     |

| 4.0        |     |          | nction                                             |     |

|            | 4.  | 6.1      | Programmable wait function                         | 162 |

| 4.9 Boundary Operation Conditions. 4.9.1 Program space 4.9.2 Data space  Chapter 5 Memory Access Control Function 5.1 SRAM, External ROM, External I/O Interface. 5.1.1 Features 5.1.2 SRAM connection. 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller). 6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADCO, ADC1) 6.4.2 DMA transfer of Serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable Interrupt status flag (ID) 7.3.8 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.1 Non-maskable interrupt status flag (ID) 7.3.2 Restore 7.3.3 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.9 Respondent of the service of t |      | 4.7<br>4.8 | Bus P  | rate Insertion Functionriority Order            | 167 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|--------|-------------------------------------------------|-----|

| Chapter 5 Memory Access Control Function 5.1 SRAM, External ROM, External I/O Interface. 5.1.1 Features 5.1.2 SRAM connection 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller). 6.1 Features 6.2 Control Registers. 6.3 DMA Channel Priorities. 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADCO, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts. 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 4.9        | Bound  |                                                 |     |

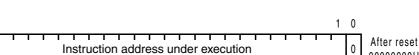

| Chapter 5 Memory Access Control Function 5.1 SRAM, External ROM, External I/O Interface 5.1.1 Features 5.1.2 SRAM connection 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller). 6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation 6.4.1 DMA transfer of A/D converter result registers (ADCO, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt transfer of maskable interrupts 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts. 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |            | 4.9.1  | Program space                                   | 168 |

| 5.1 SRAM, External ROM, External I/O Interface. 5.1.1 Features 5.1.2 SRAM connection 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller). 6.1 Features 6.2 Control Registers. 6.3 DMA Channel Priorities. 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADCO, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Deperation 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |            | 4.9.2  | Data space                                      | 168 |

| 5.1 SRAM, External ROM, External I/O Interface. 5.1.1 Features 5.1.2 SRAM connection 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller). 6.1 Features 6.2 Control Registers. 6.3 DMA Channel Priorities. 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADCO, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Deperation 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |            |        |                                                 |     |

| 5.1.1 Features 5.1.2 SRAM connection 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller). 6.1 Features 6.2 Control Registers. 6.3 DMA Channel Priorities. DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts. 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator 8.1 Features 8.1 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Chap | ter        |        |                                                 |     |

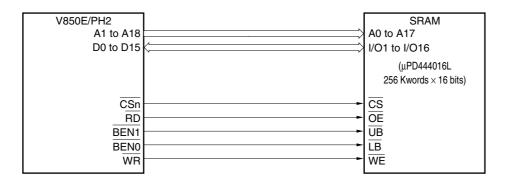

| 5.1.2 SRAM connection 5.1.3 SRAM, external ROM, external I/O access  Chapter 6 DMA Functions (DMA Controller) 6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of Serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt ringer mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 5.1        | SRAM   |                                                 |     |

| Chapter 6 DMA Functions (DMA Controller) 6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function  7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts. Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |            | 5.1.1  |                                                 |     |

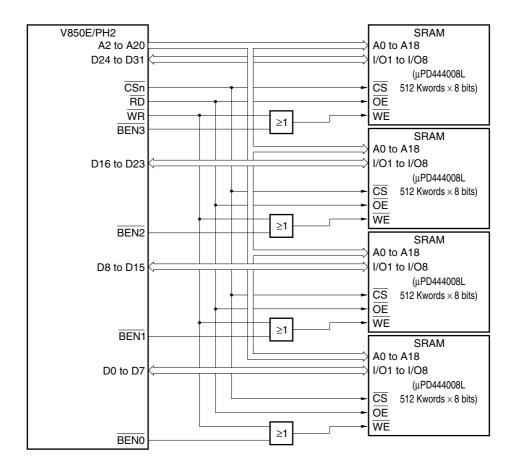

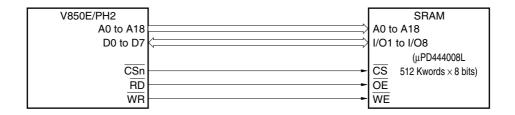

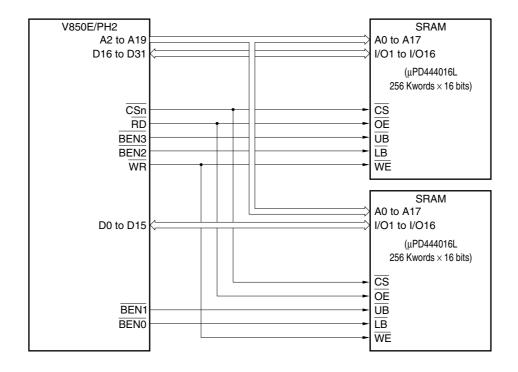

| Chapter 6 DMA Functions (DMA Controller)  6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function  7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Operation 7.4.1 Operation 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |            | 5.1.2  |                                                 |     |

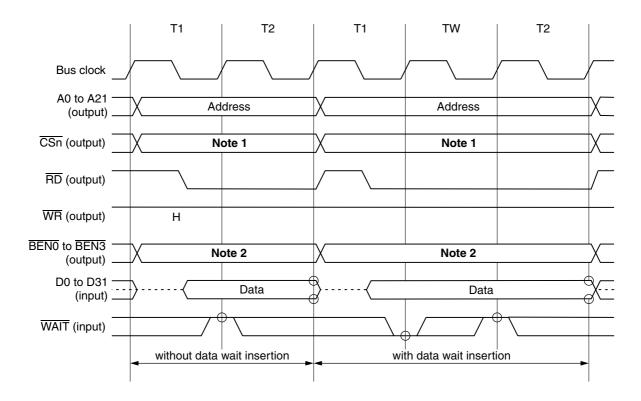

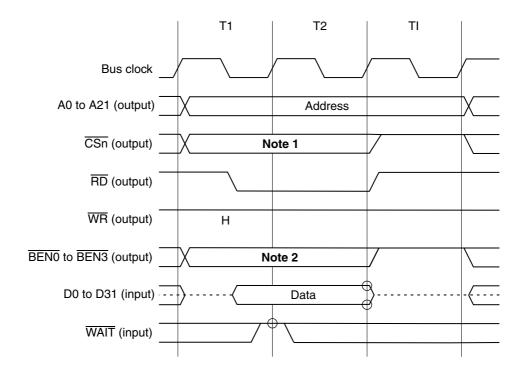

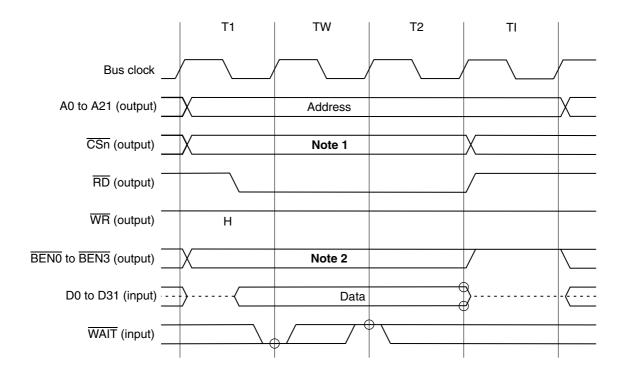

| 6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |            | 5.1.3  | SRAM, external ROM, external I/O access         | 172 |

| 6.1 Features 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chan | tor (      | е рму  | Functions (DMA Controller)                      | 101 |

| 6.2 Control Registers 6.3 DMA Channel Priorities 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of Serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts. 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -    |            |        |                                                 |     |

| 6.3 DMA Channel Priorities 6.4 DMA Operation 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.1 Operation 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |            |        |                                                 |     |

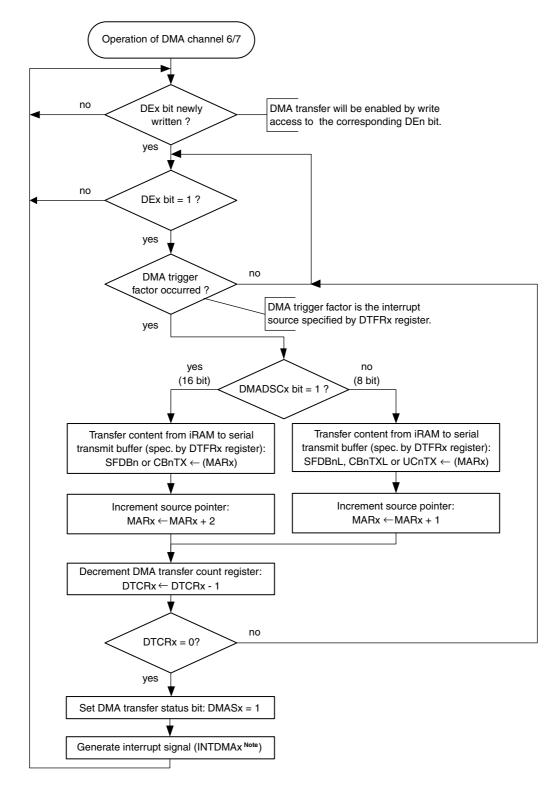

| 6.4 DMA Operation. 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function  7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection  7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition  7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | -          |        |                                                 |     |

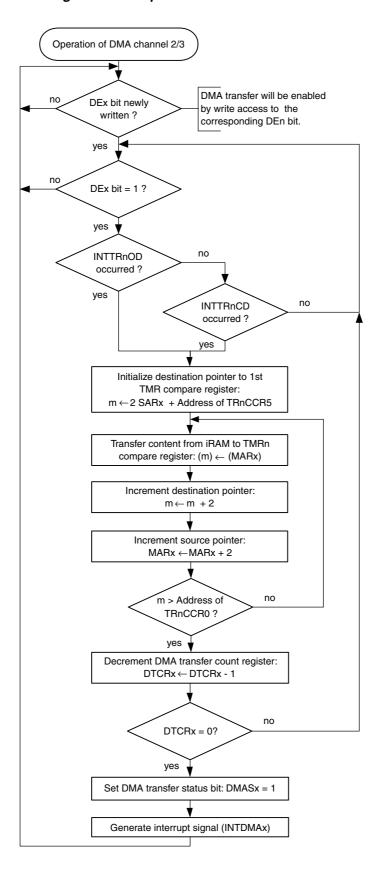

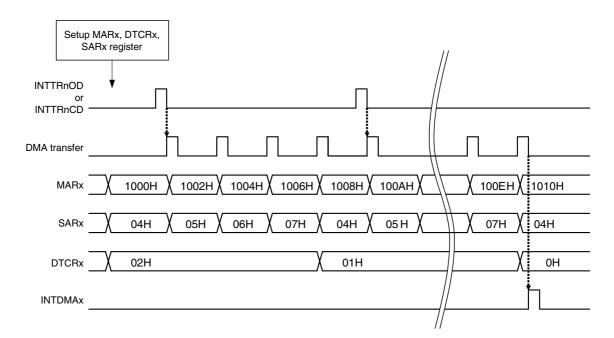

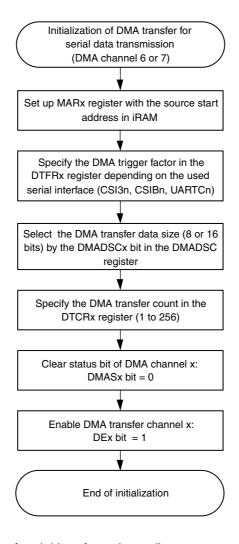

| 6.4.1 DMA transfer of A/D converter result registers (ADC0, ADC1) 6.4.2 DMA transfer of PWM timer reload (TMR0, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function  7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |            |        |                                                 |     |

| 6.4.2 DMA transfer of PWM timer reload (TMRO, TMR1) 6.4.3 DMA transfer of serial interfaces 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 0.4        |        |                                                 |     |

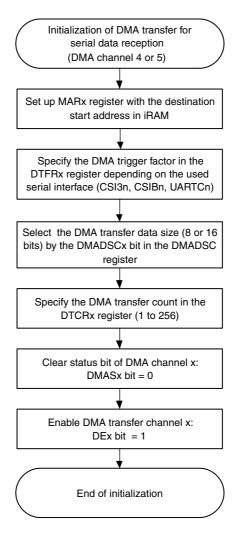

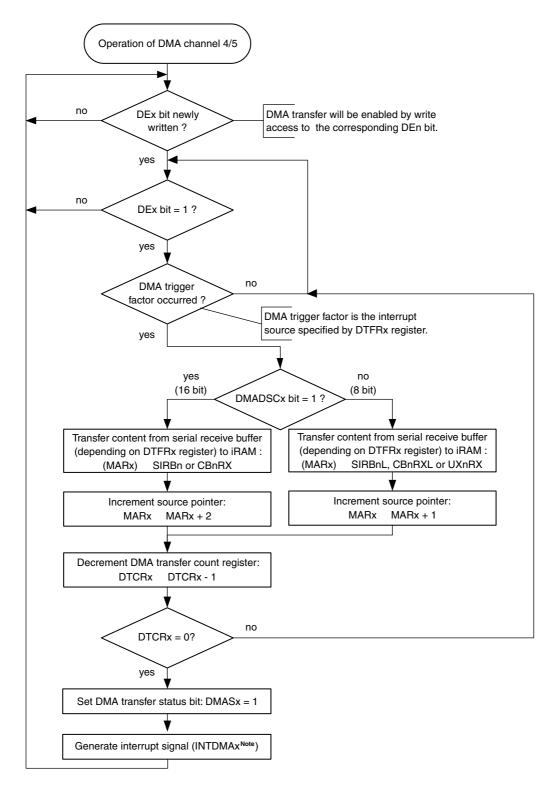

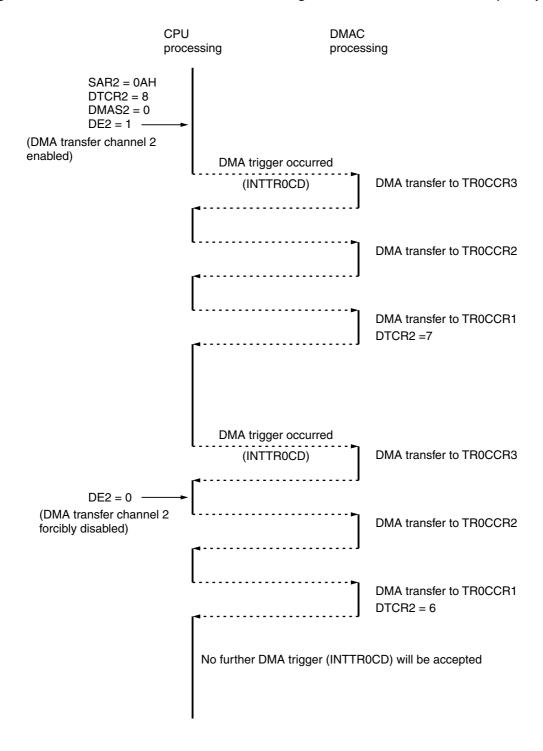

| 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts. 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |            |        |                                                 |     |

| 6.4.4 Forcible termination of DMA transfer 6.5 DMA Interrupt Function.  Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |            |        |                                                 |     |

| Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |            |        |                                                 |     |

| Chapter 7 Interrupt/Exception Processing Function 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore. 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts. 7.3.1 Operation 7.3.2 Restore. 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception 7.4.2 Restore 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 65         | -      |                                                 |     |

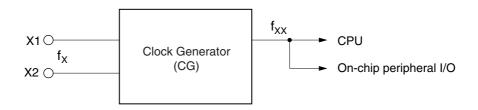

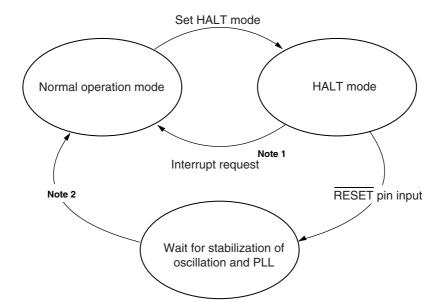

| 7.1 Features 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 0.5        | DIVIA  | menupt i unedon                                 | 200 |

| 7.2 Non-maskable Interrupt. 7.2.1 Operation 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Chap | ter        |        |                                                 |     |

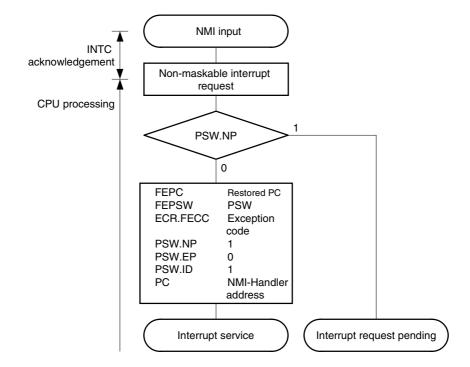

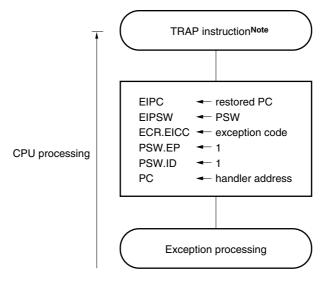

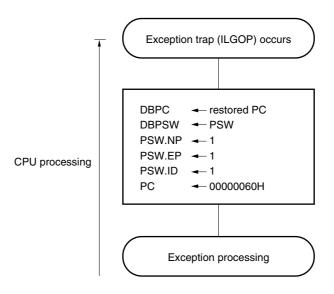

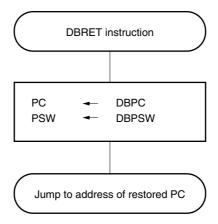

| 7.2.1 Operation 7.2.2 Restore. 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function  7.3 Maskable Interrupts. 7.3.1 Operation 7.3.2 Restore. 7.3.3 Priorities of maskable interrupts. 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection  7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP)  7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |            |        |                                                 |     |

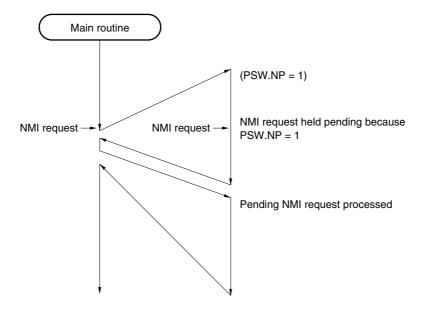

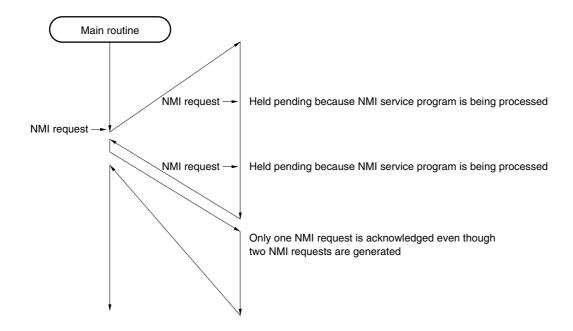

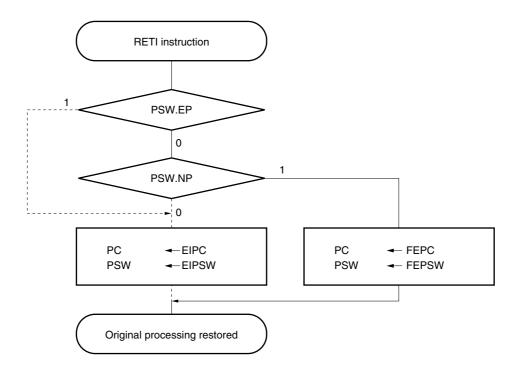

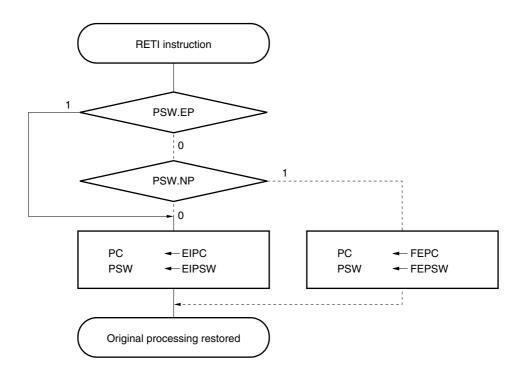

| 7.2.2 Restore 7.2.3 Non-maskable interrupt status flag (NP). 7.2.4 Edge Detection Function  7.3 Maskable Interrupts. 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection  7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP)  7.5 Exception Trap 7.5.1 Illegal opcode definition  7.6 Periods in Which CPU Does Not Acknowledge Interrupts  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 7.2        | Non-m  |                                                 |     |

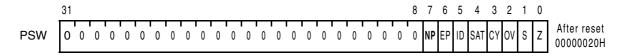

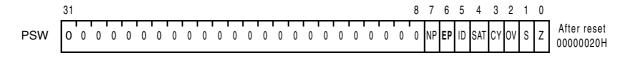

| 7.2.3 Non-maskable interrupt status flag (NP) 7.2.4 Edge Detection Function  7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection  7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP)  7.5 Exception Trap 7.5.1 Illegal opcode definition  7.6 Periods in Which CPU Does Not Acknowledge Interrupts  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |            |        |                                                 |     |

| 7.2.4 Edge Detection Function  7.3 Maskable Interrupts.  7.3.1 Operation  7.3.2 Restore.  7.3.3 Priorities of maskable interrupts  7.3.4 Interrupt control register (PICn)  7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6)  7.3.6 In-service priority register (ISPR)  7.3.7 Maskable interrupt status flag (ID)  7.3.8 Interrupt trigger mode selection  7.4 Software Exception  7.4.1 Operation  7.4.2 Restore  7.4.3 Exception status flag (EP)  7.5 Exception Trap  7.5.1 Illegal opcode definition  7.6 Periods in Which CPU Does Not Acknowledge Interrupts.  Chapter 8 Clock Generator  8.1 Features  8.2 Configuration  8.3 Power Save Control  8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |            | 7.2.2  |                                                 |     |

| 7.3 Maskable Interrupts 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |            | _      |                                                 |     |

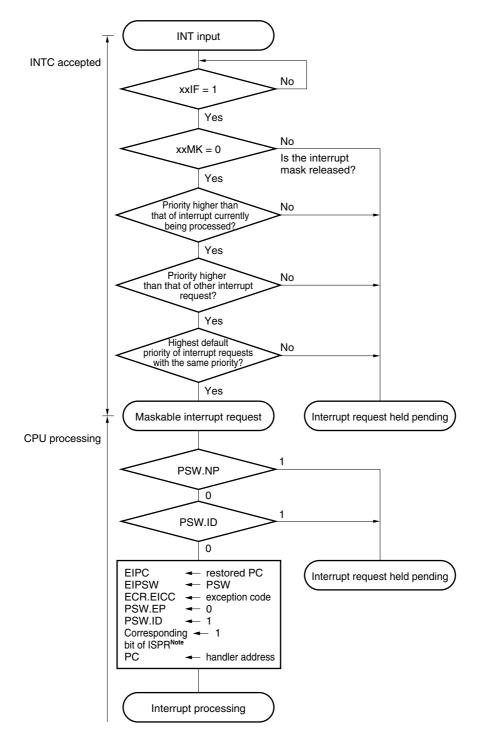

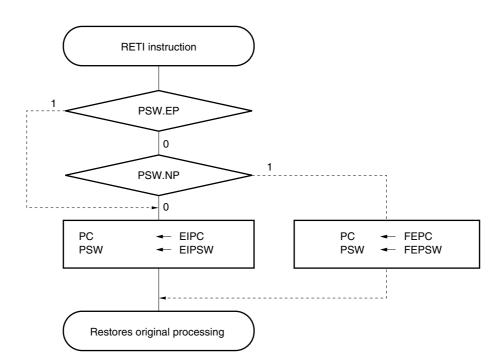

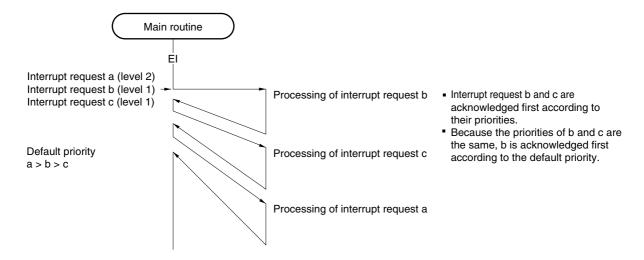

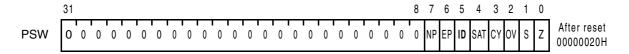

| 7.3.1 Operation 7.3.2 Restore 7.3.3 Priorities of maskable interrupts 7.3.4 Interrupt control register (PICn) 7.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6) 7.3.6 In-service priority register (ISPR) 7.3.7 Maskable interrupt status flag (ID) 7.3.8 Interrupt trigger mode selection 7.4 Software Exception 7.4.1 Operation 7.4.2 Restore 7.4.3 Exception status flag (EP) 7.5 Exception Trap 7.5.1 Illegal opcode definition 7.6 Periods in Which CPU Does Not Acknowledge Interrupts  Chapter 8 Clock Generator 8.1 Features 8.2 Configuration 8.3 Power Save Control 8.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |            |        |                                                 |     |