### **Philips Components-Signetics**

| Document No.                 | 853-0095              |  |  |  |  |  |

|------------------------------|-----------------------|--|--|--|--|--|

| ECN No.                      | 85292                 |  |  |  |  |  |

| Date of Issue                | August 26, 1986       |  |  |  |  |  |

| Status                       | Product Specification |  |  |  |  |  |

| Application Specific Product |                       |  |  |  |  |  |

#### DESCRIPTION

The SCN8049 Series Microcontrollers are self-contained, 8-bit processors which contain the system timing, control logic, RAM data memory, ROM program memory (8048/49/50 only), and I/O lines necessary to implement dedicated control functions. All SCN8049 Series devices are pin and program compatible, differing only in the size of the on-board program ROM and data RAM, as follows:

| TYPE    | RAM SIZE | ROM SIZE |

|---------|----------|----------|

| SCN8049 | 128 x 8  | 2k x 8   |

| SCN8050 | 256 x 8  | 4kx8     |

| SCN8039 | 128 x 8  | ] - ]    |

| SCN8040 | 256 x 8  |          |

Program memory can be expanded externally up to a maximum total of 4k bytes without paging. Data memory can also be expanded externally. I/O capabilities can be expanded using standard devices or the 8243 I/O expander.

The SCN8049 Series processors are designed to be efficient control processors as well as arithmetic processors. They provide an instruction set which allows the user to directly set and reset individual lines within its I/O ports as well as test individual bits within the accumulator. A large variety of branch and table look-up instructions make these processors very efficient in implementing standard logic functions. Also, special attention has been given to code efficiency. Over 70% of the instructions are a single byte long and all others are only 2 bytes long.

An on-chip 8-bit counter is provided which can count, under program control, either internal clock pulses (with a divide

# SCN8049 Series SCN8049, SCN8050, SCN8039, SCN8040 single-chip 8-bit microcontroller

by 32 prescaler) or external events. The counter can be programmed to cause an interrupt on terminal count.

#### **FEATURES**

- 8-bit CPU, ROM, RAM, I/O in a 40-pin package

- 24 quasi-bidirectional I/O lines

- Two test inputs

- Internal counter/timer

- Single-level vectored interrupts: external, counter/timer

- Over 90 instructions, 70% single byte

- 1.36μs or 2.5μs instruction cycle, all instructions one or two cycles

- Expandable memory and I/O

- Low voltage standby

- TTL compatible inputs and outputs

- Single +5V power supply

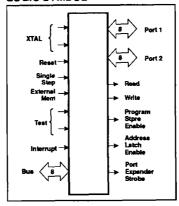

### LOGIC SYMBOL

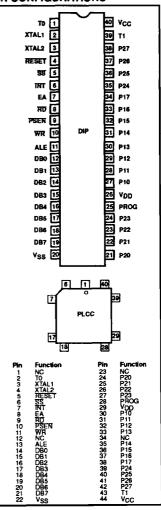

### **PIN CONFIGURATIONS**

### **SCN8049 Series**

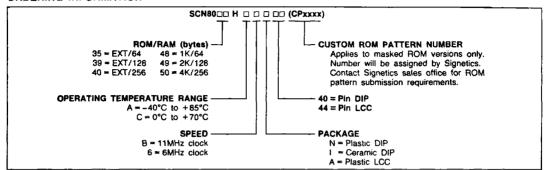

### **ORDERING INFORMATION**

### PIN DESCRIPTION

|                 | PIN     | NO.                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|---------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        | DIP     | PLCC                | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub> | 20      | 22                  |      | Circuit ground potential.                                                                                                                                                                                                                                                                                                                                                                                                      |

| $v_{DD}$        | 26      | 29                  |      | Low power standby.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Vcc             | 40      | 44                  |      | Main Power Supply: +5V during operation.                                                                                                                                                                                                                                                                                                                                                                                       |

| PROG            | 25      | 28                  | 0    | Output strobe for 8243 I/O expander.                                                                                                                                                                                                                                                                                                                                                                                           |

| P10 - P17       | 27 – 34 | 30 - 33,<br>35 - 38 | 1/0  | Port 1: 8-bit quasi-bidirectional port.                                                                                                                                                                                                                                                                                                                                                                                        |

| P20 - P27       |         | 24 – 27,<br>39 – 42 | 1/0  | Port 2: 8-bit quasi-bidirectional port. P20-23 contain the four high-order program counter bits during an external program memory fetch and serve as a 4-bit I/O expander bus for 8243.                                                                                                                                                                                                                                        |

| D80 - D87       | 12 – 19 | 14-21               | 1/0  | Data Bus: True bidirectional port which can be written or read synchronously using the RD, WR strobes. The port can also be statically latched. Contains the eight low-order program counter bits during an external program memory fetch and receives the addressed instruction under the control of PSEN. Also contains the address and data during an external RAM data store instruction, under control of ALE, RD and WR. |

| TO              | 1       | 2                   | 1    | Input pin testable using the conditional transfer instructions JT0 and JNT0. T0 and be designated as a clock output using the ENT0 CLK instruction.                                                                                                                                                                                                                                                                            |

| T1              | 39      | 43                  | ľ    | Input pin testable using the JT1 and JNT1 instructions. Can be designated the timer/counter input using the STRT CNT instruction.                                                                                                                                                                                                                                                                                              |

| XTAL1           | 2       | 3                   | ı    | Crystal 1: One side of the crystal input for internal oscillator. Also input for external source (non-TTL $V_{IH}$ ).                                                                                                                                                                                                                                                                                                          |

| XTAL2           | 3       | 4                   |      | Crystal 2: Other side of crystal input.                                                                                                                                                                                                                                                                                                                                                                                        |

| INT             | 6       | 7                   | ı    | Interrupt: Initiates an interrupt if interrupt is enabled. Interrupt is disabled after a reset. Also testable with conditional jump instruction. Interrupt must remain low for at least three machine cycles for proper operation.                                                                                                                                                                                             |

| RESET           | 4       | 5                   | '    | Reset: Used to initialize the microcomputer. Active low. Internal pullup ~75ΚΩ. During program verification the address is latched by a "0" to "1" transition on RESET and the data at the addressed location is output on BUS.                                                                                                                                                                                                |

| RD              | 8       | 8                   | 0    | Read: Output strobe activated during a bus read. Can be used to enable data onto the bus from an external device. Used as a read strobe to external data memory.                                                                                                                                                                                                                                                               |

| WR              | 10      | 11                  | 0    | Write: Output strobe during a bus write. Used as write strobe to external data memory.                                                                                                                                                                                                                                                                                                                                         |

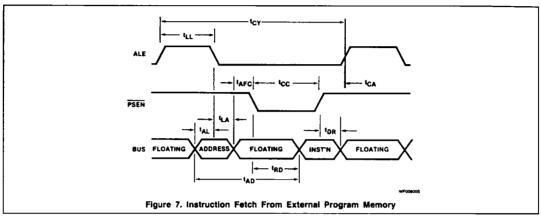

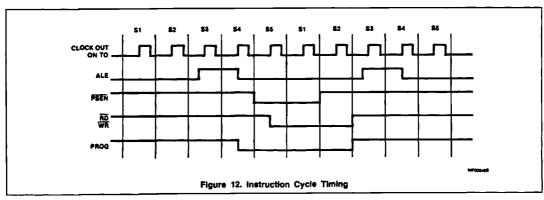

| ALE             | 11      | 13                  | 0    | Address Latch Enable: Occurs once during each cycle and is useful as a clock output. The negative edge of ALE strobes address into external data and program memory.                                                                                                                                                                                                                                                           |

| PSEN            | 9       | 10                  | 0    | Program Store Enable: Output occurs only during a fetch to external program memory.                                                                                                                                                                                                                                                                                                                                            |

| SS              | 5       | 6                   | ı    | Single Step: Can be used in conjunction with ALE to "single step" the processor through each instruction.                                                                                                                                                                                                                                                                                                                      |

| EA              | 7       | 8                   | ı    | External Access: Forces all program memory fetches to reference external memory. Useful for emulation and debug, and essential for testing and program verification.                                                                                                                                                                                                                                                           |

#### NOTE:

Each pin on these ports can be assigned, under program control, to be an input or an output. A pin is designated as an input by writing a logic "1" to the pin. RESET sets all pins to the input mode. Each pin has an internal pullup of approximately 50kΩ.

### SCN8049 Series

### **FUNCTIONAL DESCRIPTION**

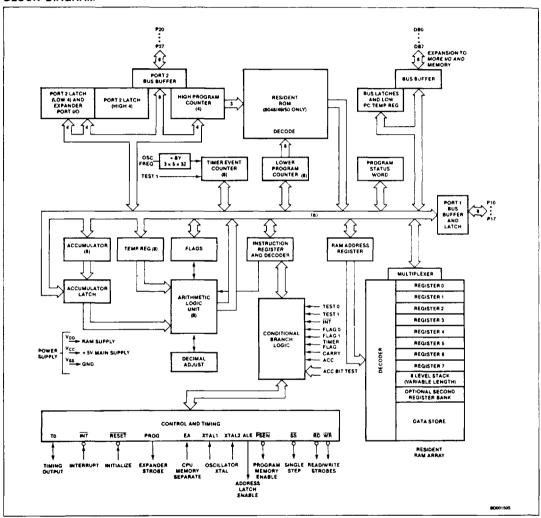

The following is a general functional description of the SCN8049 Series microcomputers. Refer to the block diagram below,

### **BLOCK DIAGRAM**

### SCN8049 Series

#### PROGRAM MEMORY

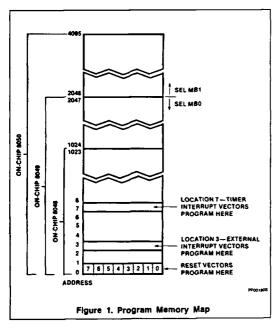

Resident program memory consists of up to 4K bytes of ROM. The program memory is divided into pages of 256 bytes each. As shown in the memory map, Figure 1, program memory is also divided into two 2048-byte banks, MB0 and MB1. A total of 4096 bytes can be addressed directly. If more memory is required, an I/O port can be used to address locations over 4095.

There are three locations in program memory of special importance. These locations contain the first instruction to be executed upon the occurrence of one of three events.

| LOCATION | EVENT                                                                    |

|----------|--------------------------------------------------------------------------|

| O        | Activation then deactivation of the RESET line.                          |

| 3        | Activation of the NT line when the external interrupt is enabled.        |

| 7        | An overflow of the timer/<br>counter if the T/C interrupt<br>is enabled. |

### DATA MEMORY

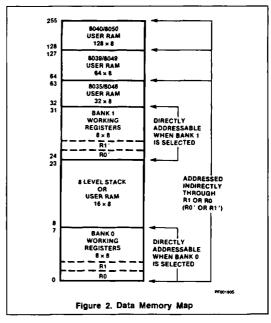

Resident data memory, as shown in Figure 2, consists of up to 256 bytes of RAM. All

locations are indirectly addressable by either of two RAM pointer registers at locations 0 and 1. The first eight locations of RAM (0-7) are designated as working registers and are directly addressable by several instructions.

By selecting register bank 1, RAM locations 24–31 become the working registers, replacing those in register bank 0 (0–7).

RAM locations 8-23 are designated as the stack. Two locations (bytes) are used per CALL, allowing nesting of up to eight subroutines.

If additional RAM is required, up to 256 bytes may be added and addressed directly using the MOVX instructions. If more RAM is required an I/O port can be used to select one (256-byte) bank of external memory at a time.

# PROGRAM COUNTER AND STACK

The Program Counter (PC) is a 12-bit counter/register that points to the location from which the next instruction is to be fetched. The 8048 and 8049 will automatically address external memory when the boundary of their internal memory is exceeded. All processors access external memory if EA is high.

An interrupt or CALL to a subroutine causes the contents of the program counter to be stored in one of the 8 register pairs of the program counter stack. The pair to be used is determined by a 3-bit stack pointer which is part of the Program Status Word (PSW). Data RAM locations 8 through 23 are available as stack registers and are used to store the program counter and 4 bits of PSW. The stack pointer, when initialized to 000, points to RAM locations 8 and 9. The first subroutine jump or interrupt results in the program counter contents being transferred to locations 8 and 9 of the RAM array. The stack pointer is then incremented by one to point to locations 10 and 11 in anticipation of another CALL. Nesting of subroutines within subroutines can continue up to eight times without overflowing the stack. If overflow does occur the deepest address stored (location 8 and 9) will be overwritten and lost since the stack pointer overflows from 111 to 000. It also underflows from 000 to 111.

The end of a subroutine, which is signalled by a return instruction (RET or RETR), causes the stack pointer to be decremented and the contents of the resulting register pair to be transferred to the program counter.

### **SCN8049 Series**

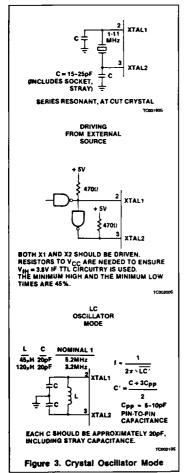

#### OSCILLATOR AND CLOCK

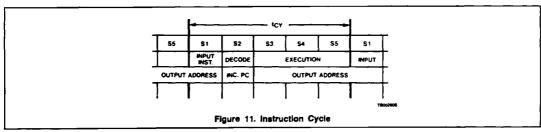

The processor contains its own internal oscillator and clock driver. A crystal, inductor, or external pulse generator may be used to determine the oscillator frequency (see Figure 3). The output of the oscillator is divided by three and can be output on the T0 pin by executing the ENTO CLK instruction. This CLK signal is divided by 5 to define a machine (instruction) cycle. It is available on Pin 11 as ALE.

### TIMER/EVENT COUNTER

An internal counter is available which can count either external events or machine cycles (÷ 32). The machine cycles are divided by 32 before they are input to the 8-bit

counter. External events are input directly to the counter. The maximum frequency that can be counted is one third of the frequency of the cycle counter. The minimum positive duty cycle that can be detected is 0.2 t<sub>CY</sub>. The counter is under program control and can be made to generate an interrupt to the processor when it overflows.

#### INTERRUPT

An interrupt may be generated by either an external input (INT, Pin 6) or the overflow of the internal counter, when enabled. In either case, the processor completes execution of the present instruction and then does a CALL to the interrupt service routine. After service, a RETR instruction restores the machine to the state it was prior to the interrupt. The external interrupt has priority over the internal interrupt.

#### INPUT/OUTPUT

The processor has 27 lines which can be used for input or output functions. These lines are grouped as 3 ports of 8 lines each which serve as either inputs, outputs or bidirectional ports and 3 "test" inputs which can alter program sequences when tested by conditional jump instructions.

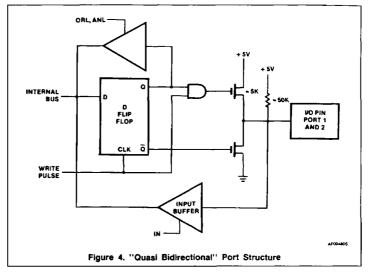

#### Ports 1 and 2

Ports 1 and 2 are each 8 bits wide and have identical characteristics. Data written to these ports is statically latched and remains unchanged until rewritten. As input ports these

lines are non-latching; i.e., inputs must be present until read by an input instruction. Inputs are fully TTL compatible and outputs will drive one standard TTL load.

The lines of ports 1 and 2 are called quasibidirectional because of a special output circuit structure which allows each line to serve as an input, an output, or both even though outputs are statically latched. Figure 4 shows the circuit configuration. Each line is continuously pulled up to +5V through a resistive device of relatively high impedance (~50K). This pullup is sufficient to provide the source current for a TTL high level yet can be pulled low by a standard TTL gate thus allowing the same pin to be used for both input and output. To provide fast switching times in a "0" to "1" transition a relatively low impedance device ( $\sim$ 50K $\Omega$ ) is switched in momentarily (~500ns) whenever a "1" is written to the line. When a "0" is written to the line, a low impedance ( $\sim$ 3000 $\Omega$ ) device overcomes the light pullup and provides TTL current sinking capability.

Since the pulldown transistor is a low impedance device a "1" must first be written to any line which is to be used as an input. Reset initializes all lines to the high impedance "1" state. This structure allows input and output on the same pin and also allows a mix of input lines and output lines on the same port. The quasi-bidirectional port in combination with the ANL and ORL logical instructions provide an efficient means for handling single line inputs and outputs within an 8-bit processor.

### SCN8049 Series

### BUS

BUS is also an 8-bit port which is a true bidirectional port with associated input and output strobes. If the bidirectional feature is not needed, BUS can serve as either a statically latched output port or non-latching input port. Input and output lines on this port cannot be mixed.

As a static port, data is written and latched using the OUTL instruction and input using the INS instruction. The INS and OUTL instructions generate pulses on the corresponding RD and WR output strobe lines; however, in the static port mode they are generally not used. As a bidirectional port, the MOVX instructions are used to read and write to the port. A write to the port generates a pulse on the WR output line and output data is valid at the trailing edge of WR. A read of the port generates a pulse on the RD output line and input data must be valid at the trailing edge of RD. When not being written or read, the BUS lines are in a high impedance state.

#### Test and INT inputs

Three pins serve as inputs and are testable with the conditional jump instruction. These are T0, T1, and INT. These pins allow inputs to cause program branches without the necessity to load an input port into the accumulator. The T0, T1, and INT pins have other possible functions as well.

#### RESET INPUT

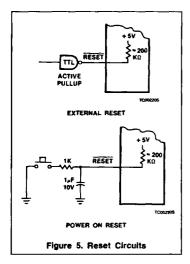

The reset input provides a means for initialization for the processor. This Schmilt-trigger input has an internal pullup resistor which in combination with an external 1µF capacitor provides an internal reset pulse of sufficient length to guarantee all circuitry is reset. If the reset pulse is generated externally, the reset pin must be held at ground (0.5V) for at least 10 milliseconds after the power supply is within tolerance. Only five machine cycles (12.5µs @ 6MHz) are required if power is already on and the oscillator has stabilized. Typical circuitry is shown in Figure 5.

#### SINGLE STEP

By proper control of the SS line, the mircrocomputer can be made to execute one instruction and then pause or wait until the single step switch is activated again.

#### **POWER DOWN MODE**

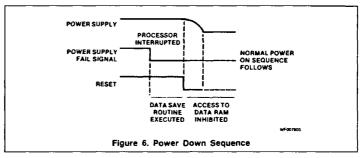

The SCN8049 Series devices permit power to be removed from all but the data RAM array for low power standby operation. In the power down mode the contents of data RAM can be maintained while drawing typically 5% of normal operating power.

$V_{CC}$  serves as the 5V supply pin for the bulk of the circuitry while the  $V_{DD}$  pin supplies only the RAM array. In normal operation both pins are at + 5V. In standby,  $V_{CC}$  is at ground and only  $V_{DD}$  is maintained at its specified voltage. Applying RESET to the processor through the RESET pin inhibits any access to the RAM by the processor and guarantees that RAM cannot be inadvertently altered as power is removed from  $V_{CC}$ .

A typical power down sequence occurs as shown in Figure 6.

#### INSTRUCTION SET

The SCN8049 Series instruction set consists of over 90 one and two byte instructions (see Table 1). Program code efficiency is high because: (1) working registers and program variables are stored in RAM, which require only one byte to address and (2) program memory is divided into pages of 256 bytes each, which means that branch destination addresses require one byte.

The instruction set efficiently manipulates and tests bits in addition to performing logical and arithmetic operations upon and the testing of bytes. A set of move instructions operates indirectly upon either RAM or ROM, which permits efficient access of pointers and data tables. The indirect jump instruction performs a multi (up to 256) way branch upon the content of the accumulator to addresses stored in a lookup table. The "decrement register and jump if not zero" instruction saves a byte every time it is used versus using separate increment and test instructions.

The on-chip counter enables either external events or time to be counted off-line from the main program. The processor can either test the counter (under program control) or cause its overflow to generate an interrupt. These features are highly desirable for real time applications. See Table 2 for instruction timing.

### **SCN8049 Series**

### **ABSOLUTE MAXIMUM RATINGS 1**

| SYMBOL           | PARAMETER                                                                  | RATING                 | UNIT |

|------------------|----------------------------------------------------------------------------|------------------------|------|

| TA               | Operating ambient temperature <sup>2</sup> range<br>SCN80xxHC<br>SCN80xxHA | 0 to +70<br>-40 to +85 | င့်င |

| T <sub>STG</sub> | Storage temperature range                                                  | -65 to +150            | °C   |

| V <sub>IN</sub>  | Input voltages with respect to V <sub>SS</sub> <sup>3</sup>                | -0.5 to +7             | V    |

| PD               | Power dissipation                                                          | 1.5                    | w    |

## DC ELECTRICAL CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{CC} = V_{DD} = 5V \pm 10\%$ , $V_{SS} = 0V^{4.5, 6}$

| CVMDOI                                                | DADAMETED                                                     | TEST CONDITIONS <sup>7</sup>                                                                                                                                                           |              | LIMITS         |                       |                  |

|-------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|-----------------------|------------------|

| SYMBOL                                                | PARAMETER                                                     | TEST CONDITIONS                                                                                                                                                                        | Min          | Тур            | Max                   | UNIT             |

| V <sub>IL</sub>                                       | Input low-voltage<br>All except XTAL1, XTAL2<br>XTAL1, XTAL2  |                                                                                                                                                                                        | -0.5<br>-0.5 |                | 0.8<br>0.6            | V                |

| V <sub>IH</sub>                                       | Input high voltage<br>All except RESET,<br>XTAL1, XTAL2       |                                                                                                                                                                                        | 2.0          | :              | Voc                   | v                |

| V <sub>IH1</sub>                                      | RESET, XTAL1, XTAL2                                           |                                                                                                                                                                                        | 3.8          |                | Vcc                   | ٧                |

| Vol                                                   | Output low-voltage                                            | I <sub>OL</sub> = 2.0mA                                                                                                                                                                |              | ]              | 0.4                   | ٧                |

| V <sub>OH</sub>                                       | Output high-voltage<br>All except BUS<br>BUS                  | l <sub>OH</sub> = ~125μA<br>l <sub>OH</sub> = ~400μA                                                                                                                                   | 2.4<br>2.4   |                |                       | v                |

| <sub>111</sub><br>  <sub>11</sub><br>  <sub>112</sub> | Port1, Port2, EA, SS<br>T1, Int<br>RESET                      | $ \begin{array}{c} V_{SS} + 0.45 \leqslant V_{IN} \leqslant V_{CC} \\ V_{SS} + 0.45 \leqslant V_{IN} \leqslant V_{CC} \\ V_{SS} + 0.45 \leqslant V_{IN} \leqslant V_{CC} \end{array} $ | -10          |                | -500<br>± 10<br>-300  | μΑ<br>μΑ<br>μΑ   |

| łor                                                   | Output leakage current<br>BUS, T0 (high inpedance state)      | V <sub>SS</sub> + 0.45 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                                                             |              |                | ± 10                  | μΑ               |

| loo                                                   | Standby supply current<br>8035/8048<br>8039/8049<br>8040/8050 | RESET   V <sub>IL</sub> All inputs = 0V  V <sub>∞</sub> = 0V                                                                                                                           | :            |                | 2.5<br>4.5<br>8.5     | mA<br>mA<br>mA   |

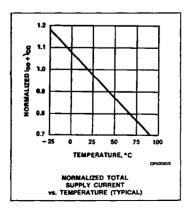

| Ipp+Icc                                               | Total supply current<br>8035/8048<br>8039/8049<br>8040/8050   | RESET < V <sub>IL</sub>                                                                                                                                                                |              | 45<br>50<br>60 | 80<br>95<br>110       | mA<br>mA<br>mA   |

| V <sub>DD</sub>                                       | Standby power supply                                          |                                                                                                                                                                                        | 2.5          |                |                       | v                |

| T <sub>A</sub> = -40 to 85                            | °C, Automotive temperature range <sup>8</sup>                 |                                                                                                                                                                                        |              |                |                       |                  |

| V <sub>IH</sub>                                       | Input high voltage All except XTAL1 and XTAL2                 |                                                                                                                                                                                        | 2.2          |                |                       | v                |

| VIHT                                                  | RESET, XTAL1, XTAL2                                           |                                                                                                                                                                                        | 4.0          |                |                       | v                |

| i <sub>IL1</sub><br>I142                              | Input leakage current<br>Port1, Port2, EA, SS<br>RESET        | V <sub>SS</sub> + .45 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub><br>V <sub>SS</sub> + .45 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                 | -5           |                | -750<br>-300          | μΑ<br>Α <b>μ</b> |

| l <sub>DO</sub>                                       | Standby supply current<br>8035/8048<br>8039/8049<br>8040/8050 | RESET < V <sub>IL</sub> All inputs = 0V V <sub>CC</sub> = 0V                                                                                                                           |              |                | 3.75<br>6.75<br>12.75 | mA<br>mA<br>mA   |

| lcc + loo                                             | Total supply current<br>8035/8048<br>8039/8049<br>8040/8050   | RESET ≤ V <sub>IL</sub>                                                                                                                                                                |              |                | 90<br>105<br>120      | mA<br>mA<br>mA   |

### SCN8049 Series

AC ELECTRICAL CHARACTERISTICS TA = 0°C to 70°C, VCC = VDD = 5V ± 10%, VSS = 0V4, 5, 6

| SYMBOL          | PARAMETER                                      | TEST                    |      | MHz<br>SIONS |      | MHz<br>SIONS | UNIT |

|-----------------|------------------------------------------------|-------------------------|------|--------------|------|--------------|------|

|                 |                                                | CONDITIONS <sup>7</sup> | Min  | Max          | Min  | Max          | ]    |

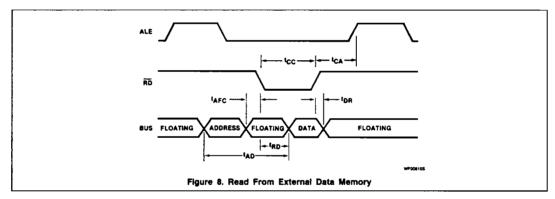

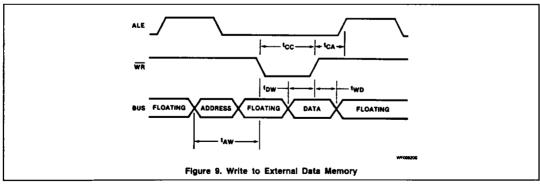

| (Refer to Figu  | ures 7, 8 and 9)                               |                         |      |              |      |              |      |

| <b>L</b> L      | ALE pulse width                                |                         | 150  |              | 400  |              | ns   |

| <sup>8</sup> AL | Address setup to ALE                           |                         | 70   |              | 150  |              | ns   |

| t <sub>LA</sub> | Address hold from ALE                          |                         | 50   |              | 80   |              | ns   |

| tcc             | Control pulse width (PSEN, RD, WR)             |                         | 300  |              | 700  |              | ns   |

| tow             | Data setup before WR                           |                         | 250  |              | 500  |              | ns   |

| two             | Data hold after WR                             |                         | 40   | 1            | 120  |              | ns   |

| <b>I</b> CY     | Cycle time                                     |                         | 1.36 | 3.75         | 2.5  | 15.0         | μs   |

| t <sub>DR</sub> | Data hold                                      |                         | 0    | 100          | 0    | 200          | ns   |

| <sup>‡</sup> RD | PSEN, RD to data in                            |                         | 1    | 200          | ,    | 500          | ns   |

| taw             | Address setup to WR                            |                         | 200  |              | 230  |              | กร   |

| 1 <sub>AD</sub> | Address setup to data in                       |                         | 1    | 400          |      | 950          | ns   |

| LAFC            | Address float to RD, PSEN                      |                         | -10  |              |      | ł            | ns   |

| €A              | Control pulse to ALE                           |                         | 10   |              | 10   |              | ns   |

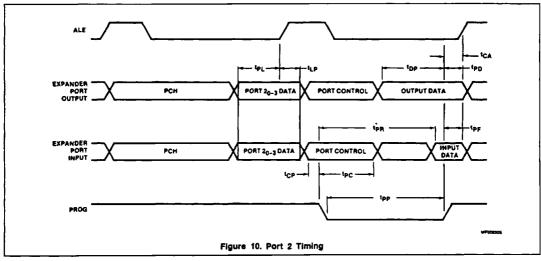

| (Refer to Figu  | ire 10)                                        |                         |      |              |      |              |      |

| top             | Port control setup before falling edge of PROG |                         | 100  |              | 110  |              | ns   |

| <b>t</b> PC     | Port control hold after falling edge of PROG   |                         | 60   |              | 130  |              | ns   |

| <b>t</b> en     | PROG to time P2 input must be valid            |                         |      | 650          |      | 810          | ns   |

| toe             | Output data setup time                         |                         | 200  | l '          | 250  |              | ns   |

| l <sub>PD</sub> | Output data hold time                          |                         | 20   |              | 65   |              | ns   |

| <b>I</b> PF     | Input data hold time                           |                         | 0    | 150          | 0    | 150          | ns   |

| 1pp             | PROG pulse width                               |                         | 700  |              | 1200 |              | ns   |

| te <sub>L</sub> | Port 2 I/O data setup                          |                         | 250  |              | 350  |              | ns   |

| t p             | Port 2 I/O data hold                           |                         | 20   |              | 150  |              | ns   |

#### HOTES:

- 1. Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of

- the device at these insect incertainty and uncertainty and the person of this specification is not implied.

2. For operating at elevated temperatures, the device must be derated based on + 150°C maximum junction temperature.

3. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to aviod applying any voltages larger than the rated maximum.

4. Parameters are valid over operating temperature range unless otherwise specified.

- 5. All voltage measurements are referenced to ground (Vss). For testing, all input signals swing between 0.4V and 2.4V with a transition time of 20ns maximum. All time measurements are referenced at input voltages of 0.8V and 2.0V and output voltages 0.8V and 2.0V as appropriate.

- Typical values are at +25°C, typical ssupply voltages and typical processing parameters.

- 7. Control outputs: C<sub>L</sub> = 80pF

Bus outputs: C<sub>L</sub> = 150pF

t<sub>CY</sub> = 1.36µs for 11 MHz versions

- tcy = 2.5 us for 6 MHz versions

- 8. Where no specification is shown, the commercial temperature range specification applies.

## **SCN8049 Series**

### TIMING DIAGRAMS

### **SCN8049 Series**

### TIMING DIAGRAMS (Continued)

## **SCN8049 Series**

Table 1. Instruction Set

| MNEMONIC       | FUNCTION                                                                                     | DESCRIPTION                                                                      | L! | NS'            | RI             | JC1 | rio | N ( | CO             | DE        | CYCLES | BYTES | FLAGS |     |    |    |    |  |

|----------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----|----------------|----------------|-----|-----|-----|----------------|-----------|--------|-------|-------|-----|----|----|----|--|

|                | 1 3.1311014                                                                                  | DESCRIPTION                                                                      | D7 | 06             | Ds             | D,  | , D | 3 D | 2 0            | , D       |        |       | С     | AC  | FO | F1 | F2 |  |

| Accumulator    |                                                                                              |                                                                                  |    |                |                |     |     |     |                |           |        |       |       | _   |    |    | _  |  |

| ADD A, # data  | (A) ← (A) + data                                                                             | Add immediate the specified data to the accumulator.                             | d7 | d <sub>6</sub> | d <sub>5</sub> | d   | d   | 3 d | <sub>2</sub> d | 1<br>1 d  |        | 2     | •     |     |    |    |    |  |

| ADD A, Rr      | (A) ← (A) + (Rr)<br>for r = 0 - 7                                                            | Add contents of designated register to the accumulator.                          | l  |                |                |     |     |     |                | r         |        | 1     | •     | •   |    |    |    |  |

| ADD A, @ Rr    | (A) ← (A) + ((Rr))<br>for r = 0 - 1                                                          | Add indirect the contents the data memory location to the accumulator.           | °  | 1              | 1              | 0   | 0   | 0   | • •            | ) r       | 1      | 1     | •     | •   |    |    |    |  |

| ADDC A, # data | (A) ← (A) + (C) + data                                                                       | Add immediate with carry the specified data to the accumulator.                  |    |                |                |     |     |     |                | 1<br>1. d |        | 2     | •     | ١٠, |    |    |    |  |

| ADDC A, Rr     | (A) ← (A) + (C) + (Rr)<br>for r = 0 - 7                                                      | Add with carry the contents of the designated register to the accumulator.       | 0  | 1              | 1              | 1   | 1   | ٢   | ſ              | г         | 1      | 1     | •     | •   |    |    |    |  |

| ADDC A, @ Rr   | $(A) \leftarrow (A) + (C) + ((Rr))$<br>for $r = 0 - 1$                                       | Add indirect with carry the contents of data memory location to the accumulator. | 0  | 1              | 1              | 1   | 0   | 0   | C              | ) г       | 1      | 1     | •     | •   |    |    |    |  |

| ANL A, # data  | (A) ← (A) AND data                                                                           | Logical AND specified immediate data with accumulator.                           |    |                |                |     |     |     |                | 1<br>1 de | 2      | 2     |       |     |    |    |    |  |

| ANL A, Fir     | (A) ← (A) AND (Rr)<br>for r = 0 - 7                                                          | Logical AND contents of designated register with accumulator.                    |    |                |                |     |     |     |                | r         | 1      | 1     |       |     |    |    |    |  |

| ANL A, @ Rr    | (A) ← (A) AND ((Rr))<br>for r = 0 – 1                                                        | Logical AND indirect the contents of data memory with accumulator.               | 0  | 1              | 0              | 1   | 0   | 0   | 0              | r         | 1      | 1     |       |     |    |    |    |  |

| CPL A          | (A) ← NOT (A)                                                                                | Complement the contents of the accumulator.                                      | ٥  | 0              | 1              | 1   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    |    |  |

| CLR A          | (A) ← 0                                                                                      | Clear the contents of the accumulator.                                           | 0  | 0              | 1              | 0   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    |    |  |

| DA A           |                                                                                              | Decimal adjust the contents of the accumulator.                                  | 0  | 1              | 0              | 1   | 0   | 1   | 1              | 1         | 1      | 1     | •     | •   |    |    |    |  |

| DEC A          | (A) ← (A) - 1                                                                                | Decrement the accumulator's contents by 1.                                       | 0  | 0              | 0              | 0   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    |    |  |

| NC A           | (A) ← (A) + 1                                                                                | Increment the accumulator's contents by 1.                                       | ٥  | 0              | 0              | 1   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    |    |  |

| ORL A, # data  | (A) ← (A) OR data                                                                            | Logical OR specified immediate data with accumulator.                            |    |                |                |     |     |     |                | 1<br>1 de | 2      | 2     |       |     |    |    |    |  |

| ORL A, Rr      | (A) ← (A) OR (Rr)<br>for r = 0 – 7                                                           | Logical OR contents of designated register with accumulator.                     | 0  | 1              | 0              | 0   | 1   | r   | •              | r         | 1      | 1     |       |     |    |    |    |  |

| ORLA, Ge Br    | (A) ← (A) OR ((Rr))<br>for r = 0 - 1                                                         | Logical OR indirect the contents of data memory location with accumulator.       | 0  | 1              | 0              | 0   | 0   | 0   | C              | ) г       | 1      | 1     |       |     |    |    |    |  |

| RL A           | $(An + 1) \leftarrow (An)$<br>$(A_0) \leftarrow (A_7)$<br>for N = 0 \leftarrow 6             | Rotate accumulator left by 1-bit without carry.                                  | 1  | 1              | 1              | 0   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    |    |  |

| ALC A          | $(An + 1) \leftarrow (An);$<br>n = 0 - 6<br>$(A_0) \leftarrow (C)$<br>$(C) \leftarrow (A_7)$ | Rotate accumulator left by 1-bit through carry.                                  | 1  | 1              | 1              | 1   | 0   | 1   | 1              | 1         | 1      | 1     | •     |     |    |    |    |  |

| RR A           | $(An) \leftarrow (An + 1);$<br>n = 0 - 6<br>$(A_7) \leftarrow (A_0)$                         | Rotate accumulator right by 1-bit without carry.                                 | 0  | 1              | 1              | 1   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    |    |  |

| RC A           | $(An) \leftarrow (An + 1);$<br>n = 0 - 6<br>$(A_7) \leftarrow (C)$<br>$(C) \leftarrow (A_0)$ | Rotate accumulator right by 1-bit through carry.                                 | 0  | 1              | 1              | 0   | 0   | 1   | 1              | 1         | 1      | 1     | •     |     |    |    |    |  |

| SWAP A         | $(A_{4-7}) \leftarrow (A_0-3)$                                                               | Swap the 2 4-bit nibbles in the accumulator.                                     | ٥  | 1              | 0              | 0   | 0   | 1   | 1              | 1         | 1      | 1     |       |     |    |    | l  |  |

| KRL A, # data  | (A) ← (A) XOR data                                                                           | Logical XOR specified immediate data with accumulator.                           |    |                |                |     |     |     |                | 1<br>1 d  |        | 2     |       |     |    |    | 1  |  |

| KRL A, Rr      | (A) ← (A) XOR (Rr)<br>for r = 0 - 7                                                          | Logical XOR contents of designated register with accumulator.                    | 1  | 1              | 0              | 1   | 1   | ſ   | •              | • •       | 1      | 1     |       |     |    |    |    |  |

| XRLA, @ Rr     | (A) ← (A) XOR ((Rr))<br>for r = 0 - 1                                                        | Logical XOR indirect the contents of data memory location with accumulator.      | 1  | 1              | 0              | 1   | O   | 0   | • •            | ) r       | 1      | 1     |       |     |    |    |    |  |

587

August 26, 1986

# SCN8049 Series

Table 1. Instruction Set (Continued)

| MNEMONIC         | FUNCTION                                                                              | DESCRIPTION                                                   | INS                                   | STF              | 100            | CT | 101            | ı c | OD | E  | CYCLES | BYTES | <u> </u> | <del>, _ f</del> | LAG | S  | _  |

|------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------|------------------|----------------|----|----------------|-----|----|----|--------|-------|----------|------------------|-----|----|----|

|                  | 10.00.00                                                                              |                                                               | 0, 0                                  | ) <sub>6</sub> i | D <sub>5</sub> | D4 | D <sub>3</sub> | 02  | ٥, | Do |        |       | С        | AC               | FO  | F1 | F2 |

| Branch           |                                                                                       |                                                               |                                       |                  |                |    |                |     |    |    |        |       |          |                  |     |    |    |

| DJNZ Fir, addr   | (Rr) ← (Rr) - 1; r = 0 - 7<br>if (Ar) ≠ 0:<br>(PC 0 - 7) ← addr                       | Decrement the specified register<br>and test contents.        | 1 1<br>a <sub>7</sub> a               |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JBb addr         | (PC 0-7) ← addr if<br>Bb = 1<br>(PC) ← (PC) + 2 if Bb<br>= 0                          | Jump to specified address if accumulator bit is set.          | b <sub>2</sub> b<br>a <sub>7</sub> a  |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JC addr          | (PC 0-7) ← addr if<br>C = 1<br>(PC) ← (PC) + 2 if C = 0                               | Jump to specified address if carry flag is set.               | 1 1<br>a <sub>7</sub> a               |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     | l  |    |

| JFO addr         | $(PC \ 0 - 7) \leftarrow addr \ if$ $F0 = 1$ $(PC) \leftarrow (PC) + 2 \ if$ $F0 = 0$ | Jump to specified address if flag<br>F0 is set.               | 1 C<br>a <sub>7</sub> a               |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JF1 <b>add</b> r | (PC 0 - 7) ← addr if<br>F1 = 1<br>(PC) ← (PC) + 2 if<br>F1 = 0                        | Jump to specified address if flag<br>F1 is set.               | 0 1<br>a <sub>7</sub> a               |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     | :  | 1  |

| JMP addr         | (PC 8 - 10) ← addr<br>8 - 10<br>(PC 0 - 7) ← addr 0 - 7<br>(PC 11) ← (DBF)            | Direct jump to specified address within the 2K address block. | a <sub>10</sub> a<br>a <sub>7</sub> a |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JMPP @ A         | (PC 0-7) ← ((A))                                                                      | Jump indirect to specified address within address page.       | 1 0                                   | •                | 1              | 1  | 0              | 0   | 1  | 1  | 2      | 1     |          |                  |     |    |    |

| JNC addr         | (PC 0-7) ← addr if<br>C=0<br>(PC) ← (PC) + 2 if C=1                                   | Jump to specified address if carry flag is low.               | 1 1<br>2 <sub>7</sub> 8               |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JNI              | (PC 0-7) ← addr if<br>INT = 0<br>(PC) ← (PC) + 2 if<br>INT = 1                        | Jump to specified address if INT input is low.                | 1 C                                   |                  |                |    |                |     |    | -  | 2      | 2     |          |                  |     |    |    |

| JNT0 addr        | $(PC \ 0-7) \leftarrow addr \ if$ $T0 = 0$ $(PC) \leftarrow (PC) + 2 \ if$ $T0 = 1$   | Jump to specified address if test 0 is low.                   | 0 0<br>87 8                           |                  |                |    |                |     |    | -  | 2      | 2     |          |                  |     |    |    |

| JNT1 addr        | $(PC \ 0-7) \leftarrow addr \ if$ $T1 = 0$ $(PC) \leftarrow (PC) + 2 \ if$ $T1 = 1$   | Jump to specified address if test 1 is low.                   | 0 1<br>87 8                           |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    | i  |

| JNZ addr         | (PC 0-7) ← addr if<br>A = 0<br>(PC) ← (PC) + 2 if A = 0                               | Jump to specified address if accumulator is non-zero.         | 1 C                                   |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JTF addr         | (PC 0 - 7) ← addr if<br>TF = 1<br>(PC) ← (PC) + 2 if<br>TF = 0                        | Jump to specified address if timer flag is set to 1.          | 0 0<br>87 8                           |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JTO addr         | (PC 0 - 7) ← addr if<br>T0 = 1<br>(PC) ← (PC) + 2 if<br>T0 = 0                        | Jump to specified address if test 0 is a 1.                   | 0 0<br>87 8                           |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JT1 addr         | (PC 0 - 7) ← addr if<br>T1 = 1<br>(PC) ← (PC) + 2 if<br>T1 = 0                        | Jump to specified address if test 1 is a 1.                   | 0 1<br>87 8                           |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| JZ addr          | (PC 0-7) ← addr if<br>A = 0<br>(PC) ← (PC) + 2 if A ≠ 0                               | Jump to specified address if accumulator is 0.                | 1 1<br>87 a                           |                  |                |    |                |     |    |    | 2      | 2     |          |                  |     |    |    |

| Control          | <u> </u>                                                                              |                                                               |                                       |                  |                |    |                |     |    |    |        |       |          | •                |     | _  |    |

| EN I             |                                                                                       | Enable the external (INT) interrupt.                          | 0 0                                   | ) (              | 0              | 0  | 0              | 1   | 0  | 1  | 1      | 1     |          |                  |     |    | Г  |

| DIS I            | (DC) (= 0                                                                             | Disable the external (INT) interrupt.                         | 0 0                                   |                  | -              |    | -              |     |    |    | 1      | 1     |          |                  |     |    | ١. |

| SEL RBO          | (BS) ← 0                                                                              | Select bank 0 (locations 0 - 7) of data memory.               | l''                                   | , ,              |                | U  | U              | ٠   | U  | '  | '      | '     |          |                  |     |    | Ι. |

588

August 26, 1986

## **SCN8049 Series**

Table 1. Instruction Set (Continued)

| MNEMONIC          | FINATION                            | DECORITION.                                                                        | Ħ       | NST     | RL             | СТ             | 101            | N C                 | OE | E    |        |       |     | F       | LAG      | s  |    |

|-------------------|-------------------------------------|------------------------------------------------------------------------------------|---------|---------|----------------|----------------|----------------|---------------------|----|------|--------|-------|-----|---------|----------|----|----|

| MAEMONIC          | FUNCTION                            | DESCRIPTION                                                                        | D7      | De      | Ds             | D4             | D <sub>3</sub> | D <sub>2</sub>      | Dı | Do   | CYCLES | BYTES | С   | AC      | FO       | F1 | F2 |

| Control (Cont.)   |                                     |                                                                                    |         |         |                |                |                |                     |    |      |        | -     |     |         |          |    | •  |

| SEL RB1           | (BS) ← 1                            | Select bank 1 (locations 24-31) of data memory.                                    | 1       | 1       | 0              | 1              | 0              | 1                   | 0  | 1    | 1      | 1     |     |         |          |    | •  |

| SEL MB0           | (DBF) ← 0                           | Select program memory bank 0, addresses 0 - 2047.                                  | 1       | 1       | 1              | 0              | 0              | 1                   | 0  | 1    | 1      | 1     |     |         |          |    |    |

| SEL MB1           | (DBF) ← 1                           | Select program memory bank 1,<br>addresses 2048 - 4095                             | 1       | 1       | 1              | 1              | 0              | 1                   | 0  | 1    | 1      | 1     |     |         |          |    |    |

| ENTO CLK          |                                     | Enable clock output on T0 pin.                                                     | 0       | 1       | 1              | 1              | 0              | 1                   | 0  | 1    | 1      | 1     |     |         |          |    |    |

| Data moves        |                                     |                                                                                    |         |         |                |                |                |                     |    |      |        | _     |     |         |          |    | _  |

| MOV A, # data     | (A) ← data                          | Move immediate the specified data into the accumulator.                            | O<br>d7 | O<br>de |                |                |                | 0                   |    |      | 2      | 2     |     |         |          |    |    |

| MOV A, Rr         | (A) ← (Ar); r = 0 - 7               | Move the contents of the designated register into the accumulator.                 |         | 1       |                |                |                |                     |    |      | 1      | 1     |     |         |          |    |    |

| MOV A, @ Fir      | (A) ← ((Ar)); r = 0 - 1             | Move indirect the contents of data memory location into the accumulator.           | ,       | 1       | 1              | 1              | 0              | 0                   | 0  | r    | 1      | 1     |     |         |          |    |    |

| MOV A, PSW        | (A) ← (PSW)                         | Move contents of the program status word into the accumulator.                     | 1       | 1       | 0              | 0              | 0              | 1                   | 1  | 1    | 1      | 1     |     |         |          |    |    |

| MOV Rr, # data    | (Rr) ← data; r = 0 - 7              | Move immediate the specified data into the designated register.                    | 1<br>07 | 0<br>de |                |                |                | f<br>d <sub>2</sub> |    |      | 2      | 2     |     |         | '        |    |    |

| MOV Rr, A         | (Ar) ← (A); r = 0 - 7               | Move accumulator contents into the designated register.                            | 1       | 0       |                |                |                |                     |    |      | 1      | 1     |     |         |          |    |    |

| MOV @ Fir, A      | ((Rr)) ← (A); r = 0 - 1             | Move indirect accumulator contents into data memory location.                      | 1       |         |                |                |                |                     |    |      | 1      | 1     |     |         |          |    |    |

| MOV 6 Fir, # data | ((Rr)) ← data; r = 0 - 1            | Move indirect the specified data into data memory.                                 |         | de      | d <sub>5</sub> | d <sub>4</sub> | d <sub>3</sub> |                     | d  | de   |        | 2     |     |         |          |    |    |

| MOV PSW, A        | (PSW) ← (A)                         | Move contents of accumulator into the program status word.                         | 1       | 1       | Q              | 1              | 0              | 1                   | 1  | 1    | 1      | 1     | •   | •       | •        |    | ١. |

| MOVP A, @ A       | (A) ← ((A))                         | Move data in the current page into the accumulator.                                | 1       |         |                |                |                |                     |    |      | 2      | 1     |     |         |          |    |    |

| MOVP3 A, & A      | (A) ← ((A))<br>in page 3            | Move data in page 3 into the accumulator.                                          |         | 1       |                |                |                |                     |    |      | 2      | 1     |     |         |          |    |    |

| MOVX A, & Rr      | (A) ← ((Rr)); r = 0 - 1             | Move indirect the contents of<br>external memory location into the<br>accumulator. | 1       | 0       | 0              | 0              | 0              | 0                   | 0  | r    | 2      | 1     |     |         |          |    |    |

| MOVX & Rr, A      | ((Rr)) ← (A); r = 0 - 1             | Move indirect the contents of the<br>accumulator into external memory.             | 1       |         |                |                |                | 0                   |    |      | 2      | 1     |     |         |          |    |    |

| XCH A, Rr         | (A) ++ (Br); r = 0 - 7              | Exchange the accumulator and designated register's contents.                       | 0       | 0       |                |                |                |                     | r  | r    | 1      | 1     |     |         |          |    | ١  |

| XCH A, ● Rr       | (A) ((Rr)); r = 0 - 1               | Exchange indirect contents of accumulator and location in data memory.             | 0       | 0       | 1              | 0              | 0              | 0                   | 0  | r    | 1      | 1     |     |         |          |    |    |

| XCHD A, @ Rr      | (A 0-3) → (Rr)(0-3)<br>r=0-1        | Exchange indirect 4-bit contents of accumulator and data memory.                   | 0       | 0       | 1              | 1              | 0              | 0                   | 0  | r    | 1      | 1     |     |         |          |    |    |

| Flags             |                                     |                                                                                    | _       |         |                |                |                |                     |    |      |        |       |     |         |          |    |    |

| CPL C             | (C) ← NOT (C)                       | Complement content of carry bit.                                                   | 1       | 0       | 1              |                |                | 1                   |    | 1    | 1      | 1     | •   |         | _        | _  | Γ  |

| CPL F0            | (F0) ← NOT (F0)                     | Complement content of flag F0.                                                     | 1       | 0       | 0              | 1              | 0              |                     | 0  |      | 1      | 1     |     |         | •        | l  | 1  |

| CPL F1            | (F1) ← NOT (F1)                     | Complement content of flag F1.                                                     | 1       | 0       | 1              | 1              | 0              | 1                   | 0  |      | 1      | 1     | 1   | 1       | l        | •  | ı  |

| CLR C             | (C) ← 0                             | Clear content of carry bit to 0.                                                   | 1       | 0       | 0              | 1              |                |                     | 1  |      | 1      | 1     | ٠ ا | 1       | l        |    | 1  |

| CLR FO            | (F0) ← 0                            | Clear content of flag 0 to 0.                                                      | 1       | 0       |                |                |                | 1                   |    |      | 1      | 1     | l   | 1       | ١.       |    |    |

| CLR F1            | (F1) ← 0                            | Clear content of flag 1 to 0.                                                      | 1       | 0       | 1              | 0              | 0              | _1                  | 0  | 1    | 11     | 1     |     | <u></u> | <u> </u> |    | ŀ  |

| Input/output      |                                     |                                                                                    | _       |         |                |                |                |                     |    |      |        |       |     |         |          |    | _  |

| ANL BUS, # data   | (BUS) ← (BUS) AND data              | Logical AND immediate specified data with BUS.                                     |         | de      | ds             | da             | d              |                     | d  | de   |        | 2     |     |         |          |    |    |

| ANL Pp, # data    | (Pp) ← (Pp) AND data<br>p = 1 - 2   | Logical AND immediate specified data with designated port (1 or 2).                | d,      | o<br>de | ds             | d              | d              | d                   | d  | ı dı |        | 2     |     | l       |          |    |    |

| ANLD Pp. A        | (Pp) ← (Pp) AND (A<br>0-3)<br>p=4-7 | Logical AND contents of accumulator with designated port (4-7).                    | 1       | 0       | 0              | 1              | 1              | 1                   | P  | P    | 2      | 1     |     |         |          |    |    |

### **SCN8049 Series**

Table 1. Instruction Set (Continued)

| MNEMONIC          | FUNCTION                                                                                    | DESCRIPTION                                                       | <u></u> | NST | TRI | JCT | 101 | 1 0                 | QD | E   | CYCLES | BYTES | L  | F     | LAG | S  |   |

|-------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------|-----|-----|-----|-----|---------------------|----|-----|--------|-------|----|-------|-----|----|---|

| MMEMORIC          | PONCTION                                                                                    | DESCRIPTION                                                       | 07      | De  | 05  | 04  | 03  | 02                  | 0, | ď   |        | BTIES | С  | AC    | FO  | F1 | F |

| Input/output (Cor | it.)                                                                                        |                                                                   |         |     |     |     |     |                     |    |     |        |       |    |       |     |    |   |

| IN A, Pp          | (A) ← (Pp); p = 1 - 2                                                                       | Input data from designated port (1 - 2) into accumulator.         | 0       | 0   | 0   | 0   | 1   | 0                   | P  | P   | 2      | 1     |    |       |     |    | T |

| INS A, BUS        | (A) ← (BUS)                                                                                 | Input strobed BUS data into accumulator.                          | 0       | 0   | 0   | 0   | 1   | 0                   | 0  | 0   | 1      | 2     |    |       |     |    |   |

| MOVD A, Pp        | (A 0-3) ← (Pp);<br>p = 4-7<br>(A 4-7) ← 0                                                   | Move contents of designated port (4 – 7) into accumulator.        | l°      | 0   | 0   | 0   | 1   | 1                   | P  | P   | 2      | 1     |    |       |     | ŀ  |   |

| MOVD Pp, A        | (Pp) ← A 0-3; p = 4-7                                                                       | Move contents of accumulator to designated port (4 - 7).          | 0       | 0   | 1   | 1   | 1   | 1                   | P  | Р.  | 1      | 1     |    |       |     |    |   |

| ORLD Pp, A        | (Pp) ← (Pp) OR (A<br>0-3)<br>p=4-7                                                          | Logical OR contents of accumulator with designated port (4 - 7).  | 1       | 0   | 0   | 0   | 1   | 1                   | P  | P   | 1      | 1     |    |       |     |    |   |

| ORL BUS, # data   | (BUS) ← (BUS) OR data                                                                       | Logical OR immediate specified data with BUS.                     |         |     |     |     |     | 0<br>d <sub>2</sub> |    |     | 2      | 2     |    |       |     |    |   |

| ORL Pp. # data    | (Pp) ← (Pp) OR data<br>p = 1 ~ 2                                                            | Logical OR immediate specified data with designated port (1 - 2). |         |     |     |     |     | 0<br>d <sub>2</sub> |    |     | 2      | 2     |    |       |     |    |   |

| OUTL BUS, A       | (BUS) ← (A)                                                                                 | Output contents of accumulator onto BUS.                          | °       | 0   | 0   | 0   | 0   | 0                   | 1  | 0   | 1      | 2     |    |       |     |    |   |

| OUTL Pp. A        | (Pp) ← (A); p = 1 - 2                                                                       | Output contents of accumulator to designated port (1 - 2).        | 0       | 0   | 1   | 1   | 1   | 0                   | P  | P   | 1      | 1     |    |       |     |    |   |

| Registers         |                                                                                             |                                                                   |         |     |     |     |     |                     |    |     |        |       |    |       |     |    |   |

| DEC Rr            | (Rr) ← (Rr) - 1; r = 0 - 7                                                                  | Decrement contents of designated register by 1.                   | 1       | 1   | 0   | 0   | 1   | r                   | r  | ٦   | 1      | 1     |    |       |     |    |   |

| INC Fir           | (Rr) ← (Rr) + 1; r = 0 - 7                                                                  | Increment contents of designated register by 1.                   | ٥       | 0   | 0   | 1   | 1   | ſ                   | r  | ٢   | 1      | 1     |    |       |     |    | ١ |

| INC & Rr          | ((Rr)) ← ((Rr)) + 1;<br>r = 0 - 1                                                           | Increment indirect the contents of data memory location by 1.     | 0       | 0   | 0   | 1   | 0   | 0                   | 0  | r   | 1      | 1     |    |       |     |    |   |

| Subroutine        | •                                                                                           |                                                                   |         |     |     | _   |     |                     |    |     |        |       |    |       |     |    | _ |

| CALL addr         | ((SP)) ← (PC), (PSW<br>4-7)                                                                 | Call designated subroutine.                                       |         |     |     |     |     | 1 82                |    |     | 2      | 2     |    |       |     |    | Г |

|                   | (SP) ← (SP) + 1<br>(PC 8 - 10) ← addr<br>8 - 10<br>(PC 0 - 7) ← addr 0 - 7<br>(PC 11) ← DBF |                                                                   |         | •   |     |     | •   | •                   |    |     |        |       |    |       |     |    |   |

| RET               | (SP) ← (SP) - 1<br>(PC) ← ((SP))                                                            | Return from subroutine without restoring program status word.     | 1       | 0   | 0   | 0   | 0   | 0                   | 1  | 1   | 2      | 1     |    |       |     |    |   |

| RETR              | (SP) ← (SP) - 1<br>(PC) ← ((SP))<br>(PSW 4-7) ← ((SP))                                      | Return from subroutine restoring program status word.             | 1       | 0   | 0   | 1   | 0   | 0                   | 1  | 1   | 2      | 1     |    |       |     |    | i |

| Timer/counter     |                                                                                             |                                                                   |         |     |     |     |     |                     |    |     |        |       |    |       |     |    |   |

| EN TCNTI          |                                                                                             | Enable timer/counter interrupt.                                   |         |     |     | 0   |     |                     | 0  | 1   | 1      | 1     |    |       |     |    |   |

| DIS TONTI         |                                                                                             | Disable timer/counter interrupt.                                  | 1       |     | 1   |     | 0   |                     | 0  | 1   | 1      | 1     |    |       |     |    | l |

| MOV A, T          | (n) ← (n)                                                                                   | Move contents of timer/counter into accumulator.                  |         |     | 0   |     |     | 0                   |    |     | 1      | 1     |    |       |     |    |   |

| MOV T, A          | (N → (N                                                                                     | Move contents of accumulator into<br>timer/counter.               | İ       |     |     |     |     | 0                   |    |     | 1      | 1     |    |       |     |    |   |

| STOP TONT         |                                                                                             | Stop count for event counter or timer.                            |         |     |     |     |     | 1                   |    | ı   | 1      | 1     |    |       | i   |    |   |

| STRT CNT          |                                                                                             | Start count for event counter.                                    | 1       |     |     |     |     | 1                   |    | - 1 | 1      | 1     |    |       |     |    |   |

| STRT T            |                                                                                             | Start count for timer.                                            | 0       | 1   | U   | 1   | U   | 1_                  | 0  | 1   | 1      | 1     | L_ | لـــا |     | L  | L |

| Miscellaneous     |                                                                                             |                                                                   |         | _   | _   | _   | _   | _                   | _  |     |        |       |    |       |     | _  | _ |

| <b>NOP</b>        | i l                                                                                         | No operation performed                                            | 0       | 0   | 0   | 0   | 0   | 0                   | 0  | 0   | 1      | 1     |    |       |     |    | 1 |

NOTES:

1. Instruction code designations r and p form the binary representation of the registers and ports involved.

2. The dot under the appropriate flag bit indicates that its content is subject to change by the instruction in which it appears.

3. Numerical subscripts appearing in the FUNCTION column reference the specific bits affected.

### **SCN8049 Series**

### SYMBOL DEFINITIONS

| SYMBOL                          | DESCRIPTION                      |

|---------------------------------|----------------------------------|

| Α                               | The accumulator                  |

| AC                              | The auxiliary carry flag         |

| addr                            | Program memory address (11 bits) |

| ₽b                              | Bit designator (b = 0 - 7)       |

| BS                              | The bank switch                  |

| С                               | Carry flag                       |