# STA510F

## 44-V, 5.5-A, quad power half bridge

## Features

- Minimum input output pulse width distortion

- 150 mW Rdson complementary DMOS output stage

- CMOS compatible logic inputs

- Thermal protection

- thermal warning output

- Under-voltage protection

- No power-on, power- off sequence required

## Description

STA510F is a monolithic, quad, half-bridge stage in Multipower BCD technology. The device can be used as dual bridge or reconfigured, by connecting CONFIG pin to Vdd pin, as single bridge with double current capability, and as half bridge (binary mode) with half current capability.

The device is particularly designed to make the output stage of a stereo all-digital high-efficiency (FFX) amplifier capable of delivering 100 W + 100 W output power into 8- $\Omega$  loads with THD = 10% and V<sub>cc</sub> = 39 V. In single BTL configuration the device can deliver 200 W into a 4- $\Omega$  load with THD = 10% and V<sub>cc</sub> = 39 V.

The device is fully compatible with the  $\text{DDX}^{\textcircled{R}}$  driver device.

The input pins have a threshold proportional to  $\ensuremath{\mathsf{V_L}}$  pin voltage.

#### Table 1. Device summary

| Order code | Operating Temp. range | Package             | Packing |

|------------|-----------------------|---------------------|---------|

| STA510F    | 0° to 70° C           | PowerSO36 (slug up) | Tube    |

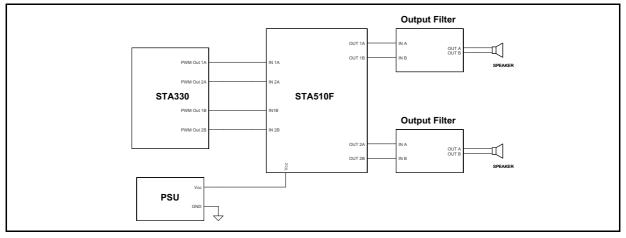

#### Figure 1. Typical application

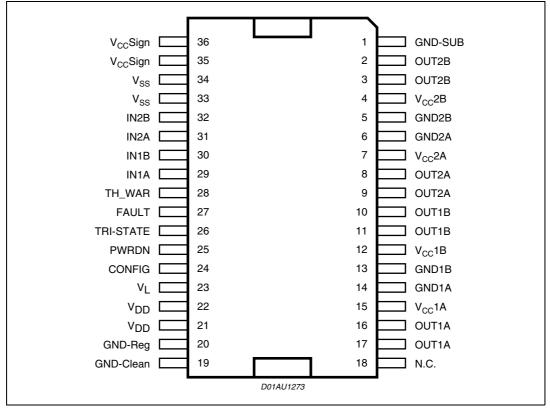

## 1 Pin description

#### Table 2. Pin list

| Pin    | Name    | Description           |

|--------|---------|-----------------------|

| 1      | GND-SUB | Substrate ground      |

| 2, 3   | OUT2B   | Output half bridge 2B |

| 4      | Vcc2B   | Positive Supply       |

| 5      | GND2B   | Negative Supply       |

| 6      | GND2A   | Negative Supply       |

| 7      | Vcc2A   | Positive Supply       |

| 8, 9   | OUT2A   | Output half bridge 2A |

| 10, 11 | OUT1B   | Output half bridge 1B |

| 12     | Vcc1B   | Positive Supply       |

| 13     | GND1B   | Negative Supply       |

| 14     | GND1A   | Negative Supply       |

| 15     | Vcc1A   | Positive Supply       |

| 16, 17 | OUT1A   | Output half bridge 1A |

| Pin    | Name      | Description                        |

|--------|-----------|------------------------------------|

| 18     | NC        | Not connected                      |

| 19     | GND-clean | Logical ground                     |

| 20     | GND-Reg   | Ground for regulator Vdd           |

| 21, 22 | Vdd       | 5V Regulator referred to ground    |

| 23     | VL        | High logical state setting voltage |

| 24     | CONFIG    | Configuration                      |

| 25     | PWRDN     | Stand-by                           |

| 26     | TRI-STATE | Hi-Z                               |

| 27     | FAULT     | Fault pin advisor                  |

| 28     | TH-WAR    | Thermal warning advisor            |

| 29     | IN1A      | Input of half bridge 1A            |

| 30     | IN1B      | Input of half bridge 1B            |

| 31     | IN2A      | Input of half bridge 2A            |

| 32     | IN2B      | Input of half bridge 2B            |

| 33, 34 | Vss       | 5-V regulator referred to +Vcc     |

| 35, 36 | VCCSIGN   | Signal positive supply             |

Table 2. Pin list (continued)

### Table 3.

| Pin                   | Logical value | Device status                                                    |  |  |  |

|-----------------------|---------------|------------------------------------------------------------------|--|--|--|

| FAULT <sup>(1)</sup>  | 0             | Fault detected (short circuit, or thermal)                       |  |  |  |

| FAULI                 | 1             | Normal operation                                                 |  |  |  |

| TRI-STATE             | 0             | All power stages in Hi-Z state                                   |  |  |  |

| TRI-STATE             | 1             | Normal operation                                                 |  |  |  |

| PWBDN 0               |               | Low-power mode                                                   |  |  |  |

| רייחטוי               | 1             | Normal operation                                                 |  |  |  |

| THWAR <sup>(1)</sup>  | 0             | Temperature of the IC =130° C                                    |  |  |  |

|                       | 1             | Normal operation                                                 |  |  |  |

|                       | 0             | Normal Operation                                                 |  |  |  |

| CONFIG <sup>(2)</sup> | 1             | OUT1A = OUT1B, OUT2A = OUT2B<br>(IF IN1A = IN1B and IN2A = IN2B) |  |  |  |

1. The pin is open collector. To have the high logic value, it needs a pull-up resistor.

2. CONFIG = 1 means connect Pin 24 (CONFIG) to Pins 21, 22 (Vdd).

## 2 Electrical specifications

### 2.1 Absolute maximum ratings

#### Table 4. Absolute maximum ratings

| Symbol                            | Parameter                            | Value      | Unit |

|-----------------------------------|--------------------------------------|------------|------|

| V <sub>CC</sub>                   | DC supply voltage (Pin 4, 7, 12, 15) | 44         | V    |

| V <sub>max</sub>                  | Maximum voltage on pins 23 to 32     | 5.5        | V    |

| ESD                               | Max ESD on pins (HBM)                | ±1000      | V    |

| T <sub>op</sub>                   | Operating temperature range          | 0 to 70    | °C   |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and junction temperature     | -40 to 150 | °C   |

## 2.2 Thermal data

### Table 5. Thermal data

| Symbol              | Parameter                                         | Min | Тур | Мах | Unit |

|---------------------|---------------------------------------------------|-----|-----|-----|------|

| T <sub>j-case</sub> | Thermal resistance junction to case (thermal pad) |     | 1   | 2.5 | °C/W |

| T <sub>jSD</sub>    | Thermal shut-down junction temperature            |     | 150 |     | °C   |

| T <sub>warn</sub>   | Thermal warning temperature                       |     | 130 |     | °C   |

| t <sub>hSD</sub>    | Thermal shut-down hysteresis                      |     | 25  |     | °C   |

## 2.3 Electrical specifications

Unless otherwise stated, the results in *Table 6* below are given for the conditions:  $V_L = 3.3 \text{ V}$ , Vcc = 37 V and T = 25° C unless otherwise specified.

| Symbol            | Parameter                                  | Condition                                                                                                 | Min | Тур | Max | Unit |

|-------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>dsON</sub> | Power Pchannel/Nchannel<br>MOSFET RdsON    | ld = 1 A                                                                                                  |     | 150 | 200 | mΩ   |

| I <sub>dss</sub>  | Power Pchannel/Nchannel<br>leakage current |                                                                                                           |     |     | 100 | μA   |

| g <sub>N</sub>    | Power Pchannel RdsON matching              | ld = 1 A                                                                                                  | 95  |     |     | %    |

| 9 <sub>P</sub>    | Power Nchannel RdsON matching              | ld = 1 A                                                                                                  | 95  |     |     | %    |

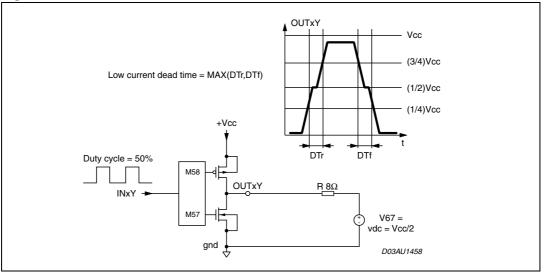

| Dt_s              | Low current dead time (static)             | see test circuit Figure 3                                                                                 |     | 10  | 20  | ns   |

| Dt_d              | High current dead time<br>(dynamic)        | L=22 $\mu$ H, C = 470nF,<br>R <sub>L</sub> = 8 $\Omega$ , Id = 4.5 A,<br>see test circuit <i>Figure 4</i> |     |     | 50  | ns   |

Table 6. Electrical specifications

| Symbol                     | Parameter                                                                         | Condition                                                                                     | Min                             | Тур | Max                              | Unit |

|----------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------|-----|----------------------------------|------|

| t <sub>d ON</sub>          | Turn-on delay time                                                                | Resistive load                                                                                |                                 |     | 100                              | ns   |

| t <sub>d OFF</sub>         | Turn-off delay time                                                               | Resistive load                                                                                |                                 |     | 100                              | ns   |

| t <sub>r</sub>             | Rise time                                                                         | Resistive load, as <i>Figure 4</i>                                                            |                                 |     | 25                               | ns   |

| t <sub>f</sub>             | Fall time                                                                         | Resistive load, as <i>Figure 4</i>                                                            |                                 |     | 25                               | ns   |

| V <sub>CC</sub>            | Supply voltage operating voltage                                                  |                                                                                               | 10                              |     | 40                               | V    |

| V <sub>IN-High</sub>       | High level input voltage                                                          |                                                                                               | V <sub>L</sub> /2<br>+300<br>mV |     |                                  | v    |

| V <sub>IN-Low</sub>        | Low level input voltage                                                           |                                                                                               |                                 |     | V <sub>L</sub> /2 -<br>300m<br>V | v    |

| I <sub>IN-H</sub>          | High level input current                                                          | Pin voltage = $V_L$                                                                           |                                 | 1   |                                  | μA   |

| I <sub>IN-L</sub>          | Low level input current                                                           | Pin voltage = 0.3V                                                                            |                                 | 1   |                                  | μA   |

| I <sub>PWRDN-H</sub>       | High level PWRDN pin input<br>current                                             | V <sub>L</sub> = 3.3V                                                                         |                                 | 35  |                                  | μA   |

| V <sub>Low</sub>           | Low logical state voltage (pins PWRDN, TRISTATE) (see <i>Table 7</i> )            | V <sub>L</sub> = 3.3V                                                                         |                                 |     | 0.8                              | v    |

| V <sub>High</sub>          | High logical state voltage (pins<br>PWRDN, TRISTATE) (see<br><i>Table 7</i> )     | V <sub>L</sub> = 3.3V                                                                         | 1.7                             |     |                                  | v    |

| I <sub>VCC-</sub><br>PWRDN | Supply current from Vcc in power down                                             | PWRDN = 0                                                                                     |                                 |     | 3                                | mA   |

| I <sub>FAULT</sub>         | Output current pins<br>FAULT -TH-WARN when<br>FAULT CONDITIONS                    | Vpin = 3.3V                                                                                   |                                 | 1   |                                  | mA   |

| I <sub>VCC-hiz</sub>       | Supply current from Vcc in tri-<br>state                                          | Pin TRI-STATE = 0                                                                             |                                 | 22  |                                  | mA   |

| I <sub>VCC</sub>           | Supply current from Vcc in<br>operation<br>both channel switching)                | Input pulse width duty<br>cycle = 50%,<br>switching frequency<br>= 384 kHz,<br>no LC filters; |                                 | 70  |                                  | mA   |

| I <sub>OUT-SH</sub>        | Overcurrent protection threshold<br>lsc (short circuit current limit)<br>(note 2) |                                                                                               | 5.5                             | 7   | 9                                | A    |

| V <sub>UV</sub>            | Undervoltage protection threshold                                                 |                                                                                               |                                 | 7   |                                  | v    |

| t <sub>pw_min</sub>        | Output minimum pulse width                                                        | No Load                                                                                       | 25                              |     | 40                               | ns   |

Table 6.

Electrical specifications (continued)

| VL  | V <sub>Low</sub> max | V <sub>High</sub> min | Unit |

|-----|----------------------|-----------------------|------|

| 2.7 | 0.7                  | 1.5                   | V    |

| 3.3 | 0.8                  | 1.7                   | V    |

| 5   | 0.85                 | 1.85                  | V    |

Table 7. V<sub>low</sub>, V<sub>high</sub> threshold variation with V<sub>L</sub>

#### Table 8.Logic truth table

| TRI-STATE | INxA | INxB | Q1  | Q2  | Q3  | Q4  | Output mode |

|-----------|------|------|-----|-----|-----|-----|-------------|

| 0         | х    | х    | OFF | OFF | OFF | OFF | Hi-Z        |

| 1         | 0    | 0    | OFF | OFF | ON  | ON  | DUMP        |

| 1         | 0    | 1    | OFF | ON  | ON  | OFF | NEGATIVE    |

| 1         | 1    | 0    | ON  | OFF | OFF | ON  | POSITIVE    |

| 1         | 1    | 1    | ON  | ON  | OFF | OFF | Not used    |

Figure 3. Test circuit for low current dead time

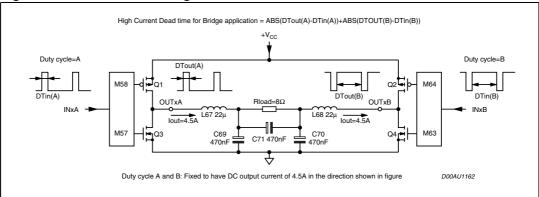

#### Figure 4. Test circuit for high current dead time

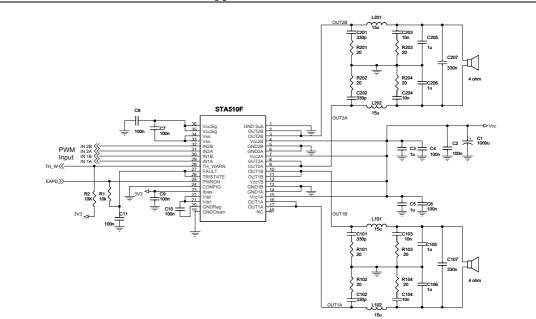

Figure 5. Typical quad half-bridge configuration giving 200 W per channel into 4  $\Omega$  speakers, 10% THD, V<sub>CC</sub> = 39 V

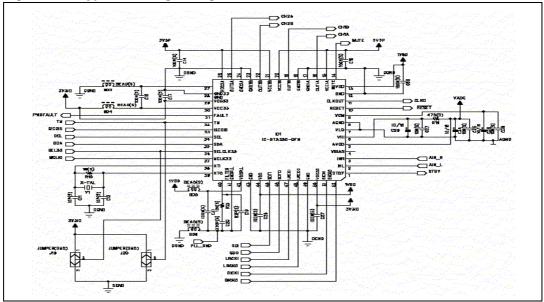

Figure 6. Typical driving configuration with STA330

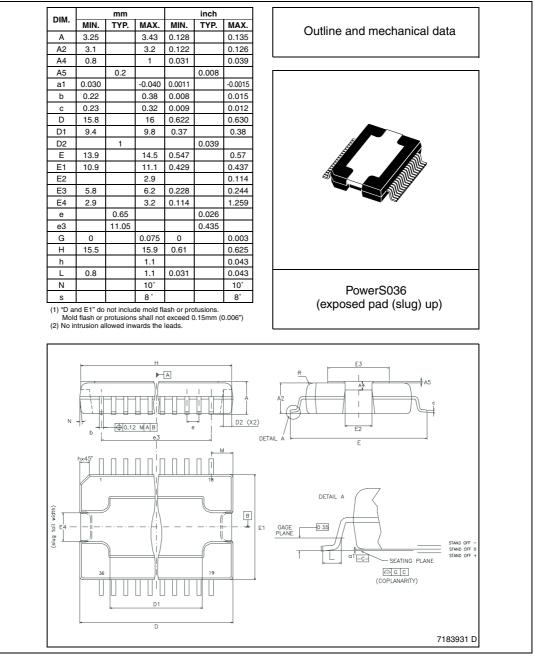

## 3 Package information

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark.

ECOPACK specifications are available at: http://www.st.com.

Figure 7. PowerSO36 package dimensions

## 4 Trademarks and other acknowledgements

FFX is a STMicroelectronics proprietary digital modulation technology. DDX is a registered trademark of Apogee Technology, Inc. ECOPACK is a registered trademark of STMicroelectronics.

## 5 Revision history

### Table 9.Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 13-Dec-2007 | 1        | Initial release. |

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com