# IBW ®

# IBM PowerNP™ NP4GS3

# **Databook**

© Copyright International Business Machines Corporation 1999, 2000

#### All Rights Reserved

US Government Users Restricted Rights - Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Printed in the United States of America September 2000

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM IBM Logo

PowerPC

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the design, sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

np3\_DL\_title.fm.01 09/25/00

### **Contents**

**Preliminary**

| List of Tables                             | 11  |

|--------------------------------------------|-----|

| List of Figures                            | 17  |

| About This Book                            | 19  |

| Who Should Read This Manual                | 19  |

| Related Publications                       | 19  |

| Conventions Used in This Manual            | 19  |

| 1. General Information                     | 21  |

| 1.1 Features                               | 21  |

| 1.2 Ordering Information                   | 22  |

| 1.3 Overview                               |     |

| 1.4 NP4GS3-Based System Design             |     |

| 1.4.1 Coprocessors                         |     |

| 1.4.2 Hardware Accelerators                |     |

| 1.4.3 NP4GS3 Memory                        |     |

| 1.4.4 Distributed Software Model           |     |

| 1.5 NP4GS3 Structure                       |     |

| 1.6 NP4GS3 Data Flow                       | 26  |

| 2. Physical Description                    | 29  |

| 2.1 Pin Information                        | 30  |

| 2.1.1 PLL Filter Circuit                   |     |

| 2.1.2 Thermal I/O Usage                    |     |

| 2.1.2.1 Temperature Calculation            |     |

| 2.1.2.2 Measurement Calibration            |     |

| 2.2 Mechanical Specifications              |     |

| 2.3 Signal Pin Lists                       |     |

| 2.4 IEEE 1149 (JTAG) Compliance            |     |

| 2.4.1 Statement of JTAG Compliance         |     |

| 2.4.3 JTAG Compliance Mode                 |     |

| 2.4.4 Brief Overview of JTAG Instructions  |     |

| 3. PMM Overview                            | Q?  |

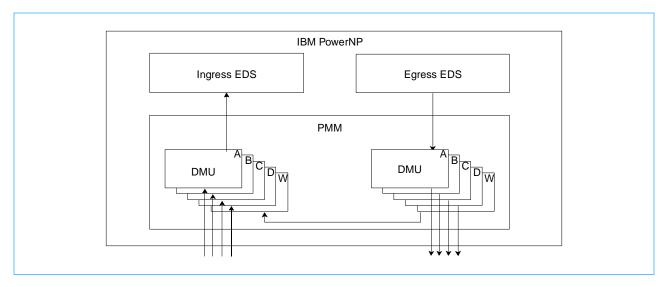

| 3.1 Ethernet Overview                      |     |

| 3.2 POS Overview                           |     |

| 3.2.1 POS Counters                         |     |

| 3.2.1.1 Long Frames                        |     |

| <b>C</b>                                   |     |

| 4. Ingress Enqueuer / Dequeuer / Scheduler | 111 |

| 4.1 Overview                               | 111 |

| 4.2 Ingress Flow Control                   |     |

| 4.2.1 Overview                             | 112 |

| IBM PowerNP                               | Preliminar     |

|-------------------------------------------|----------------|

| 4.2.2 Flow Control Hardware Facilities    | 112            |

| 4.2.3 Hardware Function                   | 114            |

| 4.2.3.1 Exponentially Weighted Moving Ave | rage (EWMA)114 |

| 4.2.3.2 Flow Control Hardware Actions     | 114            |

| 5. Switch Interface                       | 115            |

| 5.1 Overview                              | 115            |

|                                           | 117            |

|                                           | 117            |

|                                           | 119            |

|                                           | 121            |

|                                           | 121            |

|                                           |                |

|                                           | ell            |

|                                           | ss123          |

|                                           | 124            |

| • • • • • • • • • • • • • • • • • • • •   | 124            |

|                                           |                |

|                                           | ess Idle Cell  |

|                                           | 127            |

| •                                         | 127            |

| 3.7 Egress Switch Data Mover (E-3DM)      | 121            |

| 6. Egress Enqueuer / Dequeuer / Schedule  | r 120          |

|                                           |                |

|                                           | 129            |

| · ·                                       | 130            |

| •                                         | 132            |

|                                           | 136            |

|                                           | 136            |

|                                           | 136            |

| •                                         | 137            |

|                                           | 137            |

| ,                                         | 137            |

|                                           |                |

|                                           | rage (EWMA)139 |

|                                           | 139 (EVNNA)    |

|                                           | 141            |

| •                                         | 141            |

|                                           |                |

|                                           |                |

| <u> </u>                                  |                |

|                                           |                |

| <u> </u>                                  |                |

|                                           | 147            |

| 5                                         |                |

| 7. Embedded Processor Complex             | 149            |

| 7.1 Overview                              | 149            |

| 7.1.1 Thread Types                        | 152            |

|                                           |                |

IBM PowerNP

### **Preliminary**

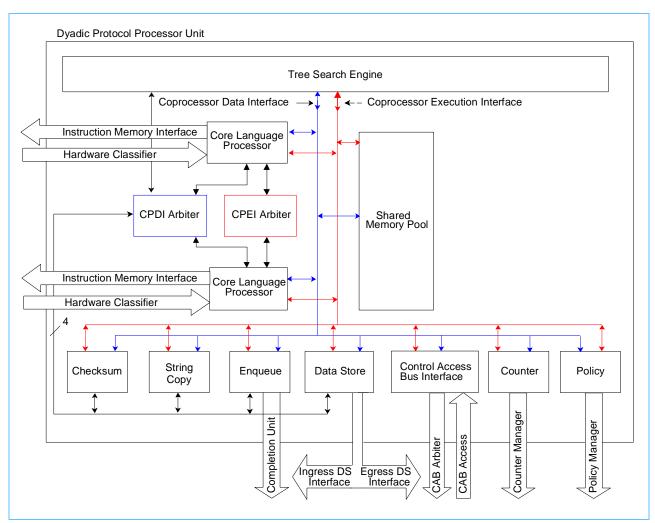

| 7.2 Dyadic Protocol Processor Unit (DPPU)           | 153 |

|-----------------------------------------------------|-----|

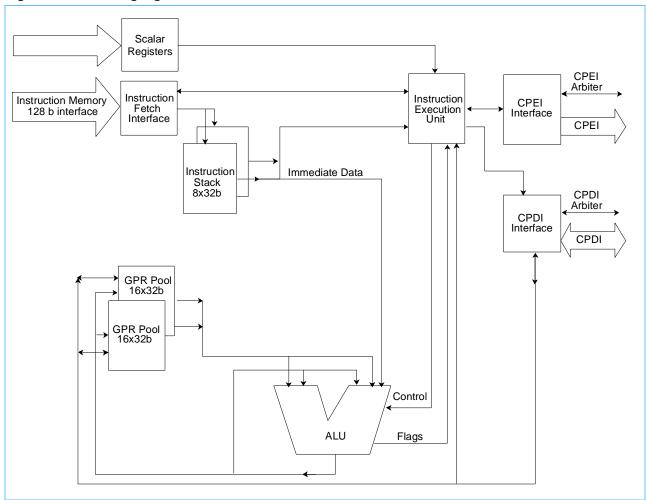

| 7.2.1 Core Language Processor (CLP)                 |     |

| 7.2.1.1 Core Language Processor Address Map         |     |

| 7.2.2 DPPU Coprocessors                             |     |

| 7.2.3 The Data Store Coprocessor                    |     |

| 7.2.3.1 Data Store Coprocessor Address Map          |     |

| 7.2.3.2 Data Store Coprocessor Commands             |     |

| 7.2.4 The Control Access Bus (CAB) Coprocessor      |     |

| 7.2.4.1 CAB Coprocessor Address Map                 |     |

| 7.2.4.2 CAB Access to NP4GS3 Structures             |     |

| 7.2.4.3 CAB Coprocessor Commands                    | 175 |

| 7.2.5 Enqueue Coprocessor                           | 176 |

| 7.2.5.1 Enqueue Coprocessor Address Map             | 177 |

| 7.2.5.2 Enqueue Coprocessor Commands                | 183 |

| 7.2.6 Checksum Coprocessor                          | 188 |

| 7.2.6.1 Checksum Coprocessor Address Map            | 188 |

| 7.2.6.2 Checksum Coprocessor Commands               | 189 |

| 7.2.7 String Copy Coprocessor                       | 192 |

| 7.2.7.1 String Copy Coprocessor Address Map         | 193 |

| 7.2.7.2 String Copy Coprocessor Commands            | 193 |

| 7.2.8 Policy Coprocessor                            | 194 |

| 7.2.8.1 Policy Coprocessor Address Map              |     |

| 7.2.8.2 Policy Coprocessor Commands                 | 194 |

| 7.2.9 Counter Coprocessor                           |     |

| 7.2.9.1 Counter Coprocessor Address Map             |     |

| 7.2.9.2 Counter Coprocessor Commands                |     |

| 7.2.10 Shared Memory Pool                           | 198 |

| 7.3 Interrupts and Timers                           |     |

| 7.3.1 Interrupts                                    |     |

| 7.3.1.1 Interrupt Vector Registers                  |     |

| 7.3.1.2 Interrupt Mask Registers                    |     |

| 7.3.1.3 Interrupt Target Registers                  |     |

| 7.3.1.4 Software Interrupt Registers                |     |

| 7.3.2 Timers                                        |     |

| 7.3.2.1 Timer Interrupt Counters                    |     |

| 7.3.3 Port Configuration Memory                     |     |

| 7.3.3.1 Port Configuration Memory Index Definition  |     |

| 7.3.4 Port Configuration Memory Contents Definition |     |

| 7.4 Hardware Classifier                             |     |

| 7.4.1 Ingress Classification                        |     |

| 7.4.1.1 Ingress Classification Input                |     |

| 7.4.1.2 Ingress Classification Output               |     |

| 7.4.2 Egress Classification                         |     |

| 7.4.2.1 Egress Classification Input                 |     |

| 7.4.2.2 Egress Classification Output                |     |

| 7.5 Policy Manager                                  | 208 |

| 7.6 Counter Manager                                 | 211 |

| 7.6.1 Counter Manager Usage                         | 213 |

| 8. Tree Search Engine                                | 219 |

|------------------------------------------------------|-----|

| 8.1 Overview                                         | 219 |

| 8.1.1 Addressing Control Store                       |     |

| 8.1.2 Control Store Use Restrictions                 |     |

| 8.1.3 Object Shapes                                  | 221 |

| 8.1.4 Illegal Memory Access                          |     |

| 8.1.5 Memory Range Checking                          |     |

| 8.2 Trees and Tree Searches                          |     |

| 8.2.1 Input Key and Color Register for FM and LPM Tr |     |

| 8.2.2 Input Key and Color Register for SMT Trees     |     |

| 8.2.3 Direct Table                                   |     |

| 8.2.3.1 Pattern Search Control Blocks (PSCB)         | 227 |

| 8.2.3.2 Leaves and Compare-at-End Operation          |     |

| 8.2.3.3 Cache                                        |     |

| 8.2.3.4 Cache Flag and NrPSCBs Registers             | 228 |

| 8.2.3.5 Cache Management                             | 228 |

| 8.2.3.6 Search Output                                | 229 |

| 8.2.4 Tree Search Algorithms                         | 229 |

| 8.2.4.1 FM Trees                                     | 229 |

| 8.2.4.2 LPM Trees                                    | 229 |

| 8.2.4.3 SMT Trees                                    |     |

| 8.2.4.4 Compare-at-End Operation                     | 230 |

| 8.2.4.5 Ropes                                        |     |

| 8.2.4.6 Aging                                        |     |

| 8.2.5 Tree Configuration and Initialization          |     |

| 8.2.5.1 The LUDefTable                               |     |

| 8.2.5.2 TSE Free Lists (TSE_FL)                      |     |

| 8.2.6 TSE Registers and Register Map                 |     |

| 8.2.7 TSE Instructions                               |     |

| 8.2.7.1 FM Tree Search (TS_FM)                       |     |

| 8.2.7.2 LPM Tree Search (TS_LPM)                     |     |

| 8.2.7.3 SMT Tree Search (TS_SMT)                     |     |

| 8.2.7.4 Memory Read (MRD)                            |     |

| 8.2.7.5 Memory Write (MWR)                           |     |

| 8.2.7.6 Hash Key (HK)                                |     |

| 8.2.7.7 Read LUDefTable (RDLUDEF)                    |     |

| 8.2.7.8 Compare-at-End (COMPEND)                     |     |

| 8.2.8.1 Hash Key GTH (HK_GTH)                        |     |

| 8.2.8.2 Read LUDefTable GTH (RDLUDEF GTH) .          |     |

| 8.2.8.3 Tree Search Enqueue Free List (TSENQFL)      |     |

| 8.2.8.4 Tree Search Dequeue Free List (TSDQFL)       |     |

| 8.2.8.5 Read Current Leaf from Rope (RCLR)           |     |

| 8.2.8.6 Advance Rope with Optional Delete Leaf (A    |     |

| 8.2.8.7 Tree Leaf Insert Rope (TLIR)                 | •   |

| 8.2.8.8 Clear PSCB (CLRPSCB)                         |     |

| 8.2.8.9 Read PSCB (RDPSCB)                           |     |

| 8.2.8.10 Write PSCB (WRPSCB)                         |     |

| 8.2.8.11 Push PSCB (PUSHPSCB)                        |     |

| 8.2.8.12 Distinguish (DISTPOS)                       |     |

| 8.2.8.13 TSR0 Pattern (TSR0PAT)                      |     |

| , , , , , , , , , , , , , , , , , , , ,              |     |

### **Preliminary**

| Preliminary                                                                                                    | IBM PowerNP |

|----------------------------------------------------------------------------------------------------------------|-------------|

| 8.2.8.14 Pattern 2DTA (PAT2DTA)                                                                                | 255         |

| 8.2.9 Hash Functions                                                                                           |             |

| O. Carial/Davallal Manager Interfere                                                                           | 262         |

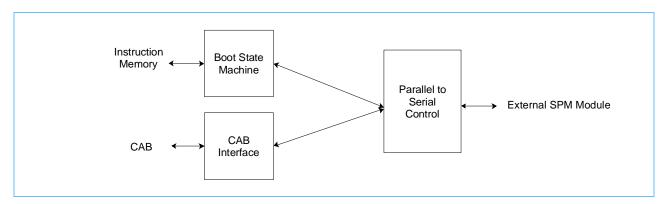

| 9. Serial/Parallel Manager Interface                                                                           |             |

| 9.1 SPM Interface Components                                                                                   |             |

| 9.2 SPM Interface Data Flow                                                                                    |             |

| 9.3 SPM Interface Protocol                                                                                     |             |

| 9.4 SPM CAB Address Space                                                                                      |             |

| 9.4.1 Byte Access Space                                                                                        |             |

| 9.4.2 Word Access Space                                                                                        |             |

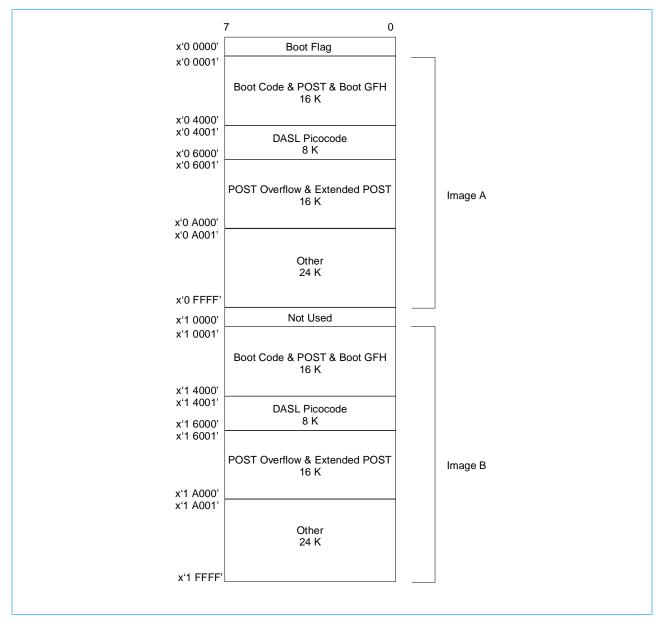

| 9.4.3 EEPROM Access Space                                                                                      |             |

| 9.4.3.1 EEPROM Byte Access                                                                                     |             |

| 9.4.3.2 EEPROM 2 Byte Access                                                                                   |             |

| 9.4.3.3 EEPROM 3 Byte Access                                                                                   |             |

| 9.4.3.4 EEPROM 4 Byte Access                                                                                   | 272         |

| 10. Embedded PowerPC™                                                                                          | 273         |

| 10.1 Description                                                                                               | 273         |

| 10.2 Processor Local Bus and Device Control Register B                                                         | uses274     |

| 10.3 Universal Interrupt Controller (UIC)                                                                      |             |

| 10.4 PCI/PLB Macro                                                                                             |             |

| 10.5 PLB Address Map                                                                                           |             |

| 10.6 CAB Address Map                                                                                           |             |

| •                                                                                                              |             |

| 10.7 CAB Interface Macro                                                                                       |             |

| 10.7.1 PowerPC CAB Address (PwrPC_CAB_Addr) Register                                                           |             |

| 10.7.2 PowerPC CAB Data (PwrPC_CAB_Data) Registe 10.7.3 PowerPC CAB Control (PwrPC_CAB_Cntl) Register          |             |

| 10.7.3 FOWEIPC CAB Control (PWIPC_CAB_Chil) Registrers 10.7.4 PowerPC CAB Status (PwrPC_CAB_Status) Registrers |             |

| 10.7.5 PCI Host CAB Address (Host_CAB_Addr) Registe                                                            |             |

| 10.7.6 PCI Host CAB Data (Host_CAB_Data) Register                                                              |             |

| 10.7.7 PCI Host CAB Control (Host_CAB_Cntl) Register                                                           |             |

| 10.7.8 PCI Host CAB Status (Host_CAB_Status) Register                                                          |             |

| 10.8 Mailbox Communications and DRAM Interface Macro                                                           |             |

| 10.8.1 Mailbox Communications Between PCI Host and I                                                           |             |

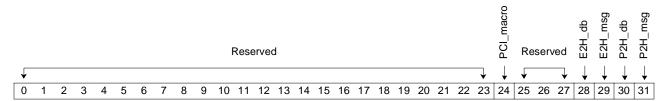

| 10.8.2 PCI Interrupt Status (PCI_Interr_Status) Register                                                       |             |

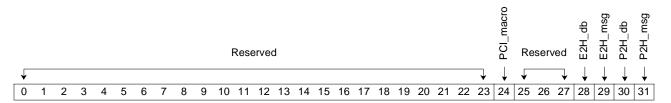

| 10.8.3 PCI Interrupt Enable (PCI_Interr_Ena) Register                                                          |             |

| 10.8.4 PowerPC to PCI Host Message Resource (P2H_N                                                             |             |

| 10.8.5 PowerPC to Host Message Address (P2H_Msg_A                                                              |             |

| 10.8.6 PowerPC to Host Doorbell (P2H_Doorbell) Regist                                                          | , •         |

| 10.8.7 Host to PowerPC Message Address (H2P_Msg_A                                                              |             |

| 10.8.8 Host to PowerPC Doorbell (H2P_Doorbell) Registe                                                         | , •         |

| 10.8.9 Mailbox Communications Between PowerPC and                                                              |             |

| 10.8.10 EPC to PowerPC Resource (E2P_Msg_Resourc                                                               |             |

| 10.8.11 EPC to PowerPC Message Address (E2P_Msg_                                                               |             |

| 10.8.12 EPC to PowerPC Doorbell (E2P_Doorbell) Regis                                                           | , -         |

| 10.8.13 EPC Interrupt Vector Register                                                                          |             |

| 10.8.14 EPC Interrupt Mask Register                                                                            | 305         |

| 10.8.15 PowerPC to EPC Message Address (P2E_Msg_                                                               |             |

| 10.8.16 PowerPC to EPC Doorbell (P2E_Doorbell) Regis                                                           |             |

| 10.8.17 Mailbox Communications Between PCI Host and                                                            | EPC309      |

| 10.8.18 EPC to PCI Host Resource (E2H_Msg_Resource) Register          |     |

|-----------------------------------------------------------------------|-----|

| 10.8.19 EPC to PCI Host Message Address (E2H_Msg_Addr) Register       |     |

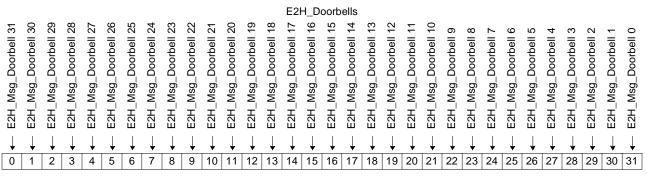

| 10.8.20 EPC to PCI Host Doorbell (E2H_Doorbell) Register              |     |

| 10.8.21 PCI Host to EPC Message Address (H2E_Msg_Addr) Register       |     |

| 10.8.22 PCI Host to EPC Doorbell (H2E_Doorbell) Register              |     |

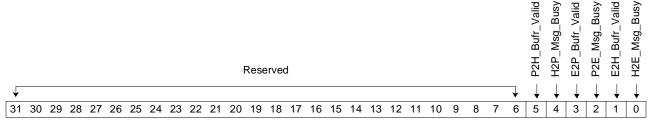

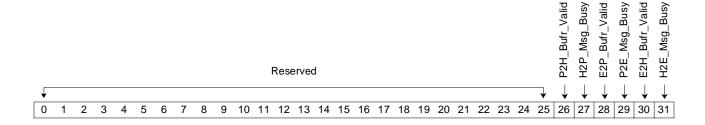

| 10.8.23 Message Status (Msg_Status) Register                          |     |

| 10.8.25 Slave Error Status Register (SESR)                            |     |

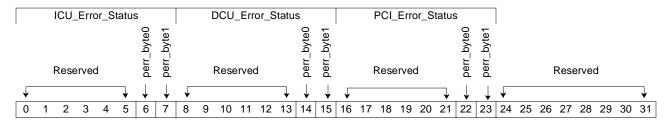

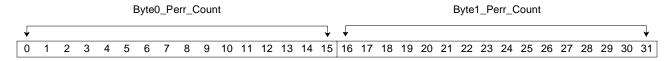

| 10.8.26 Parity Error Counter (Perr_Count) Register                    |     |

| 10.9 System Start-Up and Initialization                               |     |

| 10.9.1 NP4GS3 Resets                                                  |     |

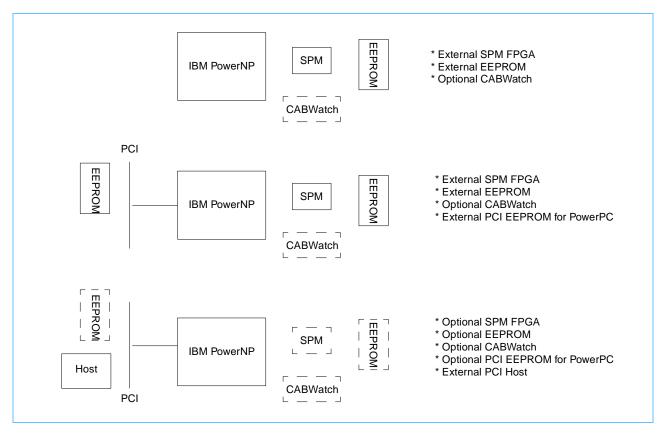

| 10.9.2 Systems Initialized by External PCI Host Processors            |     |

| 10.9.3 Systems with PCI Host Processors and Initialized by PowerPC    |     |

| 10.9.4 Systems Without PCI Host Processors and Initialized by PowerPC |     |

| 10.9.5 Systems Without PCI Interface Hardware and Initialized by EPC  | 326 |

| 11. Reset and Initialization                                          | 227 |

| 11.1 Overview                                                         | _   |

| 11.2 Step 1: Set I/Os                                                 |     |

| 11.3 Step 2: Reset the NP4GS3                                         |     |

| 11.4 Step 3: Boot                                                     |     |

| 11.4.1 Boot the Embedded Processor Complex (EPC)                      |     |

| 11.4.2 Boot the PowerPC                                               |     |

| 11.4.3 Boot Summary                                                   |     |

| 11.5 Step 4: Setup 1                                                  | 330 |

| 11.6 Step 5: Diagnostics 1                                            | 331 |

| 11.7 Step 6: Setup 2                                                  | 332 |

| 11.8 Step 7: Hardware Initialization                                  | 332 |

| 11.9 Step 8: Diagnostics 2                                            |     |

| 11.10 Step 9: Operational                                             |     |

| 11.11 Step 10: Configure                                              |     |

| 11.12 Step 11: Initialization Complete                                |     |

| 40. Dobug Fooilide                                                    | 227 |

| 12. Debug Facilities                                                  |     |

| 12.1 Single Step                                                      |     |

| 12.1.2 Break Points                                                   |     |

| 12.1.3 CAB Accessible Registers                                       |     |

| 12.2 RISCWatch                                                        |     |

|                                                                       |     |

| 13. IBM PowerNP Configuration                                         |     |

| 13.1 Memory Configuration                                             |     |

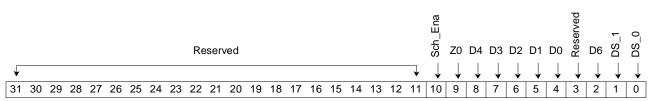

| 13.1.1 Memory Configuration Register (Memory_Config)                  |     |

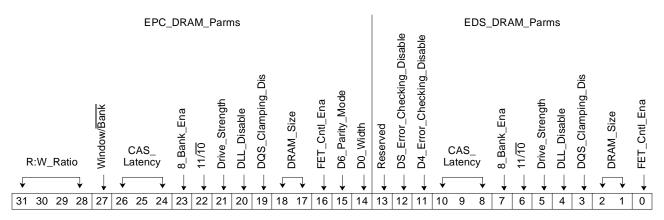

| 13.1.2 DRAM Parameter Register (DRAM_Parm)                            |     |

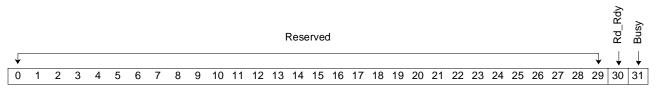

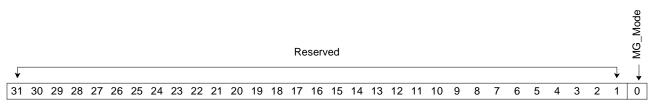

| 13.2 Master Grant Mode Register (MG_Mode)                             |     |

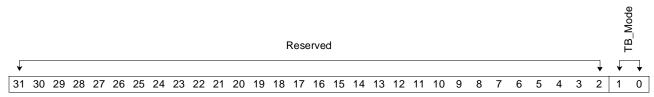

| 13.3 TB Mode Register (TB_Mode)                                       |     |

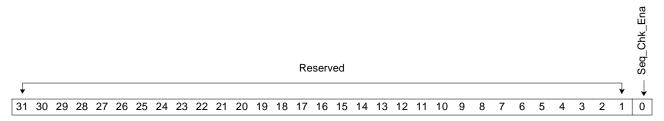

| 13.4 Egress Reassembly Sequence Check Register (E_Reassembly_Seq_Ck)  |     |

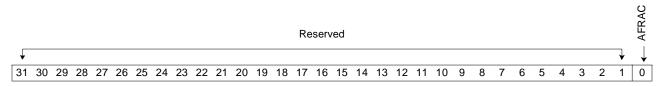

| 13.5 Aborted Frame Reassembly Action Control Register (AFRAC)         | 347 |

IBM PowerNP

### **Preliminary**

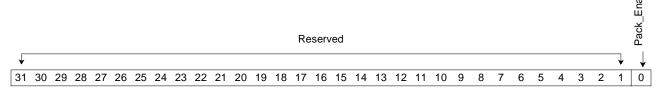

| 13.6 Packing Control Register (Pack_Ctrl)                                    |     |

|------------------------------------------------------------------------------|-----|

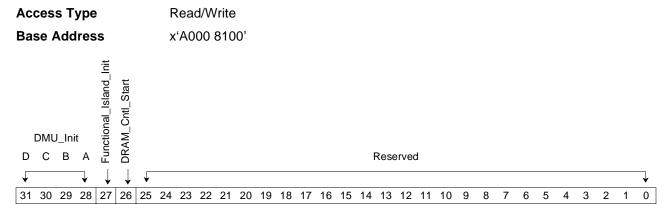

| 13.7 Initialization Control Registers                                        | 349 |

| 13.7.1 Initialization Register (Init)                                        |     |

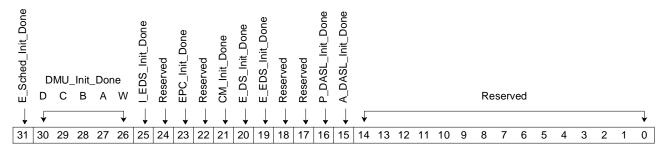

| 13.7.2 Initialization Done Register (Init_Done)                              | 350 |

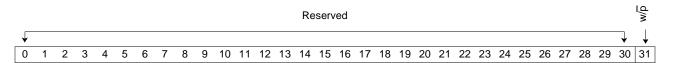

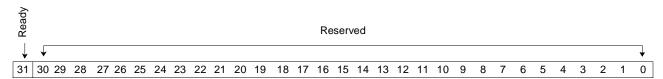

| 13.8 Network Processor Ready Register (NPR_Ready)                            | 351 |

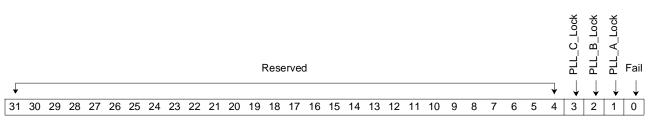

| 13.9 Phase Locked Loop Fail Register (PLL_Lock_Fail)                         | 352 |

| 13.10 Software Controlled Reset Register (Soft_Reset)                        | 353 |

| 13.11 Ingress Free Queue Threshold Configuration                             |     |

| 13.11.1 BCB_FQ Threshold Registers                                           |     |

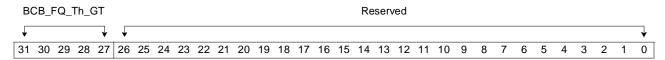

| 13.11.2 BCB_FQ Threshold for Guided Traffic (BCB_FQ_Th_GT)                   |     |

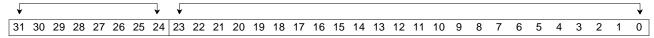

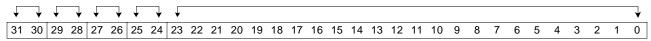

| 13.11.3 BCB_FQ_Threshold_0 / _1 / _2 Registers (BCB_FQ_Th_0/_1/_2)           |     |

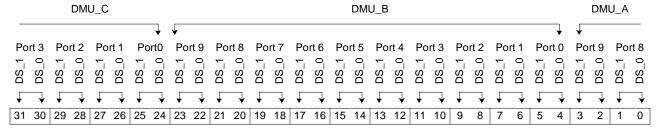

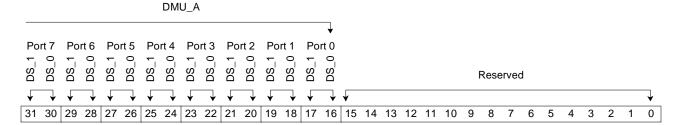

| 13.12 Ingress Target DMU Data Storage Map Register (I_TDMU_DSU)              |     |

| 13.13 Embedded Processor Complex Configuration                               |     |

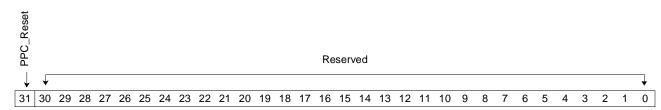

| 13.13.1 PowerPC Core Reset Register (PowerPC_Reset)                          |     |

| 13.13.2 PowerPC Boot Redirection Instruction Registers (Boot_Redir_Inst)     |     |

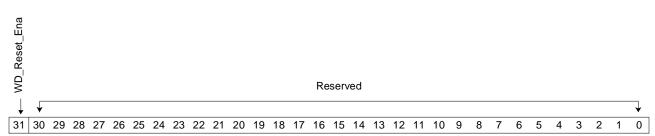

| 13.13.3 Watch Dog Reset Enable Register (WD_Reset_Ena)                       |     |

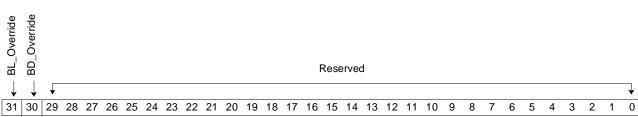

| 13.13.4 Boot Override Register (Boot_Override)                               |     |

| 13.13.5 Thread Enable Register (Thread_Enable)                               |     |

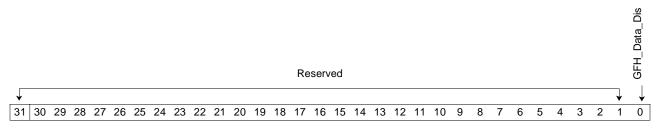

| 13.13.6 GFH Data Disable Register (GFH_Data_Dis)                             |     |

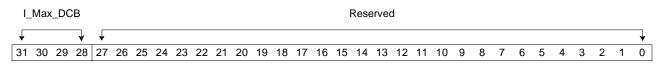

| 13.13.7 Ingress Maximum DCB Entries (I_Max_DCB)                              |     |

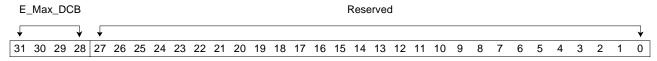

| 13.13.8 Egress Maximum DCB Entries (E_Max_DCB)                               |     |

| 13.13.9 My Target Blade Address Register (My_TB)                             |     |

| 13.13.10 Local Target Blade Vector Register (Local_TB_Vector)                |     |

| 13.13.11 Local MCTarget Blade Vector Register (Local_MC_TB_Max)              | 367 |

| 13.14 Flow Control Structures                                                | 368 |

| 13.14.1 Ingress Flow Control Hardware Structures                             | 368 |

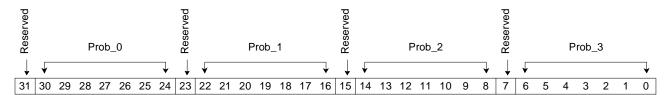

| 13.14.1.1 Ingress Transmit Probability Memory Register (I_Tx_Prob_Mem)       |     |

| 13.14.1.2 Ingress Pseudo-Random Number Register (I_Rand_Num)                 |     |

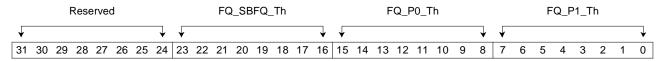

| 13.14.1.3 Free Queue Thresholds Register (FQ_Th)                             |     |

| 13.14.2 Egress Flow Control Structures                                       |     |

| 13.14.2.1 Egress Transmit Probability Memory (E_Tx_Prob_Mem) Register        |     |

| 13.14.2.2 Egress Pseudo-Random Number (E_Rand_Num)                           |     |

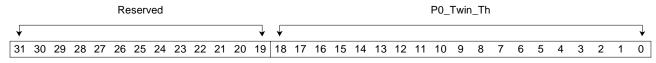

| 13.14.2.3 P0 Twin Count Threshold (P0_Twin_Th)                               |     |

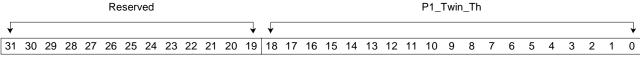

| 13.14.2.4 P1 Twin Count Threshold (P1_Twin_Th)                               |     |

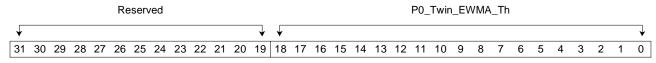

| 13.14.2.5 Egress P0 Twin Count EWMA Threshold Register (E_P0_Twin_EWMA_Th)   |     |

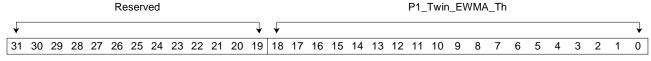

| 13.14.2.6 Egress P1 Twin Count EWMA Threshold Register (E_P1_Twin_EWMA_Th)   |     |

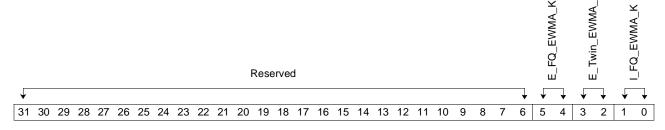

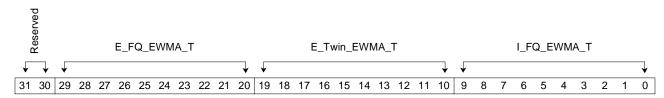

| 13.14.3 Exponentially Weighted Moving Average Constant (K) Register (EWMA_K) |     |

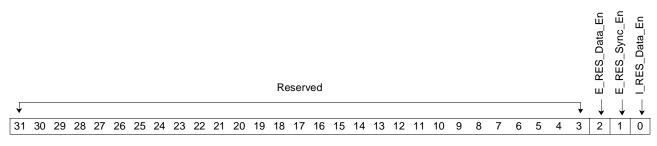

| 13.14.5 Remote Egress Status Bus Configuration Enables (RES_Data_Cnf)        |     |

|                                                                              |     |

| 13.15 Target Port Data Storage Map (TP_DS_MAP) Register                      |     |

| 13.16 Egress SDM Stack Threshold Register (E_SDM_Stack_Th)                   |     |

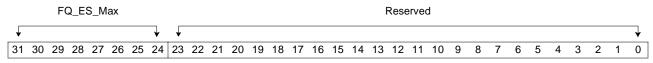

| 13.17 Free Queue Extended Stack Maximum Size (FQ_ES_Max) Register            |     |

| 13.18 Egress Free Queue Thresholds                                           | 385 |

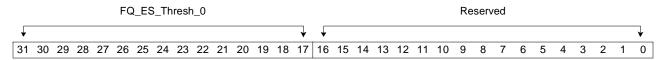

| 13.18.1 FQ_ES_Threshold_0 Register (FQ_ES_Th_0)                              |     |

| 13.18.2 FQ_ES_Threshold_1 Register (FQ_ES_Th_1)                              |     |

| 13.18.3 FQ_ES_Threshold_2 Register (FQ_ES_Th_2)                              |     |

| 13.19 Discard Flow QCB Register (Discard_QCB)                                |     |

| 13.20 Frame Control Block FQ Size Register (FCB_FQ_Max)                      |     |

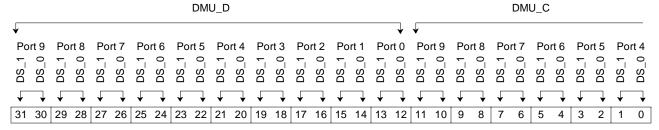

| 13.21 Data Mover Unit (DMU) Configuration                                    |     |

| 13.22 QD Accuracy Register (QD_Acc)                                          | 394 |

| 40.00 Perlat Control Perlate (POC.044)                            | 005 |

|-------------------------------------------------------------------|-----|

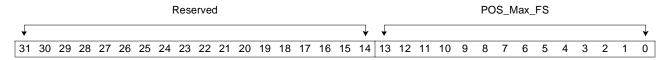

| 13.23 Packet Over SONET Control Register (POS_Ctrl)               |     |

| 13.24 Packet Over SONET Maximum Frame Size (POS_Max_FS)           |     |

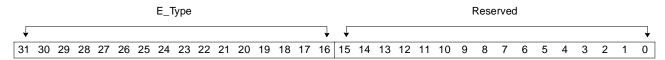

| 13.25 Ethernet Encapsulation Type Register for Control (E_Type_C) | 397 |

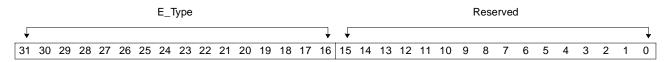

| 13.26 Ethernet Encapsulation Type Register for Data (E_Type_D)    |     |

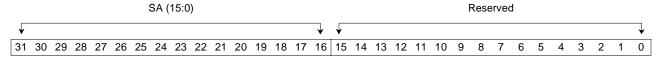

| 13.27 Source Address Array (SA_Array)                             | 399 |

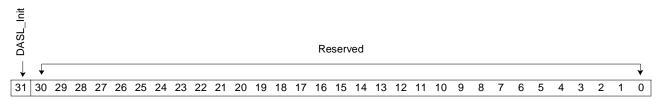

| 13.28 DASL Initialization and Configuration                       |     |

| 13.28.1 DASL Configuration Register (DASL_Config)                 |     |

| 13.28.2 DASL Bypass and Wrap Register (DASL_Bypass_Wrap)          |     |

| 13.28.3 DASL Start Register (DASL_Start)                          |     |

| 14. Electrical and Thermal Specifications                         | 405 |

| 14.1 Driver Specifications                                        |     |

| 14.2 Receiver Specifications                                      | 428 |

| 14.3 Other Driver and Receiver Specifications                     | 430 |

| 15. Glossary of Terms and Abbreviations                           | 433 |

| Revision Log                                                      | 443 |

| List of Tables                                                                                                                                              |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1: I/O Signal Pin Summary                                                                                                                             | 31  |

| Table 2: IBM 28.4 Gbps Packet Routing Switch Interface Pins                                                                                                 |     |

| Table 3: Flow Control Pins                                                                                                                                  |     |

| Table 4: Z0 ZBT SRAM Interface Pins                                                                                                                         | 33  |

| Table 5: Z1 ZBT SRAM Interface Pins                                                                                                                         | 34  |

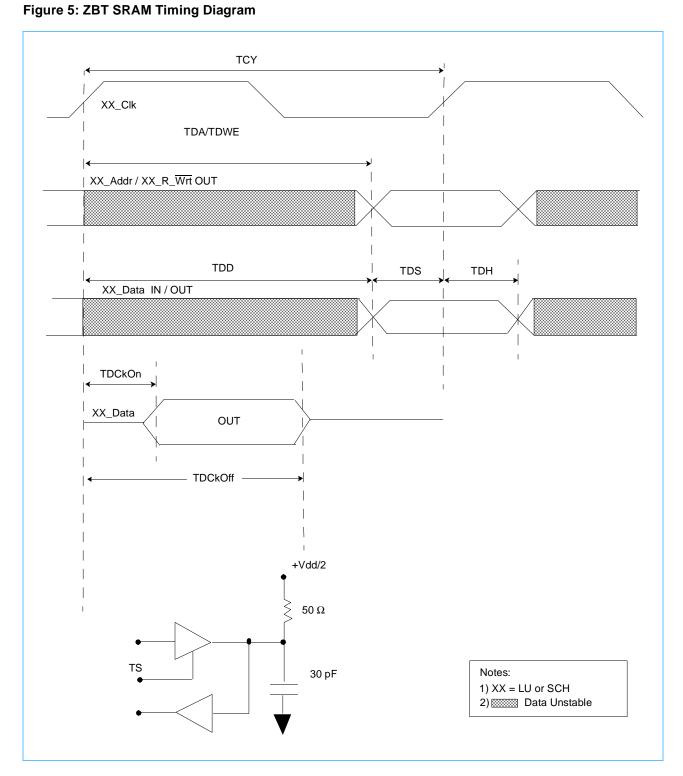

| Table 6: ZBT SRAM Timing Diagram Legend                                                                                                                     | 36  |

| Table 7: D3, D2, and D1 Memory Pins                                                                                                                         |     |

| Table 8: D0 Memory Pins                                                                                                                                     | 37  |

| Table 9: D4_0 / D4_1 Memory Pins                                                                                                                            |     |

| Table 10: D6_5 / D6_4 / D6_3 / D6_2 / D6_1 / D6_0 Memory Pins                                                                                               | 39  |

| Table 11: DS1 and DS0 Pins                                                                                                                                  |     |

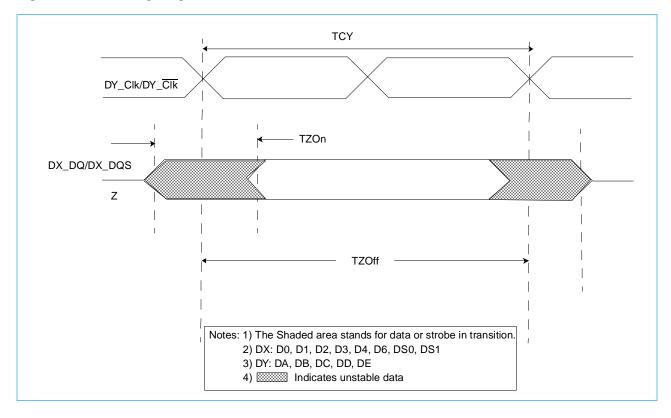

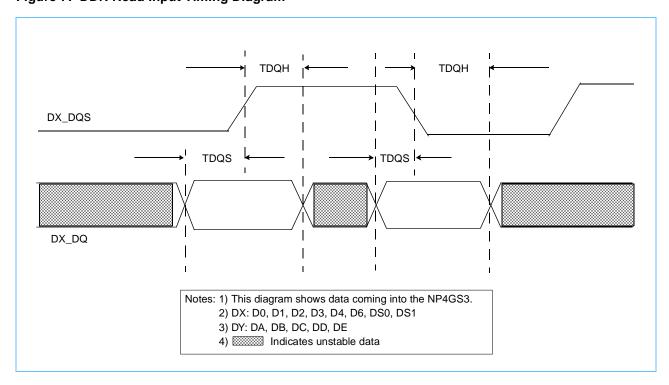

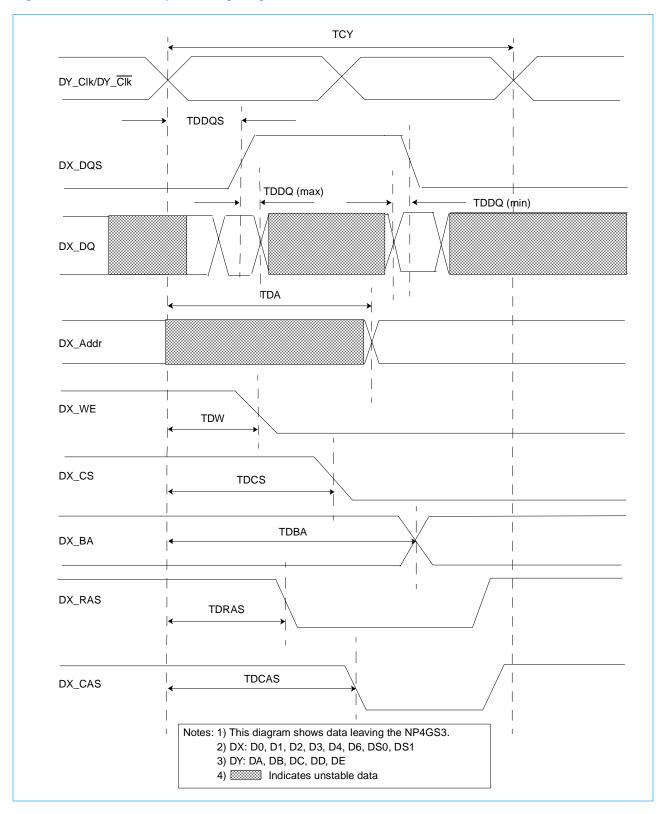

| Table 12: DDR Timing Diagrams Legend                                                                                                                        | 43  |

| Table 13: PMM Interface Pins                                                                                                                                |     |

| Table 14: PMM Interface Pin Multiplexing                                                                                                                    |     |

| Table 15: Parallel Data Bit to 8B/10B Position Mapping (TBI Interface)                                                                                      |     |

| Table 16: PMM Interface Pins POS32 Mode                                                                                                                     |     |

| Table 17: PMM Interface Signals: GMII Mode                                                                                                                  | 48  |

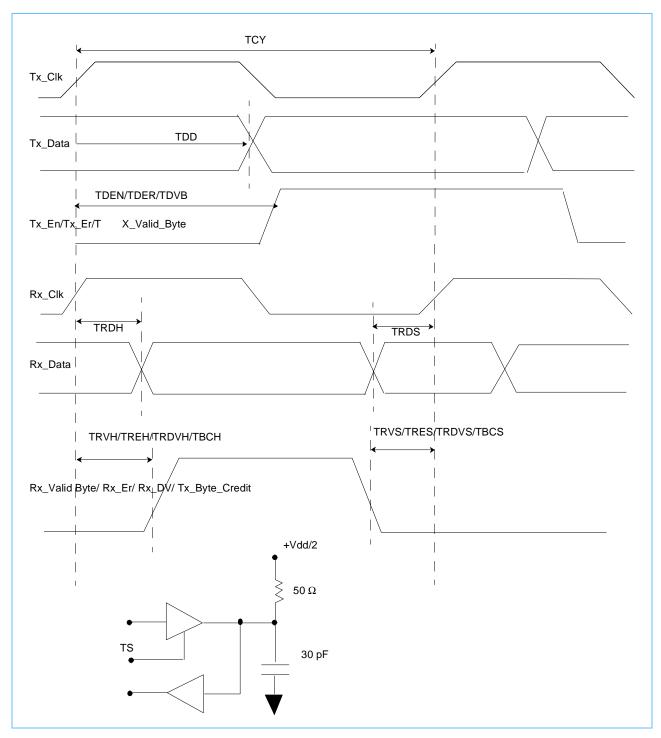

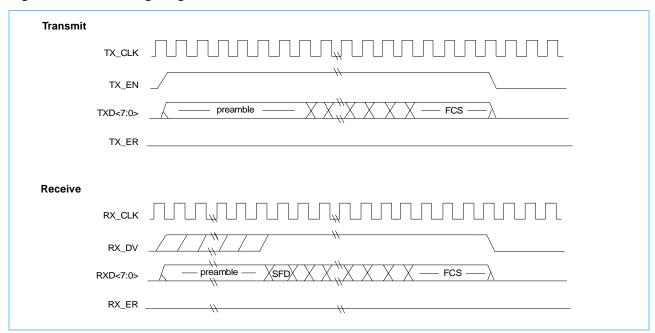

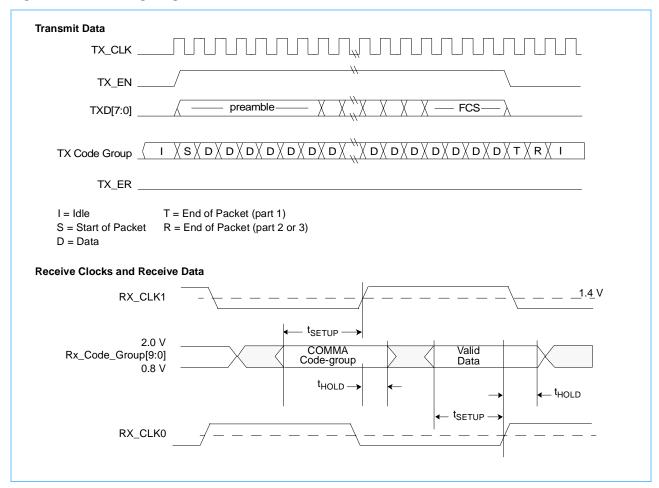

| Table 18: GMII Timing Diagram Legend                                                                                                                        | 50  |

| Table 19: PMM Interface Pins: TBI Mode                                                                                                                      |     |

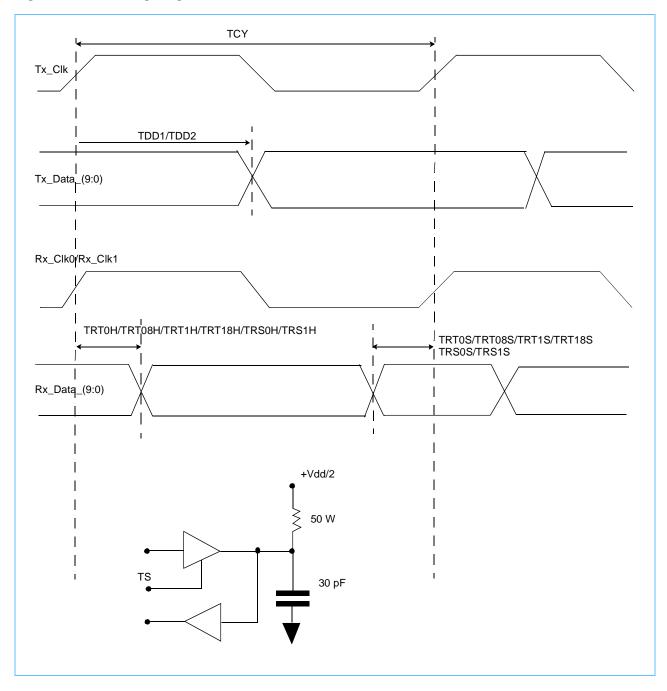

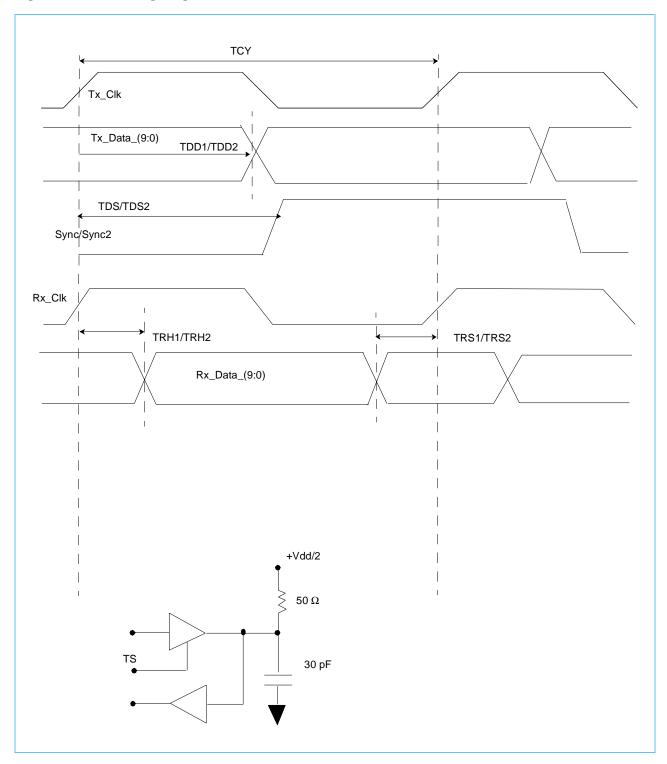

| Table 20: TBI Timing Diagram Legend                                                                                                                         |     |

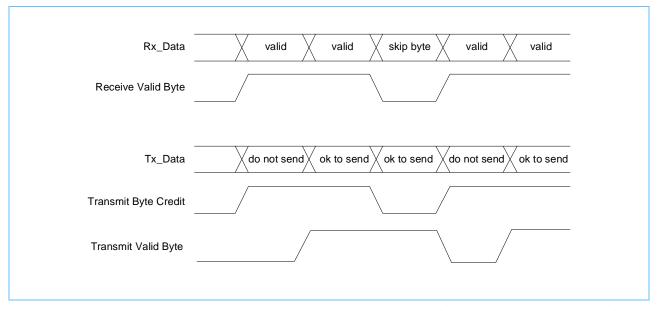

| Table 21: PMM Interface Pins: SMII Mode                                                                                                                     |     |

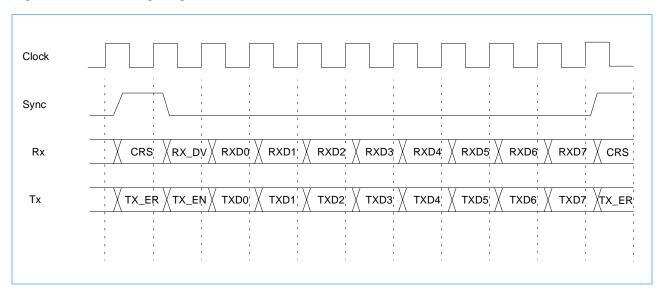

| Table 22: SMII Timing Diagram Legend                                                                                                                        |     |

| Table 23: POS Signals                                                                                                                                       |     |

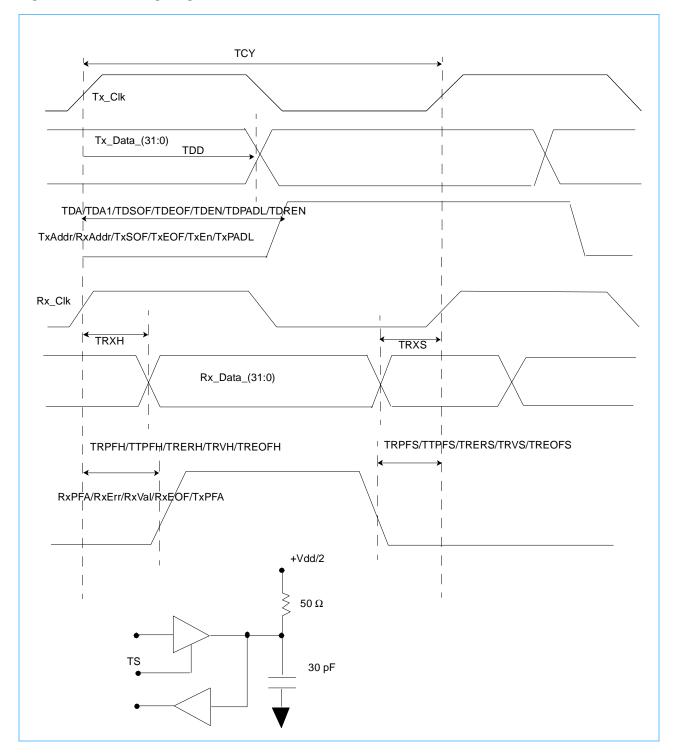

| Table 24: POS Timing Diagram Legend                                                                                                                         |     |

| Table 25: PCI Interface Pins                                                                                                                                |     |

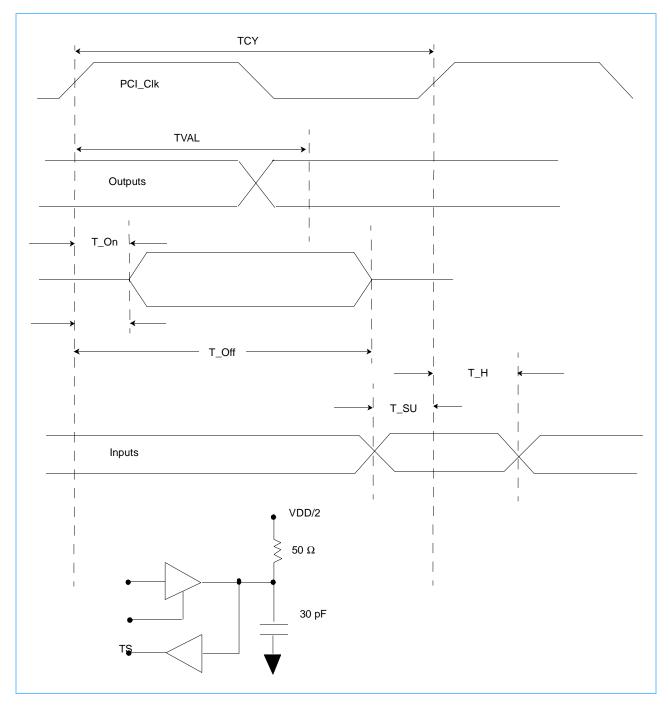

| Table 26: PCI Timing Diagram Legend                                                                                                                         |     |

| Table 27: Management Bus Pins                                                                                                                               |     |

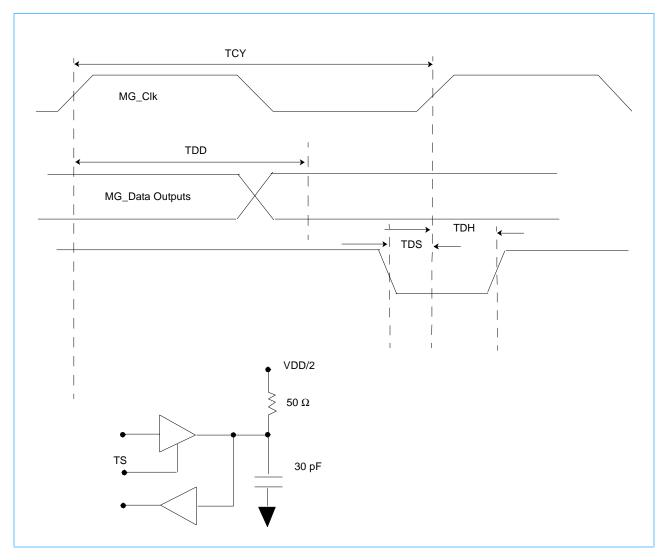

| Table 28: Management Bus Timing Diagram Legend                                                                                                              |     |

| Table 29: Miscellaneous Pins                                                                                                                                |     |

| Table 30: Signals Requiring Pull-Up or Pull-Down                                                                                                            |     |

| Table 31: Mechanical Specifications                                                                                                                         |     |

| Table 32: Complete Signal Pin Listing by Signal Name                                                                                                        |     |

| Table 33: Complete Signal Pin Listing by Grid Position                                                                                                      |     |

| Table 34: JTAG Compliance-Enable Inputs                                                                                                                     |     |

| Table 35: Implemented JTAG Public Instructions                                                                                                              |     |

| Table 36: Ingress Ethernet Counters                                                                                                                         |     |

| Table 37: Egress Ethernet Counters                                                                                                                          |     |

| Table 38: Ethernet Support                                                                                                                                  |     |

| Table 39: Receive Counter RAM Addresses for Ingress POS MAC                                                                                                 |     |

| Table 40: Transmit Counter RAM Addresses for Egress POS MAC                                                                                                 |     |

| Table 41: POS Support                                                                                                                                       |     |

|                                                                                                                                                             |     |

| Table 43: Cell Header Fields                                                                                                                                |     |

| Table 44: Frame Header Fields                                                                                                                               |     |

| Table 45: Idle Cell Format Transmitted to the Switch Interface                                                                                              |     |

| Table 46: Switch Data Cell Format                                                                                                                           |     |

| Table 47: Receive Cell Header Byte Ho for an Idle Cell                                                                                                      |     |

| Table 48: Idle Cell Format Received From the Switch Interface - 16-blade Mode Table 49: Idle Cell Format Received From the Switch Interface - 64-blade Mode |     |

| Table 49: Idie Cell Format Received From the Switch Interface - 64-blade Mode                                                                               |     |

| Table 30. List of flow Control Pataware Facilities                                                                                                          | 136 |

| IBM PowerNP                                              | Preliminary |

|----------------------------------------------------------|-------------|

| Table 51: Flow Queue Parameters                          | 141         |

| Table 52: Valid Combinations of Scheduler Parameters     | 143         |

| Table 53: Configure a Flow QCB                           | 147         |

| Table 54: Core Language Processor Address Map            | 156         |

| Table 55: Coprocessor Instruction Format                 | 158         |

| Table 56: Data Store Coprocessor Address Map             | 159         |

| Table 57: Ingress DataPool Byte Address Definitions      |             |

| Table 58: Egress Frames DataPool Quadword Addresses      | 164         |

| Table 59: DataPool Byte Addressing with Cell Header Skip |             |

| Table 60: Number of Frame-bytes in the DataPool          | 165         |

| Table 61: Data Store Coprocessor Commands Summary        | 167         |

| Table 62: WREDS Input                                    | 167         |

| Table 63: WREDS Output                                   | 168         |

| Table 64: RDEDS Input                                    |             |

| Table 65: RDEDS Output                                   | 168         |

| Table 66: WRIDS Input                                    | 169         |

| Table 67: WRIDS Output                                   | 169         |

| Table 68: RDIDS Input                                    |             |

| Table 69: RDIDS Output                                   |             |

| Table 70: RDMOREI Input                                  |             |

| Table 71: RDMOREI Output                                 |             |

| Table 72: RDMOREE Input                                  |             |

| Table 73: RDMOREE Output                                 |             |

| Table 74: EDIRTY Output                                  |             |

| Table 75: IDIRTY Inputs                                  |             |

| Table 76: IDIRTY Output                                  |             |

| Table 77: LEASETWIN Output                               |             |

| Table 78: CAB Coprocessor Address Map                    |             |

| Table 79: CAB Address Field Definitions                  |             |

| Table 80: CAB Address, Functional Island Encoding        |             |

| Table 81: CAB Coprocessor Commands Summary               |             |

| Table 82: CABARB Input                                   |             |

| Table 83: CABACCESS Input                                | 176         |

| Table 84: CABACCESS Output                               |             |

| Table 85: Enqueue Coprocessor Address Map                |             |

| Table 86: Ingress FCBPage Description                    |             |

| Table 87: Egress FCBPage Description                     |             |

| Table 88: Enqueue Coprocessor Commands Summary           |             |

| Table 89: ENQE Target Queues                             |             |

| Table 90: Egress Target Queue Selection Coding           |             |

| Table 91: Egress Target Queue Parameters                 |             |

| Table 92: Type Field for Discard Queue                   |             |

| Table 93: ENQE Command Input                             |             |

| Table 94: Egress Queue Class Definitions                 |             |

| Table 95: ENQI Target Queues                             |             |

| Table 96: Ingress Target Queue Selection Coding          |             |

| Table 97: Ingress Target Queue FCBPage Parameters        |             |

| Table 98: ENQI Command Input                             |             |

| Table 99: Ingress-Queue Class Definition                 |             |

| Table 100: ENQCLR Command Input                          |             |

| Table 101: ENQCLR Output                                 |             |

| Table 102: Checksum Coprocessor Address Map              |             |

| Table 103: Checksum Coprocessor Commands Summary                                     | 189 |

|--------------------------------------------------------------------------------------|-----|

| Table 104: GENGEN/GENGENX Command Inputs                                             |     |

| Table 105: GENGEN/GENGENX/GENIP/GENIPX Command Outputs                               |     |

| Table 106: GENIP/GENIPX Command Inputs                                               |     |

| Table 107: CHKGEN/CHKGENX Command Inputs                                             |     |

| Table 108: CHKGEN/CHKGENX/CHKIP/CHKIPX Command Outputs                               |     |

| Table 109: CHKIP/CHKIPX Command Inputs                                               |     |

| Table 110: String Copy Coprocessor Address Map                                       |     |

| Table 111: String Copy Coprocessor Commands Summary                                  |     |

| Table 112: StrCopy Command Input                                                     |     |

| Table 113: StrCopy Command Output                                                    |     |

| Table 114: Policy Coprocessor Address Map                                            |     |

| Table 115: Policy Coprocessor Commands Summary                                       | 194 |

| Table 116: PolAccess Input                                                           | 195 |

| Table 117: PolAccess Output                                                          | 195 |

| Table 118: Counter Coprocessor Address Map                                           | 195 |

| Table 119: Counter Coprocessor Commands Summary                                      | 196 |

| Table 120: Ctrinc Input                                                              | 196 |

| Table 121: CtrAdd Input                                                              | 197 |

| Table 122: CtrRd/CtrRdClr Input                                                      | 197 |

| Table 123: CtrRd/CtrRdClr Output                                                     |     |

| Table 124: CtrWr15_0/CtrWr31_16 Input                                                | 198 |

| Table 125: Shared Memory Pool                                                        |     |

| Table 126: Port Configuration Memory Index                                           | 200 |

| Table 127: Relationship Between SP Field, Queue, and Port Configuration Memory Index | 201 |

| Table 128: Port Configuration Memory Content                                         | 201 |

| Table 129: Protocol Identifiers                                                      | 203 |

| Table 130: HCCIA Table                                                               |     |

| Table 131: Protocol Identifiers for Frame Encapsulation Types                        | 205 |

| Table 132: General Purpose Register Bit Definitions for Ingress Classification Flags | 205 |

| Table 133: Flow Control Information Values                                           |     |

| Table 134: HCCIA Index Definition                                                    |     |

| Table 135: PolCB Field Definitions                                                   |     |

| Table 136: Counter Manager Components                                                |     |

| Table 137: Counter Types                                                             |     |

| Table 138: Counter Actions                                                           |     |

| Table 139: Counter Definition Entry Format                                           |     |

| Table 140: Counter Manager Passed Parameters                                         |     |

| Table 141: Control Store Address Mapping for TSE References                          |     |

| Table 142: CS Address Map and Use                                                    |     |

| Table 143: DTEntry, PSCB, and Leaf Shaping                                           |     |

| Table 144: Height, Width, and Offset Restrictions for TSE Objects                    |     |

| Table 145: FM and LPM Tree Fixed Leaf Formats                                        |     |

| Table 146: SMT Tree Fixed Leaf Formats                                               |     |

| Table 147: Search Input Parameters                                                   |     |

| Table 148: Cache Status Registers                                                    |     |

| Table 149: Search Output Parameters                                                  |     |

| Table 150: DTEntry and PSCBLine Formats                                              |     |

| Table 151: LPM DTEntry and PSCBLine Formats                                          |     |

| Table 152: NLASMT Field Format                                                       |     |

| Table 153: CompDefTable Entry Format                                                 |     |

| Table 154: LUDefTable Rope Parameters                                                | 232 |

| IBM PowerNP                                         | Preliminar |

|-----------------------------------------------------|------------|

| Table 155: NLARope Field Format                     | 233        |

| Table 156: LUDefTable Entry Definitions             |            |

| Table 157: Free List Entry Definition               | 235        |

| Table 158: TSE Scalar Registers for GTH Only        | 236        |

| Table 159: TSE Array Registers for All GxH          | 237        |

| Table 160: TSE Registers for GTH (Tree Management)  | 237        |

| Table 161: TSE Scalar Registers for GDH and GTH     |            |

| Table 162: PSCB Register Format                     | 238        |

| Table 163: TSE GTH Indirect Registers               | 238        |

| Table 164: Address Map for PSCB0-2 Registers in GTH | 239        |

| Table 165: General TSE Instructions                 |            |

| Table 166: FM Tree Search Input Operands            | 240        |

| Table 167: FM Tree Search Results (TSR) Output      | 241        |

| Table 168: LPM Tree Search Input Operands           | 241        |

| Table 169: LPM Tree Search Results (TSR) Output     | 242        |

| Table 170: SMT Tree Search Input Operands           | 242        |

| Table 171: SMT Tree Search Results (TSR) Output     | 243        |

| Table 172: Memory Read Input Operands               |            |

| Table 173: Memory Read Output Results               | 243        |

| Table 174: Memory Write Input Operands              | 244        |

| Table 175: Hash Key Input Operands                  | 244        |

| Table 176: Hash Key Output Results                  | 245        |

| Table 177: RDLUDEF Input Operands                   | 245        |

| Table 178: RDLUDEF Output Results                   | 245        |

| Table 179: COMPEND Input Operands                   | 246        |

| Table 180: COMPEND Output Results                   | 246        |

| Table 181: General GTH Instructions                 | 247        |

| Table 182: Hash Key GTH Input Operands              | 247        |

| Table 183: Hash Key GTH Output Results              | 248        |

| Table 184: RDLUDEF_GTH Input Operands               | 248        |

| Table 185: RDLUDEF_GTH Output Results               | 248        |

| Table 186: TSENQFL Input Operands                   | 249        |

| Table 187: TSENQFL Output Results                   | 249        |

| Table 188: TSDQFL Input Operands                    | 249        |

| Table 189: TSDQFL Output Results                    | 250        |

| Table 190: RCLR Input Operands                      | 250        |

| Table 191: RCLR Output Results                      | 250        |

| Table 192: ARDL Input Operands                      | 251        |

| Table 193: ARDL Output Results                      | 251        |

| Table 194: TLIR Input Operands                      | 252        |

| Table 195: TLIR Output Results                      | 252        |

| Table 196: CLRPSCB Input Operands                   | 252        |

| Table 197: CLRPSCB Output Results                   | 252        |

| Table 198: RDPSCB Input Operands                    | 253        |

| Table 199: RDPSCB Output Results                    | 253        |

| Table 200: WRPSCB Input Operands                    | 253        |

| Table 201: PUSHPSCB Input Operands                  |            |

| Table 202: PUSHPSCB Output Results                  |            |

| Table 203: DISTPOS Input Operands                   |            |

| Table 204: DISTPOS Output Results                   |            |

| Table 205: TSR0PAT Input Operands                   |            |

| Table 206: TSR0PAT Output Results                   |            |

| Table 207: | PAT2DTA Input Operands                                                                                         | 255 |

|------------|----------------------------------------------------------------------------------------------------------------|-----|

| Table 208: | PAT2DTA Output Results                                                                                         | 255 |

| Table 209: | General Hash Functions                                                                                         | 256 |

|            | Field Definitions for CAB Addresses                                                                            |     |

| Table 211: | PLB Master Connections                                                                                         | 274 |

| Table 212: | UIC Interrupt Assignments                                                                                      | 275 |

|            | PLB Address Map for PCI/PLB Macro                                                                              |     |

|            | Reset Domains                                                                                                  |     |

| Table 215: | Reset and Initialization Sequence                                                                              | 327 |

|            | Set I/Os Checklist                                                                                             |     |

|            | Setup 1 Checklist                                                                                              |     |

|            | Diagnostics 1 Checklist                                                                                        |     |

|            | Setup 2 Checklist                                                                                              |     |

|            | Hardware Initialization Checklist                                                                              |     |

|            | Diagnostic 2 Checklist                                                                                         |     |

|            | Configure Checklist                                                                                            |     |

|            | Absolute Maximum Ratings                                                                                       |     |

|            | Input Capacitance (pF)                                                                                         |     |

|            | Operating Supply Voltages                                                                                      |     |

|            | Thermal Characteristics                                                                                        |     |

|            | Definition of Terms                                                                                            |     |

|            | 1.8 V CMOS Driver DC Voltage Specifications                                                                    |     |

|            | 1.8 V CMOS Driver Minimum DC Currents at Rated Voltage                                                         |     |

|            | 2.5 V CMOS Driver DC Voltage Specifications                                                                    |     |

|            | 2.5 V CMOS Driver Minimum DC Currents at Rated Voltage                                                         |     |

|            | 3.3 V-Tolerant 2.5 V CMOS Driver DC Voltage Specifications                                                     |     |

|            | 3.3 V LVTTL Driver DC Voltage Specifications                                                                   |     |

|            | 3.3 V LVTTL/5.0 V-Tolerant Driver DC Voltage Specifications                                                    |     |

|            | 3.3 V LVTTL Driver Minimum DC Currents at Rated Voltage                                                        |     |

|            | 1.8 V CMOS Receiver DC Voltage Specifications                                                                  |     |

|            | 2.5 V CMOS Receiver DC Voltage Specifications                                                                  |     |

|            | 3.3 V LVTTL Receiver DC Voltage Specifications                                                                 |     |

|            | 3.3 V LVTTL/5V-Tolerant Receiver DC Voltage Specifications                                                     |     |

|            | Receiver Maximum Input Leakage DC Current Input Specifications                                                 |     |

|            | LVDS Receiver DC Specifications                                                                                |     |

|            | taran da antara da a | 430 |

List of Tables np3\_DLLOT.fm Page 16 09/25/00

| List of Figures                                                                               |      |

|-----------------------------------------------------------------------------------------------|------|

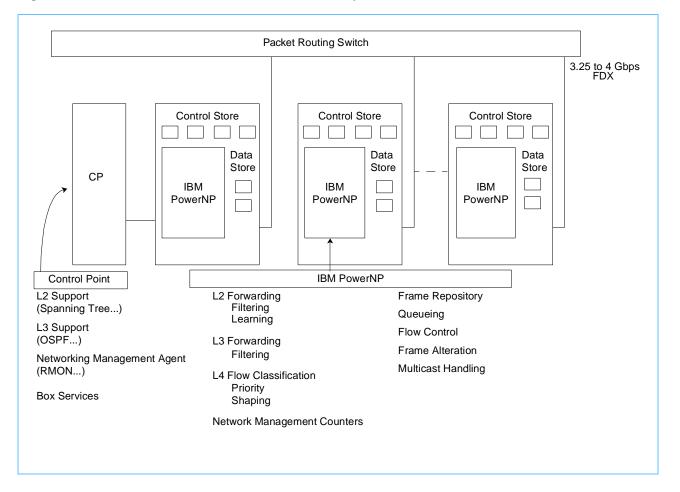

| Figure 1: Function Placement in an NP4GS3-Based System                                        | . 25 |

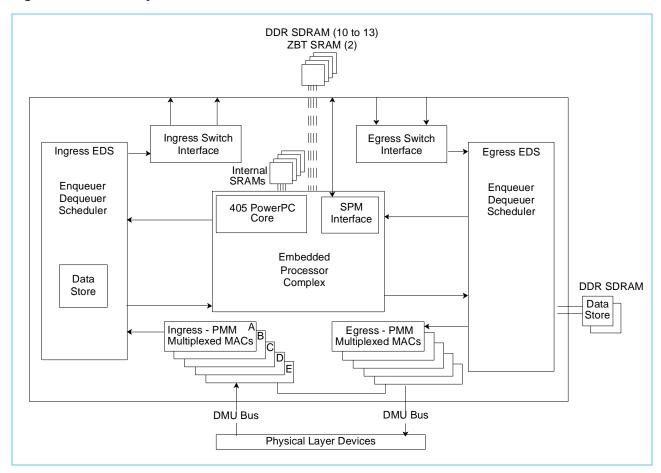

| Figure 2: NP4GS3 Major Sections                                                               | . 26 |

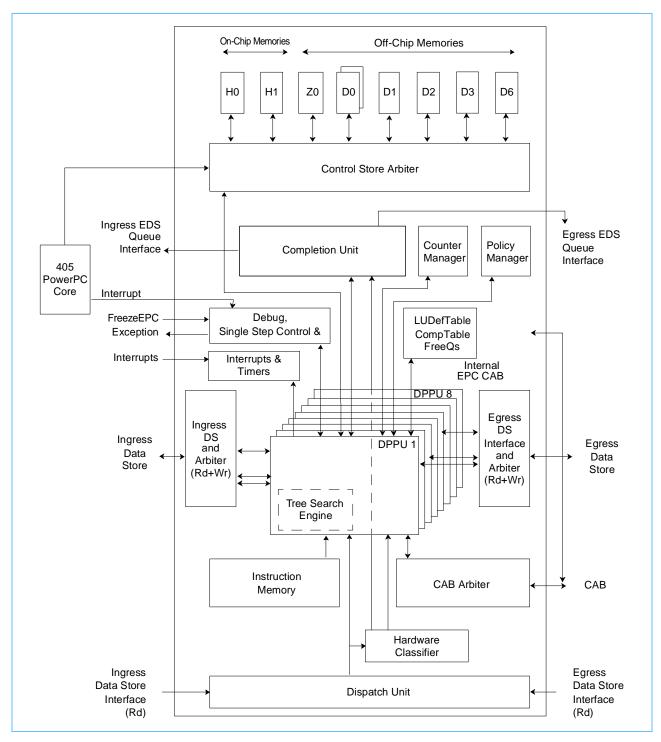

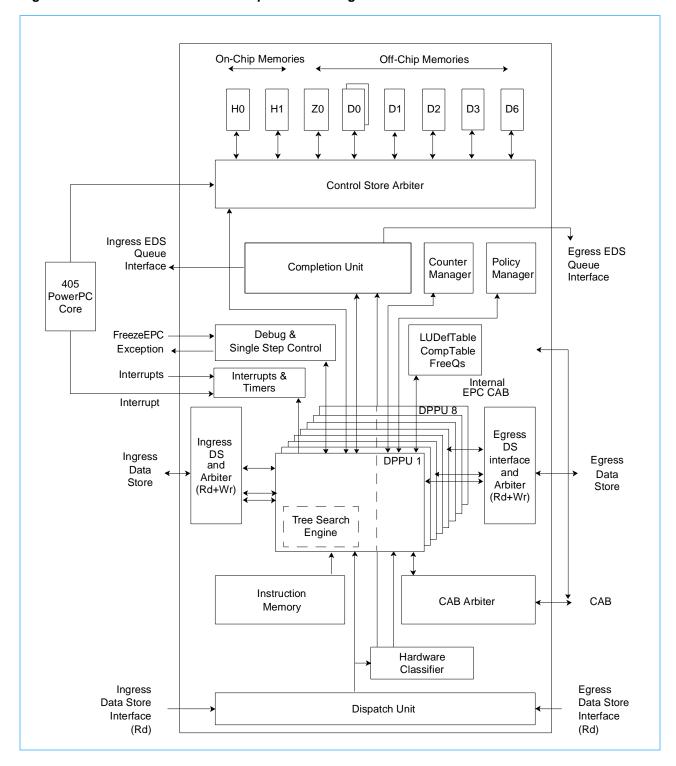

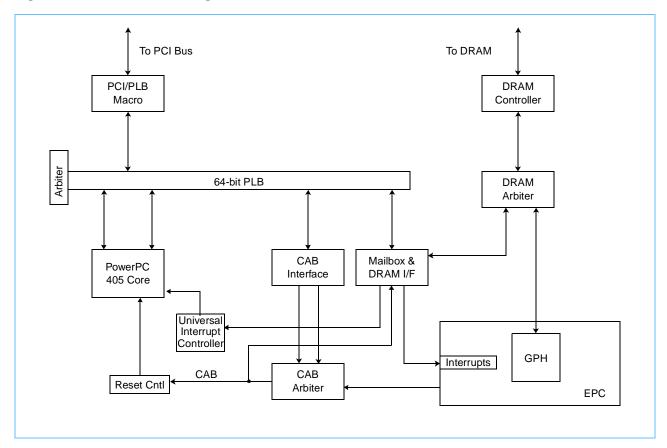

| Figure 3: Embedded Processor Complex Block Diagram                                            | 27   |

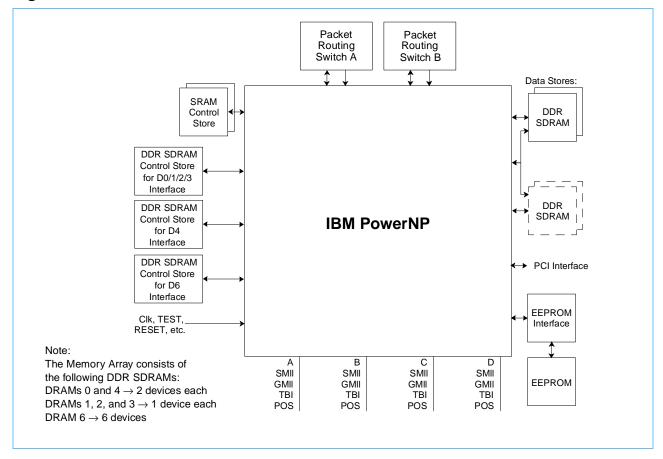

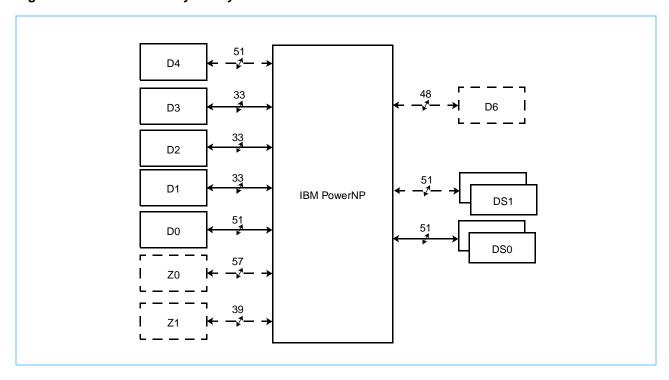

| Figure 4: Devices Interfaces                                                                  | 29   |

| Figure 5: ZBT SRAM Timing Diagram                                                             | 35   |

| Figure 6: DDR Timing Diagram                                                                  |      |

| Figure 7: DDR Read Input Timing Diagram                                                       | . 41 |

| Figure 8: DDR Write Output Timing Diagram                                                     |      |

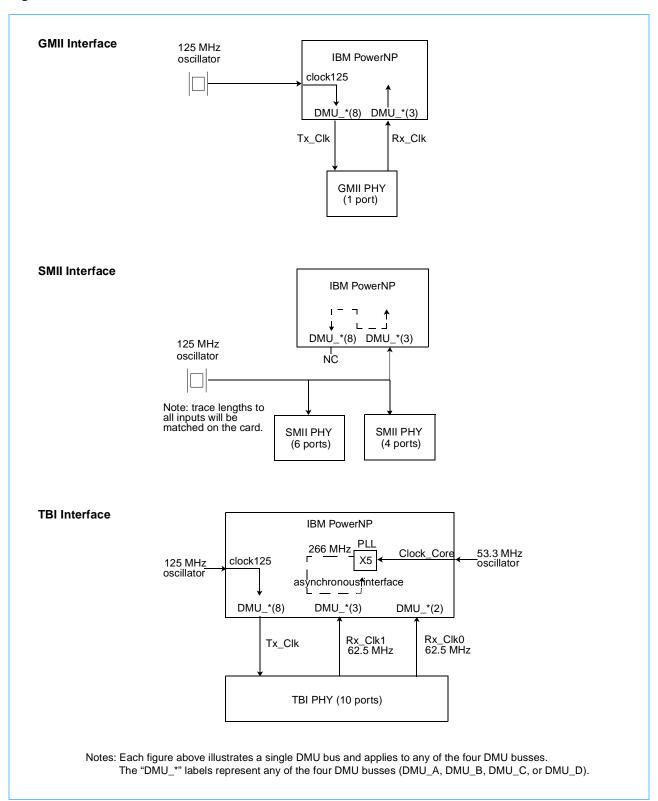

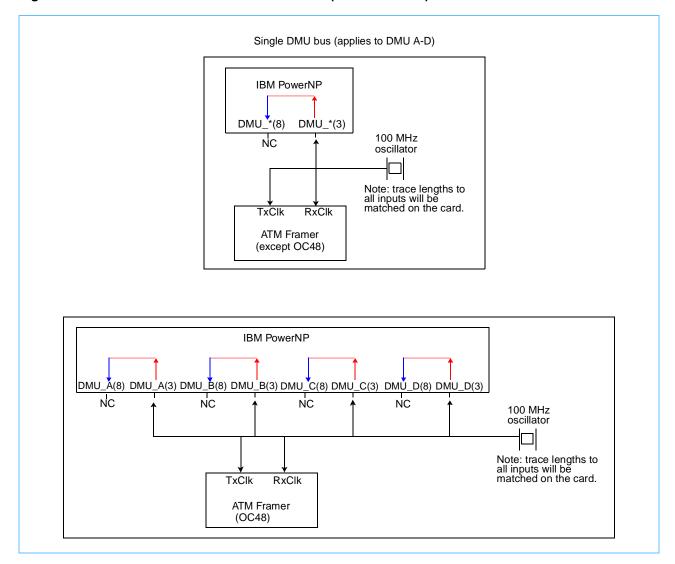

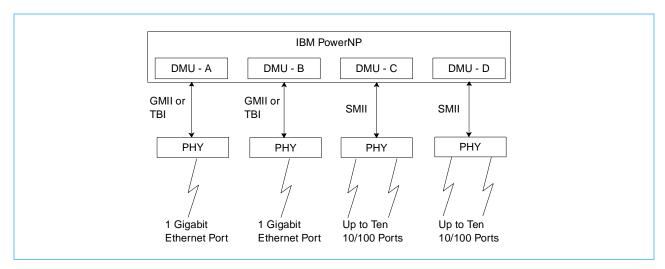

| Figure 9: NP4GS3 DMU Bus Clock Connections                                                    | . 46 |

| Figure 10: NP4GS3 DMU Bus Clock Connections (POS Overview)                                    | . 47 |

| Figure 11: GMII Timing Diagram                                                                | . 49 |

| Figure 12: TBI Timing Diagram                                                                 | . 52 |

| Figure 13: SMII Timing Diagram                                                                | . 54 |

| Figure 14: POS Timing Diagram                                                                 | . 57 |

| Figure 15: PCI Timing Diagram                                                                 | . 60 |

| Figure 16: Management Bus Timing Diagram                                                      | . 62 |

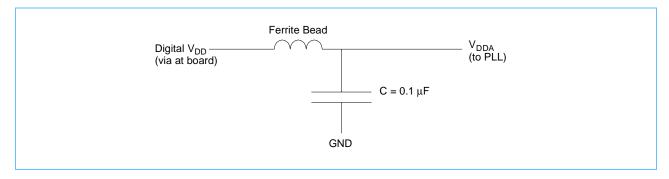

| Figure 17: PLL Filter Circuit Diagram                                                         | . 66 |

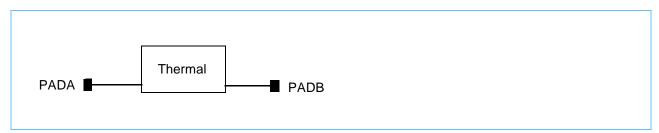

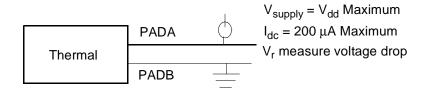

| Figure 18: Thermal Monitor                                                                    | . 66 |

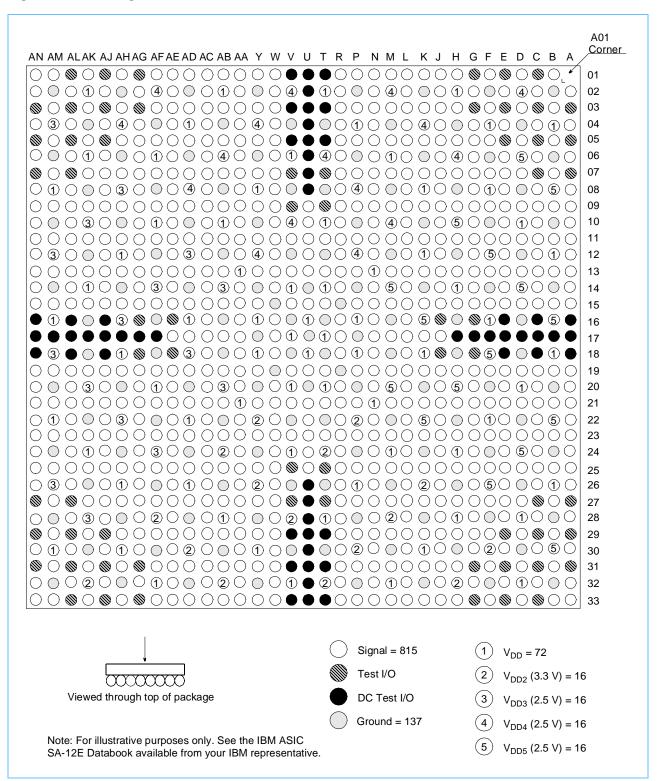

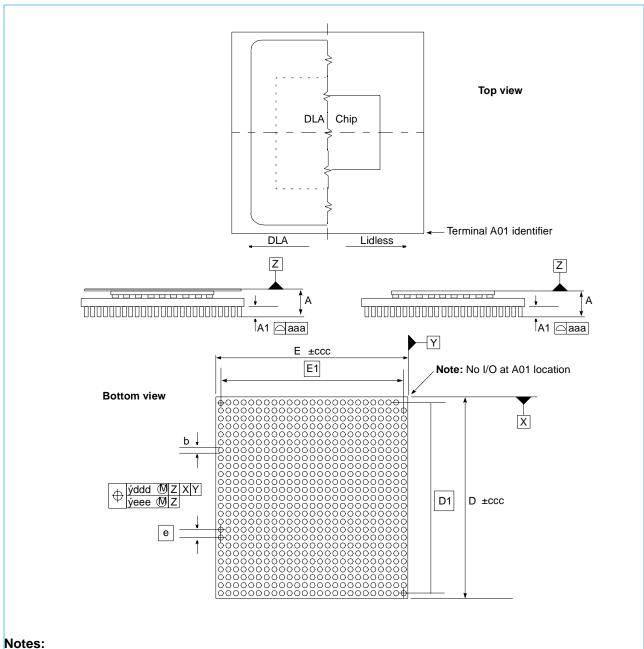

| Figure 19: Pins Diagram                                                                       |      |

| Figure 20: Mechanical Diagram                                                                 | . 69 |

| Figure 21: PMM Overview                                                                       | . 93 |

| Figure 22: SMII Timing Diagram                                                                | . 94 |

| Figure 23: GMII Timing Diagrams                                                               | . 94 |

| Figure 24: TBI Timing Diagrams                                                                | . 95 |

| Figure 25: Ethernet Mode                                                                      | . 95 |

| Figure 26: GMII POS Mode Timing Diagram                                                       |      |

| Figure 27: Receive POS8 Interface Timing for 8-bit data bus (OC-3c, OC-12, OC-12c, and OC-48) | 105  |

| Figure 28: Receive POS32 Interface Timing for 32-bit data bus (OC-48c)                        |      |

| Figure 29: Transmit POS8 Interface Timing for 8-bit data bus (OC-3c, OC-12)                   |      |

| Figure 30: Transmit POS8 Interface Timing for 8-bit data bus (OC-12c, OC-48)                  |      |

| Figure 31: Transmit POS32 Interface Timing for 32-bit data bus (OC-48c)                       |      |

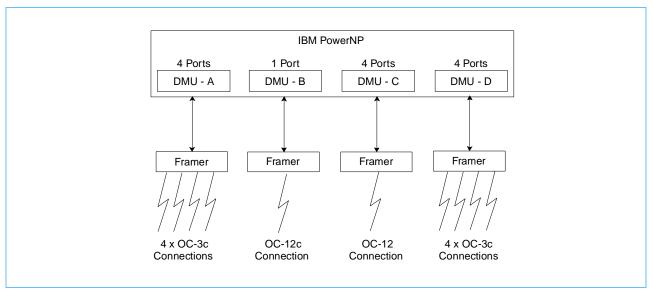

| Figure 32: OC-3c/12/12c Configuration                                                         |      |

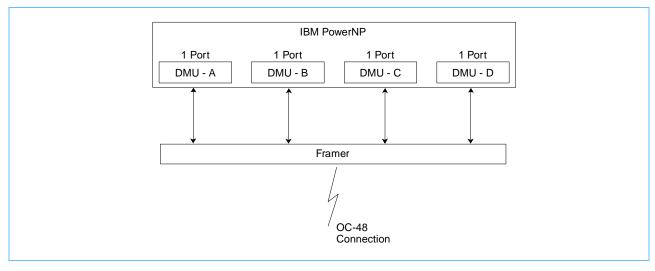

| Figure 33: OC-48 Configuration                                                                |      |

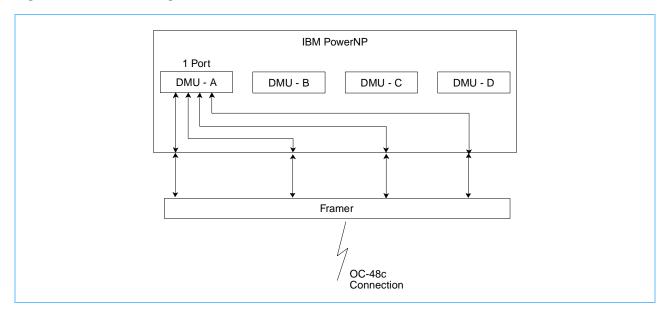

| Figure 34: OC-48c Configuration                                                               |      |

| Figure 35: Logical Organization of the Data Flow Managed by the Ingress EDS                   |      |

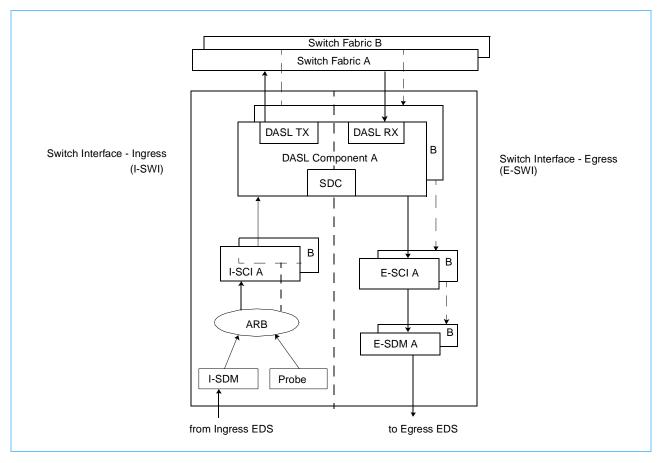

| Figure 36: Switch Interface Functional Units                                                  |      |

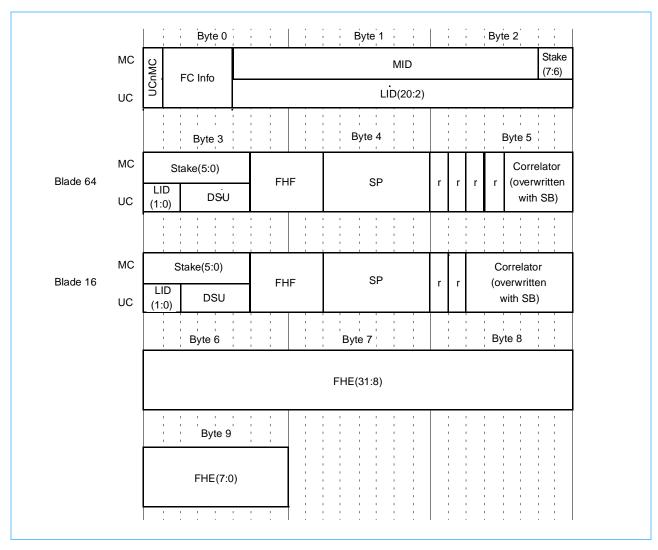

| Figure 37: Cell Header Format                                                                 |      |

| Figure 38: Frame Header Format                                                                |      |

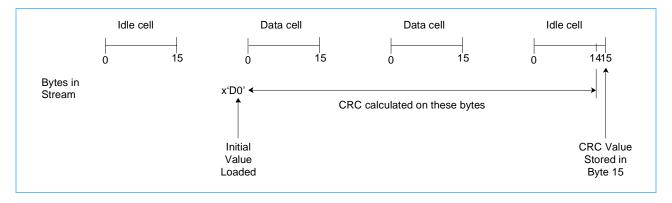

| Figure 39: CRC Calculation Example                                                            |      |

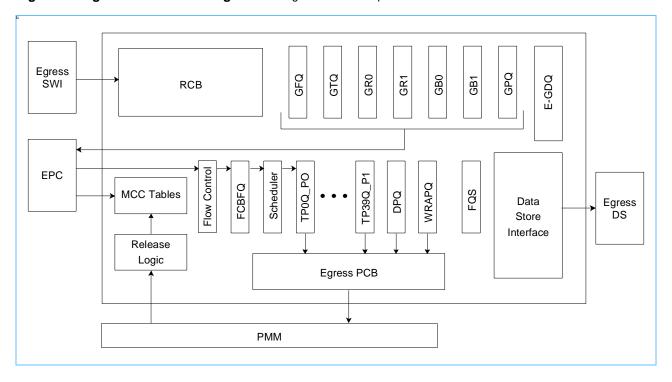

| Figure 40: Egress EDS Block Diagram                                                           |      |

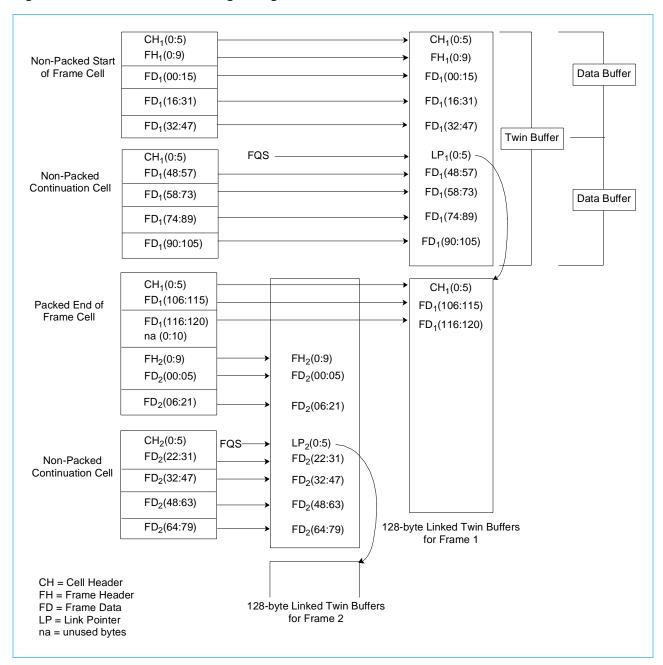

| Figure 41: Cell Formats and Storage in Egress Data Store                                      |      |

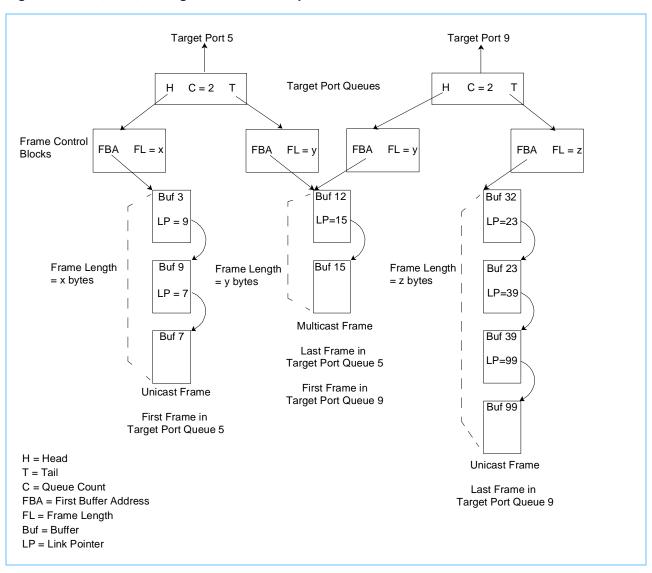

| Figure 42: TPQ, FCB, and Egress Frame Example                                                 |      |

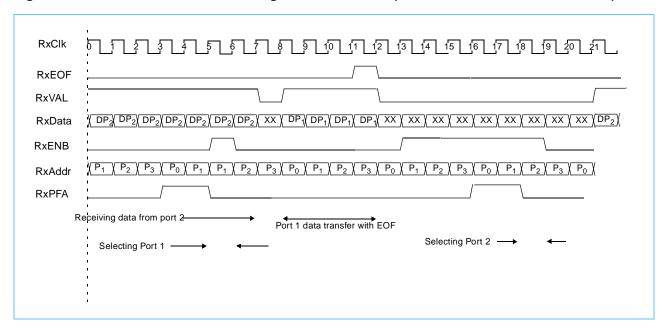

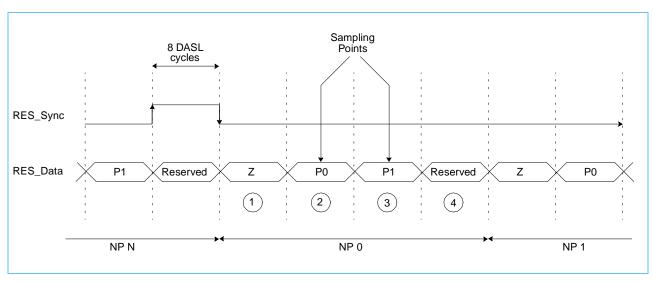

| Figure 43: RES Bus Timing                                                                     |      |

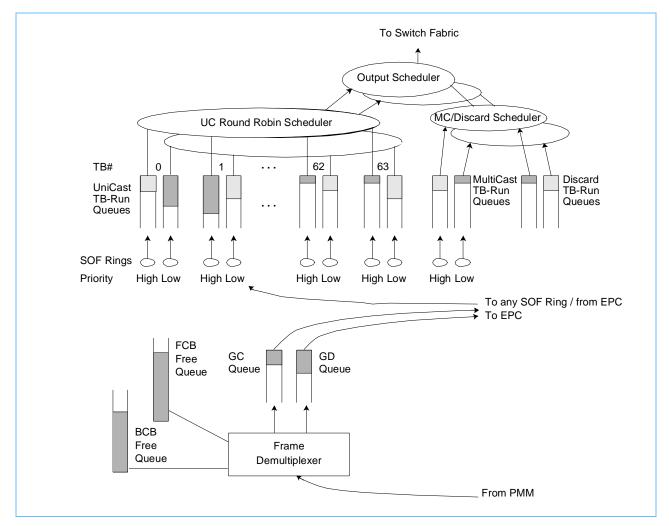

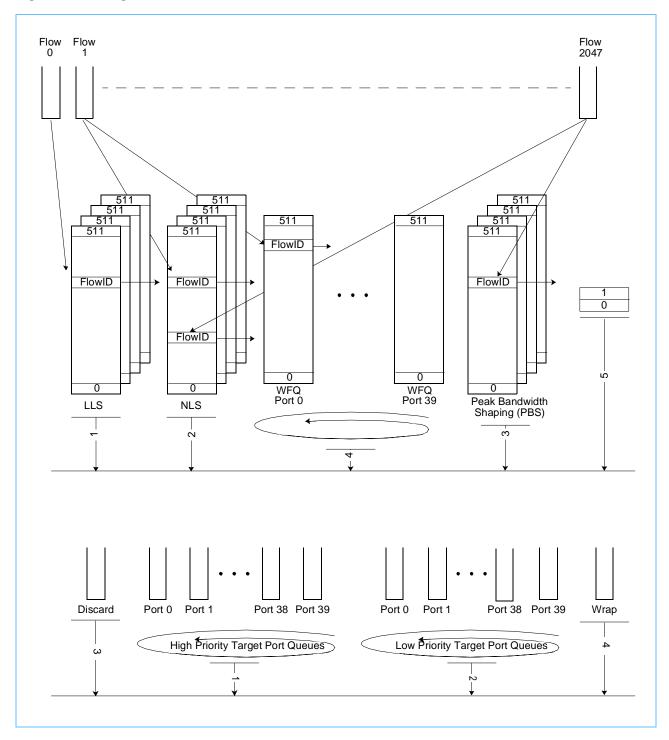

| Figure 44: The Egress Scheduler                                                               |      |

| Figure 45: Embedded Processor Complex Block Diagram                                           | 151  |

| Figure 46: Dyadic Protocol Processor Unit Block Diagram                                       |      |

| Figure 47: Core Language Processor                                                            | 155  |

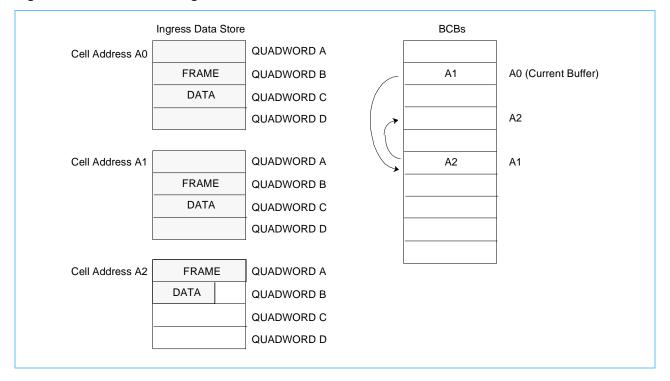

| Figure 48: A Frame in the Ingress Data Store                                                  | 162  |

| Figure 49: A Frame in the Egress Data Store                                                   |      |

| Figure 50: Ingress FCBPage Format                                                             | 177  |

### NP4GS3

### IBM PowerNP Preliminary

| Figure 51: Egress FCBPage Format                                                     | 180 |

|--------------------------------------------------------------------------------------|-----|

| Figure 52: Split between Picocode and Hardware for the Policy Manager                |     |

| Figure 53: Counter Manager Block Diagram                                             |     |

| Figure 54: Counter Definition Entry                                                  |     |

| Figure 55: Counter Blocks and Sets                                                   |     |

| Figure 56: Example Shaping Dimensions                                                |     |

| Figure 57: Effects of Using a Direct Table                                           |     |

| Figure 58: Example Input Key and Leaf Pattern Fields                                 |     |

| Figure 59: Rope Structure                                                            |     |

| Figure 60: No-Hash Function                                                          |     |

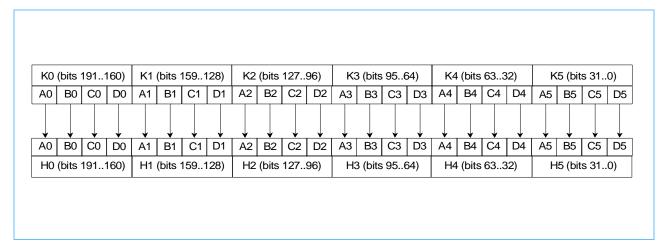

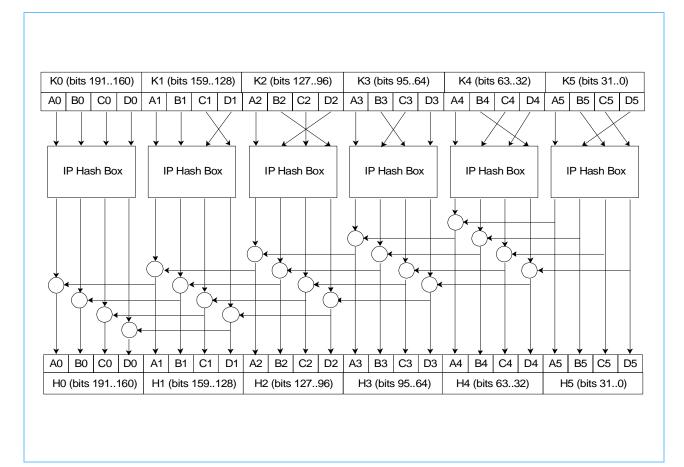

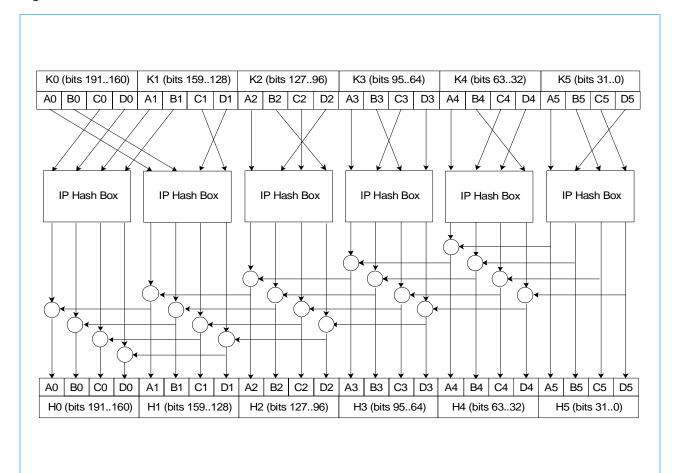

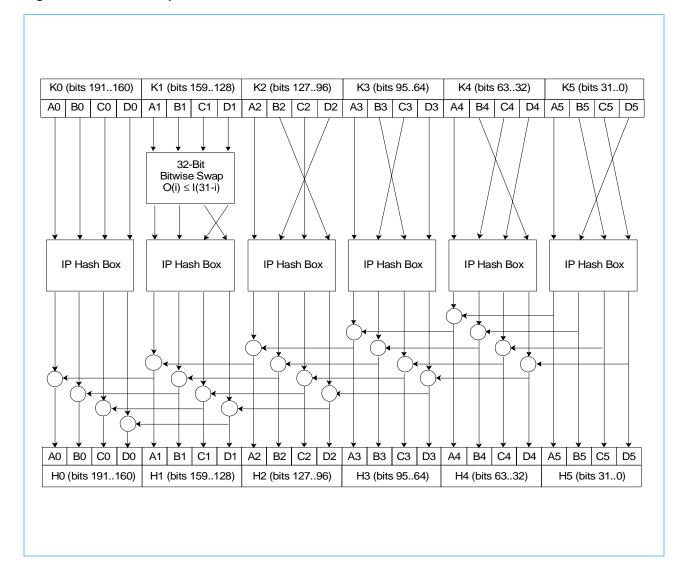

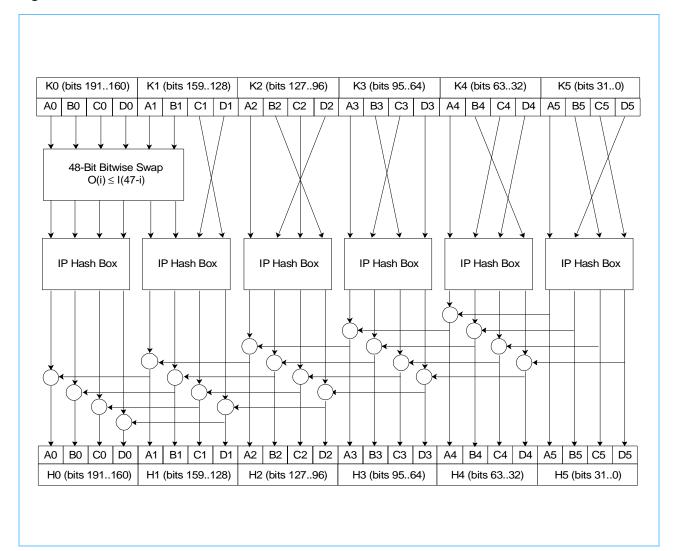

| Figure 61: 192-Bit IP Hash Function                                                  |     |

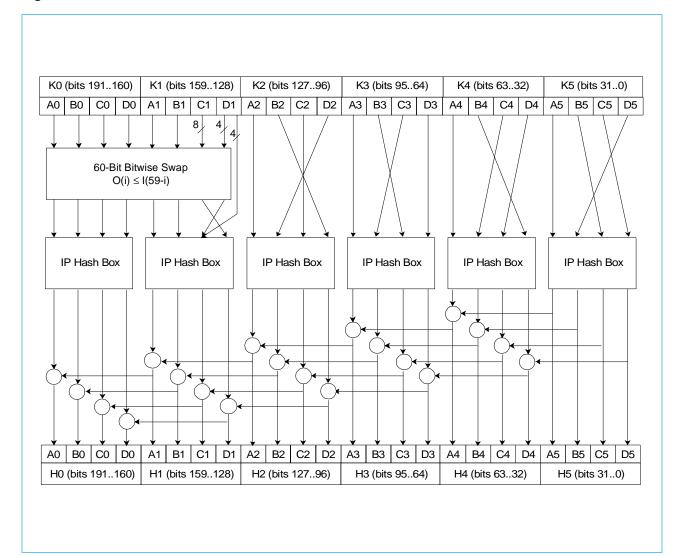

| Figure 62: MAC Hash Function                                                         |     |

| Figure 63: Network Dispatcher Hash Function                                          | 259 |

| Figure 64: 48-Bit MAC Hash Function                                                  |     |

| Figure 65: 60-Bit MAC Hash Function                                                  |     |

| Figure 66: SPM Interface Block Diagram                                               |     |

| Figure 67: EPC Boot Image in External EEPROM                                         |     |

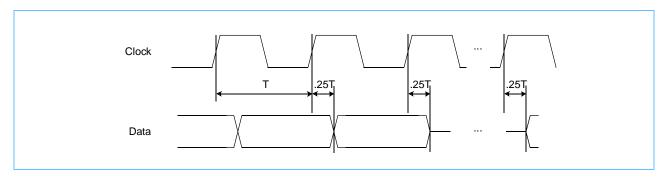

| Figure 68: SPM Bit Timing                                                            |     |

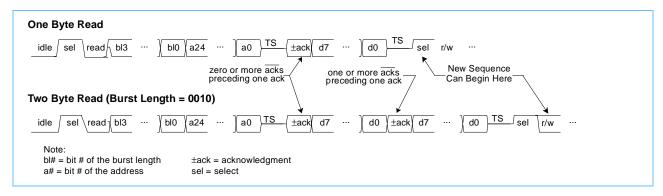

| Figure 69: SPM Interface Read Protocol                                               |     |

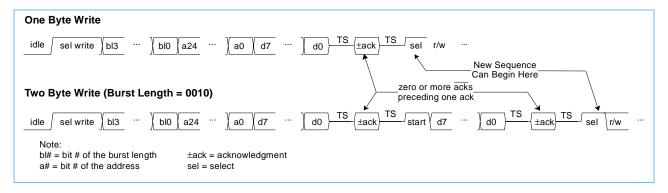

| Figure 70: SPM Interface Write Protocol                                              |     |

| Figure 71: PowerPC Block Diagram                                                     |     |

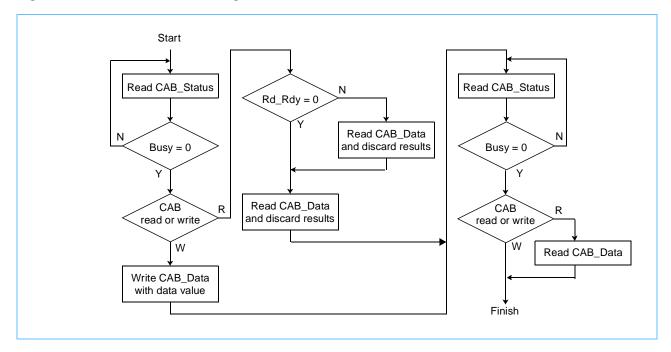

| Figure 72: Polled Access Flow Diagram                                                |     |

| Figure 73: System Environments                                                       |     |

| Figure 74: NP4GS3 Memory Subsystems                                                  |     |

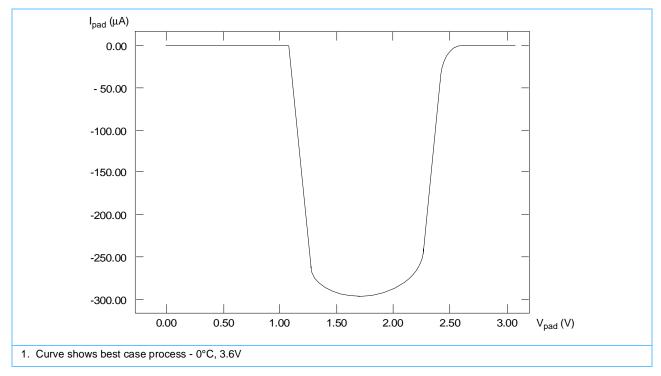

| Figure 75: 3.3V LVTTL/5V Tolerant BP33 and IP33 Receiver Input Current/Voltage Curve |     |

### **About This Book**

This databook describes the IBM PowerNP NP4GS3 and explains the basics of building a system using it.

A list of terms and abbreviations is provided in section 15. Glossary of Terms and Abbreviations on page 433.

### **Who Should Read This Manual**

This document is intended to provide information to programmers and engineers using the NP4GS3 for development of interconnect solutions for Internet or enterprise network providers.

Technology information to enable development of cards and boards includes electrical specifications and interface protocol and timings.

Programmer information includes descriptions of the Dyadic Protocol processors and the available command set. Additional information on configuring the network processor features for operation such as the egress scheduler and the flow control hardware is provided.

### **Related Publications**

PPC405GP Embedded Controller User's Manual (http://www.chips.ibm.com/techlib/products/powerpc/datasheets.html)

PCI Specification, version 2.2. (http://www.pcisig.com)

### **Conventions Used in This Manual**

The following conventions are used in this manual.

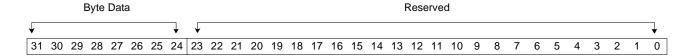

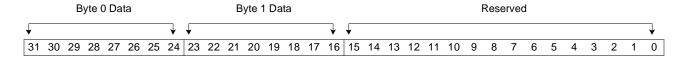

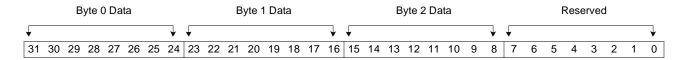

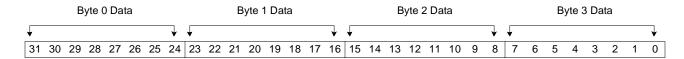

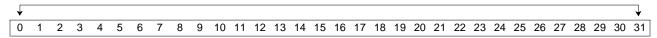

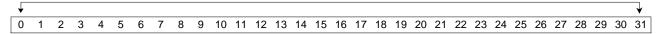

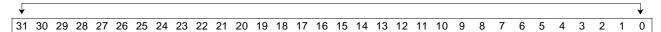

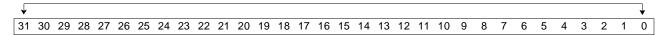

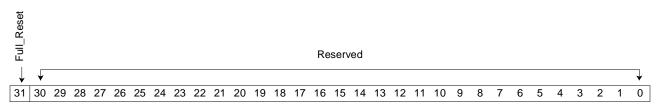

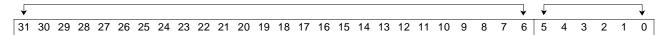

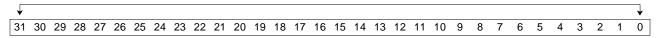

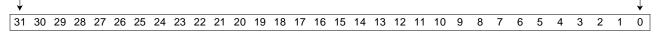

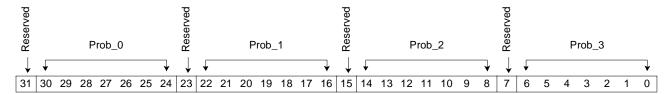

The bit notation for Physical Description, Physical MAC Multiplexer, Enqueuer / Dequeuer / Scheduler, Switch Interface, Embedded Processor Complex, Control Access Bus, and the Serial/Parallel Manager Interface, is non-IBM, meaning that bit zero is the least significant bit and bit 31 is the most significant bit in a 4-byte word.

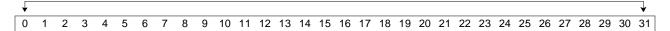

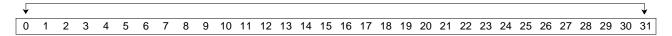

The bit notation for Tree Search Engine and Embedded PowerPC is IBM-standard, meaning that bit 31 is the least significant bit and bit zero is the most significant bit in a 4-byte word.

- 2. Nibble numbering is the same as byte numbering. The left-most nibble is most significant and starts at zero

- 3. Overbars, e.g. TxEnb, designate signals that are asserted "low".

- 4. Numeric notation is as follows:

- Hexadecimal values are preceded by x or X. For example: x'0B00'.

- Binary values in text are either spelled out (zero and one) or appear in quotation marks.

For example: '10101'.

- Binary values in the Default and Description columns of the register sections are often isolated from text as in this example:

- 0: No action on read access

- 1: Auto-reset interrupt request register upon read access

- 5. Field length conventions are as follows:

- 1 byte = 8 bits

- 1 word = 4 bytes

- 1 double word (DW) = 2 words = 8 bytes

- 1 quadword (QW) = 4 words = 16 bytes

- 6. For signal and field definitions, when a field is designated as reserved ('r'):

- As an input to the NP4GS3 it must be sent as zero.

- As an output from the NP4GS3 it must not be checked or modified.

- Its use as code point results in unpredictable behavior.

### 1. General Information

### 1.1 Features

- 4.5 million packets per second (Mpps) Layer 2 and Layer 3 Switching.

- 40 Fast Ethernet / 4 Gb MACs accessed through SMII, GMII, and TBI interfaces supporting industry standard PHY components. The Ethernet MAC provides 36 Ethernet statistics counters. Software can define an additional one million counters. Once these counts are defined, the hardware assists in updating them. With this hardware support, many standard MIBs can be supported at wire speed.

- Supports IEEE 802.3 ad link aggregation and VLAN detection (frame type 8100).

- 16xOC-3c / 4xOC-12 / 4xOC-12c / 1xOC-48 / 1xOC-48c integrated Packet over SONET (POS) interfaces support industry standard POS framers.

- Two Data-Aligned Synchronous Link (DASL)

ports, rated 3.25 to 4 Gbps, for attachment to

the Packet Routing Switch, another IBM PowerNP NP4GS3, or to itself through a wrap path

for a stand-alone solution. (DASLs are electrically I/O compliant with the EIA/JEDEC JESD86 standard for differential HSTL.)

- Addressing capability of 64 target network processors, allowing the design of a network interconnect solution supporting 1024 ports.

- Advanced flow control mechanisms which tolerate high rates of temporary oversubscription without TCP collapse.

- Geometric hash functions yield lower collision rates than conventional bit scrambling methods, providing faster lookups and more powerful search engines.

- Hardware support for Port Mirroring<sup>1</sup>. Depending on the application, mirrored traffic can either share bandwidth with user traffic or use a separate Switch data path, eliminating the penalty

- normally associated with Port Mirroring.

- Support for jumbo frames (9018 without VLAN, 9022 with VLAN).

- Hardware managed and software configured bandwidth allocation control of 2048 concurrent communication flows.

- Embedded PowerPC<sup>™</sup> and external 33/66 Mhz 32-bit PCI Bus for enhanced design flexibility.

- Supports RISCWatch through the JTAG interface

- Eight Dyadic Protocol Processor Units (DPPU)

- two picocode engines per DPPU

- eight coprocessor units per DPPU to reduce picocode path lengths for common tasks

- Multi-thread support of four threads per DPPU (two per picocode engine)

- Zero context switching overhead between threads

- Serial management interface to support physical layer devices, board and box functions

- IBM SA-27E, 0.18 μm technology.

- · Voltage ratings.

- 1.8 V supply voltage

- 2.5 V and 3.3 V compatibility with drivers and receivers

- 1.25 V reference voltage for SSTL drivers

- 1.5 V compatibility for DASL interfaces

- 1088-pin Bottom Surface Metallurgy Ceramic Column Grid Array (BSM-CCGA) package with 815 Signal I/O.

- IEEE 1149.1a JTAG compliant.

<sup>1.</sup> OC48c ports are not supported by port mirroring functions.

## 1.2 Ordering Information

| Part Number          | Description        |

|----------------------|--------------------|

| IBM32NPR161EPXCAC133 | IBM PowerNP NP4GS3 |

#### 1.3 Overview

The IBM PowerNP™ NP4GS3 is IBM's latest technology for supporting media-rate, multi-layer Ethernet switching. It also supports the IP over Sonet (POS) and PPP protocol. The NP4GS3 provides a highly customizable, scalable technology for the development of interconnect solutions for Internet or enterprise network providers. A single device can be used in desktop solution or be a component in a large multi-rack solution with up to 1024 ports. When used with the IBM Packet Routing Switch, addressing is limited to 640 ports. Scaling of this nature is accomplished through the use of IBM's high performance, non-blocking, packet switching technology and IBM's Data-Aligned Synchronous Link (DASL) interface which can be adapted to other industry switch technologies.

The NP4GS3 integrates switching engine, search engine, and security functions on one device to support the needs of customers who require high capacity, media rate switching of Layer 2 and 3 frames. Three switch priority levels are supported for port mirroring, high priority user frames, and low priority frames. The device's ability to enforce hundreds of rules with complex range and action specifications, a new industry benchmark for filtering capabilities, makes an NP4GS3-based system uniquely suited for server farm applications.

The NP4GS3 contains dyadic protocol processor units that work with hardware accelerators to support high speed pattern search, data manipulation, internal chip management functions, frame parsing, and data prefetching.

Systems developed with the NP4GS3 use a distributed software model. A rich instruction set includes conditional execution, packing (for input hash keys), conditional branching, signed and unsigned operations, counts of leading zeros, and more. To support this model, the device hardware and Code Development Suite include on-chip debugger facilities, a picocode assembler, and a picocode and system simulator which decrease the time to market for new applications.

The NP4GS3's scalability allows the design of multiple system configurations:

- Low-end systems with only one device which can use the device's switch interface to wrap traffic from the Ingress side to the Egress side.

- Medium-end systems with two devices which are directly interconnected through their switch interfaces.

- High-end systems with up to 64 NP4GS3s which are interconnected through a single or redundant switch. The IBM Packet Routing Switch is limited to addressing up to 16 NP4GS3s.

### 1.4 NP4GS3-Based System Design

The NP4GS3 contains eight dyadic protocol processor units (DPPUs) with 16 K words of internal picocode instruction store, providing 2128 MIPS of processing power. Each DPPU contains two processors (CLPs) which share eight dedicated coprocessors. All eight DPPUs share three hardware accelerators. Each CLP can run two threads; each DPPU can therefore run four threads. Context switching occurs when the CLP is waiting for a shared resource (for example, waiting for one of the coprocessors to complete an operation, return the results of a search, or access DRAM). Context switching is accomplished by hardware assists that maintain separate sets of General Purpose Registers (GPR). Coprocessors can run in parallel with the protocol processors.

The Control Store for the protocol processors is provided by both internal and external memories: internal SRAM for immediate access, external ZBT SRAM for fast access, and external DDR SDRAM for large storage requirements. The internal Control Access Bus (CAB) allows access to internal registers, counters, and memory. The CAB also includes an external interface to control instruction step and interrupt control for debugging and diagnostics.

### 1.4.1 Coprocessors

- The Data Store coprocessor interfaces frame buffer memory (ingress and egress directions) providing a 320-byte working area.

- The Checksum coprocessor calculates and verifies header checksums.

- The Enqueue coprocessor manages control blocks containing key frame parameters. This coprocessor

interfaces with the Completion Unit hardware assist, to enqueue frames to the switch and target port output queues.

- The CAB interface coprocessor controls thread access to the CAB through the CAB Arbiter.

- The String Copy coprocessor accelerates data movement between coprocessors.

- The Counter coprocessor manages counter updates for the picocode engines.

- The Policy coprocessor determines if the incoming data stream complies with configured profiles.

- The Tree Search Engine performs pattern analysis through tree searches, along with regular read and write accesses, all protected by memory range checking.

#### 1.4.2 Hardware Accelerators

- The Completion Unit assures frame order.

- The Dispatch Unit parses the work out among the dyadic processors.

- The Control Store Arbiter is a shared memory interface.

### 1.4.3 NP4GS3 Memory

The NP4GS3 utilizes:

- A common instruction memory which holds 16 K instruction words for normal processing and control functions

- · A 128 K byte internal SRAM for input frame buffering

- 113 K bytes of internal SRAM Control Store

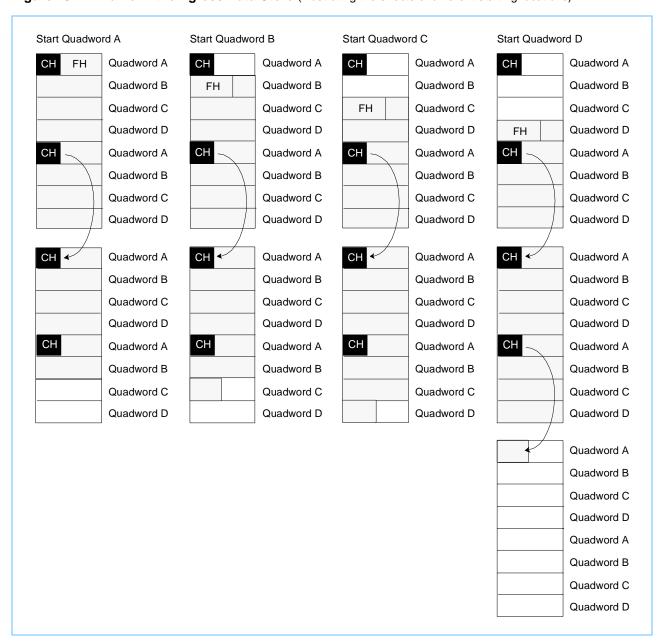

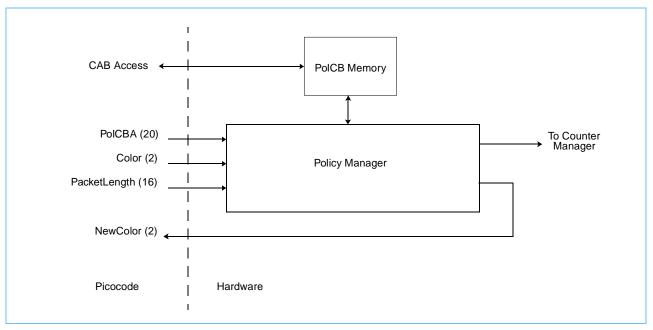

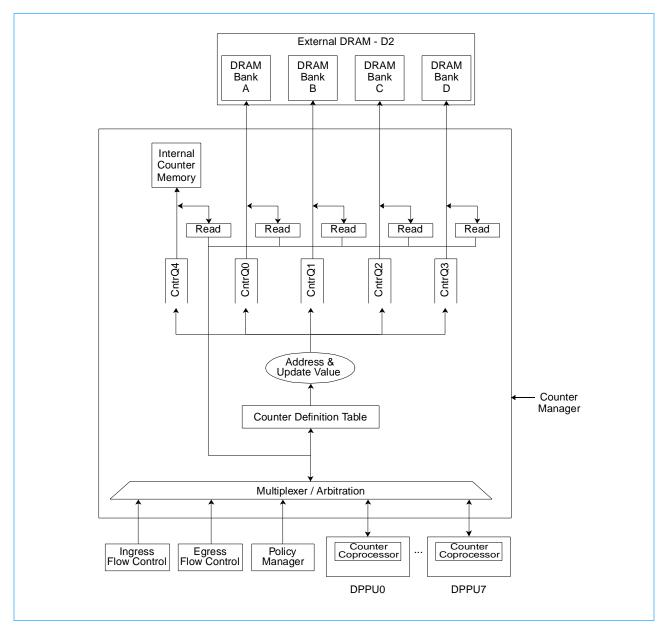

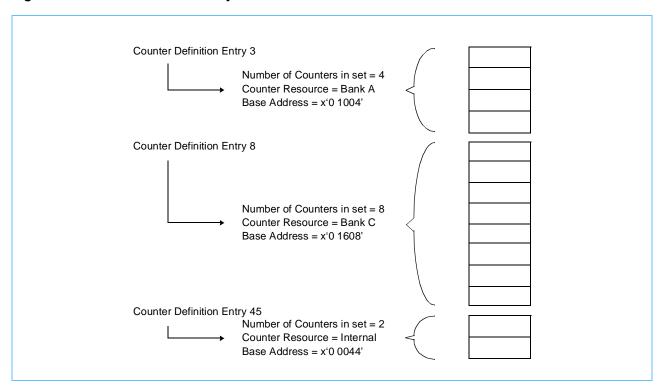

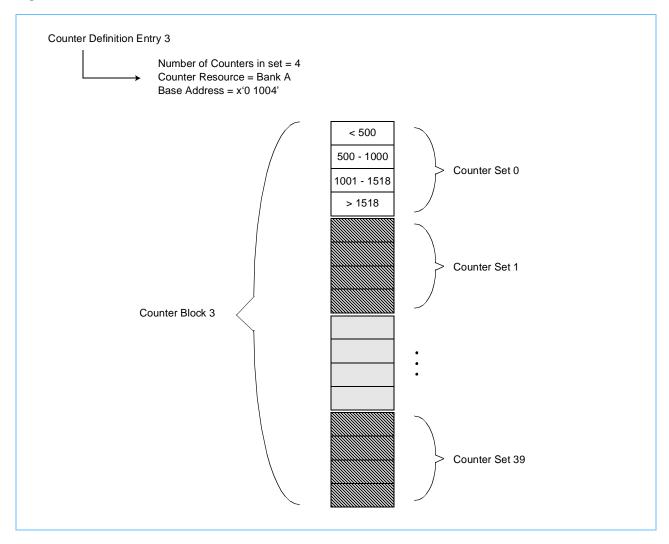

- High capacity external DDR DRAM for egress frame buffering and to support large forwarding tables