# **YDA147**

D-515

#### STEREO 5W-15W DIGITAL AUDIO POWER AMPLIFIER

#### ■General Description

YDA147 (D-515) is a high-efficiency digital audio power amplifier IC with the maximum output of 15W × 2ch. YDA147 has a "Pure Pulse Direct Speaker Drive Circuit" that directly drives speakers while reducing distortion of pulse output signal and reducing noise on the signal, which realizes the highest standard low distortion rate characteristics and low noise characteristics among digital amplifier ICs in the same class.

In addition, supporting filterless design allows circuit design with fewer external parts to be realized depending on use conditions.

YDA147 features Power Limit Function, Non-clip Function, and DRC (Dynamic Range Control) Function that were developed by Yamaha original digital amplifier technology.

YDA147 has overcurrent protection function for speaker output terminals, high temperature protection function, and lowsupply voltage malfunction prevention function.

■ Features ·Operating supply voltage range PVDD: 8.0V to 16.5V ·Maximum momentary output 20 W×2ch ( $V_{DDP}$ =14V,  $R_L$ =4 $\Omega$ , THD+N=10%) 15 W×2ch ( $V_{DDP}$ =12V,  $R_L$ =4 $\Omega$ , THD+N=10%) · Maximum continuous output 15 W\* $^1$ ×2ch (V<sub>DDP</sub>=15V, R<sub>L</sub>=8 $\Omega$ , THD+N=10%, Ta=70°C, SQFP48, 4 layers) 10.5W\* $^1$ ×2ch (V<sub>DDP</sub>=15V, R<sub>L</sub>=4 $\Omega$ , THD+N=10%, Ta=25°C, SQFP48, 4 layers)  $10 \text{ W}^{*1} \times 2 \text{ch}$  (V<sub>DDP</sub>=12V, R<sub>L</sub>=8 $\Omega$ , THD+N=10%, Ta=25°C, LQFP48, 1 layer) •Distortion Rate (THD+N)  $0.01\% (V_{DDP} = 12V, R_{L} = 8\Omega, Po = 0.1W, 1kHz)$ ·Residual Noise 48μVrms (V<sub>DDP</sub>=12V, GAIN[1:0]=L,L, NCDRC[1:0]=L,L) Efficiency 92 % ( $V_{DDP}=12V, R_{L}=8\Omega$ ) ·S/N Ratio 105 dB (V<sub>DDP</sub>=12V, GAIN[1:0]=L,L, NCDRC[1:0]=L,L) Channel separation -80 dB ( $\hat{V}_{DDP}$ =12V, GAIN[1:0]=L,L, NCDRC[1:0]=L,L) ·PSRR 60dB (V<sub>DDP</sub>=12V,Vripple=100mV, 1kHz, GAIN[1:0]=L,L, NCDRC[1:0]=L,L) • Non-clip function/DRC function (switchable) Power limit function ·Clock External Synchronization Function ·Master/Slave Synchronization Function using clock outputs ·Over-current Protection Function, High Temperature Protection Function, Low Voltage Malfunction Prevention Function, and DC Detection Function ·Sleep Function using SLEEPN terminal and Output Mute Function using MUTEN terminal Stereo/Monaural Switching Function ·Spread Clock Function • Pop Noise Reduction Function Package Lead-free 48-pin Plastic SQFP (Exposed stage) Lead-free 48-pin Plastic LQFP

Note) \*1: A value based on Yamaha's board implementation conditions (See Note \*2,\*3 of page 28)

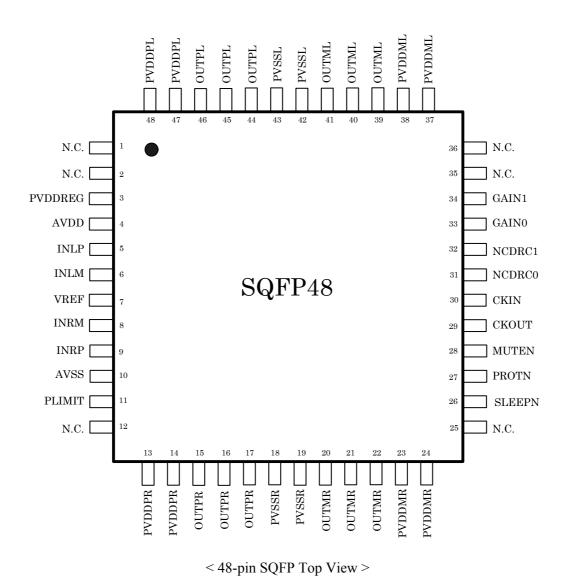

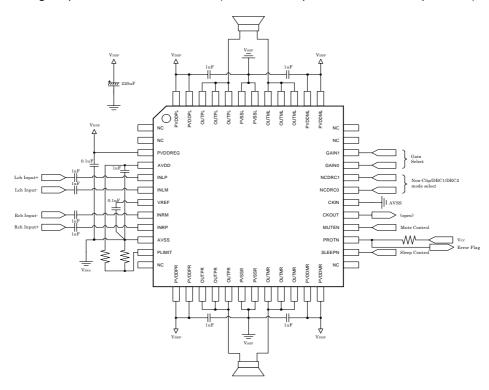

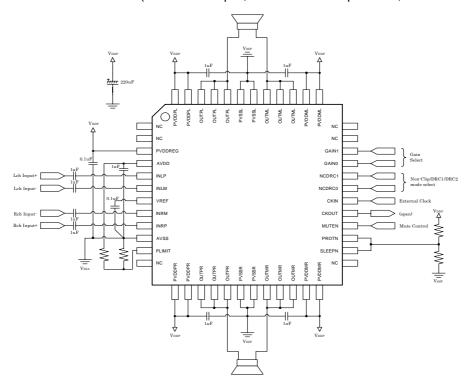

#### ■Terminal Configuration

CATALOG No.:LSI-4DA147A61

(Note) VSS pin should be connected to the ground pattern as wide as possible to improve the heat radiation.

#### ■Terminal Function

<48-pin SQFP >

| <48-pin SQI | FP>         |                   |                                                           |

|-------------|-------------|-------------------|-----------------------------------------------------------|

| No.         | Name *4)    | I/O *1), *2), *3) | Function                                                  |

| 1           | NC          | _                 | Normally, use this terminal with nothing connected.       |

| 2           | NC          |                   | Normally, use this terminal with nothing connected.       |

| 3           | PVDDREG     | PVDD              | Power supply terminal for regulators                      |

| 4           | AVDD        | OA                | 3.3V regulator output terminal                            |

| 5           | INLP        | IA                | Analog input terminal (Lch+)                              |

| 6           | INLM        | IA                | Analog input terminal (Lch-)                              |

| 7           | VREF        | OA                | Reference voltage output terminal                         |

| 8           | INRM        | IA                | Analog input terminal (Rch-)                              |

| 9           | INRP        | IA                | Analog input terminal (Rch+)                              |

| 10          | AVSS        | GND               | Analog ground terminal                                    |

| 11          | PLIMIT      | IA                | Power limit setting terminal                              |

| 12          | NC          | _                 | Normally, use this terminal with nothing connected.       |

| 13          | PVDDPR      | PVDD              | Power supply terminal for digital amplifier output (Rch+) |

| 14          | PVDDPR      | PVDD              | Power supply terminal for digital amplifier output (Rch+) |

| 15          | OUTPR       | 0                 | Digital amplifier output terminal (Rch+)                  |

| 16          | OUTPR       | 0                 | Digital amplifier output terminal (Rch+)                  |

| 17          | OUTPR       | 0                 | Digital amplifier output terminal (Rch+)                  |

| 18          | PVSSR       | GND               | Ground terminal for digital amplifier output (Rch)        |

| 19          | PVSSR       | GND               | Ground terminal for digital amplifier output (Rch)        |

| 20          | OUTMR       | 0                 | Digital amplifier output terminal (Rch-)                  |

| 21          | OUTMR       | 0                 | Digital amplifier output terminal (Rch-)                  |

| 22          | OUTMR       | 0                 | Digital amplifier output terminal (Rch-)                  |

| 23          | PVDDMR      | PVDD              | Power supply terminal for digital amplifier output (Rch-) |

| 24          | PVDDMR      | PVDD              | Power supply terminal for digital amplifier output (Rch-) |

| 25          | NC          | _                 | Normally, use this terminal with nothing connected.       |

| 26          | SLEEPN      | I                 | Sleep control terminal *5)                                |

| 27          | PROTN       | O/D               | Error flag output terminal                                |

| 28          | MUTEN       | l                 | MUTE control terminal                                     |

| 29          | CKOUT       | 0                 | Clock output terminal for synchronization                 |

| 30          | CKIN        | l                 | External clock input terminal                             |

| 31          | NCDRC0      |                   | Non-clip/DRC1/DRC2 mode selection terminal 0              |

| 32          | NCDRC1      | <u> </u>          | Non-clip/DRC1/DRC2 mode selection terminal 1              |

| 33          | GAIN0       | <u> </u>          | GAIN setting terminal 0                                   |

| 34          | GAIN1       | l                 | GAIN setting terminal 1                                   |

| 35          | NC<br>NC    | _                 | Normally, use this terminal with nothing connected.       |

| 36          | NC<br>DVDDM |                   | Normally, use this terminal with nothing connected.       |

| 37          | PVDDML      | PVDD              | Power supply terminal for digital amplifier output (Lch-) |

| 38          | PVDDML      | PVDD              | Power supply terminal for digital amplifier output (Lch-) |

| 39          | OUTML       | 0                 | Digital amplifier output terminal (Lch-)                  |

| 40          | OUTML       | 0                 | Digital amplifier output terminal (Lch-)                  |

| 41          | OUTML       | 0                 | Digital amplifier output terminal (Lch-)                  |

| 42          | PVSSL       | GND               | Ground terminal for digital amplifier output (Lch)        |

| 43          | PVSSL       | GND               | Ground terminal for digital amplifier output (Lch)        |

| 44          | OUTPL       | 0                 | Digital amplifier output terminal (Lch+)                  |

| 45          | OUTPL       | 0                 | Digital amplifier output terminal (Lch+)                  |

| 46          | OUTPL       | 0                 | Digital amplifier output terminal (Lch+)                  |

| 47          | PVDDPL      | PVDD              | Power supply terminal for digital amplifier output (Lch+) |

| 48          | PVDDPL      | PVDD              | Power supply terminal for digital amplifier output (Lch+) |

(Notes) \*1: I: Input terminal, O: Output terminal, A: Analog terminal, O/D: Open/Drain output terminal

CATALOG No.:LSI-4DA147A61

<sup>\*2:</sup> PVDD should be connected each other on a board.

<sup>\*3:</sup> GND should be connected each other on a board.

<sup>\*4:</sup> Each output terminal with the same name (OUTPR, OUTMR, OUTPL, and OUTML) should be connected on a board.

<sup>\*5:</sup> Don't use the terminal AVDD to apply "H" level to the terminal SLEEPN. When the terminal SLEEPN is "L" level, the terminal AVDD is not supplied.

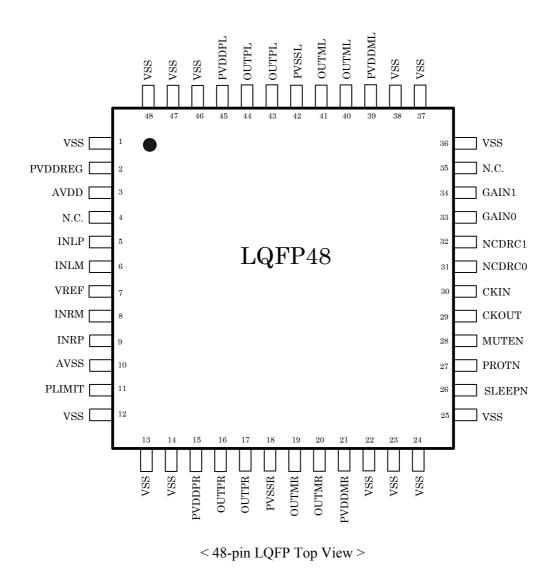

< 48-pin LOFP >

| < 48-pin LQ |          | 1/0 +4) +5) +5)   | - ·                                                        |

|-------------|----------|-------------------|------------------------------------------------------------|

| No.         | Name *4) | I/O *1), *2), *3) | Function                                                   |

| 1           | VSS      | GND               |                                                            |

| 2           | PVDDREG  | PVDD              | Power supply terminal for regulators                       |

| 3           | AVDD     | OA                | 3.3V regulator output terminal                             |

| 4           | NC       | _                 | Normally, use this terminal with nothing connected.        |

| 5           | INLP     | IA                | Analog input terminal (Lch+)                               |

| 6           | INLM     | IA                | Analog input terminal (Lch-)                               |

| 7           | VREF     | OA                | Reference voltage output terminal                          |

| 8           | INRM     | IA                | Analog input terminal (Rch-)                               |

| 9           | INRP     | IA                | Analog input terminal (Rch+)                               |

| 10          | AVSS     | GND               | Analog ground terminal                                     |

| 11          | PLIMIT   | IA                | Power limit setting terminal                               |

| 12          | VSS      | GND               |                                                            |

| 13          | VSS      | GND               |                                                            |

| 14          | VSS      | GND               |                                                            |

| 15          | PVDDPR   | PVDD              | Power supply terminal for digital amplifier output (Rch+)  |

| 16          | OUTPR    | 0                 | Digital amplifier output terminal (Rch+)                   |

| 17          | OUTPR    | 0                 | Digital amplifier output terminal (Rch+)                   |

| 18          | PVSSR    | GND               | Ground terminal for digital amplifier output (Rch)         |

| 19          | OUTMR    | 0                 | Digital amplifier output terminal (Rch-)                   |

| 20          | OUTMR    | 0                 | Digital amplifier output terminal (Rch-)                   |

| 21          | PVDDMR   | PVDD              | Power supply terminal for digital amplifier output (Rch-)  |

| 22          | VSS      | GND               |                                                            |

| 23          | VSS      | GND               |                                                            |

| 24          | VSS      | GND               |                                                            |

| 25          | VSS      | GND               |                                                            |

| 26          | SLEEPN   | I                 | Sleep control terminal *5)                                 |

| 27          | PROTN    | O/D               | Error flag output terminal                                 |

| 28          | MUTEN    | I                 | MUTE control terminal                                      |

| 29          | CKOUT    | 0                 | Clock output terminal for synchronization                  |

| 30          | CKIN     | I                 | External clock input terminal                              |

| 31          | NCDRC0   | I                 | Non-clip/DRC1/DRC2 mode selection terminal 0               |

| 32          | NCDRC1   | ı                 | Non-clip/DRC1/DRC2 mode selection terminal 1               |

| 33          | GAIN0    | ı                 | GAIN setting terminal 0                                    |

| 34          | GAIN1    | I                 | GAIN setting terminal 1                                    |

| 35          | NC       | _                 | Normally, use this terminal with nothing connected.        |

| 36          | VSS      | GND               | ,,                                                         |

| 37          | VSS      | GND               |                                                            |

| 38          | VSS      | GND               |                                                            |

| 39          | PVDDML   | PVDD              | Power supply terminal for digital amplifier output (Lch-)  |

| 40          | OUTML    | 0                 | Digital amplifier output terminal (Lch-)                   |

| 41          | OUTML    | 0                 | Digital amplifier output terminal (Lch-)                   |

| 42          | PVSSL    | GND               | Ground terminal for digital amplifier output (Lch)         |

| 43          | OUTPL    | 0                 | Digital amplifier output terminal (Lch+)                   |

| 44          | OUTPL    | 0                 | Digital amplifier output terminal (Lch+)                   |

| 45          | PVDDPL   | PVDD              | Power supply terminal for digital amplifier output (Lch+)  |

| 46          | VSS      | GND               | - Ower supply terminal for digital amplifier output (LCH+) |

| 47          | VSS      | GND               |                                                            |

| 48          | VSS      | GND               |                                                            |

| 40          | V 33     | GIND              |                                                            |

(Notes) \*1: I: Input terminal, O: Output terminal, A: Analog terminal, O/D: Open/Drain output terminal

<sup>\*2:</sup> PVDD should be connected each other on a board.

<sup>\*3:</sup> GND should be connected each other on a board.

<sup>\*4:</sup> Each output terminal with the same name (OUTPR, OUTMR, OUTPL, and OUTML) should be connected on a board.

<sup>\*5:</sup> Don't use the terminal AVDD to apply "H" level to the terminal SLEEPN. When the terminal SLEEPN is "L" level, the terminal AVDD is not supplied.

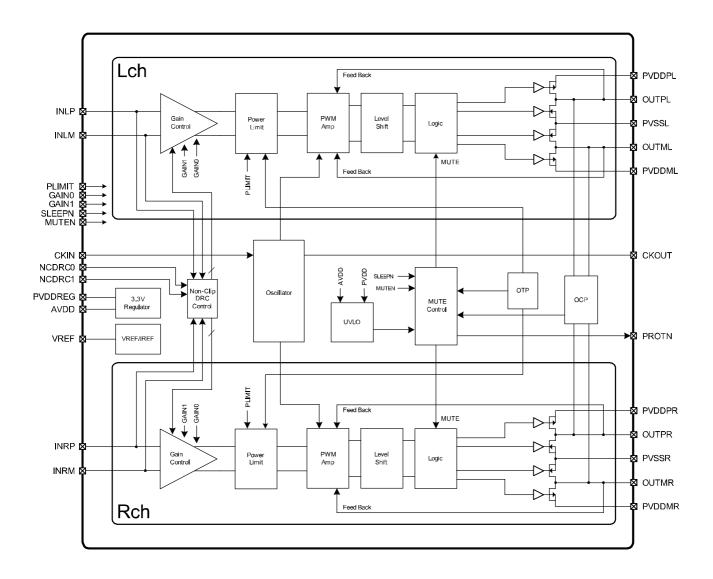

#### **■**Block Diagram

#### ■Functional Description

#### Digital Amplifier Function

YDA147 has digital amplifiers with analog input, PWM pulse output, the maximum output of 20W × 2ch. Adopting "Pure Pulse Direct Speaker Drive Circuit" reduces distortion and noise on PWM pulse output signal.

#### Digital Amplifier Gain

The total gain of the digital amplifier varies depending on operation modes, as shown below.

| NCDRC1 | NCDRC0 | GAIN1 | GAIN0 | Total Gain | Operation Mode |

|--------|--------|-------|-------|------------|----------------|

|        |        | L     | L     | +22dB      | Normal mode    |

| 1      |        | L     | Η     | +28dB      | Non-clip: OFF  |

| _      | _      | Ι     | L     | +34dB      | DRC: OFF       |

|        |        | Ι     | Η     | +16dB      | DIG. OF I      |

|        |        | L     | L     | +34dB      |                |

| 1      | Н      | L     | Η     | +40dB      | Non-clip mode  |

| _      | 11     | Ι     | L     | +46dB      | Non-clip mode  |

|        |        | H     | Η     | +28dB      |                |

|        |        | L     | L     | +34dB      |                |

| н      |        | L     | Η     | +40dB      | DRC1 mode      |

| ''     | _      | Ι     | L     | +46dB      | DRCTIIIode     |

|        |        | H     | Η     | +28dB      |                |

|        |        | L     | L     | +34dB      |                |

| Н      | Н      | L     | Η     | +40dB      | DRC2 mode      |

| ''     | ''     | H     | Ĺ     | +46dB      | DIVOZ IIIOGE   |

|        |        | Н     | Н     | +28dB      |                |

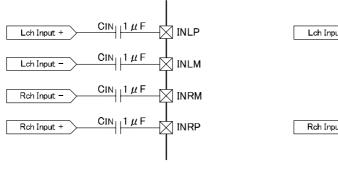

#### · Audio Signal Input

For a differential input, the signal should be input to INLP and INLM terminals (Lch) and to INRP and INRM terminals (Rch) through a DC-cut capacitor ( $C_{IN}$ ).

On the contrary, for a single-ended input, the signal should be input to INLP terminal (Lch) and to INRP terminal (Rch) through a DC-cut capacitor ( $C_{IN}$ ). At this time, INLM and INRM terminals should be connected to AVSS through DC-cut capacitors ( $C_{IN}$ ) with the same value.

Input terminal connection in a differential input

$\begin{array}{c|c} \text{CiN} & 1 \ \mu \ \text{F} \\ \hline \\ \text{CiN} & 1 \ \mu \ \text{F} \\ \hline \\ \text{CiN} & 1 \ \mu \ \text{F} \\ \hline \\ \text{Rch Input} + \\ \hline \\ \text{CIN} & 1 \ \mu \ \text{F} \\ \hline \\ \text{AVSS} \\ \end{array}$

Input terminal connection in a single-ended input

In the differential input mode, use signal sources with the same impedance to reduce pop-noise. Its value should be  $10k\Omega$  or less. Use a DC-cut capacitor ( $C_{IN}$ ) of  $1\mu F$ . (The capacitance value should be less than  $1.5\mu F$  throughout the operating temperature range.)

#### (Cautions)

When inputting audio signals in Power-off state (  $PVDD < V_{HUVLL}$  ) or Sleep state, current may flow toward the former device from YDA147's ground, through each protection circuit of analog pins (INLP, INLM, INRP, and INRM). For this reason, audio signals should not be input in Power-off state (  $PVDD < V_{HUVLL}$  ) or Sleep state.

#### Input Impedance

The input impedance ( $Z_{IN}$ ) is  $18.8k\Omega$  regardless of a Gain setting.

#### • Reference Voltage Output Function

Half a voltage of AVDD terminal is output to the reference voltage terminal (VREF). Connect a capacitor of 0.1 µF for voltage stabilization.

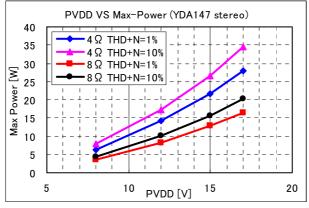

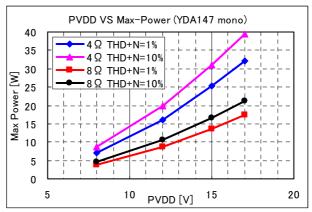

#### Maximum Output

The output varies depending on load impedance and a supply voltage, as shown below.

Maximum Momentary Output:

$20W \times 2ch$  (PVDD=14V,  $R_L$ =4 $\Omega$ , THD+N=10%)  $15W \times 2ch$  (PVDD=12V,  $R_L$ =4 $\Omega$ , THD+N=10%)

Maximum Continuous Output:

$15W \times 2ch \ (V_{DDP}=15V, \ R_L=8\Omega, \ THD+N=10\%, \ Ta=70^{\circ}C, \ SQFP48, \ 4-layer \ board) \\ 10.5W \times 2ch \ (V_{DDP}=15V, \ R_L=4\Omega, \ THD+N=10\%, \ Ta=25^{\circ}C, \ SQFP48, \ 4-layer \ board) \\ 10W \times 2ch \ (V_{DDP}=12V, \ R_L=8\Omega, \ THD+N=10\%, \ Ta=25^{\circ}C, \ LQFP48, \ 1 \ layer \ board)$

The maximum momentary output means a possible maximum output by considering heat problems due to power loss separately.

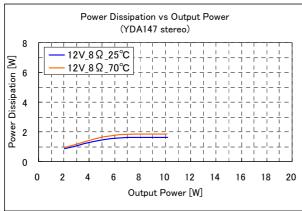

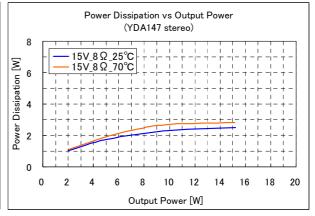

The maximum continuous output means a maximum output with Tjmax not exceeding 150°C at a given temperature while outputting a sine wave continuously. In addition, this value is based on Yamaha's board implementation conditions. (See Note \*2, \*3 at Page 28)

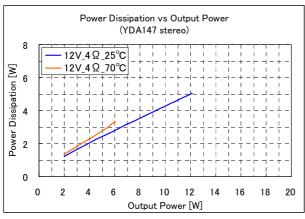

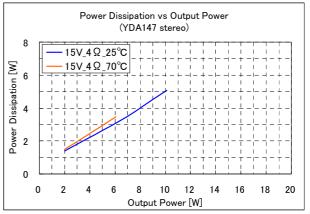

A possible maximum continuous output in other settings can be converted by the following data:

- 1. Graph of Power Dissipation vs Output Power of Example of typical characteristics. (See Page 32)

- 2. Power Dissipation of Electrical Characteristics. (See Page 28)

#### Control Function

#### Output Power limit Function

This is the function to set a voltage at which the output is clipped.

At this time, a value at which the output is clipped is defined as a power limit value  $(V_{PL})$ .

Using this function prevents increase of temperature in a device as well as allowing the maximum output power to be limited.

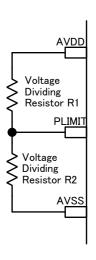

The output power limit value is determined by a voltage (voltage dividing resistor 1, 2) applied to PLIMIT terminal.

In addition, changing the voltage at PLIMIT terminal during power-on is prohibited.

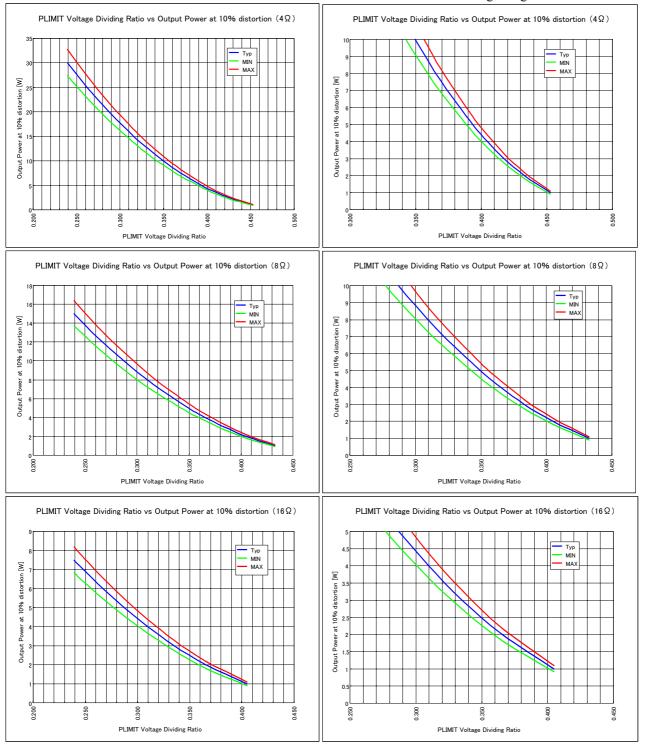

The relation between a resistor ratio (R2/(R1+R2)(between voltage dividing resistor 1 and 2) and an output power with a 10% distortion is shown below.

Since it may vary between MIN and MAX due to variation of internal AVDD, select resistors in consideration of the variation.

The setting values shown here are common to stereo and monaural mode.

PLIMIT resistor R1 and R2 should be set as follows.

R1+R2=500k $\Omega$  or less

$R1/\!/R2\!=\!\!50k\Omega$  to  $70k\Omega$  (R1//R2 means a parallel resistance between R1 and R2)

Example 1:  $4\Omega \max 30W (8\Omega \max 15W)$

R1=220k+4.7k, R2=75kExample 2:  $8\Omega \min 10W$ R1=200k, R2=75k+1.5k

PLIMIT terminal setting circuit

## **YDA147**

\* Minimum value restriction on the output power limit.

The minimum value of the output-power limit values is restricted by the value determined with the resistance voltage division ratio of "0.45."

Even though the resistance voltage division ratio is set beyond "0.45," the output-power limit value wouldn't be set lower.

\* Cancellation of the output power limit function.

It is possible to disable the power limit by setting "0"V (voltage division ratio "0") to the PLIMIT pin.

However, it is necessary to set the power limit value when the following function is used.

- · Non-clip function (Non-clip/DRC Function: P.11).

- · DRC function (Non-clip/DRC Function : P.11).

- High Temperature Power Limiter State of High Temperature Protection (High Temperature Protection Function: P.20).

For the relation between each function and the power limit value, see the item of each function.

#### **Enlarged Figures**

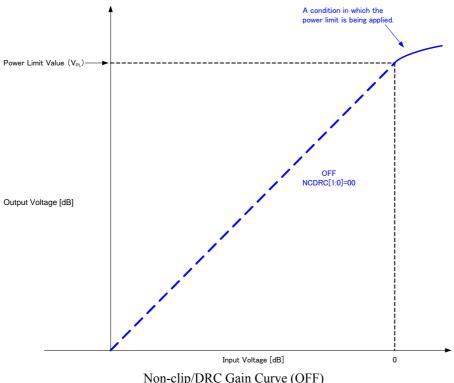

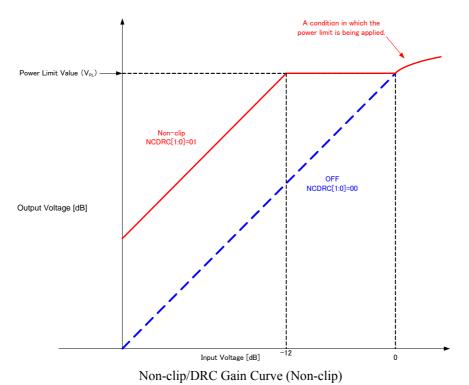

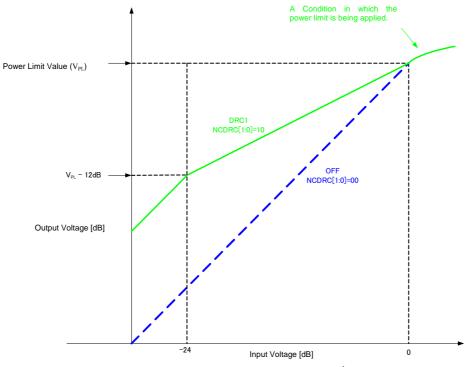

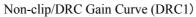

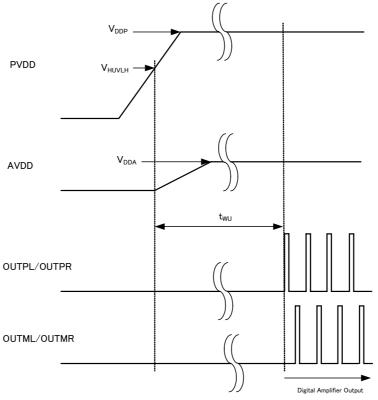

#### ·Non-clip/DRC Function

This is the function to change the gain by detecting an input level to the PWM amplifier and to raise an average output level while suppressing clipping.

A mode is determined by the combination of NCDRC[1:0] terminals, as shown below.

| NCDRC1 | NCDRC0 | Mode                    |

|--------|--------|-------------------------|

| L      | L      | Non-clip & DRC mode OFF |

| L      | Н      | Non-clip mode           |

| Н      | L      | DRC1 mode               |

| Н      | Н      | DRC2 mode               |

In Non-clip mode, the gain increases by 12dB. The gain is automatically adjusted so that an output peak voltage becomes a power limit value. The maximum attenuation is -12dB. Attack Time is 0 second. The release time from -12dB to 0dB is 7.7 s (typ.).

In DRC1 mode, the gain increases by 12dB. Dynamic Range Compression (a half of gain in dB) is performed within an output range of -12dB (-24dB for input range) from the power limit value. Attack Time is 0 s. The release time from -12dB to 0dB is 3.9 s (typ.).

In DRC2 mode, the gain increases by 12dB. As with DRC1, similar compression is performed, but power-limit operation is not performed. PLIMIT terminal can be used to set a DRC operating point. Therefore, the setting of a gain curve is possible regardless of the maximum output power, and this allows for DRC operation from a low output power. NCDRC [1:0] terminal should be switched under either of the following conditions.

- •Before PVDD power-on (lower than the PVDD start-up threshold voltage (V<sub>HUVLH</sub>))

- ·SLEEPN=L

Pop noise may occur when switching it under an operating condition other than the above.

Non-clip/DRC Gain Curve (OFF)

CATALOG No.:LSI-4DA147A61

#### · Sleep Function

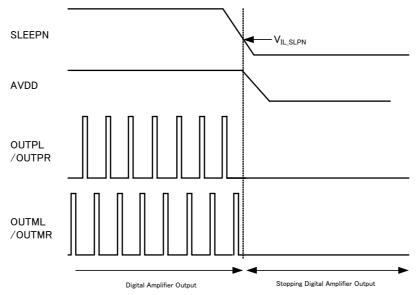

YDA147 shifts into sleep mode when SLEEPN terminal goes to "L" level.

In the sleep mode, all functions stop and consumption current is minimized (I<sub>SLEEP</sub>).

When shifting into sleep mode during any protection mode, the protection mode is cancelled and PROTN terminal output becomes Hi-Z state.

The digital amplifier output becomes Weak Low (a state grounded through a high resistance).

AVDD and VREF outputs are pulled down.

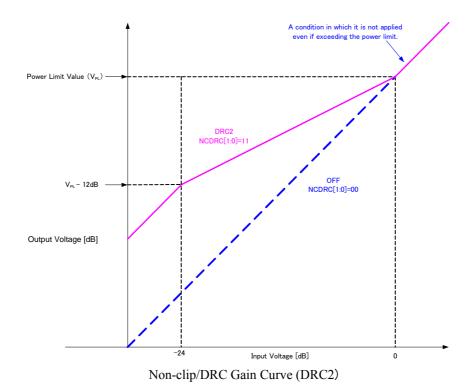

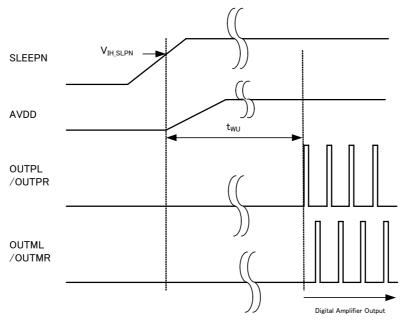

When the level at SLEEPN terminal is changed from "L" to "H" under the condition that the voltage at PVDDREG terminal is higher than the threshold voltage ( $V_{HUVLH}$ ) for low voltage malfunction prevention cancellation, the sleep mode is cancelled and the state shifts into the normal operation state after the period of sleep recovery time ( $t_{WU}$ ).

#### Mute Function

YDA147 shifts into mute mode when MUTEN terminal goes to "L" level.

In the mute mode, the digital amplifier output becomes Weak Low (a state grounded through a high resistance).

When the level at MUTEN terminal is changed from "L" to "H" under the condition that the voltage at PVDDREG terminal is higher than the threshold voltage ( $V_{HUVLH}$ ) for low voltage malfunction prevention cancellation and state of SLEEPN terminal=H, the mute mode is cancelled and the state shifts into the normal operation state after the period of mute recovery time ( $t_{MRCV}$ ).

#### Clock Control Function

The setting of CKIN terminal controls the clock mode as shown below.

| CKIN terminal Setting | Mode                               | CKOUT                                                       |

|-----------------------|------------------------------------|-------------------------------------------------------------|

| L fixed               | Internal Clock mode                | Internal Clock (frequency: f <sub>CK</sub> ) output         |

| H fixed               | Internal Clock (Spread clock) mode | Internal Clock (Spread Clock) frequency: (f <sub>CK</sub> ) |

|                       |                                    | output                                                      |

| Clock input           | External Clock mode                | CKIN input buffer output (frequency: f <sub>CKIN</sub> )    |

When CKIN terminal is held L or H level, internal clock mode is selected to generate a clock internally.

And, when CKIN terminal is held H level, Spread Clock function operates to reduce EMI.

When an external clock is input to CKIN terminal, its frequency should be  $f_{CKIN}$ .

Do not use with CKIN terminal left open.

#### Stereo/Monaural Switching Function

When INRP and INRM terminals (Rch input) are connected to AVDD, monaural mode is selected.

In the monaural mode, input signals input to INLP and INLM terminals (Lch input) are output from Lch and Rch digital amplifiers.

With the monaural mode, parallel operation can be realized by connecting OUTPL to OUTPR and connecting OUTML to OUTMR.

For details of connections, see "Single operation in monaural mode" (See page 24) in the "Examples of Application Circuits."

The switching between stereo and monaural modes should be performed under the following conditions.

• Before PVDD power-on (lower than the PVDD shutdown threshold voltage)

#### Digital Amplifier Pop Noise Reduction Function

Pop noise that may occur at the power-on, power-off, power-down, and power-down cancel operations, etc. is reduced by minimizing an output offset voltage.

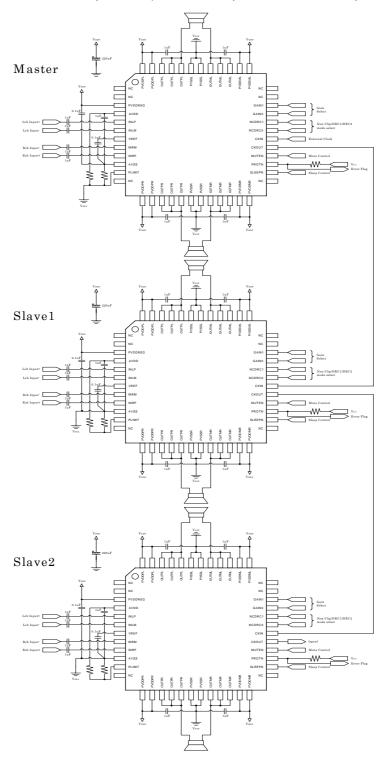

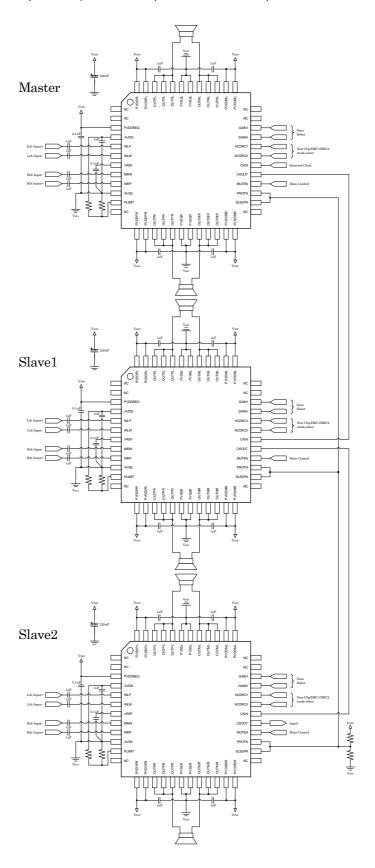

#### Multi-chip Synchronization Function

The external clock synchronization function and clock output function are prepared and the use of master/slave configuration realizes carrier clock synchronization.

When using it with multi chips synchronized, one is used as a master chip and the other is used as a slave chip. At this time, connect CKOUT terminal of a master chip to CKIN terminal of a slave chip.

When using 3 chips (master/slave1/slave2), connect CKOUT terminal of a slave1 chip to CKIN terminal of a slave2 chip. For details of connections, see "MASTER-SLAVE operation" (See page 26 and 27) in the "Examples of Application Circuits."

PVDD pins should be connected each other on a board.

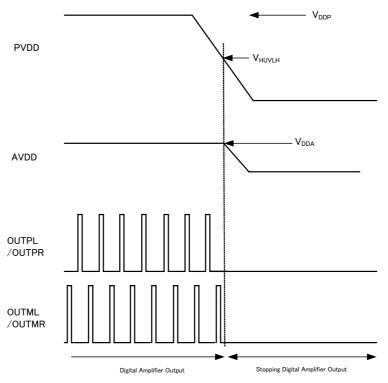

·Startup Sequence, Shutdown Sequence

Power Supply Startup Sequence

Power Supply Shutdown Sequence

Startup Sequence from Sleep State

Transient Sequence to Sleep State

#### Regulator Output

When SLEEPN terminal is at H, YDA147 outputs  $V_{DDA}$  to AVDD terminal. Connect a capacitor of  $1\mu F$  to  $4.7\mu F$  to AVDD terminal for stabilization. (0.8 $\mu F$  or more should be secured including its variation and temperature change.) AVDD output must be used only for YDA147. If this output is used in a peripheral circuit of YDA147, the maximum current that can be driven will be  $I_{DDA}$ .

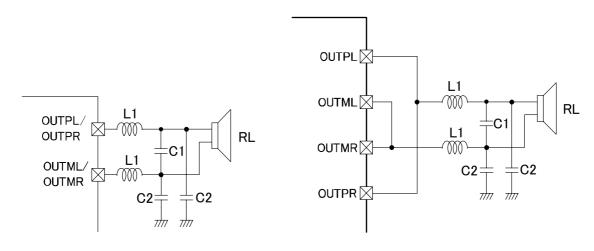

#### ●LC Filter

YDA147 adopts the modulation method that reduces speaker loss sufficiently at mute state by the use of only an inductance the speaker has, and this allows for direct connection to a speaker without an LC filter.

When an LC filter is used, use the LC filter circuits shown below. At this time, the following constant should be used according to an impedance of a speaker. Using these constants makes a low-pass filter with a cut-off frequency of 50kHz or so, Q=0.7 or so.

#### LC filter constants:

| RL | L1            | C1       | C2             |

|----|---------------|----------|----------------|

| 4Ω | 10 <i>μ</i> Η | 0.33 μ F | 0.22 μ F       |

| 8Ω | 22 μ H        | 0.22 μ F | 0.1 <i>μ</i> F |

LC Filter circuit (Stereo)

LC Filter circuit (Monaural)

\* With use of LC filters, if there is a possibility of not using a speaker, audio signals within 20kHz should be input. And, if its band limitation is not possible, remove the speaker under the following conditions: SLEEPN terminal = L or MUTEN terminal = L, or PVDD = Power Off.

#### Speaker Inductance

In the following cases, use a speaker with an inductance of  $20\mu H$  or more (at around the switching frequency ( $f_{CKIN}$  or  $f_{CK}$ )).

- 1. Direct connection of a speaker to an output pin of the digital amplifier without an LC filter.

- 2. Connection of a speaker to a position after components for EMI measures such as ferrite beads etc. (filterless). With an inductance of less than  $20\mu H$ , power loss in the speaker and this device may increase.

#### Protection Function

YDA147 has the following four digital amplifier protection functions: overcurrent protection function, high temperature protection function, low voltage malfunction prevention function, and DC detection function.

| Protection Functions             | PROTN    | PROTN       | Digital Amplifier | Protection Mode Cancel |

|----------------------------------|----------|-------------|-------------------|------------------------|

|                                  | terminal | terminal    | Output State      |                        |

|                                  | Output   | Latch       |                   |                        |

| Over current                     | Low      | Latabad     | WL*1)             | SLEEPN terminal=L or   |

| Protection Function              | Low      | Latched     | VVL '             | PVDD shutdown          |

| High Temperature                 |          |             | Power Limit       | SLEEPN terminal=L or   |

| Protection Function              | _        | Not latched | (-6dB)            | PVDD shutdown or       |

| (High Temp. power limiter state) |          |             | (-6ub)            | lower temperature      |

| High Temperature                 |          |             |                   | SLEEPN terminal=L or   |

| Protection Function              | Low      | Not latched | WL <sup>*1)</sup> | PVDD shutdown or       |

| (High Temp. shutdown state)      |          |             |                   | lower temperature      |

| Low Voltage Malfunction          | /LI; 7\  | _           | WL*1)             | _                      |

| Prevention Function              | (Hi-Z)   | _           | VVL '             | _                      |

| DC Detection Function            | Low      | Latched     | WL*1)             | SLEEPN terminal=L or   |

| DC Detection Function            | LOW      | Laterieu    | VVL '             | PVDD shutdown          |

<sup>\*1:</sup> WL=Weak Low (a state grounded with a high resistance)

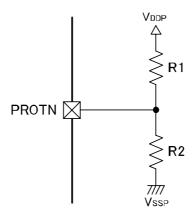

Use a circuit as shown below when pulling up PROTN terminal output externally.

1) Pull up the terminal to a voltage obtained by dividing the voltage between PVDD and GND with voltage-dividing resistors.

Find values with reference to the following formula so that a voltage at the terminal becomes 3.3V or less when PROTN terminal is in "H" output (Hi-Z).

$$2.0V \ \leq \ (R2 \ / \ (R1 + R2)) \times V_{DDP} \ \leq \ 3.3V \quad \ ; however, \ R1 > 100 k\Omega, \ 10 k\Omega < R2 < 100 k\Omega$$

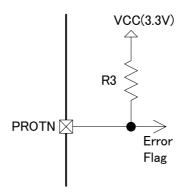

2) The pull-up should be performed to an external supply voltage lower than 3.3V. The pull-up resistor R3 should be a value as follows.  $40k\Omega < R3 < 200k\Omega$  (47k $\Omega$  is recommended.)

In each case, select these values so that 0.4mA or more current will not flow into the terminal while PROTN terminal is in L state.

PROTN terminal Pull-Up Connection 1 (A pull-up to PVDD)

PROTN terminal Pull-Up Connection 2 (A pull-up to 3.3V)

- \* If automatic return setting is given by connecting PROTN terminal to SLEEPN terminal, use a separate power supply as VCC, not the same power supply as AVDD.

- \* When VCC is used as AVDD, see Startup Sequence (page 14 and 15).

#### Digital Amplifier Over current Protection Function

This is the function to protect the device by detecting short-circuiting (to the supply voltage, to the ground, and between terminals) at digital amplifier output terminals.

In the protection mode, PROTN terminal becomes L level and output terminals become Weak Low state (a state grounded through a high resistance).

The protection mode can be cancelled by turning off the power supply or inputting an L level signal to SLEEPN terminal momentarily.

And, when PROTN terminal is externally connected to SLEEPN terminal, automatic return mode is selected. At this time, the protection mode is cancelled even if the protection mode is established by detecting an overcurrent state, and PROTN terminal output is turned from L level into Hi-Z state and a normal operation state is given after a given standby time (t<sub>WU</sub>). (Automatic Return Function)

The current value to detect a short-circuiting between terminals is 8A (typ,V<sub>DDP</sub>=12V), 10A (typ,V<sub>DDP</sub>=15V).

#### High Temperature Protection Function

This is the function to protect the device by detecting an unusual temperature in YDA147.

The protection mode operates in the following two modes according to the temperature.

#### 1) High Temperature Power Limiter State

If the temperature rises and reaches 155°C (typ.), the high temperature power limiter state is given. This state decreases the power limit level by 6dB in order to limit the digital amplifier output power, and attempts to lower the temperature.

In this way, when the temperature falls and lowers than 130°C (typ.), the high temperature power limiter state is automatically cancelled and the gain is restored to the original setting value.

In the power limiter state, this does not affect on PROTN terminal.

#### 2) High Temperature Shutdown State

If the temperature rises and reaches 165°C (typ.) during the high temperature power limiter state, the high temperature cutoff state is given. This state outputs an L level signal from PROTN terminal and digital amplifier output terminals become Weak Low state (a state grounded through a high resistance).

In this way, when the temperature goes down and lowers than  $130^{\circ}$ C (typ.), the high temperature shutdown state is automatically cancelled.

And, even if the cutoff state is established by detecting an unusual temperature, when PROTN terminal is externally connected to SLEEPN terminal, the cutoff state is cancelled and PROTN terminal output is turned from L into Hi-Z state and a normal operation state is given if the temperature is sufficiently lowered after a given standby time (t<sub>WU</sub>). (Automatic Return Function)

If the temperature is not sufficiently lowered, the high temperature protection mode will be established.

#### Low Voltage Malfunction Prevention Function

This is the function to protect the device when the supply voltage at PVDDREG terminal is unusually lowered.

In this protection mode, the digital amplifier output terminals become Weak Low state (a state grounded through a high resistance).

This protection mode is given if the supply voltage at PVDDREG terminal becomes a voltage lower than PVDD shutdown threshold voltage ( $V_{HUVLL}$ ).

When the supply voltage at PVDDREG terminal exceeds PVDD startup threshold voltage ( $V_{HUVLH}$ ), the protection mode is cancelled and a normal operation mode is given after a given standby time ( $t_{WU}$ ). (Automatic Return Function)

## **YDA147**

#### DC Detection Function

This is the function to protect the speaker connected to the digital amplifier output when a DC signal is continuously output from the digital amplifier.

When MUTEN terminal=L, the DC detection function is disabled.

When a voltage in excess of a given time  $(t_{DCDET})$  and a given level  $(V_{DCDET})$  is output to the digital amplifier output, the DC detection mode is given. This state outputs an L level signal from PROTN terminal and digital amplifier output terminals become Weak Low state (a state grounded through a high resistance).

Once the DC detection mode is given, an L level signal keeps outputting from PROTN terminal even if the DC output state is cancelled. The protection mode is cancelled by turning off the power supply or inputting an L level signal to SLEEPN terminal momentarily.

And, even if DC protection mode is established by detecting a DC signal, when PROTN terminal is externally connected to SLEEPN terminal, the protection mode is cancelled and PROTN terminal output is turned from L into Hi-Z state and a normal operation state is given after a given standby time  $(t_{WU})$ .

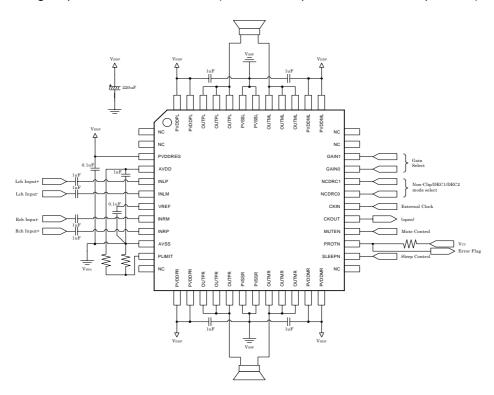

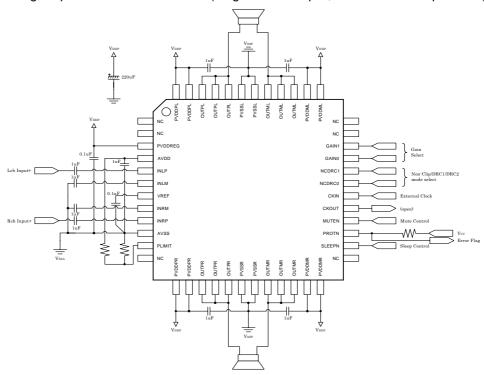

#### ■ Examples of Application Circuits

#### (Caution)

- $\cdot$ A ceramic capacitor of  $1\mu F$  should be used as a bypass capacitor between the following terminals: PVDDPL-PVSSL, PVDDML-PVSSL, PVDDPR-PVSSR, and PVDDMR-PVSSR. Please mount the capacitor as close as possible to each terminal.

- •A former-stage impedance of input terminals should be  $10k\Omega$  or less.

- •Select resistor values so that a voltage becomes 2.0V to 3.3V when PROTN terminal is at H level and current becomes 0.4mA or less when PROTN terminal is at L.

- •For PLIMIT terminal setting, see page 8 and 9.

- For a pull-up resistor for PROTN terminal, see page 18 and 19.

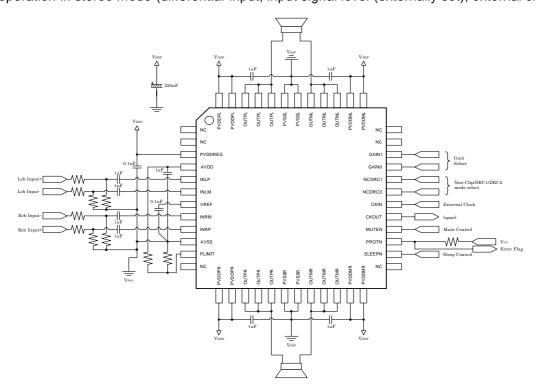

#### Single operation in stereo mode (differential-input, external clock operation)

:

Single operation in stereo mode (single-ended input, external clock operation)

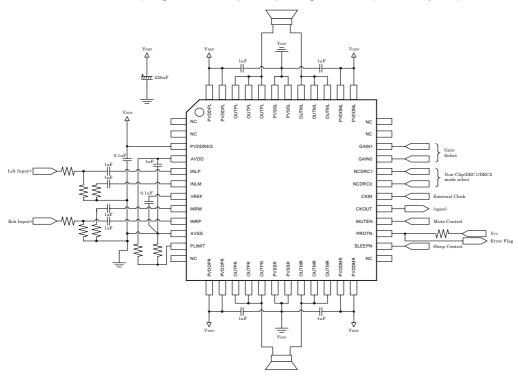

Single operation in stereo mode (differential-input, input signal level (externally set), external clock operation)

Single operation in stereo mode (single-ended input, input signal level (externally set), external clock operation)

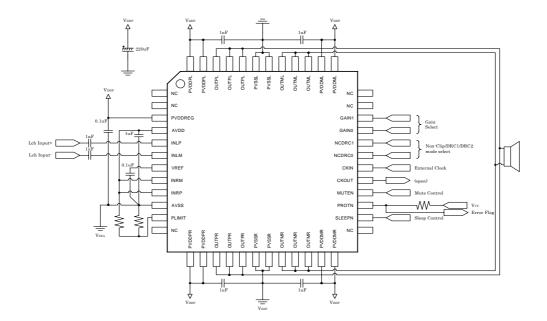

Single operation in monaural mode (differential-input, external clock operation)

Single operation in stereo mode (differential-input, external clock operation, automatic return setting)

MASTER-SLAVE operation (differential-input, external clock operation)

MASTER-SLAVE operation (differential-input, external clock operation, automatic return setting)

#### ■ Electrical Characteristics

• Absolute Maximum Ratings \*1)

|                              |                             | Parameter                   | Symbol             | Min. | Max.                | Unit |

|------------------------------|-----------------------------|-----------------------------|--------------------|------|---------------------|------|

| Power Su                     | pply termir                 | nal (PVDD) Voltage Range    | $V_{\mathrm{DDP}}$ | -0.3 | 20                  | V    |

| Input Ter                    | minal Volta                 | age Range                   | $V_{\rm IN}$       | -0.3 | 4                   | V    |

| PROTN Terminal Voltage Range |                             | $V_{PROTN}$                 | -0.3               | 4    | V                   |      |

|                              | Power Dissipation (Ta=25°C) |                             | $P_{\mathrm{D25}}$ |      | 6.5 <sup>*2)</sup>  | W    |

|                              | 4 layers                    | Power Dissipation (Ta=70°C) | $P_{\mathrm{D70}}$ |      | 4.21*2)             | W    |

| SQFP48                       |                             | Power Dissipation (Ta=85°C) | $P_{\mathrm{D85}}$ |      | 3.4 <sup>*2)</sup>  | W    |

| 3QFF46                       |                             | Power Dissipation (Ta=25°C) | $P_{\mathrm{D25}}$ |      | 3.72 <sup>*3)</sup> | W    |

|                              | 2 layers                    | Power Dissipation (Ta=70°C) | $P_{\mathrm{D70}}$ |      | 2.38*3)             | W    |

|                              |                             | Power Dissipation (Ta=85°C) | $P_{D85}$          |      | 1.93*3)             | W    |

|                              |                             | Power Dissipation (Ta=25°C) | $P_{\mathrm{D25}}$ |      | $2.67^{*4}$         | W    |

| LQFP48                       | 1 layer                     | Power Dissipation (Ta=70°C) | $P_{\mathrm{D70}}$ |      | 1.70*4)             | W    |

|                              |                             | Power Dissipation (Ta=85°C) | $P_{D85}$          |      | 1.38*4)             | W    |

| Junction                     | Temperatur                  | re                          | $T_{JMAX}$         |      | 150                 | °C   |

| Storage T                    | emperature                  | <del>-</del>                | $T_{STG}$          | -40  | 150                 | °C   |

- Note) \*1: Absolute Maximum Ratings is values which must not be exceeded to guarantee device reliability and life, and when using a device in excess even a moment, it may immediately cause damage to device or may significantly deteriorate its reliability.

- \*2: A value based on the following implementation conditions:

Board Layer: 4 layers (FR-4), Board Size: 136 [mm] × 85 [mm], Board Copper Foil Thickness: 35 [µm], Wiring Density: 379%, Exposed stage: soldering on the board

Through Hole for heat radiation:  $25 (5 \times 5)$  holes from a point just below the exposed stage to the inner layer (VSS) and B layer.

\*3: A value based on the following implementation conditions:

Board Layer: 2 layers (FR-4), Board Size: 136 [mm]  $\times$  85 [mm], Board Copper Foil Thickness: 35 [ $\mu$ m],

Wiring Density: 187%, Exposed stage: soldering on the board

Through Hole for heat radiation: 25 (5×5) holes from a point just below the exposed stage to B layer.

\*4: 1 layer board, Copper Foil Thickness: 35 [µm], Wiring Density: 80%, Board Size: 114.3 [mm] × 76.2 [mm]

Recommended Operating Condition

| Parameter                                  | Symbol       | Min. | Тур. | Max. | Unit |

|--------------------------------------------|--------------|------|------|------|------|

| Power Supply Voltage (PVDD)                | $V_{ m DDP}$ | 8    | -    | 16.5 | V    |

| Digital terminals*1) H level input voltage | $V_{\rm IN}$ | 2.52 | 3.3  | 3.6  | V    |

| SLEEPN terminal H level input voltage      | $V_{\rm IN}$ | 2.0  | 3.3  | 3.6  | V    |

| Operating Ambient Temperature              | Ta           | -40  | 25   | 85   | °C   |

| Speaker Impedance (Stereo)                 | $R_{\rm L}$  | 3.6  | 4    | -    | Ω    |

| Speaker Impedance (Monaural) *2)           | $R_{L}$      | 3.6  | 4    | -    | Ω    |

Note) \*1: This specification is applicable to MUTEN, CKIN, NCDRC0, NCDRC1, GAIN0, and GAIN1(CMOS I/F) pins

<sup>\*2:</sup> Connect terminals between OUTPL and OUTPR and between OUTML and OUTMR before use.

●DC Characteristics (V<sub>SS</sub>=0V, V<sub>DDP</sub>=8V to 16.5V, Ta=-40°C to 85°C, CKIN=1MHz, unless otherwise specified.)

| Parameter                                                  | Symbol               | Conditions                     | Min. | Тур.            | Max. | Unit |

|------------------------------------------------------------|----------------------|--------------------------------|------|-----------------|------|------|

| PVDD Startup threshold voltage                             | $V_{HUVLH}$          | -                              | -    | 6.5             | -    | V    |

| PVDD Shutdown threshold voltage                            | $V_{\mathrm{HUVLL}}$ | -                              | -    | 6.0             | -    | V    |

| DC Detection Voltage                                       | $V_{DCDET}$          | PVDD=15V                       | -    | 4               | -    | V    |

| DC Detection Time                                          | $t_{ m DCDET}$       | -                              | i    | 0.5             | -    | S    |

| Digital terminal*1) H level input voltage                  | $ m V_{IH}$          | -                              | 2.52 | -               | =    | V    |

| Digital terminal*1) L level input voltage                  | $ m V_{IL}$          | -                              | -    | -               | 0.9  | V    |

| Digital terminal *1) Input Impedance                       | $R_{\rm IN\ D}$      | -                              | 3.3  | -               | -    | ΜΩ   |

| SLEEPN terminal H level input voltage                      | $V_{\text{IH SLPN}}$ | -                              | 2.0  | -               | -    | V    |

| SLEEPN terminal L level input voltage                      | $V_{\rm IL\ SLPN}$   | -                              | -    | -               | 0.8  | V    |

| SLEEPN terminal Input Impedance                            | R <sub>IN SLPN</sub> | -                              | 3.3  | -               | -    | ΜΩ   |

| CKOUT Output Voltage                                       | $V_{ m OL}$          | I <sub>OL</sub> =4mA           | ı    | -               | 0.4  | V    |

| CKOUT Output Voltage                                       | $V_{\mathrm{OH}}$    | $I_{OH}$ =-4mA                 | 2.4  | -               | -    | V    |

| PROTN Output Voltage                                       | $V_{OL}$             | $I_{OL}=0.4$ mA                | Ī    | -               | 0.4  | V    |

| INLP, INLM, INRP, INRM terminals Input impedance           | $R_{\mathrm{IN}}$    | -                              | -    | 18.8            | -    | kΩ   |

| AVDD Output Voltage                                        | $V_{\mathrm{DDA}}$   |                                | 3.0  | 3.3             | 3.6  | V    |

| AVDD Output Current                                        | $I_{DDA}$            |                                | ı    | -               | 1    | mA   |

| VREF Output Voltage                                        | $V_{ m REF}$         |                                | Ī    | $V_{\rm DDA}/2$ | -    | V    |

| PVDD Consumption Current                                   | $I_{\mathrm{DDP}}$   | V <sub>DDP</sub> =12V, no-load | -    | 32              | -    | mA   |

| PVDD consumption current during power-down mode (SLEEPN=L) | $I_{SLEEP}$          | V <sub>DDP</sub> =15V, Ta=25°C | -    | 20              | -    | μΑ   |

| PVDD consumption current during Mute state (MUTEN=L)       | $I_{MUTE}$           | V <sub>DDP</sub> =15V, Ta=25°C | -    | 16              | -    | mA   |

| PVDD consumption current during no signal input            | $I_{NOSIG}$          | V <sub>DDP</sub> =15V, Ta=25°C | -    | 32              | -    | mA   |

Note) \*1: This specification is applicable to MUTEN, CKIN, NCDRC0, NCDRC1, GAIN0, and GAIN1 (CMOS I/F) terminals.

●AC characteristics (V<sub>SS</sub>=0V, V<sub>DDP</sub>=8V to 16.5V, Ta=-40°C to 85°C, CKIN=1MHz, unless otherwise specified.)

| Parameter                    | Symbol       | Min. | Тур. | Max. | Unit |

|------------------------------|--------------|------|------|------|------|

| CKIN Input Frequency         | $f_{CKIN}$   | 0.9  | 1,0  | 1.1  | MHz  |

| CKIN Input Duty              | $DT_{CKEXT}$ | 40   | -    | 60   | %    |

| Self-excited Clock Frequency | $f_{CK}$     | ı    | 1.0  | -    | MHz  |

| Sleep Recovery Time          | $t_{ m WU}$  | Ī    | 1    | 1.5  | S    |

| Mute Recovery Time           | $t_{MRCV}$   | -    | -    | 1    | ms   |

Analog Characteristics

(V<sub>SS</sub>=0V, V<sub>DDP</sub>=12V, Ta=25°C, GAIN[1:0]=L,L, NCDRC[1:0]=L,L, CKIN= CKIN= L<sup>\*2)</sup>, unless otherwise specified.)

| Parameter                                              | Symbol    | Conditions                                    | Min. | Тур. | Max. | Unit  |

|--------------------------------------------------------|-----------|-----------------------------------------------|------|------|------|-------|

| Mariana and an order                                   |           | $R_L=4\Omega$ , $V_{DDP}=12V$ , THD+N=10%     |      | 15   |      | W     |

| Maximum momentary Output (stereo)                      | Po        | $R_L=8\Omega, V_{DDP}=15V, THD+N=10\%$        |      | 15   |      | W     |

| (Stereo)                                               |           | $R_L=4\Omega$ , $V_{DDP}=14V$ , THD+N=10%,    |      | 20   |      | W     |

| Maximum momentary Output                               | Po        | $R_L$ =4 $\Omega$ , $V_{DDP}$ =12V, THD+N=10% |      | 20   |      | W     |

| (monaural)                                             | PO        | $R_L=4\Omega, V_{DDP}=15V, THD+N=10\%$        |      | 30   |      | W     |

|                                                        |           | GAIN[1:0]=L,L                                 |      | 22   |      | dB    |

| Voltage Gain                                           |           | GAIN[1:0]=L,H                                 |      | 28   |      | dB    |

| Voltage Gain                                           | $A_{V}$   | GAIN[1:0]=H,L                                 |      | 34   |      | dB    |

|                                                        |           | GAIN[1:0]=H,H                                 |      | 16   |      | dB    |

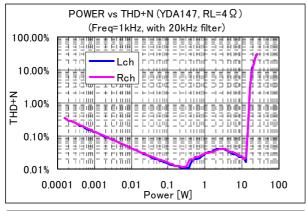

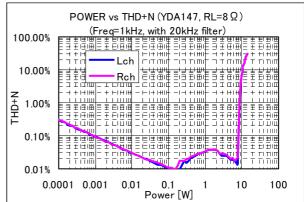

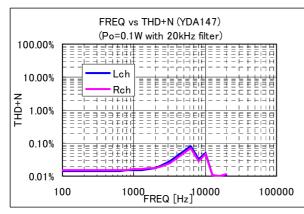

| Total Harmonic Distortion Rate (stereo) (BW::20kHz)    | THD+N     | $R_L = 4\Omega, P_O = 0.1W$                   |      | 0.01 |      | %     |

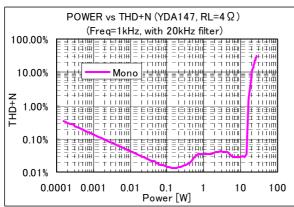

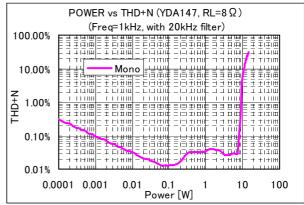

| Total Harmonic Distortion Rate (monaural) (BW::20kHz)  | THD+N     | $R_L = 4\Omega, P_O = 0.2 \text{ W}$          |      | 0.02 |      | %     |

| Signal /Noise Ratio (stereo)<br>(BW::20kHz A-Filter)   | SNR       | $R_L$ =4 $\Omega$ ,GAIN[1:0]=H,H              |      | 105  |      | dB    |

| Signal /Noise Ratio monaural)<br>(BW::20kHz A-Filter)  | SNR       | $R_L$ =4 $\Omega$ ,GAIN[1:0]=H,H              |      | 105  |      | dB    |

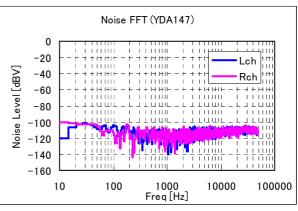

| Residual Noise (stereo)<br>(BW::20kHz A-Filter)        | Vn        | $R_L$ =4 $\Omega$ ,GAIN[1:0]=H,H              |      | 48   |      | μVrms |

| Residual Noise (monaural)<br>(BW::20kHz A-Filter)      | Vn        | $R_L$ =4 $\Omega$ ,GAIN[1:0]=H,H              |      | 48   |      | μVrms |

| Channel Separation Ratio                               | CS        | 1kHz                                          |      | 80   |      | dB    |

| Power Supply Rejection Ratio (stereo) (PVDD applied)   | PSRR      | Vripple=200mV, f=1kHz                         |      | 60   |      | dB    |

| Power Supply Rejection Ratio (monaural) (PVDD applied) | PSRR      | Vripple=200mV, f=1kHz                         |      | 60   |      | dB    |

| Common Mode Rejection Ratio (stereo)                   | CMRR      | f=1kHz                                        |      | 41   |      | dB    |

| Common Mode Rejection Ratio (monaural)                 | CMRR      | f=1kHz                                        |      | 41   |      | dB    |

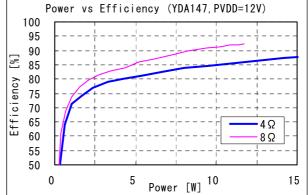

| Marianan Efficiency (start)                            |           | $R_L=4\Omega$                                 |      | 88   |      | %     |

| Maximum Efficiency (stereo)                            | η         | $R_L=8\Omega$                                 |      | 92   |      | %     |

| Mariana Efficience (                                   |           | $R_L=4\Omega$ , 20W output                    |      | 93   |      | %     |

| Maximum Efficiency (monaural)                          | η         | $R_L=8\Omega$ , 10W output                    |      | 93   |      | %     |

| Output Offset Voltage (stereo) *1)                     | Vo        |                                               |      | 5    | 15   | mV    |

| Output Offset Voltage (monaural) *1)                   | Vo        |                                               |      | 5    | 15   | mV    |

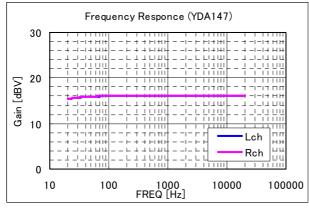

|                                                        |           | f=20Hz                                        | -1   | 0    | 1    | dB    |

| Frequency characteristics                              | $f_{RES}$ | f=20kHz                                       | -1   | 0    | 1    | dB    |

Note) \*1: The offset voltage is denoted by considering a typical value and the maximum value as  $\sigma$  and  $3\sigma$ , respectively.

CATALOG No.:LSI-4DA147A61

<sup>\*2:</sup> The same specification is applied to the external clock mode and internal clock (spread clock mode).

All the values of analog characteristics were obtained in our evaluation circumstance.

Depending upon pattern layout etc., characteristics may vary.

The measurement is performed with an  $8\Omega$  or  $4\Omega$  resistor connected in series with a  $30\mu H$  coil as an output load.

#### Example of typical characteristics

(V<sub>SS</sub>=0V, V<sub>DDP</sub>=12V, Ta=25°C, GAIN[1:0]=L,L, NCDRC[1:0]=L,L, CKIN=1MHz, unless otherwise specified)

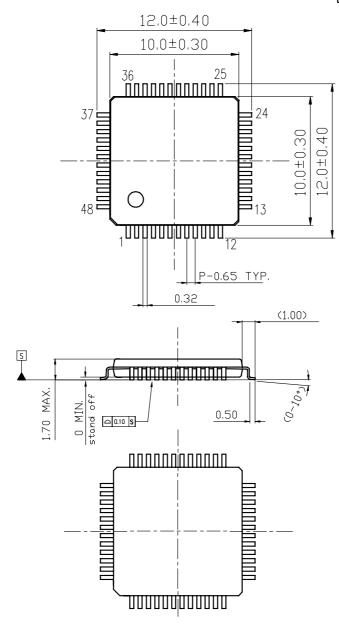

### ■ Package Outline

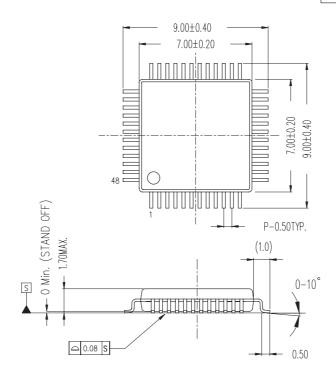

< SQFP48 >

C-PK48SP1-3

端子厚さ/Lead Thickness: 0.15 or 0.17

モールドコーナー形状は、この図面と若干異なるタイプもあります。カッコ内の寸法値は参考値です。

モールド外形寸法はバリを含みません。

単位: mm

The shape of the molded corner may slightly differ from the shape in this diagram.

The figure in the parentheses () should be used as a reference.

Plastic body dimensions do not include resin burr.

UNIT: mm

注) 表面実装LSIは、保管条件、及び半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせください。

ote: The storage and soldering of LSIs for surface mounting need special consideration. For detailed information, please contact your local Yamaha agent.

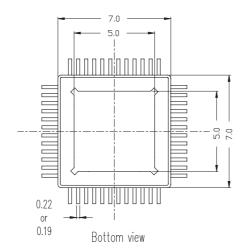

< LQFP48 >

#### C-PK48VP2-1

端子厚さ/Lead Thickness: 0.17 or 0.145

モールドコーナー形状は、この図面と若干異なるタイプもあります。

カッコ内の寸法値は参考値です。

モールド外形寸法はバリを含みません。

単位:mm

The shape of the molded corner may slightly differ from the shape in this diagram.

The figure in the parentheses () should be used as a reference.

Plastic body dimensions do not include resin burr.

UNIT: mm

注) 表面実装LSIは、保管条件、及び半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせください。

Note: The storage and soldering of LSIs for surface mounting need special consideration.

For detailed information, please contact your local Yamaha agent.

**YDA147**

MEMO

#### IMPORTANT NOTICE

- 1 YAMAHA RESERVES THE RIGHT TO MAKE CHANGES TO ITS PRODUCTS AND TO THIS DOCUMENT WITHOUT NOTICE. THE INFORMATION CONTAINED IN THIS DOCUMENT HAS BEEN CAREFULLY CHECKED AND IS BELIEVED HOWEVER YAMAHA SHALL ASSUME NO RESPONSIBILITIES FOR INACCURACIES AND MAKE NO COMMITMENT TO LIPDATE OR TO KEEP CURRENT THE INFORMATION CONTAINED IN THIS DOCUMENT.

- 2. THESE YAMAHA PRODUCTS ARE DESIGNED ONLY FOR COMMERCIAL AND NORMAL INDUSTRIAL APPLICATIONS, AND ARE NOT SUITABLE FOR OTHER USES, SUCH AS MEDICAL LIFE SUPPORT FOUIPMENT. NUCLEAR FACILITIES, CRITICAL CARE EQUIPMENT OR ANY OTHER APPLICATION THE FAILURE OF WHICH COULD LEAD TO DEATH, PERSONAL INJURY OR ENVIRONMENTAL OR PROPERTY DAMAGE, USE OF THE PRODUCTS IN ANY SUCH APPLICATION IS AT THE CUSTOMER'S OWN RISK AND EXPENSE.

- 3. YAMAHA SHALL ASSUME NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCT.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS. INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF PRODUCTS. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMES OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

- 6. YAMAHA MAKES EVERY EFFORT TO IMPROVE THE QUALITY AND RELIABILITY OF ITS PRODUCTS. HOWEVER, ALL SEMICONDUCTOR PRODUCTS FAIL WITH SOME PROBABILITY. THEREFORE, YAMAHA REQUIRES THAT SUFFICIENT CARE BE GIVEN TO ENSURING SAFE DESIGN IN CUSTOMER PRODUCTS SUCH AS REDUNDANT DESIGN, ANTI-CONFLAGRATION DESIGN, AND DESIGN FOR PREVENTING MALFUNCTION IN ORDER TO PREVENT ACCIDENTS RESULTING IN INJURY OR DEATH, FIRE OR OTHER SOCIAL DAMAGE FROM OCCURRING AS A RESULT OF PRODUCT FAILURE.

- 7. INFORMATION DESCRIBED IN THIS DOCUMENT: APPLICATION CIRCUITS AND ITS CONSTANTS AND CALCULATION FORMULAS, PROGRAMS AND CONTROL PROCEDURES ARE PROVIDED FOR THE PURPOSE OF EXPLAINING TYPICAL OPERATION AND USAGE. THEREFORE, PLEASE EVALUATE THE DESIGN SUFFICIENTLY AS WHOLE SYSTEM UNDER THE CONSIDERATION OF VARIOUS EXTERNAL OR ENVIRONMENTAL CONDITIONS AND DETERMINE THEIR APPLICATION AT THE CUSTOMER'S OWN RISK, YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR CLAIMS, DAMAGES, COSTS AND EXPENSES CAUSED BY THE CUSTOMER OR ANY THIRD PARTY, OWING TO THE USE OF THE ABOVE INFORMATION.

**Notice**

The specifications of this product are subject to improvement changes without prior notice.

|   |         | $\longrightarrow$ YAN                        |

|---|---------|----------------------------------------------|

|   | AGENT — | Address inquiries to:<br>Semiconductor Sales |

|   |         | ■ Head Office                                |

|   |         | ■ Tokyo Office                               |

|   |         | ■ Osaka Office                               |

| \ |         | ,                                            |

#### MAHA CORPORATION -

& Marketing Department

203, Matsunokijima, Iwata,

Shizuoka, 438-Ŏ192, Japan Геl. +81-539-62-4918 — Fax. +81-539-62-5054

-17-11, Takanawa, Minato-ku,

okyo, 108-8568, Japan

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

3-12-12, Minami Senba, Chuo-ku, Osaka City, Osaka, 542-0081, Japan

'el. +81-6-6252-6221 Fax. +81-6-6252-6229