## OEM Manual

## Hard Disk Drive Specifications Travelstar C4K60-60/40/30/20

## REV.1

www.DataSheet4U.com

Models: HTC426060G9AT00 HTC426040G9AT00 HTC426030G7AT00 HTC426020G7AT00

<u>Caution for Safety</u>

Read Safety descriptions carefully.

Read and recommend drive usage cautions to your end user.

Keep this manual with care.

(Total 146 pages)

HITACHI ©2004, Hitachi Global Storage Technologies. All rights reserved.

Rev.0: Aug 26, 2004 Preliminary Rev.1: Nov 19, 2004

ww.DataSheet4U.com

This manual is for the original purchaser of Travelstar C4K60-60/4030/20 and intendes to provide information about handling, installation, specifications, principles of operation and interface command implementation.

To use the product, read safety descriptions below and understand thoroughly. Keep this manual with care to insure unlimited use.

#### General Caution for Safety

The followings are general cautions for safe use of this product.

#### (Caution before Product Use)

Please read and follow all instructions and cautions described on "Safety Instructions" (Page 5) and "1.2 General Caution" (Page 12) before attempting to use this product.

- Follow all instructions and cautions indicated throughout this manual and the product. Failure to follow these instructions and cautions may cause injury, fire and product damage.

#### • Advise your end user of the safety caution

Read and recommend that your end users read the caution for drive usage in this manual.

#### • Protect yourself

The safety instructions in this manual were thoroughly considered, but unexpected situations can occur. Not only follow the instructions on this manual, but also be careful for the safety of yourself.

#### • Headline of safety caution

Safety instructions and cautions are indicated as the following headline, which consists a word of "Caution". The indication and meaning are as follows:

**Caution:** This symbol indicates that potential danger may exist which may cause slight or medium grade bodily injury ,if safety instructions are not followed.

**Caution:** This symbol indicates that potential danger may exist which may cause damage to the product or to the neighboring property ,if safety instructions are not followed.

## • A Safety caution in this manual

Followings are the cautions and contents described in this manual.

| Items of | <sup>i</sup> indicating |

|----------|-------------------------|

|----------|-------------------------|

Caution :

- Safety Instructions

Page 5

#### Items of indicating Caution :

- General Caution

- Power Supply Requirements

- Data Reliability

- Mounting HDD

- Attention for HDD Installation

- Packing

- Handling

Sec. 1.2, Page 12 Sec. 3.1, Page 15 Sec. 3.2, Page 16 Sec. 4.2.1, Page 20 Sec. 4.2.3, Page 22 Sec. 5.1, Page 24 Sec. 5.2, Page 25

# To use this product safely (Continued)

### • Environmental circumstance

Although this product partially scatters electro-magnetic field into the air, it has been inspected and was installed under Electro-magnetic regulations of resident areas, such as EMC standard EN55022 (corresponding to FCC part 15 Class B, etc.). However, anything other than this product, such as an interface cable, is excluded. Therefore, the following cases require a system side improvement for the electro-magnetic field regulations.

1) Disturbance of operations of other products or equipment in resident area

Disturbance caused by other product, such as cabling, to operations of other products or equipment.

Only Hitachi trained persons should change this product Hitachi assumes no responsibility for products which have been changed by anyone else.

#### • Safety regulations

This product meets the following safety regulations, but the system side should consider the safety of the system with this product.

Regulations:

- UL1950 Third Edition dated July 28, 1995

- CSA C22.2 N0.950-M95

- IEC60950 A4: 1996

- EN60950 A11: 1992

## Warranty and Limited Liability

This product is sold with a limited warranty and specific remedies are available to the original purchaser in the event the product fails to conform to the limited warranty. Hitachi's liability may be further limited in accordance with its sales contact.

In general, Hitachi shall not be responsible for product damages caused by natural disasters, fire, static discharge, misuse, abuse, neglect, improper handling or installation, unauthorized repair, alteration or accident. In no event will Hitachi be liable for loss of data stored on product.

HITACHI SHALL NOT BE LIABLE FOR ANY SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF INFORMED OF THE POSSIBILITY THEREOF IN ADVANCE.

Please see your sales contract for a complete statement of warranty rights, remedies and limitation of liability.

## Safety Instructions

# Caution

- 1. The product is not authorized for use in life support devices or systems or other applications that pose a significant risk of personal injury.

- Since the drive uses glass media for the disk platter, opening of Metal Head Disk Assembly (HDA) may cause bodily injury. Warranty void in case of opened HDA or any broken HDA seals. Don't open the HDA or break any HDA seals.

- 3. Dropping of the HDD may cause bodily injury. Handle with care.

- 4. Do not hit the interface connector pins against other objects. Do not make contact with the interface connector pins. Contact causes pin dent, electrical discharge distraction or contact failure. Also, pins or

- HDA corners may cause bodily injury. Handle with care.

## Caution

- 5. Observe Clause 3.3 "Drive Usage Condition Specifications". Since reliability and product life depends on usage conditions, please consult our sales or application engineers.

- 6. Keep usage conditions within specifications (Power Supply, Environment, etc.). If the conditions are not kept within the specifications, failures may occur.

- 7. Hot swapping (Power-on swapping) can damage the drive. The drive shall be swapped during Power Off only.

- 8. Electro Static Discharge (ESD) can damage the drive. Protect the drive from ESD during handling.

- 9. Voltage rise time 5 100 ms at power on is required for power supply. The power supply voltage must not be under -0.3V at power off.

- 10. This product is required over current protection for possible combustion due to circuit or component failure. Secondary over current protection shall be prepared by the system. The requirement of the current limitation is max. 10 A for the protection.

- 11. Improper insertion of connector or wrong jumper setting may cause catastrophic failures. Referring to this manual prior to the connector insertion or jumper setting can help to insure correct insertion.

- 12. If a foreign conductive substance (metallic powder, fluid, etc.) adheres to active metal of the drive (Printed pattern, component lead, etc. on PCBA), it may cause catastrophic failures. Customer should protect the drive from the above condition.

- 13. The PCBA side of the drive should be covered with insulation sheet if the active metal of host system may contact to the PCBA of the drive. If the insulation sheet is not provided for the possible contact of the live metal, failures may occur.

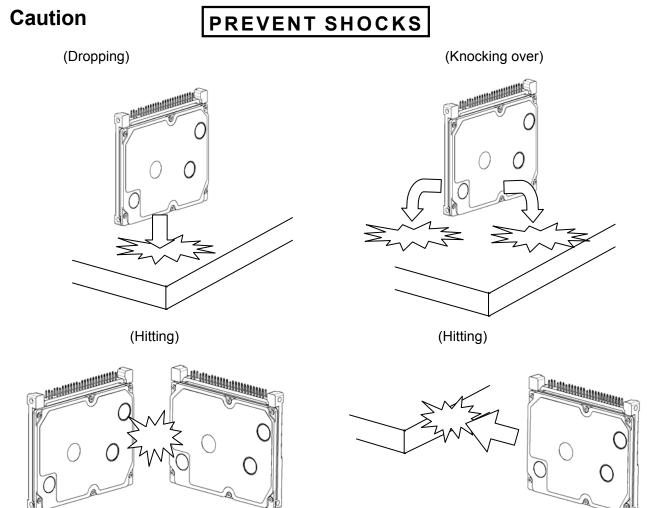

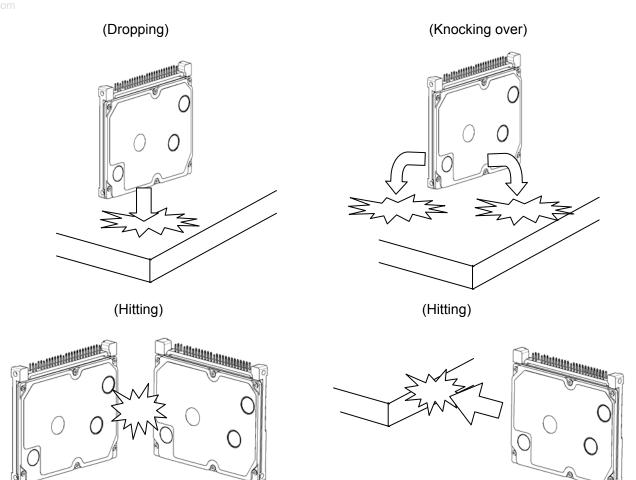

- 14. Shock can result in permanent damage to the drive and/or loss of data. Prevent shocks, which is often incurred by dropping, knocking over, or hitting the drive.

- 15. To fix the drive, use the size of screws and the torque recommended in this manual. If non-recommended size screws and torque are used, it may cause catastrophic failures.

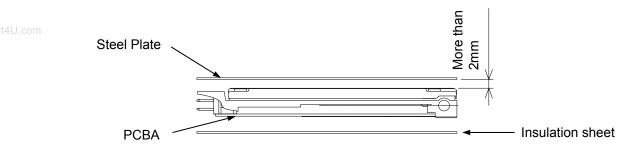

- 16. Do not press top cover. It may cause catastrophic failures. In case of steel plate installation on HDD cover side, the spacing between HDD cover and steel plate should be kept more than 2 mm. If this spacing is not kept for the steel plate, it may affect Load/Unload mechanism.

- 17. Do not push the bottom PCBA of the drive. It may cause catastrophic failures.

## Safety Instructions (Continued)

# Caution

- 18. Prevent humidity when the drive is packed in a box.

- 19. Use original packages during drive transportation to protect from any damage. (Keep some extra packages for the drive transportation)

- 20. Recorded data on the disk may be lost due to accidents such as disasters, shock damage during handling or drive failure. To prepare for accidents, back up data. Hitachi does not perform data recovery.

- 21. Data may be lost due to unexpected or accidental power loss during write operation.

/w.DataSheet4U.com

### NOTE TO USERS

While every effort has been made to ensure that the information provided herein is correct please feel free to notify us in the event of an error or inconsistency.

Hitachi makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties or merchantability or fitness for any purpose.

Further Hitachi reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation to notify any person of such revisions or changes.

| OEM Manual                                        | 1 |

|---------------------------------------------------|---|

| To use this product safely                        | 2 |

| 1.0 General                                       | 2 |

| 1.1. Introduction                                 | 2 |

| 1.2. General Caution                              | 2 |

| 2.0 Components                                    | 2 |

| 3.0 Specification Summary                         | 2 |

| 3.1. Principal Specifications                     | 2 |

| 3.2. Environmental Specifications and Reliability | 2 |

| 3.3. Drive Usage Condition Specifications         | 2 |

| et4U3:4 <sup>n</sup> Load/Unload Specifications   | 2 |

| 3.4.1. Normal Load/Unload                         | 2 |

| 3.4.2. Emergency Unload                           |   |

| 3.4.3. Required Power Off Sequence                | 2 |

| 4.0 Installation                                  | 2 |

| 4.1. Installation Direction                       | 2 |

| 4.2. Mounting HDD                                 | 2 |

| 4.2.1. Mounting HDD with screws                   | 2 |

| 4.2.2. Single HDD Test Condition                  |   |

| 4.2.3. Attention for HDD Installation             |   |

| 4.3. Device Address Setting (DRIVE 0/DRIVE 1)     |   |

| 4.4. Dimensions                                   | 2 |

| 5.0 Packing and Handling                          |   |

| 5.1. Packing                                      | 2 |

| 5.2. Handling                                     |   |

| 6.0 Physical Interface                            | 2 |

| 6.1. Power Interface                              | 2 |

| 6.2. Physical Interface                           | 2 |

| 6.2.1. Connector                                  |   |

| 6.2.2. Connector Pin Assignment                   | 2 |

| 6.2.3. Description of the Interface Signals       | 2 |

| 7.0 Logical Interface                             | 2 |

| 7.1. I/O Registers                                | 2 |

| 7.1.1. Data register                              | 2 |

| 7.1.2. Error register                             | 2 |

| 7.1.3. Features Register                          | 2 |

| 7.1.4. Sector Count Register                      | 2 |

| 7.1.5. LBA Low Register (Sector Number Register)  |   |

| 7.1.6. LBA Mid Register (Cylinder Low Register)   | 2 |

| 7.1.7. LBA High Register (Cylinder High Register) | 2 |

| 7.1.8. Device/Head Register                       | 2 |

| 7.1.9. Status Register                            | 2 |

|                                                   |   |

| 7.1.10. Command Register                                  | 2 |

|-----------------------------------------------------------|---|

| 7.1.11. Alternate Status Register                         | 2 |

| 7.1.12. Device Control Register                           | 2 |

| 7.2. General Operations                                   | 2 |

| 7.2.1. 48-bit Addressing Feature Set                      | 2 |

| 7.2.2. Power Management                                   | 2 |

| 7.2.3. SMART Feature                                      | 2 |

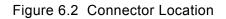

| 7.2.4. Security Mode Feature                              | 2 |

| 7.2.5. Protected Area Feature                             | 2 |

| 7.2.6. Address Offset Feature (Vendor Specific)           | 2 |

| 7.2.7. Device Configuration Overlay Feature               | 2 |

| <sup>4U.co</sup> 7.2.8. Write Cache and Auto Reallocation | 2 |

| 7.3. Command Protocol                                     |   |

| 7.3.1. PIO Data In Command                                | 2 |

| 7.3.2. PIO Data Out Command                               | 2 |

| 7.3.3. DMA Data In/Out Command                            | 2 |

| 7.3.4. Non-Data Command                                   | 2 |

| 7.3.5. Command BSY Timing                                 | 2 |

| 7.4. Command Summary                                      | 2 |

| 7.5. Command Descriptions                                 | 2 |

| 7.5.1. Check Power Mode [98h, E5h]                        |   |

| 7.5.2. Device Configuration Identify [B1h, Sub 02h]       |   |

| 7.5.3. Device Configuration Freeze Lock [B1h, Sub 01h]    |   |

| 7.5.4. Device Configuration Restore [B1h, Sub 00h]        |   |

| 7.5.5. Device Configuration Set [B1h, Sub 03h]            |   |

| 7.5.6. Execute Device Diagnostic [90h]                    |   |

| 7.5.7. Flush Cache [E7h]                                  |   |

| 7.5.8. Flush Cache EXT [EAh]                              |   |

| 7.5.9. Format Track [50h] (Vendor Specific)               |   |

| 7.5.10. Identify Device [ECh]                             |   |

| 7.5.11. Idle [97h, E3h]                                   |   |

| 7.5.12. Idle Immediate [95h,E1h] / Unload Immediate [E1h] |   |

| 7.5.13. Initialize Device Parameters [91h]                |   |

| 7.5.14. Read Buffer [E4h]                                 |   |

| 7.5.15. Read DMA [C8h, C9h]                               |   |

| 7.5.16. Read DMA EXT [25h]                                |   |

| 7.5.17. Read Log EXT [2Fh]                                |   |

| 7.5.18. Read Long [22h, 23h]                              |   |

| 7.5.19. Read Multiple [C4h]                               |   |

| 7.5.20. Read Multiple EXT [29h]                           |   |

| 7.5.21. Read Max Address Command [F8h]                    |   |

| 7.5.22. Read Max Address EXT Command [27h]                |   |

| 7.5.23. Read Sectors [20h, 21h]                           |   |

| K6610168                                                  | - |

| N00 I U I 00                                              |   |

| 7.5.24. Read Sectors EXT [24h]                                 | . 2 |

|----------------------------------------------------------------|-----|

| 7.5.25. Read Verify [40h, 41h]                                 | . 2 |

| 7.5.26. Read Verify Sectors EXT [42h]                          | . 2 |

| 7.5.27. Recalibrate [1Xh]                                      | 2   |

| 7.5.28. Security Disable Password [F6h]                        | . 2 |

| 7.5.29. Security Erase Prepare [F3h]                           | 2   |

| 7.5.30. Security Erase Unit [F4h]                              | . 2 |

| 7.5.31. Security Freeze Lock [F5h]                             | . 2 |

| 7.5.32. Security Set Password [F1h]                            | . 2 |

| 7.5.33. Security Unlock [F2h]                                  | 2   |

| 7.5.34. Seek [7Xh]                                             | 2   |

| <sup>214U.co</sup> <b>7</b> .5.35. Set Features [EFh]          | 2   |

| 7.5.36. Set Max Address Command [F9h, Sub 00h]                 | 2   |

| 7.5.37. Set Max Address EXT Command [37h]                      | . 2 |

| 7.5.38. Set Max Freeze Lock Command [F9h, Sub 04h]             | 2   |

| 7.5.39. Set Max Lock Command [F9h, Sub 02h]                    |     |

| 7.5.40. Set Max Set Password Command [F9h, Sub 01h]            | 2   |

| 7.5.41. Set Max Unlock Command [F9h, Sub 03h]                  | . 2 |

| 7.5.42. Set Multiple Mode [C6h]                                | . 2 |

| 7.5.43. Sleep [99h,E6h]                                        |     |

| 7.5.44. SMART Disable Operations [B0h, Sub D9h]                |     |

| 7.5.45. SMART Enable/Disable Automatic Off-line [B0h, Sub DBh] |     |

| 7.5.46. SMART Enable/Disable Attribute AUTOSAVE [B0h, Sub D2h] |     |

| 7.5.47. SMART Enable Operations [B0h, Sub D8h]                 |     |

| 7.5.48. SMART Execute Off-line Immediate [B0h, Sub D4h]        |     |

| 7.5.49. SMART Read Log Sector [B0h, Sub D5h]                   |     |

| 7.5.50. SMART Return Status [B0h, Sub DAh]                     |     |

| 7.5.51. SMART Save Attribute Values [B0h, Sub D3h]             |     |

| 7.5.52. SMART Write Log Sector [B0h, Sub D6h]                  |     |

| 7.5.53. Standby [96h, E2h]                                     |     |

| 7.5.54. Standby Immediate [94h, E0h]                           |     |

| 7.5.55. Write Buffer [E8h]                                     |     |

| 7.5.56. Write DMA [CAh, CBh]                                   |     |

| 7.5.57. Write DMA EXT [35h]                                    |     |

| 7.5.58. Write DMA FUA EXT [3Dh]                                |     |

| 7.5.59. Write Log EXT [3Fh]                                    |     |

| 7.5.60. Write Long [32h, 33h]                                  |     |

| 7.5.61. Write Multiple [C5h]                                   |     |

| 7.5.62. Write Multiple EXT [39h]                               |     |

| 7.5.63. Write Multiple FUA EXT [CEh]                           |     |

| 7.5.64. Write Sectors [30h, 31h]                               |     |

| 7.5.65. Write Sectors EXT [34h]                                |     |

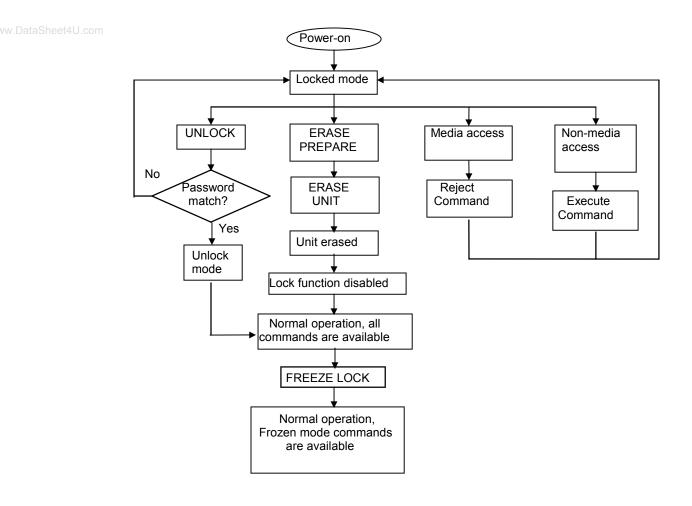

| 8.0 Interface Signal Timing                                    | . 2 |

| K6610168                                                       |     |

## Rev.1 Nov 19, 2004

| 8.1. Data Transfer Timing               | 2 |

|-----------------------------------------|---|

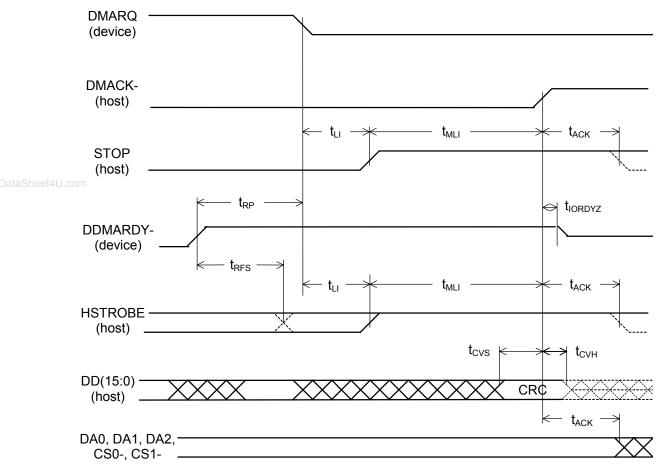

| 8.2. Ultra DMA Data Transfer Timing     | 2 |

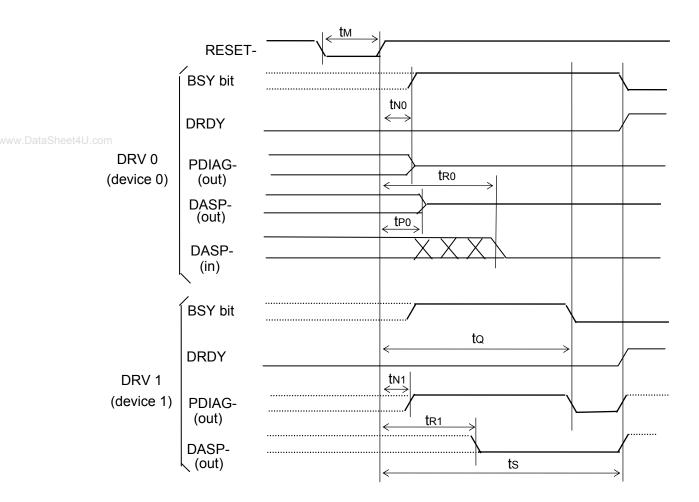

| 8.3. Power On and Hardware Reset Timing | 2 |

ww.DataSheet4U.com

#### 1.0 General

#### 1.1. Introduction

The Travelstar C4K60-60/40/30/20 disk drives reach high capacities in a 1.8 type form factor by applying the latest high-density recording technology.

|                     |                 | Capacity    |        |            |

|---------------------|-----------------|-------------|--------|------------|

| Product name        | Model name      | (Formatted) | Height | Interface  |

| Travelstar C4K60-60 | HTC426060G9AT00 | 60.011 GB   | 9.5 mm | ATA-6(IDE) |

| Travelstar C4K60-40 | HTC426040G9AT00 | 40.007 GB   | 9.5 mm | ATA-6(IDE) |

| Travelstar C4K60-30 | HTC426030G7AT00 | 30.005 GB   | 7.0 mm | ATA-6(IDE) |

| Travelstar C4K60-20 | HTC426020G7AT00 | 20.003 GB   | 7.0 mm | ATA-6(IDE) |

#### [Features]

- GMR Head

- ID-less Format

- ME<sup>2</sup>PRML Read Channel

- Data Transfer Rate

- (Host-Device)

- -16.6 MB/sec: PIO mode-4/Multiword DMA mode-2

- 100 MB/sec: Ultra DMA mode-5

- (Device-Buffer)

- 18.4 to 34.0 MB/s(60/30GB), 15.9 to 29.7 MB/sec(40/20GB)

- CDR (Constant Density Recording)

- On-the-fly ECC Correction

- Buffer: 2MB

- Read-ahead Cache/Write Cache

- Auto Read Reassign/Auto Write Reassign

- SMART

- Average Access Time 15 ms

- Embedded Sector Servo

- FDB(Fluid Dynamics Bearing) Motor

- Rotary Actuator

- Load/Unload Mechanism

- 62grams(60/40GB), 47 grams(30/20GB)

- Low Power Consumption: 0.25W at Idle mode, 0.08W at Standby mode (3.3V operation)

- Advanced Power Management(APM)

- Non-operating Shock: 11,760m/S<sup>2</sup>(1200G, 1ms, half-sine wave)

- Operating Shock: 4,900m/S<sup>2</sup>(500G, 2ms, half-sine wave)

#### [Identify Device Information for Setup]

#### Table 1.1 Identify Device information (Addressing)

| Product name    | Word 1<br>Number of CYL. | Word 3<br>Number of HD | Word 6<br>Number of SPT | Word 60 – 61 * <b>1</b><br>Word 100 - 103<br>Total LBA |

|-----------------|--------------------------|------------------------|-------------------------|--------------------------------------------------------|

| HTC426060G9AT00 | 16383 * <b>2</b>         | 16                     | 63                      | 117,210,240                                            |

| HTC426040G9AT00 | 16383 * <b>2</b>         | 16                     | 63                      | 78,140,160                                             |

| HTC426030G7AT00 | 16383 * <b>2</b>         | 16                     | 63                      | 58,605,120                                             |

| HTC426020G7AT00 | 16383 * <b>2</b>         | 16                     | 63                      | 39,070,080                                             |

\*1 : Words 60-61 reflect the total number of user addressable sectors in LBA mode.

\*2 : Maximum capacity in CHS mode is 8,455MB.

## 1.2. General Caution

**Caution** Adhere to the following cautions.

(a) Warranty void if Metal Head Disk Assembly (HDA) is opened, or any HDA seal/label is broken.

(b) Hot swapping (Power on) damages the drive. The drive should be swapped during Power Off only.

(c) Shock can result in permanent damage to the drive and/or loss of data.

Prevent shocks often incurred by dropping, knocking over, or hitting the drive.

## 2.0 Components

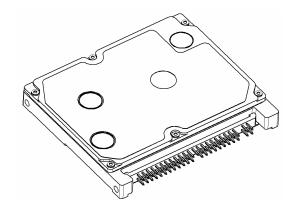

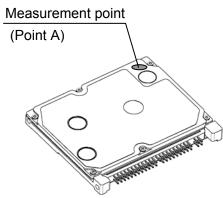

Travelstar C4K60-60/4030/20 Disk Drive

vw.DataSheet4U.com

## 3.0 Specification Summary

## 3.1. Principal Specifications

|        |                                  |                   | Specifications                     |                          |                        |                        |            |

|--------|----------------------------------|-------------------|------------------------------------|--------------------------|------------------------|------------------------|------------|

| No.    | o. Item                          |                   | Travelstar<br>C4K60-60             | Travelstar<br>C4K60-40   | Travelstar<br>C4K60-30 | Travelstar<br>C4K60-20 | Units      |

|        | Mode                             | l name            | HTC426060G9AT00                    | HTC426040G9AT00          | HTC426030G7AT00        | HTC426020G7AT00        |            |

| 1      | Capacity per di                  | rive (Formatted)  | 60.011                             | 40.007                   | 30.005                 | 20.003                 | GB         |

| neet4U | Capacity per se                  | ector             |                                    | 5                        | 12                     |                        | Bytes      |

|        | Disks                            |                   | 2                                  | 2                        |                        | 1                      |            |

|        | Heads                            |                   | 4                                  | 4                        | 2                      | 2                      |            |

| 2      | Seek time                        | Average           |                                    | 1                        | 5 * <b>1</b>           |                        | ms         |

|        | (Nominal                         | Full stroke       |                                    | 2                        | 6 * <b>1</b>           |                        | ms         |

|        | value)                           | Track to track    |                                    |                          | 3                      |                        | ms         |

| 3      | Average latenc                   | ÿ                 |                                    | 7                        | .1                     |                        | ms         |

|        | Disk rotational                  | speed             |                                    | 4,2                      | 200                    |                        | RPM        |

| 4      | Recording den                    | sity (Max.)       | 32.8 (832)                         | 28.1 (713)               | 32.8 (832)             | 28.1 (713)             | Mbpm(kBPI) |

|        | Track density                    |                   | 4.65 (118.0)                       | 4.13 (105.0)             | 4.65 (118.0)           | 4.13 (105.0)           | Mtpm(kTPI) |

|        | Recording met                    | hod               |                                    | ME <sup>2</sup> PRML, II | D-Less format          |                        |            |

| 5      | Interface                        |                   |                                    | ATA-0                    | 6(IDE)                 |                        |            |

|        | Data transfer ra                 | ate (Disk-Buffer) | 18.4 - 34.0                        | 15.9 – 29.7              | 18.4 - 34.0            | 15.9 – 29.7            | MB/sec     |

|        | Data transfer rate (Host-Buffer) |                   |                                    | Max. 16.6                |                        |                        | MB/sec     |

|        |                                  |                   | (PIO mode 4/ Multiword DMA mode 2) |                          |                        |                        |            |

|        |                                  |                   | Max. 100 (Ultra DMA mode 5)        |                          |                        |                        | MB/sec     |

|        | Buffer size                      | r size 2,048      |                                    |                          | kВ                     |                        |            |

| 6      | 6 Power on - Ready *2            |                   | 5 (Typical) * <b>3</b>             |                          |                        | sec                    |            |

|        | Sleep/Standby                    |                   |                                    |                          | ical) * <b>3</b>       |                        | sec        |

| 7      | Dimensions (W                    | /×H×D)            | 70×9                               | .5×60                    | 70×7                   | .0×60                  | mm         |

|        | Weight (Approximate value)       |                   |                                    | 62                       |                        | .7                     | grams      |

| 8      | DC Power Req                     |                   | 5.0V±                              | 5.0V±5% or 3.3V±5%, 1    |                        | mvp-p                  | W          |

|        | Supply Voltag                    | le                | 5.0V / 3.3V                        |                          | 5.0V / 3.3V            |                        |            |

|        | - Start up (Max.) * <b>5</b>     |                   |                                    |                          | / 1.4                  |                        |            |

|        | - Idle (Ave.)                    | *6                | 0.38 / 0.25                        |                          |                        |                        |            |

|        | - Active Idle                    | (Ave.) * <b>7</b> | 0.68 / 0.45                        |                          |                        |                        |            |

|        | - Seek (Ave.                     | ) *8              | 1.7 / 1.1                          |                          |                        |                        |            |

|        | - Read (Ave.                     | ) *9              | 1.5 / 1.0                          |                          |                        |                        |            |

|        | - Write (Ave.                    | ) * <b>9</b>      | 1.7 / 1.1                          |                          |                        |                        |            |

|        | - Standby (A                     | - Standby (Ave.)  |                                    |                          | / 0.08                 |                        |            |

|        | - Sleep (Ave                     | .)                |                                    | 0.11                     | / 0.07                 |                        |            |

| Table 3.1  | <b>Principal Specifications</b> |

|------------|---------------------------------|

| 1 4010 0.1 | i intelpar opoontoatione        |

- \*1 :Average time of seek is calculated under the following condition. (Read/Write ratio: Read only) Average of 10,000 random seeks, Voltage 5.0V or 3.3V, Temperature 25°C. Full stroke time of seek is calculated under the following condition. Average of 1,000 full stroke seeks, Voltage 5.0V or 3.3V, Temperature 25°C. This maximum time is not included the seek time by seek retry.

- \*2 :Periodically, during start up, the drive may perform a spin up retry operation. When this operation occurs, the start up sound will change slightly and the ready timing will also be altered from typical time.

- \*3 :Power on to Ready time could take up to 10 seconds in case of spin up retries under certain conditions of the voltage specifications(Table 3.1) and environmental specifications(Table 3.2).

- \*4 :For DC power input, the average current is measured at the connector of the PCBA of this drive and in the nominal condition in which the power voltage and the temperature are 5.0V or 3.3V and 25°C, respectively. The DC power input has to be burst free (common mode). The average current may have some tolerance after power-on. The current measurement is recommended at 5 minutes later after power-on.

# **Caution** Voltage rise time 5 - 100 ms at power on is required for power supply. The power supply voltage must not be under -0.3V at power off.

- **Caution** This product is required over current protection for possible combustion due to circuit or component failure. Secondary over current protection shall be prepared by the system. The requirement of the current limitation is max. 10 A for the protection.

- \*5 :10ms averaged peak. For more information, refer to Section 6.1.

- \*6 :This value is at Low Power Idle mode. The heads are unloaded.

- \*7 :Power mode automatically enters to Active Idle mode after Read/Write operation.

- **\*8** : Measured during random seek at the rate of three seeks per 100 msec.

- **\*9** :Measured while reading or writing 16 sectors of data located on the same track.

### 3.2. Environmental Specifications and Reliability

| No.                | . Item Specification                                   |                                                                   |                                                               |                               |                    |                 |

|--------------------|--------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|--------------------|-----------------|

|                    | licin                                                  |                                                                   | Travelstar                                                    | Travelstar                    | Travelstar         | Travelstar      |

|                    |                                                        |                                                                   | C4K60-60                                                      | C4K60-40                      | C4K60-30           | C4K60-20        |

|                    | Model                                                  | name                                                              | HTC426060G9AT00                                               | HTC426040G9AT00               | HTC426030G7AT00    | HTC426020G7AT00 |

| 1                  | Ambient *1                                             | Operational                                                       |                                                               | 5 to                          | 60°C               |                 |

|                    | temperature                                            | Non-operational                                                   |                                                               | -40 to                        | o 70°C             |                 |

|                    | Temperatu                                              | re gradient                                                       |                                                               | Max. 20                       | °C /hour           |                 |

| 2 <sup>cor</sup> 2 | Relative humidity                                      | Operational                                                       |                                                               | 5 to                          | 90 %               |                 |

|                    |                                                        | Non-operational                                                   |                                                               | 5 to                          | 95 %               |                 |

|                    | Maximum wet                                            | Operational                                                       |                                                               | 29°C (without                 | condensation)      |                 |

|                    | bulb                                                   | Non-operational                                                   |                                                               | 40°C (without                 | condensation) *2   |                 |

| 3                  | Vibration                                              | Operational                                                       |                                                               |                               | less (5 - 22Hz)    |                 |

|                    |                                                        | 9.8 m/s <sup>2</sup> (1.0G) or less m/s <sup>2</sup> (22 – 500Hz) |                                                               | )Hz)                          |                    |                 |

|                    |                                                        | Non-operational                                                   |                                                               |                               |                    |                 |

|                    |                                                        |                                                                   |                                                               | 49m/s <sup>2</sup> (5G) or le | ess (22 – 500Hz)   |                 |

| 4                  | Shock *5                                               | Operational                                                       | 4,900                                                         | m/s (500G) or les             | s (2 ms, half sine | wave)           |

|                    | Non-operational                                        |                                                                   | 11,760m/s <sup>2</sup> (1200G) or less (1 ms, half sine wave) |                               |                    |                 |

| 5                  | Atmospheri                                             | c condition                                                       | Without corrosive vapors, salt or organic-metal compound.     |                               |                    |                 |

|                    |                                                        |                                                                   |                                                               | (ex. organic sili             | con, organic tin)  |                 |

| 6                  | Acoustic-noise *3                                      | ldle(Typ.)                                                        | 1.8                                                           | Bels                          | 1.6                | Bels            |

|                    |                                                        | seek(Typ.)                                                        | 2.4                                                           | Bels                          | 2.2                | Bels            |

| 7                  | Height                                                 | Operational                                                       | 3,000m or less                                                |                               |                    |                 |

|                    | (Altitude)                                             | Non-operational                                                   | 12,000m or less                                               |                               |                    |                 |

|                    | Height gradient                                        |                                                                   | Max. 300m/min.(3.1kpa/min.)                                   |                               |                    |                 |

| 8                  | Data reliability                                       |                                                                   | Less than 1 non-recoverable error in                          |                               |                    |                 |

|                    | (with retries and ECC)                                 |                                                                   | 10 E 13 bits read *4                                          |                               |                    |                 |

| 9                  | External magnetic field 1,500 micro Tesla (DC) or less |                                                                   |                                                               |                               |                    |                 |

Table 3.2 Environmental Specification and Reliability

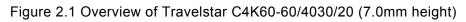

\*1: Ambient temperature should be measured at point 10 mm away from the nameplate of the drive. If the maximum operational ambient temperature cannot be measured at a point 10 mm away from the nameplate, a substitution method is stipulated in the table below.

| Ambient     | Temperature at cover |

|-------------|----------------------|

| temperature | (Point A)            |

| 60°C        | 65°C                 |

| 5°C         | 5°C                  |

\*2: In case of the maximum wet bulb 40°C, the drive should be packed in HDD package box with ESD bag and desiccant. Please see specification 5.1 Packing for reference. If the drive is not packed in the HDD package box with ESD bag and desiccant, maximum wet bulb 29°C is applied.

\*3 : 3.0 Bels are the maximum sound power levels with A-weighted. This value is specified at product K6610168 Rev.1

shipment, except during power on, load, unload or power down. Clicking noise of magnet latch operation occurs at loading and unloading operation of the magnetic heads. Also, the clicking noise of the magnet latch occurs at emergency unloading operations. Measurements are to be taken in accordance with ISO 7779. At seek mode, randomly select a cylinder and seek operation of the actuator with a delay time at each cylinder. Seek rate for the drive can be calculated as shown below.

Seek rate = 0.4/(average access time + average latency) = 0.4/(average access time + 60/RPM/2)

#### \*4 :

Caution

Data reliability is not to be used to compromise the host system data backup.

\*5 :These shock specifications are defined for each axis. For non-operating rotational shock, the specification is 50K radian/sec<sup>2</sup> or less (2 ms, half sine wave).

DataSheet4U.com

#### 3.3. Drive Usage Condition Specifications

The drive is designed for usage under the following conditions. Since reliability and product life depends on usage conditions, please consult our sales representatives or application engineers if the drive may be operated outside these conditions.

| -Power on hours (POH)                   | : Less than 333 hours/month<br>POH includes Sleep and Standby modes. The heads are unloaded during Power<br>off, Standby, Sleep or Low Power Idle modes. The spindle motor is stopped<br>during Standby and Sleep modes. This drive is not designed or intended to be<br>used for 24/7 applications. Continuous motor spinning should be limited to 48<br>hours period. In case of continuous POH condition, the transition to Standby<br>mode or Sleep mode must occur at least once every 48 hours period. |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -Operating (Seek/Write Read operations) | : Less than 20% of POH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -Motor Start/Stop Count                 | : Max. 300,000 times. This number includes Standby, Sleep and power-on/off count.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -Environment                            | : Within environmental specifications given in Table 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -Power Requirement                      | : Within DC power requirement specifications given in Table 3.1 "Principal Specifications"                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -Drive Grounding                        | : Drive frame should be grounded to system ground with four screws electrically.<br>Grounding noise should be less than 500mVp-p. The grounding noise<br>should be measured between electrical ground and system frame ground<br>without the drive. Grounding AC current (measuring between two of side<br>mounting holes) should be less than 50 mAp-p (Frequency Range: less than<br>12MHz). The grounding current should be measured through 50 ohm resistor.                                             |

| -External Magnetic Field                | : Within specifications given in Table 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -Mounting                               | : Mount with recommended screws and regular torque.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -Physical/Electrical Interf             | ace: ATA-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -Handling                               | : Do not add Electrical Static Discharge, and Vibration and Shock to the drive.<br>Do not press top cover and bottom PCBA surface of the drive.                                                                                                                                                                                                                                                                                                                                                              |

### 3.4. Load/Unload Specifications

Load /Unload is a mechanism to load/unload the heads on the disk surfaces.

#### 3.4.1. Normal Load/Unload

Normal load/unload operations are limited to maximum 600,000 times during HDD life. The normal unload operation is performed by the following commands.

- Standby

- Standby Immediate

- ww.DataSheet4U.com Sleep

Also, the normal unload is automatically performed by control software, during Idle mode. The above normal unload time does not include an emergency unload as explained in Sec. 3.4.2.

#### 3.4.2. Emergency Unload

The emergency unload is occurred by unexpected power down, and is limited to maximum 20,000 times during HDD life. Since normal unload can not be performed by the software control after power off, the heads are unloaded by a hardware control. The maximum number of emergency unload is defined separately.

#### 3.4.3. Required Power Off Sequence

To operate the load/unload normally, the following BIOS sequence is required by Host system before power off.

#### [Sequence #1]: Execute one of following commands.

- Standby

- Standby Immediate

- Sleep

Note: Such as Soft Reset, Flush Cache command or Check Power Mode command does not unload the heads.

#### [Sequence #2]: Check the Status Register, and wait the command complete.

**Note:** The head is unload by the sequence #1 command, and the command completion normally takes about 1sec. Considering the error retries, BIOS timer should be set to over 30 sec by the Host side.

#### [Sequence #3]: Power off the drive

Above sequence is required for the Host system at Power off, Suspend and Hibernation operations.

#### 4.0 Installation

#### 4.1. Installation Direction

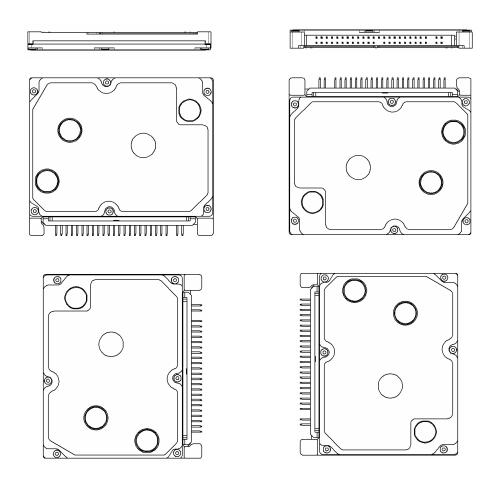

The Travelstar C4K60-60/4030/20 can be installed in the 6 directions as shown below.

Figure 4.1 Installation

### 4.2. Mounting HDD

### 4.2.1. Mounting HDD with screws

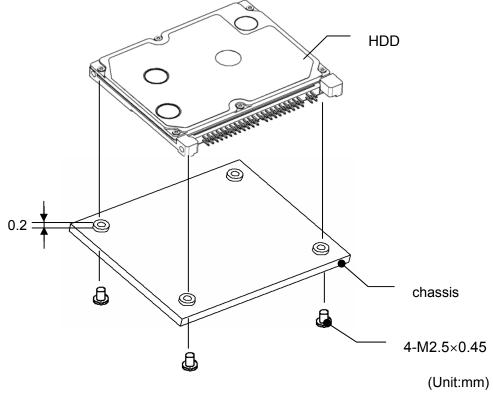

**Caution** Mount the HDD with the screws according to the following instruction to optimize the performance.

- (a) Mount the HDD with M2.5 screws. Take care not to add any distorting force to the HDD when mounting. Using 4 screws holes, secure the HDD.

- (b) Use screws with the following specifications when the HDD is mounted.

- i) M2.5 (screw engagement of 2.8mm max. However, do not use both bottom and side screw hole at the same position simultaneously.)

- ii) The torque for fixing the screws is 2.5±0.5kgcm(2.2±0.4 lb. inch)

- (c) Consider an appropriate cooling to keep the temperature of center of HDD top cover less than 65°C.

- (d) The inertia of the chassis around the Z-axis of the gravity center of the device must be more than  $3 \times 10^{-4} \text{ kg m}^2$ .

- Note) In case of general Sub-Notebook PC(Weight: 1.7kg), the inertia of the chassis around the Z-axis of the gravity center of the device is greater than 100 X 10<sup>-4</sup> kg m<sup>2</sup>. Therefore, the required inertia level has no problem with the general electronic equipment.

Figure 4-2 Mounting the HDD

## 4.2.2. Single HDD Test Condition

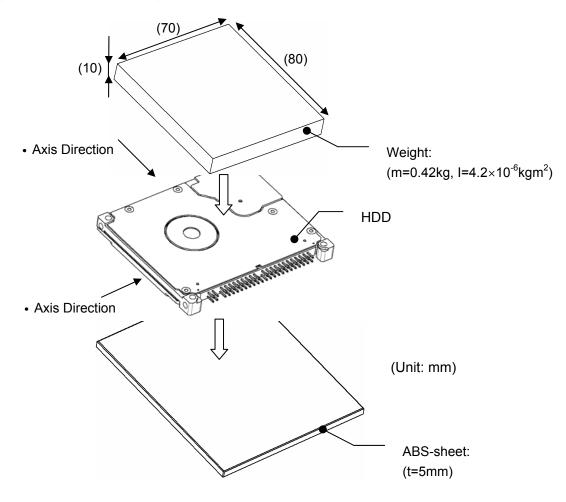

To optimize the performance, keep the following instructions.

- 1) For the Single HDD test, HDD should be placed on an ABS-sheet. HDD should be place with no movement by external force min. 0.25N for X axis and Y-axis directions.

- 2) Don't place HDD on a soft sponge sheet or hard surface at HDD test. If the HDD is placed on the soft sponge sheet or slippery hard desk surface, the HDD has unstable conditions such as HDD self-vibration at seek operations or spindle motor rotation. It may cause performance reduction or J come errors. Also, HDD floating by tension of I/F cabling may cause the similar symptom. The HDD

- should be placed without any floating. Don't test the HDD under these unstable conditions.

- 3) If the HDD cannot be fixed by the required holding torque above item 1), put a body weight on the HDD as shown in Figure 4-3. The body weight is provided for preventing the HDD movement or HDD floating by tension of I/F cabling.

Figure 4.3 Single HDD Test Condition

### 4.2.3. Attention for HDD Installation

### (1) In case of steel plate installation on HDD cover side, the spacing between HDD cover and steel plate should be kept more than 2 mm. If this spacing is not kept for the steel plate, it may affect Load/Unload mechanism.

- (2) The PCBA side of the drive should be covered with insulation sheet if the active metal of host system may contact to the PCBA of the drive. If the insulation sheet is not provided for the possible contact of the live metal, failures may occur.

- (3) Do not push the bottom PCBA. It may cause catastrophic failures.

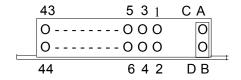

#### 4.3. Device Address Setting (DRIVE 0/DRIVE 1)

When the device is connected to the host bus, Device address setting is necessary to configure a device as DRIVE 0 or DRIVE 1. The device address setting is established between drives on the interface connector by using jumper 0-2 (pin # A, B, D)

The DRIVE 0 is assigned to device address 0, and the DRIVE 1 is assigned to device address 1.

1) DRIVE 0 (or single)

If all of pins A,B, D are open, the drive is DRIVE 0(or single).

2) DRIVE 1

If jumper Position A-B is used, the drive is DRIVE 1.

3) CSEL Selection

| 43     | 531 | CA |

|--------|-----|----|

| 0      | 000 | 0  |

| <br>0  | 000 | 0  |

| <br>44 | 642 | DB |

If jumper Position B-D is used, DRIVE 0 or DRIVE 1 setting is determined by the condition of CSEL signal (pin# 28).

(Recommended type of jumper socket) Vender: IRISO ELECTRONICS CO., LTD. Vender Part Number: 9721HJ-GF

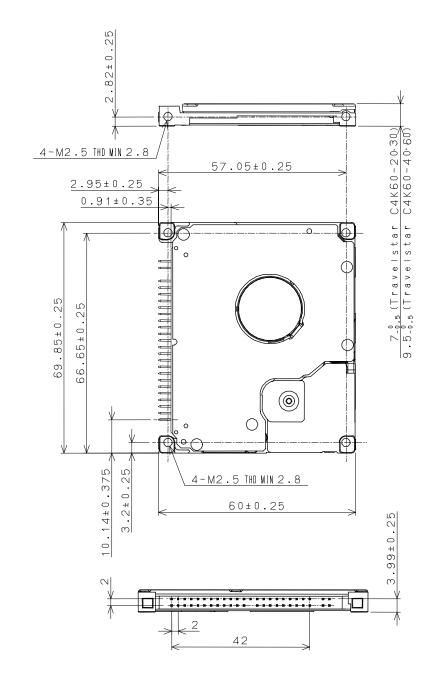

### 4.4. Dimensions

(Unit : mm)

Figure 4.4 Dimensions

## 5.0 Packing and Handling

### 5.1. Packing

## Caution

When you package the device, clean it and execute the following procedures to prevent humidity and handling damage and contamination.

- (1) Pack the device in an ESD protective bag with desiccant.

- (2) Use the original Hitachi cardboard box and the cushioning materials or equivalent cushioning structures to surround the above bag.

- (3) Never stack or package drives next to each other with at the proper cushion material separating them.

- (4) Indicate which side is upside or downside on the exterior of the package box and attach notes requesting careful treatment and preventing the box from being turned upside down.

- (5) Prevent excessive pressure from being applied on the top and bottom of the drive(top cover and PCBA side) when packing, unpacking, and transporting.

- (6) Remember, mishandling of a drive can void the drive's warranty.

- (7) Packing materials, i.e. ESD protective bag, cardboard box, cushion, etc., should not contain corrosive vapors, salt or organic-metal compound. (ex. organic silicon, organic tin)

**Caution** Prevent humidity when the drive is packed in a box.

## 5.2. Handling

# **Caution** Mount the HDD with the screws according to the following instructions to optimize the performance.

It is necessary to prevent vibration, shock, and static electricity to the drive because it will damage the precision parts. In particular, prevent vibration or shock generated by dropping, knocking over, or hitting the drive. Also, avoid touching the electrical components directly, which can discharge electrostatic energy and damage the drive.

Figure 5.1

## 6.0 Physical Interface

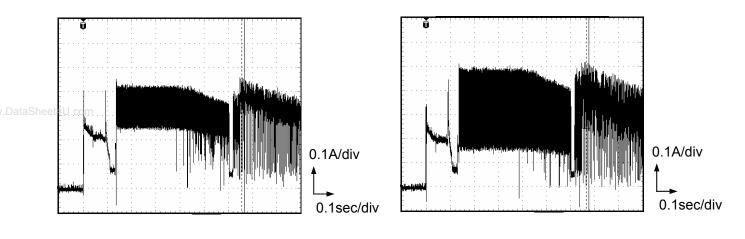

### 6.1. Power Interface

Figures 6.1 shows typical power current transitions after turning on the power.

Supply voltage : 3.3V

Supply Voltage : 5.0V

Figure 6.1 Power Current Transition

## 6.2. Physical Interface

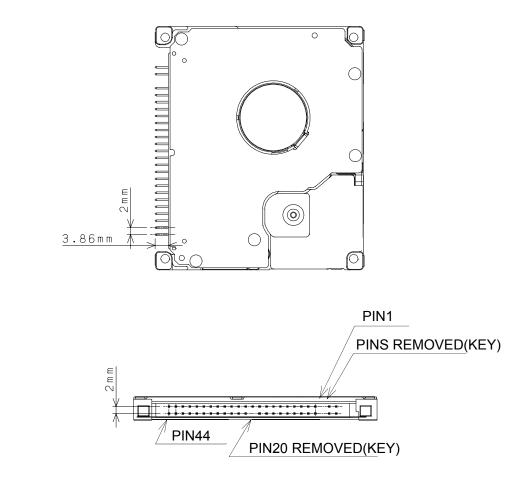

### 6.2.1. Connector

| Table 6.1 | Recommended socket connector |

|-----------|------------------------------|

|-----------|------------------------------|

| Drive interface connector | Recommended socket connector |

|---------------------------|------------------------------|

| DDK : KKS-PD50A-R23-FG    | DDK : KKS-RTS44-342N         |

| or equivalent             | or equivalent                |

## 6.2.2. Connector Pin Assignment

|                   |    | $\top$ |                   |

|-------------------|----|--------|-------------------|

| JUMPER1           | Α  | В      | JUMPER0           |

| JUMPER3           | С  | D      | JUMPER2           |

| KEY(Removed)      | E  | F      | KEY(Removed)      |

| RESET-            | 1  | 2      | GND               |

| DD7               | 3  | 4      | DD8               |

| DD6               | 5  | 6      | DD9               |

| DD5               | 7  | 8      | DD10              |

| DD4               | 9  | 10     | DD11              |

| DD3               | 11 | 12     | DD12              |

| DD2               | 13 | 14     | DD13              |

| DD1               | 15 | 16     | DD14              |

| DD0               | 17 | 18     | DD15              |

| GND               | 19 | 20     | KEY(Removed)      |

| DMARQ             | 21 | 22     | GND               |

| DIOW-             | 23 | 24     | GND               |

| DIOR-             | 25 | 26     | GND               |

| IORDY             | 27 | 28     | CSEL              |

| DMACK-            | 29 | 30     | GND               |

| INTRQ             | 31 | 32     | IOCS16-           |

| DA1               | 33 | 34     | PDIAG-            |

| DA0               | 35 | 36     | DA2               |

| CS0-              | 37 | 38     | CS1-              |

| DASP-             | 39 | 40     | GND(Motor)        |

| 3.3 / 5VDC(Logic) | 41 | 42     | 3.3 / 5VDC(Motor) |

| GND(Logic)        | 43 | 44     | Reserved          |

|                   |    |        | РСВ               |

www.DataSheet4U.com

## 6.2.3. Description of the Interface Signals

The interface is an ATA(IDE) interface. Reserved pins should be left unconnected. The signal names and the pin numbers are shown in Table 6.2. Table 6.2 shows signal definitions.

"I" of I/O type represents an input signal from the device and "O" represents an output signal from the device.

|        | Signal name | Pin  | I/O type | Description                                                       |

|--------|-------------|------|----------|-------------------------------------------------------------------|

| eet4U. | comRESET-   | 1    | I        | This is a reset signal output from the host system and to be      |

|        |             |      |          | used for interface logic circuit.                                 |

|        | DD0-DD15    | 3-18 | I/O      | This is a 16-bit bi-directional data bus. The lower 8 bits are    |

|        |             |      |          | used for register access other than data register.                |

|        | DIOW-       | 23   | I        | The rising edge of this Write Strobe signal clocks data from the  |

|        |             |      |          | host data bus into a register on the device.                      |

|        | STOP        |      |          | Assertion of this signal by the host during an Ultra DMA burst    |

|        | *1          |      |          | signals the termination of the Ultra DMA burst.                   |

|        | DIOR-       | 25   | I        | Activating this Read Strobe signal enables data from a register   |

|        |             |      |          | on the device to be clocked onto the host data bus. The rising    |

|        |             |      |          | edge of this signal latches data at the host.                     |

| -      | HDMARDY-    |      |          | This signal is a flow control signal for Ultra DMA Read.          |

|        | *1          |      |          | Host asserts this signal, and indicates that the host is ready to |

|        |             |      |          | receive Ultra DMA Read data .                                     |

|        | HSTROBE     |      |          | This signal is Write data strobe signal from the host for an      |

|        | *1          |      |          | Ultra DMA Write. Both the rising and falling edge latch           |

|        |             |      |          | the data from DD(15:0) into the device.                           |

|        | IORDY       | 27   | 0        | This signal is used to temporarily stop the host register access  |

|        |             |      |          | (read or write) when the device is not ready to respond to a      |

|        |             |      |          | data transfer request.                                            |

|        | DDMARDY-    |      |          | This signal is a flow control signal for Ultra DMA Write. Device  |

|        | *1          |      |          | asserts this signal, and indicates that the device is ready to    |

|        |             |      |          | receive Ultra DMA Write data                                      |

|        | DSTROBE     |      |          | This signal is the data in strobe signal from the device for an   |

|        | *1          |      |          | Ultra DMA Read. Both the rising and falling edge latch            |

|        |             |      |          | the data from DD(15:0) into the host.                             |

|        |             |      |          |                                                                   |

Table 6.2 Signal List(1/3)

\*1: Signal name in Ultra DMA mode

| ·i                  | Table 6.2 Signal List(2/3) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|---------------------|----------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal name         | Pin                        | I/O type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| CSEL                | 28                         | Ι        | This signal is used to configure a device as either DRIVE 0 or<br>DRIVE1 when CSEL mode is selected.<br>This signal is pulled up inside the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| INTRQ               | 31                         | 0        | This is an interrupt signal for the host system. This signal is<br>asserted by a selected device when the nIEN bit in the Device<br>Control Register is "0". In other cases, this signal should be a high<br>impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| IOCS16-             | 32                         | 0        | This signal indicates to the host that the 16-bit data port has been addressed and a 16-bit word can be read or written to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| DA0-2               | 33,35,36                   | -        | This is a register address signal from the host system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| PDIAG-:CBLID-<br>*2 | 34                         | I/O      | <ul> <li>The PDIAG- signal is asserted by Device 1 to indicate to Device 0 that it has completed diagnostics. This signal is pulled up inside the device.</li> <li>The host may sample CBLID- after a power-on or hardware reset in order to detect the presence or absence of an 80-conductor cable assembly by performing the following steps:</li> <li>a) The host shall wait until the power on or hardware reset sequence is complete for all devices on the cable;</li> <li>b) If Device 1 is present, the host should issue IDENTIFY DEVICE or IDENTIFY PACKET DEVICE and use the returned data to determine that Device 1 is compliant with ATA-3 or subsequent standards. Any device compliant with ATA-3 or subsequent standards releases PDIAG- no later than after the first command following a power on or hardware reset sequence.</li> </ul> |  |  |  |  |  |

| CS0-                | 37                         | I        | If the host detects that CBLID- is connected to ground, an 80-<br>conductor cable assembly is installed in the system. If the host<br>detects that this signal is not connected to ground, an 80-conductor<br>cable assembly is not installed in the system.<br>This device chip selection signal is used to select the Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| CS1-                | 38                         | I        | Block Registers from the host system.<br>This device chip selection signal is used to select the Control Block<br>Registers from the host system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

Table 6.2 Signal List(2/3)

\*2: PDIAG-:CBLID- (Passed diagnostics: Cable assembly type identifier

| Signal name | Pin       | I/O type | Description                                                                                                                                                                  |

|-------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DASP-       | 39        | I/O      | This signal indicates that a device is active or that Drive 1 is present<br>when the power is turned on.<br>Upon receipt of a command from the host, the device asserts this |

| DMARQ       | 21        | 0        | signal. At command completion, the device de-asserts this signal.<br>The device shall assert this signal, used for DMA data transfers                                        |

|             |           |          | between host and device, when it is ready to transfer data.                                                                                                                  |

| DMACK-      | 29        | Ι        | The host in response to DMARQ to either acknowledge that data has been accepted, or that data is available shall use this signal.                                            |

| JUMPER0,1,2 | PIN-A,B,D | -        | See Sec. 4.3 " Drive Address Setting (Drive 0/Drive 1)" for the detail.                                                                                                      |

Table 6.2 Signal List(3/3)

The I/O signal levels are as follows.

| (1) Input signal  | High level | +2.0V to Vcc+0.5V                                 |

|-------------------|------------|---------------------------------------------------|

|                   | Low level  | –0.5V to +0.8V                                    |

| (2) Output signal | High level | +2.4V to +5.25V or an open circuit                |

|                   | Low level  | +0.4V or less (IOL=2mA), +0.5V or less (IOL=12mA) |

Note) The I/F cable should be no longer than 50cm(20 inches) including the circuit pattern length in the host system. If the cable length is not within this specification, it may cause factional degradations or some errors.

## 7.0 Logical Interface

## 7.1. I/O Registers

Communication between the host system and the device is done through I/O registers. The Command Block Registers are used for sending commands to the device or posting device status. The Control Block Registers are used for controlling the device or posting device status.

|      | ŀ    | Addresse | 3    | Functions |                                    |                   |  |  |

|------|------|----------|------|-----------|------------------------------------|-------------------|--|--|

| CS0- | CS1- | DA2      | DA1  | DA0       | READ(DIOR-)                        | WRITE(DIOW-)      |  |  |

|      |      |          | Comm | and Bloo  | ck Registers                       |                   |  |  |

| 0    | 1    | 0        | 0    | 0         | Data                               | Data              |  |  |

| 0    | 1    | 0        | 0    | 1         | Error                              | Features          |  |  |

| 0    | 1    | 0        | 1    | 0         | Sector Count                       | Sector Count      |  |  |

| 0    | 1    | 0        | 1    | 1         | LBA Low                            | LBA Low           |  |  |

|      |      |          |      |           | (Sector Number)                    | (Sector Number)   |  |  |

| 0    | 1    | 1        | 0    | 0         | LBA Mid                            | LBA Mid           |  |  |

|      |      |          |      |           | (Cylinder Low)                     | (Cylinder Low)    |  |  |

| 0    | 1    | 1        | 0    | 1         | LBA High                           | LBA High          |  |  |

|      |      |          |      |           | (Cylinder High)                    | (Cylinder High)   |  |  |

| 0    | 1    | 1        | 1    | 0         | Device/Head                        | Device/Head       |  |  |

| 0    | 1    | 1        | 1    | 1         | Status                             | Command           |  |  |

|      |      |          | Cont | rol Block | Registers                          |                   |  |  |

| 1    | 0    | 1        | 1    | 0         | Alt. Status                        | Device Control    |  |  |

|      |      |          | ١n   | alid or N | lot Used                           |                   |  |  |

| 0    | 0    | ×        | ×    | ×         | Invalid address                    |                   |  |  |

| 0    | 1    | ×        | ×    | ×         | Data bus high impe                 | edance (not used) |  |  |

| 1    | 0    | 0        | ×    | ×         | Data bus high impedance (not used) |                   |  |  |

| 1    | 0    | 1        | 0    | ×         | Data bus high impe                 | edance (not used) |  |  |

Table 7.1 Register List

'0' is low signal level. '1' is high signal level.

## 7.1.1. Data register

A 16-bit register to be used for transferring data blocks between the HDD's data buffer and the host.

## 7.1.2. Error register

This register stores device status when the last command has been completed or diagnostic codes when a self-diagnostic process has been completed. The contents of this register are valid when the error bit (ERR) is set in the Status Register. The contents of this register are diagnostic codes when the device has just completed a self-diagnostic process requested when turning on the power or resetting.

| Bit  | 7    | 6   | 5 | 4    | 3 | 2    | 1 | 0    |

|------|------|-----|---|------|---|------|---|------|

| Name | ICRC | UNC | 0 | IDNF | 0 | ABRT | 0 | AMNF |

v.DataSheet4U.con

- AMNF(Address Mark Not Found):

- This bit indicates that the device is unable to execute SMART command due to a invalid data structure.

- ABRT(Aborted Command):

- This bit indicates that execution of a command is interrupted due to a device error(e.g. Not Ready and Write fault) or an invalid command code.

- IDNF (ID Not Found):

- This bit indicates that an ID field of the requested sector is not found.

- UNC(Uncorrectable Data Error):

- This bit indicates that an uncorrectable error or an data address mark not found has occurred.

- ICRC(Interface CRC Error): This bit indicates that an interface CRC error was occurred. This bit is not applied for Multiword DMA transfers.

## 7.1.3. Features Register

By combining with the Set Features command, this register is used for enabling or disabling each feature.

#### 7.1.4. Sector Count Register

The register contains the number of sectors of data requested to be transferred on a read or write operation between the host and the device. If value in the register is set to 0, a count of 256 sectors in 28-bit addressing or 65,536 sectors in 48-bit addressing is specified.

When a command has been completed and the value of this register is "0", it represents that the command has been executed successfully. If the command has not been executed successfully, this register indicates the number of the sectors yet to be processed. This definition cannot be applied to all commands. For more information on commands, refer to the corresponding sections.

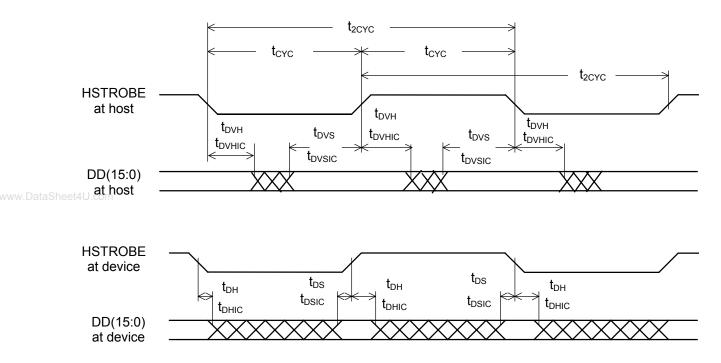

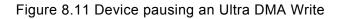

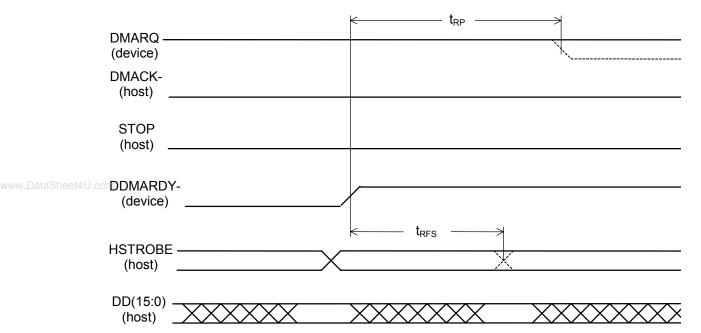

## 7.1.5. LBA Low Register (Sector Number Register)