### Features

High density

- 15K to 350K usable gates

- 256 to 5376 macrocells

- -92 to 520 maximum I/O pins

- -12 Dedicated Inputs including 4 clock pins, 4 global control signal pins and 4 JTAG interface pins for reconfigurability

Embedded Memory

- 40K to 840K bits embedded SRAM

- 32K to 672K bits of (single port) Cluster memory

- 8K to 168K bits of (dual port) Channel memory

- •High speed 250-MHz in-system operation AnyVolt<sup>™</sup> interface

- 3.3V, 2.5V and 1.8V V<sub>CC</sub> versions available

- 3.3V, 2.5V and 1.8V I/O capability on all versions

- Low Power Operation

- -0.18-μm 6-layer metal SRAM-based logic process

- Full-CMOS implementation of product term array

- Standby current as low as 100 µA at 1.8V V<sub>CC</sub> Simple timing model

- No penalty for using full 16 product terms / macrocell

- No delay for single product term steering or sharing •Flexible clocking

- 4 synchronous clocks per device

- —1 spread-aware PLL drives all 4 clock networks

- Locally generated Product Term clock

- Clock polarity control at each register

- •Carry-chain logic for fast and efficient arithmetic operations

# CPLDs at FPGA Densities<sup>™</sup>

•Multiple I/O standards supported

-LVCMOS (3.3/3.0/2.5/1.8V), LVTTL, 3.3V PCI, SSTL2 (I-II), SSTL3 (I-II), HSTL (I-IV), and GTL+

•Compatible with NOBL<sup>™</sup>, ZBT<sup>™</sup>, and QDR<sup>™</sup> SRAMs •Programmable slew rate control on each I/O pin •User-Programmable Bus Hold capability on each I/O pin •Fully PCI compliant (to 66 MHz 64-bit PCI spec rev2.2) •Compact PCI hot swap compatible

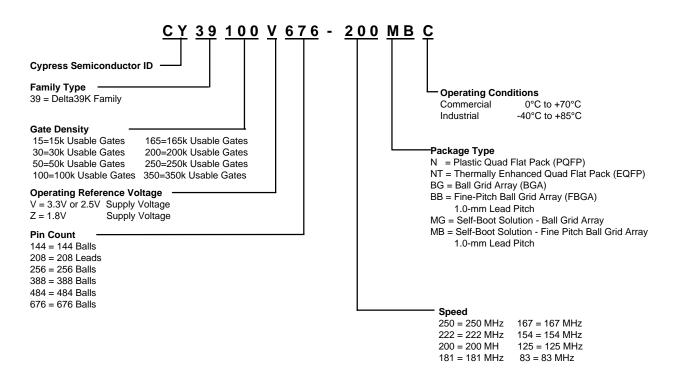

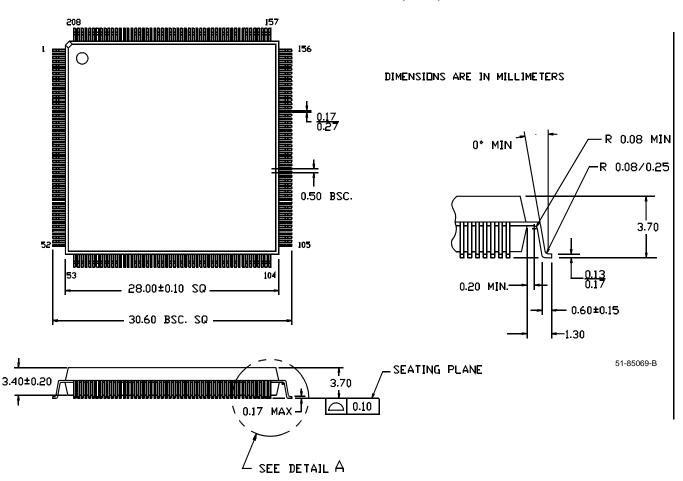

•Multiple package/pinout offering across all densities

- -144 to 676 pins in PQFP, BGA and FBGA packages

- Same pinout for 3.3V/2.5V and 1.8V devices

- Simplifies design migration across density

- Self-Boot<sup>™</sup> solution in BGA and FBGA packages In-System Reprogrammable<sup>™</sup> (ISR<sup>™</sup>)

- JTAG-compliant on-board programming

- Design changes don't cause pinout changes •IEEE1149.1 JTAG boundary scan

### **Development Software**

- •Warp<sup>™</sup>

- IEEE 1076/1164 VHDL or IEEE 1364 Verilog context sensitive editing.

- Active-HDL FSM graphical finite state machine editor

- Active-HDL SIM post-synthesis timing simulator

- Architecture Explorer for detailed design analysis

- Static Timing Analyzer for critical path analysis

- Available on Windows 95, 98 & NT for \$99

- Supports all Cypress Programmable Logic Products

|        | Typical              |            | Cluster<br>memory | Channel<br>memory |          |       | y I <sub>CC</sub> <sup>[2]</sup><br>25°C |          |         |

|--------|----------------------|------------|-------------------|-------------------|----------|-------|------------------------------------------|----------|---------|

| Device | Gates <sup>[1]</sup> | Macrocells | (Kbits)           | (Kbits)           | I/O Pins | (MHz) | (ns)                                     | 3.3/2.5V | 1.8V    |

| 39K15  | 8K–24K               | 256        | 32                | 8                 | 134      | 256   | 6.5                                      | 10 mA    | 100 μA  |

| 39K30  | 16K–48K              | 512        | 64                | 16                | 176      | 238   | 7.0                                      | 10 mA    | 200 µA  |

| 39K50  | 23K–72K              | 768        | 96                | 24                | 218      | 238   | 7.0                                      | 10 mA    | 300 μA  |

| 39K100 | 46K–144K             | 1536       | 192               | 48                | 302      | 222   | 7.5                                      | 10 mA    | 600 μA  |

| 39K165 | 77K–241K             | 2560       | 320               | 80                | 386      | 181   | 8.5                                      | 10 mA    | 1250 μA |

| 39K200 | 92K–288K             | 3072       | 384               | 96                | 428      | 181   | 8.5                                      | 10 mA    | 1250 μA |

| 39K250 | 115K–361K            | 3840       | 480               | 120               | 470      | 167   | 8.5                                      | 10 mA    | 1500 μA |

| 39K350 | 161K–505K            | 5376       | 672               | 168               | 520      | 154   | 9.0                                      | 10 mA    | 2100 μA |

### Delta39K<sup>™</sup> ISR CPLD Family Members

Upper limit of typical gates is calculated by assuming only 10% of the channel memory is used. Standby  $I_{\rm CC}$  values are with PLL not utilized, no output load and stable inputs 1.

Note:

### Delta39K Speed Bins<sup>[3]</sup>

| Device | 250 | 222 | 200 | 181 | 167 | 154 | 125 | 83 |

|--------|-----|-----|-----|-----|-----|-----|-----|----|

| 39K15  | Х   |     |     |     |     |     | Х   | Х  |

| 39K30  |     | Х   |     |     |     |     | Х   | Х  |

| 39K50  |     | Х   |     |     |     |     | Х   | Х  |

| 39K100 |     |     | Х   |     |     |     | Х   | Х  |

| 39K165 |     |     |     | Х   |     |     | Х   | Х  |

| 39K200 |     |     |     | Х   |     |     | Х   | Х  |

| 39K250 |     |     |     |     | Х   |     | Х   | Х  |

| 39K350 |     |     |     |     |     | Х   | Х   | Х  |

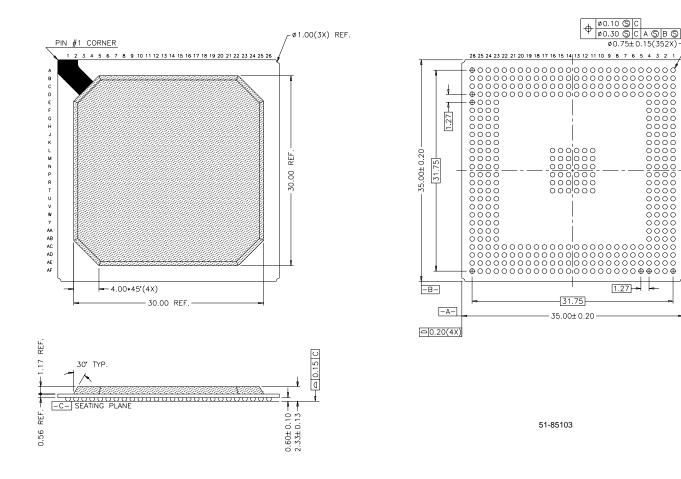

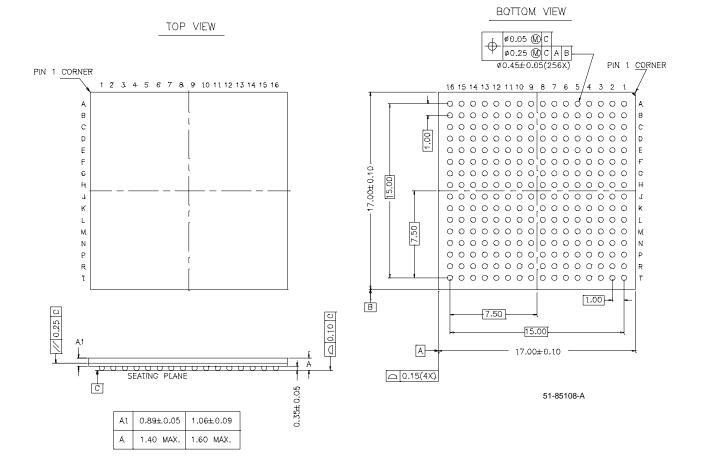

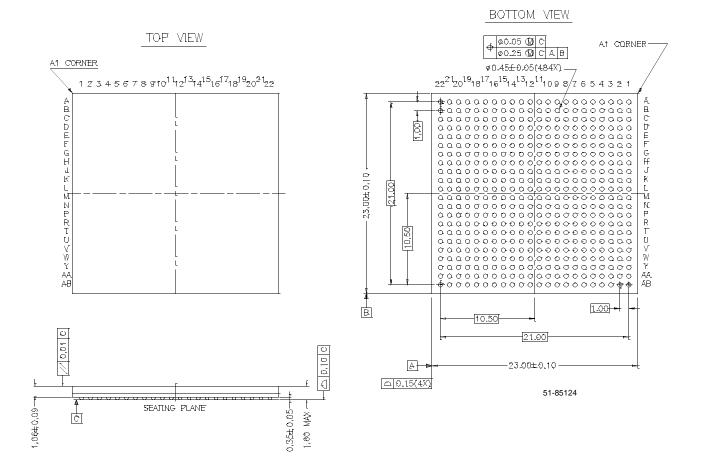

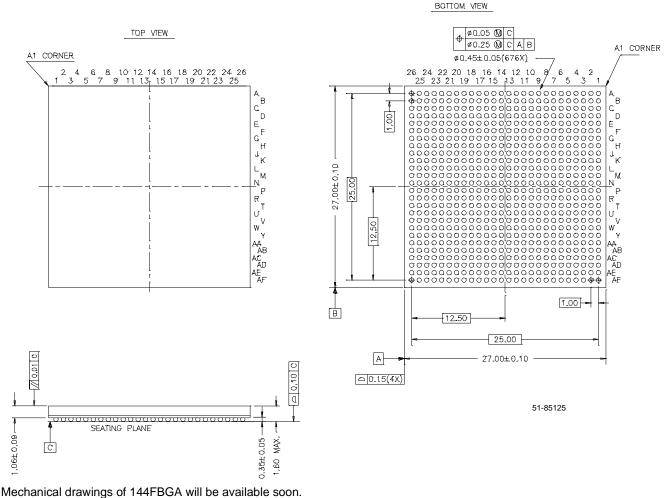

### Device Package Offering and I/O Count Including Dedicated Clock and Control Inputs

|        |                                         |                                                |                                                |                                                |                                         |                                                | Self-Boot                                      | Solution <sup>[4]</sup>                     |                                         |

|--------|-----------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|-----------------------------------------|------------------------------------------------|------------------------------------------------|---------------------------------------------|-----------------------------------------|

| Device | 208-EQFP<br>28X28 mm<br>0.5-mm<br>pitch | <b>144-FBGA</b><br>13x13 mm<br>1.0-mm<br>pitch | <b>256-FBGA</b><br>17x17 mm<br>1.0-mm<br>pitch | <b>484-FBGA</b><br>23x23 mm<br>1.0-mm<br>pitch | 676-FBGA<br>27x27 mm<br>1.0-mm<br>pitch | <b>256-FBGA</b><br>17x17 mm<br>1.0-mm<br>pitch | <b>388-BGA</b><br>35x35 mm<br>1.27-mm<br>pitch | <b>484-FBGA</b><br>23x23 mm<br>1.0-mm pitch | 676-FBGA<br>27x27 mm<br>1.0-mm<br>pitch |

| 39K15  | 134                                     | 92                                             | 134                                            |                                                |                                         | 134                                            |                                                |                                             |                                         |

| 39K30  | 136                                     | 92                                             | 176                                            |                                                |                                         | 176                                            |                                                |                                             |                                         |

| 39K50  | 136                                     |                                                | 180                                            |                                                |                                         |                                                | 218                                            | 218                                         |                                         |

| 39K100 | 136                                     |                                                | 180                                            | 302                                            |                                         |                                                | 294                                            |                                             | 302                                     |

| 39K165 | 136                                     |                                                |                                                | 356                                            |                                         |                                                | 294                                            |                                             | 386                                     |

| 39K200 | 136                                     |                                                |                                                | 368                                            |                                         |                                                | 294                                            |                                             | 428                                     |

| 39K250 | 136                                     |                                                |                                                |                                                | 470                                     |                                                | 294                                            |                                             | 470                                     |

| 39K350 | 136                                     |                                                |                                                |                                                | 520                                     |                                                | 294                                            |                                             | 520                                     |

Notes:

Speed bins shown here are for Commercial operating range. Please refer to Delta39K Ordering Information on page 41 for Industrial range speed bins. Self-Boot Solution integrates the boot PROM (Flash Memory) with Delta39K die inside the same package. 3. 4.

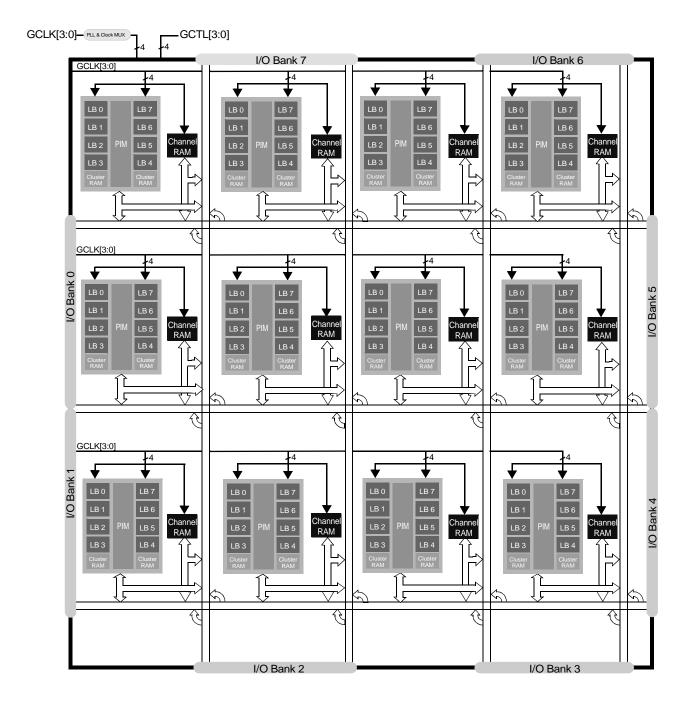

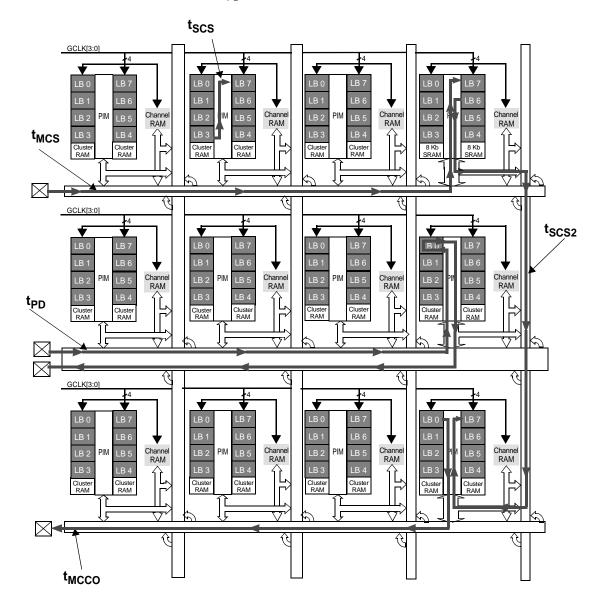

Figure 1. Delta39K100 Block Diagram (3 Rows x 4 Columns) with I/O Bank Structure

### **General Description**

The Delta39K family, based on a 0.18  $\mu$ m, 6-layer metal CMOS logic process, offers a wide range of high-density solutions at unparalleled system performance. The Delta39K family is designed to combine the high speed, predictable timing, and ease of use of CPLDs with the high densities and low power of FPGAs. With devices ranging from 15,000 to 350,000 usable gates, the family features devices ten times the size of previously available CPLDs. Even at these large densities, the Delta39K family is fast enough to implement a fully synthesizable 64-bit, 66-MHz PCI core.

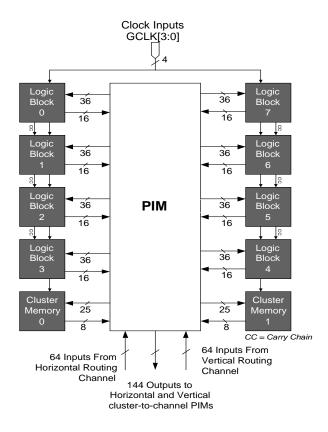

The architecture is based on Logic Block Clusters (LBC) that are connected by Horizontal and Vertical (H&V) routing channels. Each LBC features eight individual Logic Blocks (LB) and two cluster memory blocks. Adjacent to each LBC is a channel memory block, which can be accessed directly from the I/O pins. Both types of memory blocks are highly configurable and can be cascaded in width and depth. See *Figure 1* for a block diagram of the Delta39K architecture.

All the members of the Delta39K family have Cypress's highly regarded In-System Reprogrammability (ISR) feature, which simplifies both design and manufacturing flows, thereby reducing costs. The ISR feature provides the ability to reconfigure the devices without having design changes cause pinout or timing changes in most cases. The Cypress ISR function is implemented through a JTAG-compliant serial interface. Data is shifted in and out through the TDI and TDO pins respectively. Superior routability, simple timing, and the ISR allows users to change existing logic designs while simultaneously fixing pinout assignments and maintaining system performance.

The entire family features JTAG for ISR and boundary scan, and is compatible with the PCI Local Bus specification, meeting the electrical and timing requirements. The Delta39K family also features user programmable bus-hold and slew rate control capabilities on each I/O pin.

#### **AnyVolt Interface**

All Delta39KV devices feature an on-chip regulator, which accepts 3.3V or 2.5V on the V<sub>CC</sub> supply pins and steps it down to 1.8V internally, the voltage level at which the core operates.

The Delta39KZ devices accept 1.8V on the V<sub>CC</sub> supply pins directly. With Delta39K's AnyVolt technology, the I/O pins can be connected to either 1.8V, 2.5V, or 3.3V. All Delta39K devices are 3.3V tolerant regardless of V<sub>CCIO</sub> or V<sub>CC</sub> settings.

| Device | V <sub>cc</sub> | V <sub>CCIO</sub>                           |

|--------|-----------------|---------------------------------------------|

| 39KV   | 3.3V or 2.5V    | 3.3V or 2.5V or 1.8V or 1.5V <sup>[5]</sup> |

| 39KZ   | 1.8V            | 3.3V or 2.5V or 1.8V or 1.5V <sup>[5]</sup> |

#### **Global Routing Description**

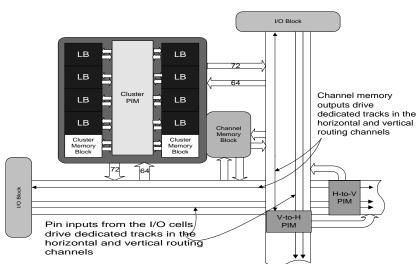

The routing architecture of the Delta39K is made up of horizontal and vertical (H&V) routing channels. These routing channels allow signals from each of the Delta39K architectural components to communicate with one another. In addition to the horizontal and vertical routing channels that interconnect the I/O banks, channel memory blocks, and logic block clusters, each LBC contains a Programmable Interconnect Matrix (PIM<sup>™</sup>), which is used to route signals among the logic blocks and the cluster memory blocks.

*Figure 2* is a block diagram of the routing channels that interface within the Delta39K architecture. The LBC is exactly the same for every member of the Delta39K CPLD family.

#### Logic Block Cluster (LBC)

The Delta39K architecture consists of several logic block clusters, each of which have 8 Logic Blocks (LB) and 2 cluster memory blocks connected via a Programmable Interconnect Matrix (PIM) as shown in *Figure* 3. Each cluster memory block consists of 8-Kbit single-port RAM, which is configurable as synchronous or asynchronous. The cluster memory blocks can be cascaded with other cluster memory blocks within the same LBC as well as other LBCs to implement larger memory functions. If a cluster memory block is not specifically utilized by the designer, Cypress's *Warp* software can automatically use it to implement large blocks of logic.

All LBCs interface with each other via horizontal and vertical routing channels.

Figure 2. Delta39K Routing Interface

Note: 5. For HSTL only. Document #: 38-03039 Rev. \*\*

PRELIMINARY

Figure 3. Delta39K Logic Block Cluster Diagram

#### Logic Block (LB)

The logic block is the basic building block of the Delta39K architecture. It consists of a product term array, an intelligent product-term allocator, and 16 macrocells.

#### **Product Term Array**

Each logic block features a 72 x 83 programmable product term array. This array accepts 36 inputs from the PIM. These inputs originate from device pins and macrocell feedbacks as well as cluster memory and channel memory feedbacks. Active LOW and active HIGH versions of each of these inputs are generated to create the full 72-input field. The 83 product terms in the array can be created from any of the 72 inputs.

Of the 83 product terms, 80 are for general-purpose use for the 16 macrocells in the logic block. Two of the remaining three product terms in the logic block are used as asynchronous set and asynchronous reset product terms. The final product term is the Product Term clock (PTCLK) and is shared by all 16 macrocells within a logic block.

#### **Product Term Allocator**

Through the product term allocator, *Warp* software automatically distributes the 80 product terms as needed among the 16 macrocells in the logic block. The product term allocator pro-

vides two important capabilities without affecting performance: product term steering and product term sharing.

#### Product Term Steering

Product term steering is the process of assigning product terms to macrocells as needed. For example, if one macrocell requires ten product terms while another needs just three, the product term allocator will "steer" ten product terms to one macrocell and three to the other. On Delta39K devices, product terms are steered on an individual basis. Any number between 1 and 16 product terms can be steered to any macrocell.

#### Product Term Sharing

Product term sharing is the process of using the same product term among multiple macrocells. For example, if more than one function has one or more product terms in its equation that are common to other functions, those product terms are only programmed once. The Delta39K product term allocator allows sharing across groups of four macrocells in a variable fashion. The software automatically takes advantage of this capability so that the user does not have to intervene.

Note that neither product term sharing nor product term steering have any effect on the speed of the product. All steering and sharing configurations have been incorporated in the timing specifications for the Delta39K devices.

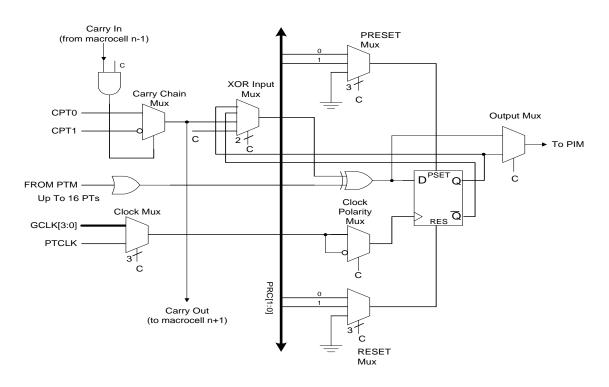

#### Macrocell

Within each logic block there are 16 macrocells. Each macrocell accepts a sum of up to 16 product terms from the product term array. The sum of these 16 product terms can be output in either registered or combinatorial mode. *Figure 4* displays the block diagram of the macrocell. The register can be asynchronously preset or asynchronously reset at the macrocell level with the separate preset and reset product terms. Each of these product terms features programmable polarity. This allows the registers to be preset or reset based on an AND expression or an OR expression.

An XOR gate in the Delta39K macrocell allows for many different types of equations to be realized. It can be used as a polarity mux to implement the true or complement form of an equation in the product term array or as a toggle to turn the D flip-flop into a T flip-flop. The carry-chain input mux allows additional flexibility for the implementation of different types of logic. The macrocell can utilize the carry chain logic to implement adders, subtractors, magnitude comparators, parity tree, or even generic XOR logic. The output of the macrocell is either registered or combinatorial.

#### Carry Chain Logic

The Delta39K macrocell features carry chain logic which is used for fast and efficient implementation of arithmetic operations. The carry logic connects macrocells in up to 4 logic blocks for a total of 64 macrocells. Effective data path operations are implemented through the use of carry-in arithmetic, which drives through the circuit quickly. *Figure 4* shows that the carry chain logic within the macrocell consists of two product terms (CPT0 and CPT1) from the PTA and an input carry-in for carry logic. The inputs to the carry chain mux are connected directly to the product terms in the PTA. The output of the carry chain mux generates the carry-out for the next macrocell in the logic block as well as the local carry input that is connected to an input of the XOR input mux. Carry-in and a configuration bit are inputs to an AND gate. This AND gate provides a method of segmenting the carry chain in any macrocell in the logic block.

#### Macrocell Clocks

Clocking of the register is highly flexible. Four global synchronous clocks (GCLK[3:0]) and a Product Term clock (PTCLK) are available at each macrocell register. Furthermore, a clock polarity mux within each macrocell allows the register to be clocked on the rising or the falling edge (see macrocell diagram in *Figure 4*).

#### PRESET/RESET Configurations

The macrocell register can be asynchronously preset and reset using the PRESET and RESET mux. Both signals are active high and can be controlled by either of two Preset/Reset product terms (PRC[1:0] in *Figure 4*) or GND. In situations where the PRESET and RESET are active at the same time, RESET takes priority over PRESET.

Figure 4. Delta39K Macrocell

#### **Embedded Memory**

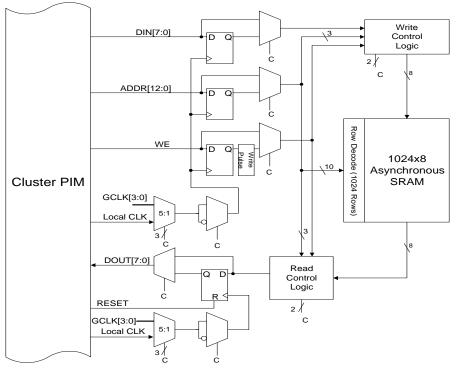

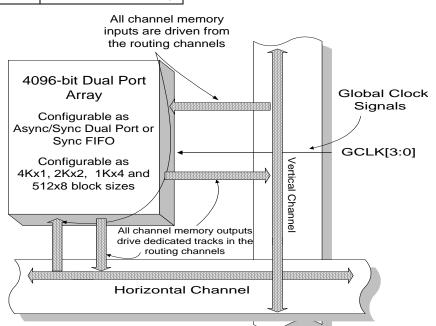

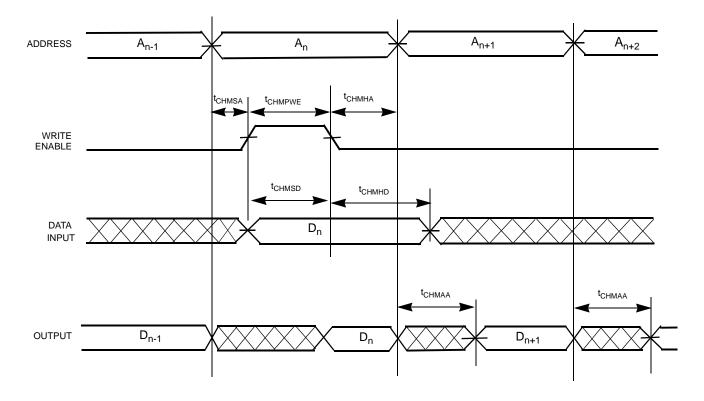

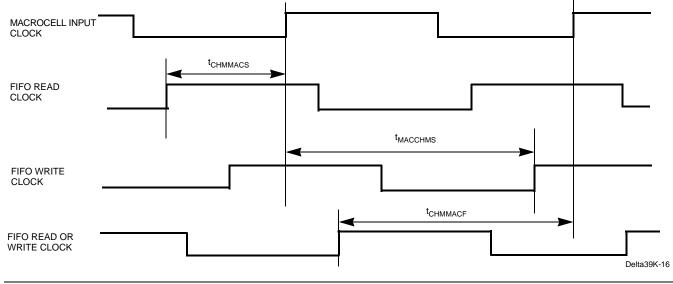

Each member of the Delta39K family contains two types of embedded memory blocks. The channel memory block is placed at the intersection of horizontal and vertical routing channels. Each channel memory block is 4096 bits in size and can be configured as asynchronous or synchronous Dual-Port RAM, Single-Port RAM, Read-Only memory (ROM), or synchronous FIFO memory. The memory organization is configurable as 4Kx1, 2Kx2, 1Kx4 and 512x8. The second type of memory block is located within each LBC and is referred to as a cluster memory block. Each LBC contains two cluster memory blocks that are 8192-bits in size. Similar to the channel memory blocks, the cluster memory blocks can be configured as 8Kx1, 4Kx2, 2Kx4 and 1Kx8 asynchronous or synchronous Single-Port RAM or ROM.

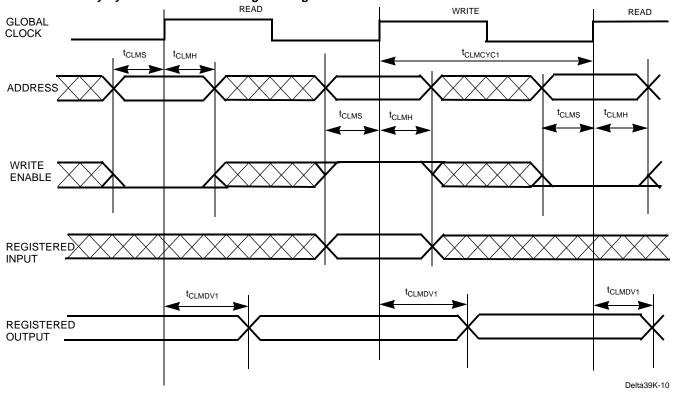

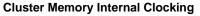

#### **Cluster Memory**

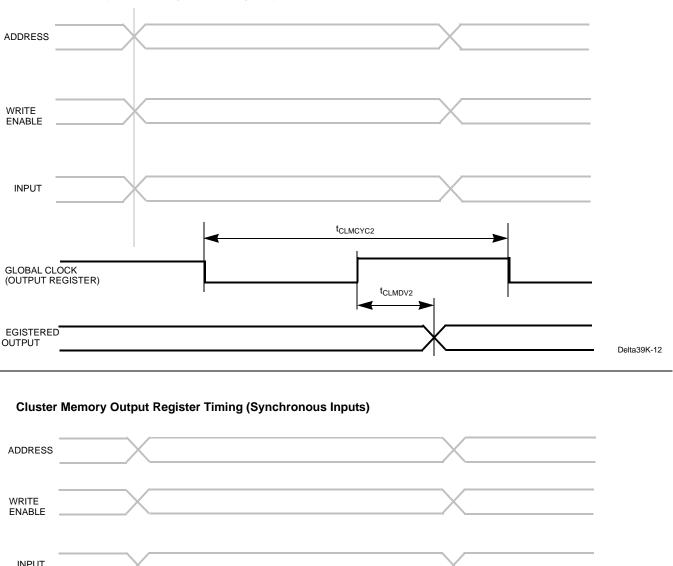

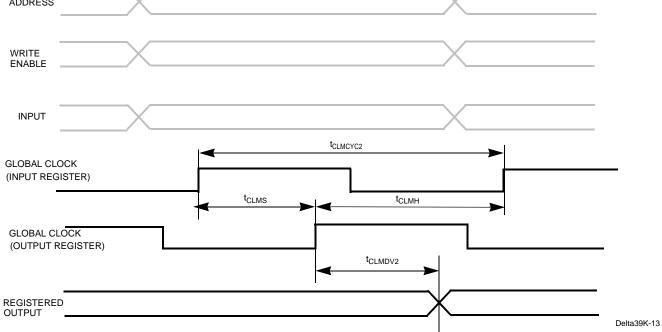

Each logic block cluster of the Delta39K contains two 8192-bit cluster memory blocks. *Figure 5* is a block diagram of the cluster memory block and the interface of the cluster memory block to the cluster PIM.

The output of the cluster memory block can be optionally registered to perform synchronous pipelining or to register asynchronous read and write operations. The output registers contain an asynchronous RESET which can be used in any type of sequential logic circuits (e.g., state machines).

There are four global clocks (GCLK[3:0]) and one local clock available for the input and the output registers. The local clock for the input registers is independent of the one used for the output registers. The local clock is generated in the user-design in a macrocell or comes from an I/O pin.

#### Cluster Memory Initialization

The cluster memory powers up in an undefined state, but is set to a user-defined known state during configuration. To facilitate the use of look-up-table (LUT) logic and ROM applications, the cluster memory blocks can be initialized with a given set of data when the device is configured at power up. For LUT and ROM applications, the user cannot write to memory blocks.

#### **Channel Memory**

The Delta39K architecture includes an embedded memory block at each crossing point of horizontal and vertical routing channels. The channel memory is a 4096-bit embedded memory block that can be configured as asynchronous or synchronous Single-Port RAM, Dual-Port RAM, ROM, or synchronous FIFO memory.

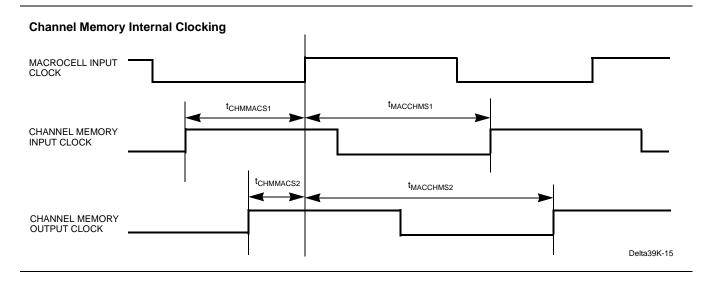

Data, address, and control inputs to the channel memory are driven from horizontal and vertical routing channels. All data and FIFO logic outputs drive dedicated tracks in the horizontal and vertical routing channels. The clocks for the channel memory block are selected from four global clocks and pin inputs from the horizontal and vertical channels. The clock muxes also include a polarity mux for each clock so that the user can choose an inverted clock.

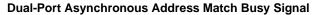

#### Dual-Port (Channel Memory) Configuration

Each port has distinct address inputs, as well as separate data and control inputs that can be accessed simultaneously. The inputs to the Dual-Port memory are driven from the horizontal and vertical routing channels. The data outputs drive dedicated tracks in the routing channels. The interface to the routing is such that Port A of the Dual-Port interfaces primarily with the horizontal routing channel and Port B interfaces primarily with the vertical routing channel.

Figure 5. Block Diagram of Cluster Memory Block

The clocks for each port of the Dual-Port configuration are selected from four global clocks and two local clocks. One local clock is sourced from the horizontal channel and the other from the vertical channel. The data outputs of the dual-port memory can also be registered. Clocks for the output registers are also selected from four global clocks and two local clocks. One clock polarity mux per port allows the use of true or complement polarity for input and output clocking purposes.

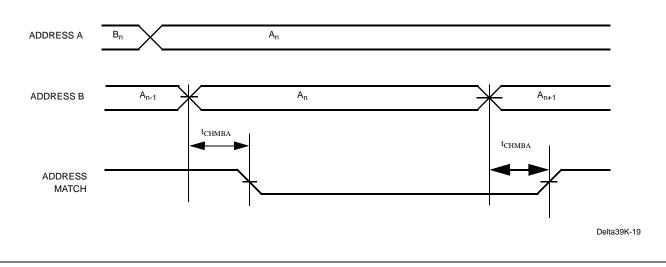

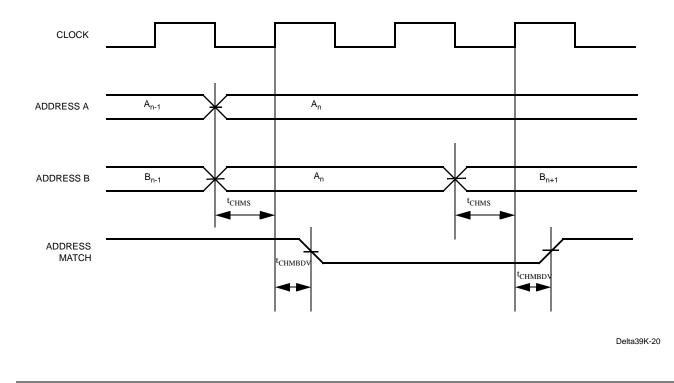

#### Arbitration

The Dual-Port configuration of the Channel Memory Block provides arbitration when both ports access the same address at the same time. Depending on the memory operation being attempted, one port always gets priority. See *Table 1* for details on which port gets priority for read and write operations. An active-LOW 'Address Match' signal is generated when an address collision occurs.

# Table 1. Arbitration Result: Address Match Signal Becomes Active

| Port A | Port B | Result of<br>Arbitration | Comment                                                                                                                                    |

|--------|--------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Read   | Read   | No arbitration required  | Both ports read at the same time                                                                                                           |

| Write  | Read   | Port A gets<br>priority  | If Port B requests first<br>then it will read the cur-<br>rent data. The output will<br>then change to the newly<br>written data by Port A |

| Read   | Write  | Port B gets<br>priority  | If Port A requests first<br>then it will read the cur-<br>rent data. The output will<br>then change to the newly<br>written data by Port B |

| Write  | Write  | Port A gets<br>priority  | Port B is blocked until<br>Port A is finished writing                                                                                      |

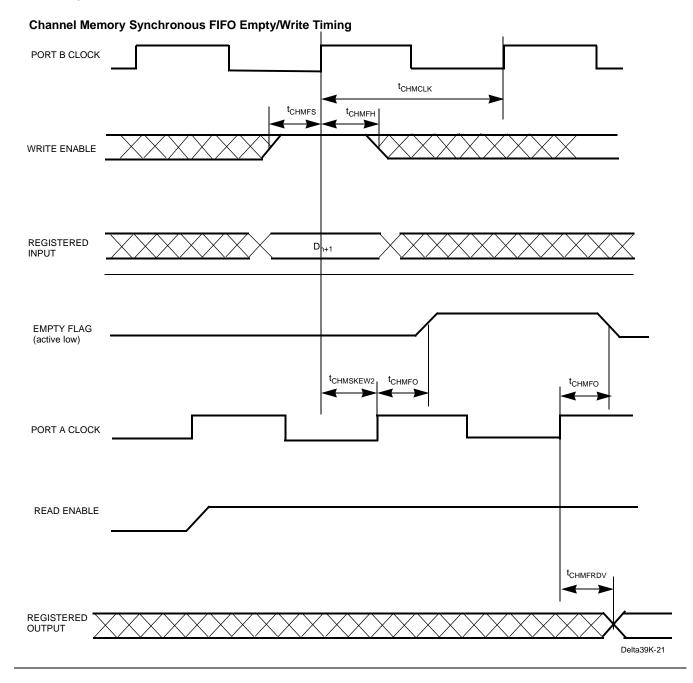

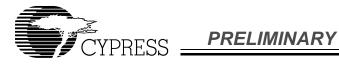

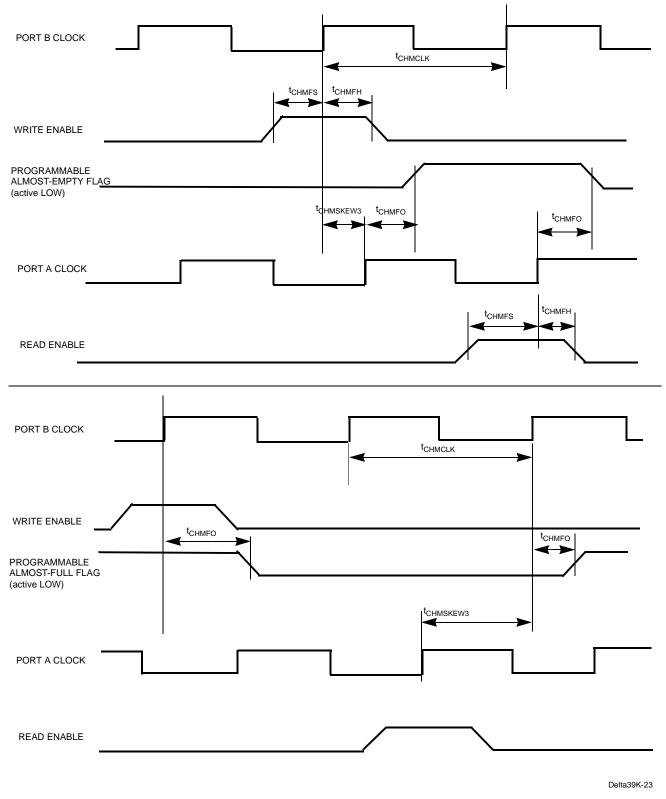

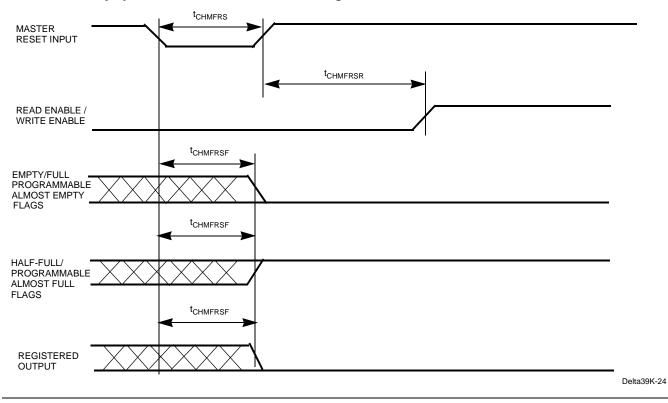

#### FIFO (Channel Memory) Configuration

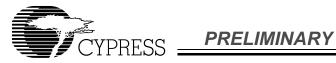

The channel memory blocks are also configurable as synchronous FIFO RAM. In the FIFO mode of operation, the channel memory block supports all normal FIFO operations without the use of any general-purpose logic resources in the device.

The FIFO block contains all of the necessary FIFO flag logic, including the read and write address pointers. The FIFO flags include an empty/full flag ( $\overline{EF}$ ), half-full flag ( $\overline{HF}$ ), and programmable almost-empty/full (PAEF) flag output. The FIFO configuration has the ability to perform simultaneous read and write operations using two separate clocks. These clocks may be tied together for a single operation or may run independently for asynchronous Read/Write (w.r.t. each other) applications. The data and control inputs to the FIFO block are driven from the horizontal or vertical routing channels. The data and flag outputs are driven onto dedicated routing tracks in both the horizontal and vertical routing channels. This allows the FIFO blocks to be expanded by using multiple FIFO blocks on the same horizontal or vertical routing channel without any speed penalty.

In FIFO mode, the write and read ports are controlled by separate clock and enable signals. The clocks for each port are selected from four global clocks and two local clocks.

One local clock is sourced from the horizontal channel and the other from the vertical channel. The data outputs from the read port of the FIFO can also be registered. One clock polarity mux per port allows using true or complement polarity for read and write operations. The write operation is controlled by the clock and the write enable pin. The read operation is controlled by the clock and the read enable pin. The enable pins can be sourced from horizontal or vertical channels.

Figure 6. Block Diagram of Channel Memory Block

The channel memory powers up in an undefined state, but is set to a user-defined known state during configuration. To facilitate the use of look-up-table (LUT) logic and ROM applications, the channel memory blocks can be initialized with a given set of data when the device is configured at power up. For LUT and ROM applications, the user cannot write to memory blocks.

#### **Channel Memory Routing Interface**

Similar to LBC outputs, the channel memory blocks feature dedicated tracks in the horizontal and vertical routing channels for the data outputs and the flag outputs, as shown in *Figure 6*. This allows the channel memory blocks to be expanded easily. These dedicated lines can be routed to I/O pips

panded easily. These dedicated lines can be routed to I/O pins as chip outputs or to other logic block clusters to be used in logic equations.

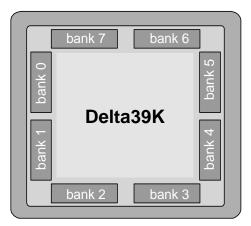

#### I/O Banks

The Delta39K interfaces the horizontal and vertical routing channels to the pins through I/O banks. There are 8 I/O banks per device as shown in *Figure 7*, and all I/Os from an I/O bank are located in the same section of a package for PCB layout convenience.

For each package type, Delta39K devices of different densities keep given pins in the same I/O banks. This supports and simplifies design migration across densities.

Each I/O bank contains several I/O cells, and each I/O cell contains an input/output register, an output enable register, programmable slew rate control and programmable bus hold control logic. Each I/O cell drives a pin output of the device; the cell also supplies an input to the device that connects to a dedicated track in the associated routing channel.

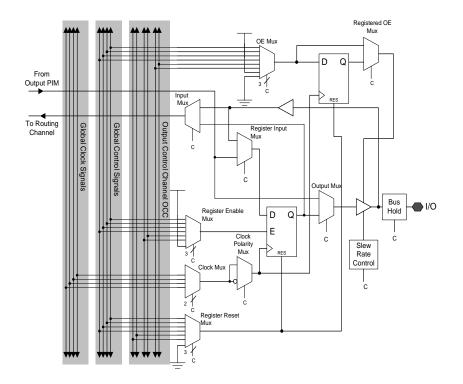

There are four dedicated inputs (GCTI[3:0]) that are used as Global Control Signals available to every I/O cell. These global control signals may be used as output enables, register resets and register clock enables as shown in *Figure 8*.

Each I/O bank can use any supported I/O standard by supplying appropriate V<sub>REF</sub> and V<sub>CCIO</sub> voltages. All the V<sub>REF</sub> and V<sub>CCIO</sub> pins in an I/O bank must be connected to the same V<sub>REF</sub> and V<sub>CCIO</sub> voltage respectively. This requirement restricts the number of I/O standards supported by an I/O bank at any given time.

The number of I/Os which can be used in each I/O bank depend on the type of I/O standards and the number of  $V_{CCIO}$  and GND pins being used. This restriction is derived from the electromigration limit of the  $V_{CCIO}$  and GND bussing on the chip. Please refer to the note on page 17 and the application

note titled "Delta39K Family Device I/O Standards and Configurations" for details.

Figure 7. Delta39K I/O Bank Block Diagram

#### I/O Standards

| I/O<br>Standard | V <sub>RE</sub> | <sub>F</sub> (V) | V <sub>CCIO</sub> | Termination<br>Voltage (V <sub>TT</sub> ) |

|-----------------|-----------------|------------------|-------------------|-------------------------------------------|

|                 | Min.            | Max.             |                   |                                           |

| LVTTL           | N               | /A               | 3.3V              | N/A                                       |

| LVCMOS          |                 |                  | 3.3V              | N/A                                       |

| LVCMOS3         |                 |                  | 3.0V              | N/A                                       |

| LVCMOS2         |                 |                  | 2.5V              | N/A                                       |

| LVCMOS18        |                 |                  | 1.8V              | N/A                                       |

| 3.3V PCI        |                 |                  | 3.3V              | N/A                                       |

| GTL+            | 0.9             | 1.1              | N/A               | 1.5                                       |

| SSTL3 I         | 1.3             | 1.7              | 3.3V              | 1.5                                       |

| SSTL3 II        | 1.3             | 1.7              | 3.3V              | 1.5                                       |

| SSTL2 I         | 1.15            | 1.35             | 2.5V              | 1.25                                      |

| SSTL2 II        | 1.15            | 1.35             | 2.5V              | 1.25                                      |

| HSTL I          | 0.68            | 0.9              | 1.5V              | 0.75                                      |

| HSTL II         | 0.68            | 0.9              | 1.5V              | 0.75                                      |

| HSTL III        | 0.68            | 0.9              | 1.5V              | 1.5                                       |

| HSTL IV         | 0.68            | 0.9              | 1.5V              | 1.5                                       |

Figure 8. Block Diagram of I/O Cell

#### I/O Cell

*Figure 8* is a block diagram of the Delta39K I/O cell. The I/O cell contains a three-state input buffer, an output buffer, and a register that can be configured as an input or output register. The output buffer has a slew rate control option that can be used to configure the output for a slower slew rate. The input of the device and the pin output can each be configured as registered or combinatorial; however, only one path can be configured as registered in a given design.

The output enable can be selected from one of the four global control signals or from one of two Output Control Channel (OCC) signals. The output enable can be configured as always enabled or always disabled or it can be controlled by one of the remaining inputs to the mux. The selection is done via a mux that includes  $V_{CC}$  and GND as inputs.

One of the global clocks can be selected as the clock for the I/O cell register. The clock mux output is an input to a clock polarity mux that allows the input/output register to be clocked on either edge of the clock.

#### Slew Rate Control

The ouput buffer has a slew rate control option. This allows the output buffer to slew at a fast rate (3 V/ns) or a slow rate (1 V/ns). All I/Os default to fast slew rate. For designs concerned with meeting FCC emissions standards the slow edge provides for lower system noise. For designs requiring very high performance the fast edge rate provides maximum system performance.

#### Programmable Bus Hold

On each I/O pin, user-programmable-bus-hold is included. Bus-hold, which is an improved version of the popular internal pull-up resistor, is a weak latch connected to the pin that does not degrade the device's performance. As a latch, bus-hold maintains the last state of a pin when the pin is placed in a high-impedance state, thus reducing system noise in bus-interface applications. Bus-hold additionally allows unused device pins to remain unconnected on the board, which is particularly useful during prototyping as designers can route new signals to the device without cutting trace connections to V<sub>CC</sub> or GND. For more information, see the application note "Understanding Bus-Hold – A Feature of Cypress CPLDs."

#### Clocks

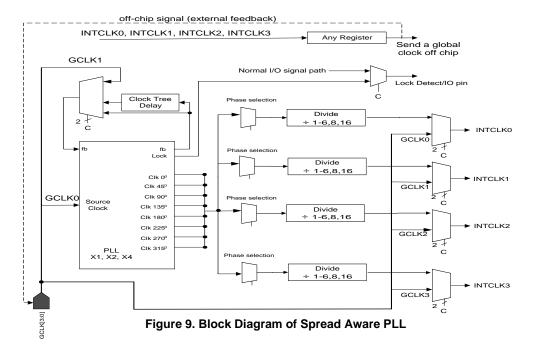

Delta39K has four dedicated clock input pins (GCLK[3:0]) to accept system clocks. One of these clocks (GCLK[0]) may be selected to drive an on-chip Phase-Locked Loop (PLL) for frequency modulation (see *Figure 9* for details).

The global clock tree for a Delta39K device can be driven by a combination of the dedicated clock pins and/or the PLL-derived clocks. The global clock tree consists of four global clocks that go to every macrocell, memory block, and I/O cell.

#### Clock Tree Distribution

The global clock tree performs two primary functions. First, the clock tree generates the four global clocks by multiplexing four dedicated clocks from the package pins and four PLL driven clocks. Second, the clock tree distributes the four global clocks to every cluster, channel memory, and I/O block on the die. The global clock tree is designed such that the clock skew is minimized while maintaining an acceptable clock delay.

#### Spread Aware<sup>™</sup> PLL

Each device in the Delta39K family features an on-chip PLL designed using Spread Aware technology for low EMI applications. In general, PLLs are used to implement time-division-multiplex circuits to achieve higher performance with fewer device resources.

For example, a system that operates on a 32-bit data path that runs at 40 MHz can be implemented with 16-bit circuitry that runs internally at 80 MHz. PLLs can also be used to take advantage of the positioning of the internally generated clock edges to shift performance towards improved setup, hold or clock-to-out times.

There are several frequency multiply (X1, X2, X4) and divide (/1, /2, /3, /4, /5, /6. /8, /16) options available to create a wide range of clock frequencies from a single clock input (GCLK[0]). For increased flexibility, there are seven phase shifting options which allow clock skew/de-skew by 45°, 90°, 135°, 180°, 225°, 270° or 315°.

The Voltage Controlled Oscillator (VCO), the core of the Delta39K PLL is designed to operate within the frequency range of 100 MHz to 266 MHz. Hence, the multiply option combined with input (GCLK[0]) frequency should be selected such that this VCO operating frequency requirement is met. This is demonstrated in *Table 2* (columns 1, 2, and 3).

Another feature of this PLL is the ability to drive the output clock (INTCLK) off the Delta39K chip to clock other devices on the board, as shown in *Figure 9* above. This off-chip clock is half the frequency of the output clock as it has to go through a register (I/O register or a macrocell register).

This PLL can also be used for board de-skewing purpose by driving a PLL output clock off-chip, routing it to the other devices on the board and feeding it back to the PLL's external feedback input (GCLK[1]). When this feature is used, only limited multiply, divide and phase shift options can be used.

*Table 2* describes the valid multiply and divide options that can be used without an external feedback. *Table 3* describes the valid multiply & divide options that can be used with an external feedback.

| Input Frequency                      | Valid Multiply Options |                               | Valid Divide Options |                                                           |                             |  |  |  |

|--------------------------------------|------------------------|-------------------------------|----------------------|-----------------------------------------------------------|-----------------------------|--|--|--|

| (GCLK[0])<br>f <sub>PLLI</sub> (MHz) | Value                  | VCO Output<br>Frequency (MHz) | Value                | Output Frequency (INTCLK[3:0])<br>f <sub>PLLO</sub> (MHz) | Off-chip Clock<br>Frequency |  |  |  |

| 25–33                                | 4                      | 100–133                       | 1–6, 8, 16           | 6.25–133                                                  | 3.12–66                     |  |  |  |

| 33–50                                | 4                      | 133–200                       | 1–6, 8, 16           | 8.33–200                                                  | 4.16–100                    |  |  |  |

| 50-66                                | 4                      | 200–266                       | 1–6, 8, 16           | 12.5–266                                                  | 6.25–133                    |  |  |  |

|                                      | 2                      | 100–133                       | 1–6, 8, 16           | 6.25–133                                                  | 3.12–66                     |  |  |  |

| 66–100                               | 2                      | 133–200                       | 1–6, 8, 16           | 8.3–200                                                   | 4.16–100                    |  |  |  |

| 100–133                              | 2                      | 200–266                       | 1–6, 8, 16           | 12.5–266                                                  | 6.25–133                    |  |  |  |

|                                      | 1                      | 100–133                       | 1–6, 8, 16           | 6.25–133                                                  | 3.12–66                     |  |  |  |

Table 2. PLL Multiply and Divide Options—without External Feedback

|                                                   | Valio | d Multiply Options            | Valid Divide Options |                                                      |                             |  |  |

|---------------------------------------------------|-------|-------------------------------|----------------------|------------------------------------------------------|-----------------------------|--|--|

| Input (GCLK) Frequency<br>f <sub>PLLI</sub> (MHz) | Value | VCO Output<br>Frequency (MHz) | Value                | Output (INTCLK) Frequency<br>f <sub>PLLO</sub> (MHz) | Off-chip Clock<br>Frequency |  |  |

| 50–66                                             | 1     | 100–133                       | 1                    | 100–133                                              | 50–66                       |  |  |

| 66–100                                            | 1     | 133–200                       | 1                    | 133–200                                              | 66–100                      |  |  |

| 100–133                                           | 1     | 200–266                       | 1                    | 200–266                                              | 100–133                     |  |  |

#### Table 3. PLL Multiply and Divide Options—with External Feedback

*Table 4* describes the valid phase shift options that can be used with or without an external feedback.

#### Table 4. PLL Phase Shift Options with and without External Feedback

| Without External Feedback                 | With External<br>Feedback |

|-------------------------------------------|---------------------------|

| 0°,45°, 90°, 135°, 180°, 225°, 270°, 315° | 0°                        |

Table 5 is an example of the effect of all the available divide and phase shift options on a VCO output of 250 MHz. It also shows the effect of division on the duty cycle of the resultant clock. Note that the duty cycle is 50-50 when a VCO output is divided by an even number. Also note that the phase shift applies to the VCO output and not to the divided output.

The Spread Aware PLL operates as specified for Delta39KV devices (2.5V/3.3V), but not Delta39KZ devices (1.8V). For more details on the architecture and operation of this PLL please refer to the application note entitled "Delta39K PLL and Clock Tree."

#### Table 5. Timing of Clock Phases for all Divide Options for a VCO Output Frequency of 250 MHz

| Divide<br>Factor | Period<br>(ns) | Duty<br>Cy-<br>cle% | 0°<br>(ns) | 45°<br>(ns) | 90°<br>(ns) | 135°<br>(ns) | 180°<br>(ns) | 225°<br>(ns) | 270°<br>(ns) | 315°<br>(ns) |

|------------------|----------------|---------------------|------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|

| 1                | 4              | 40-60               | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 2                | 8              | 50                  | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 3                | 12             | 33-67               | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 4                | 16             | 50                  | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 5                | 20             | 40-60               | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 6                | 24             | 50                  | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 8                | 32             | 50                  | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

| 16               | 64             | 50                  | 0          | 0.5         | 1.0         | 1.5          | 2.0          | 2.5          | 3.0          | 3.5          |

#### **Timing Model**

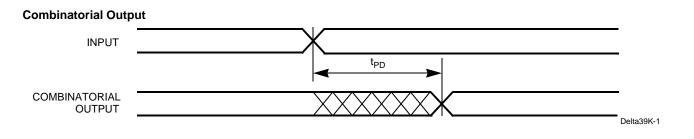

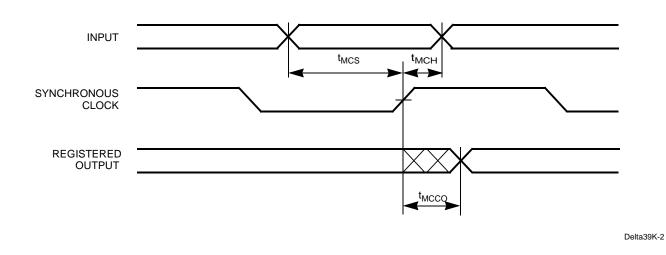

One important feature of the Delta39K family is the simplicity of its timing. All combinatorial and registered/synchronous delays are worst case and system performance is static (as shown in the AC specs section) as long as data is routed through the same horizontal and vertical channels. *Figure 10* illustrates the true timing model for the 200-MHz devices. For synchronous clocking of macrocells, a delay is incurred from macrocell clock to macrocell clock of separate Logic Blocks within the same cluster, as well as separate Logic Blocks within different clusters. This is respectively shown as  $t_{SCS2}$  and  $t_{SCS2}$  in *Figure 10*. For combinatorial paths, any input to any output (from corner to corner on the device), incurs a worst-case delay in the 39K100 regardless of the amount of logic or which horizontal and vertical channels are used. This is the  $t_{PD}$

shown in *Figure 10.* For synchronous systems, the input setup time to the output macrocell register and the clock to output time are shown as the parameters  $t_{MCS}$  and  $t_{MCCO}$  shown in the *Figure 10.* These measurements are for any output and synchronous clock, regardless of the logic placement.

The Delta39K features:

- no dedicated vs. I/O pin delays

- no penalty for using 0–16 product terms

- no added delay for steering product terms

- no added delay for sharing product terms

- · no output bypass delays

The simple timing model of the Delta39K family eliminates unexpected performance penalties.

Figure 10. Timing Model for 39K100 Device

#### IEEE 1149.1 Compliant JTAG Operation

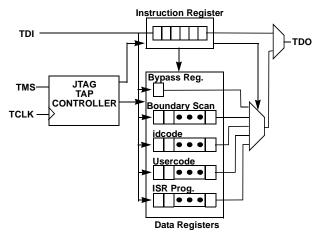

The Delta39K family has an IEEE 1149.1 JTAG interface for both Boundary Scan and ISR operations.

Four dedicated pins are reserved on each device for use by the Test Access Port (TAP).

#### Boundary Scan

The Delta39K family supports Bypass, Sample/Preload, Extest, Intest, Idcode and Usercode boundary scan instructions. The JTAG interface is shown in *Figure 11*.

Figure 11. JTAG Interface

#### In-System Reprogramming (ISR)

In-System Reprogramming is the combination of the capability to program or reprogram a device on-board, and the ability to support design changes without changing the system timing or device pinout. This combination means design changes during debug or field upgrades do not cause board respins. The Delta39K family implements ISR by providing a JTAG compliant interface for on-board programming, robust routing resources for pinout flexibility, and a simple timing model for consistent system performance.

#### Configuration

Each device of the Delta39K family is available in a volatile and a Self-Boot package. Cypress's CPLD boot EEPROM is used to store configuration data for the volatile solution and an embedded on-chip FLASH memory device is used for the Self-Boot solution.

For volatile Delta39K packages, programming is defined as the loading of a user's design into the external CPLD boot EEPROM. For Self-Boot Delta39K packages, programming is defined as the loading of a user's design into the on-chip FLASH internal to the Delta39K package. Configuration is defined as the loading of a user's design into the Delta39K die.

Configuration can begin in two ways. It can be initiated by toggling the *Reconfig* pin from LOW to HIGH, or by issuing the appropriate IEEE std 1149.1 JTAG instruction to the Delta39K device via the JTAG interface. There are two IEEE std 1149.1 JTAG instructions that initiate configuration of the Delta39K. The *Self Config* instruction causes the Delta39K to (re)configure with data stored in the serial boot PROM or the embedded FLASH memory. The *Load Config* instruction causes the Delta39K to (re)configure according to data provided by other sources such as a PC, automatic test equipment (ATE), or an embedded micro-controller/processor via the JTAG interface. For more information on configuring Delta39K devices, refer to the application note titled "Configuring Delta39K/Quantum38K" application note at http://www.cypress.com.

There are two configuration options available for issuing the IEEE std 1149.1 JTAG instructions to the Delta39K. The first method is to use a PC with the C3ISR programming cable and software. With this method, the ISR pins of the Delta39K devices in the system are routed to a connector at the edge of the printed circuit board. The C3ISR programming cable is then connected between the PC and this connector. A simple configuration file instructs the ISR software of the programming operations to be performed on the Delta39K devices in the system. The ISR software then automatically completes all of the necessary data manipulations required to accomplish configuration, reading, verifying, and other ISR functions. For more information on the Cypress ISR interface, see the ISR Programming Kit data sheet (CY3900i).

The second configuration option for the Delta39K is to utilize the embedded controller or processor that already exists in the system. The Delta39K ISR software assists in this method by converting the device HEX file into the ISR serial stream that contains the ISR instruction information and the addresses and data of locations to be configured. The embedded controller then simply directs this ISR stream to the chain of Delta39K devices to complete the desired reconfiguration or diagnostic operations. Contact your local sales office for information on availability of this option.

#### Programming

The on-chip FLASH device of the Delta39K Self-Boot package is programmed by issuing the appropriate IEEE std 1149.1 JTAG instruction to the internal FLASH memory via the JTAG interface. This can be done automatically using ISR/STAPL software. The configuration bits are sent from a PC through the JTAG port into the Delta39K via the C3ISR programming cable. The data is then internally passed from Delta39K to the on-chip FLASH. For more information on how to program the Delta39K through ISR/STAPL, please refer to the ISR/STAPL User Guide.

The external CPLD boot EEPROM used to store configuration data for the Delta39K volatile package is programmed through Cypress's CYDH2200E CPLD Boot PROM Programming Kit via a two-wire interface. For more information on how to program the CPLD boot EEPROM, please refer to the data sheet titled "CYDH2200E CPLD Boot PROM Programming Kit." For more information on the architecture and timing specification of the boot EEPROM, refer to the data sheet titled "CPLD Boot EEPROM."

#### **Third-Party Programmers**

Cypress support is available on a wide variety of third-party programmers. All major programmers (including BP Micro, System General, Hi-Lo) support the Delta39K family.

#### **Development Software Support**

#### Warp

Warp is a state-of-the-art design environment for designing with Cypress programmable logic. Warp utilizes a subset of

IEEE 1076/1164 VHDL and IEEE 1364 as the Hardware Description Language (HDL) for design entry. *Warp* accepts VHDL or Verilog input, synthesizes and optimizes the entered design, and outputs a configuration bitstream for the desired Delta39K device. For simulation, *Warp* provides a graphical waveform simulator as well as VHDL and Verilog Timing Models.

VHDL and Verilog are open, powerful, non-proprietary Hardware Description Languages (HDLs) that are standards for behavioral design entry and simulation. HDL allows designers to learn a single language that is useful for all facets of the design process.

#### **Third-Party Software**

Cypress products are supported in a number of third-party design entry and simulation tools. Refer to the third-party software data sheet or contact your local sales office for a list of currently supported third party vendors.

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                               | –65°C to +150°C |

|---------------------------------------------------|-----------------|

| Soldering Temperature                             | 220°C           |

| Ambient Temperature with<br>Power Applied         | –40°C to +85°C  |

| Junction Temperature                              | 135°C           |

| V <sub>CC</sub> to Ground Potential (39KZ device) | –0.5V to 2.5V   |

### **Operating Range**

| V <sub>CC</sub> to Ground Potential (39KV device)0.5V to 4.6V |

|---------------------------------------------------------------|

| V <sub>CCIO</sub> to Ground Potential0.5V to 4.6V             |

| DC Voltage Applied to Outputs in High Z State –0.5V to 4.5V   |

| DC Input voltage0.5V to 4.5V                                  |

| DC Current into Outputs<br>±20 mA <sup>[6]</sup>              |

| Static Discharge Voltage (per MIL-STD-8883,                   |

| Method 3015)>2001V                                            |

| Latch-Up Current>200 mA                                       |

| Range      | Ambient<br>Temperature | Junction<br>Temperature | Output<br>Condition | V <sub>CCIO</sub>          | v <sub>cc</sub>      | V <sub>CCJTAG</sub> /<br>V <sub>CCCNFG</sub> | V <sub>CCPLL</sub>         | V <sub>CCPRG</sub> |

|------------|------------------------|-------------------------|---------------------|----------------------------|----------------------|----------------------------------------------|----------------------------|--------------------|

|            | 0°C to +70°C           | 0°C to +85°C            | 3.3V                | 3.3V ± 0.3V                |                      |                                              |                            |                    |

| Commercial |                        |                         | 2.5V                | 2.5V ± 0.2V                | 3.3V ± 0.3V<br>or    | Same as                                      | Same<br>as V <sub>CC</sub> | 3.3V               |

| Commercial |                        |                         | 1.8V                | 1.8V ± 0.15V               | 2.5V ± 0.2V          | V <sub>CCIO</sub>                            |                            | ±                  |

|            |                        |                         | 1.5V                | 1.5V ± 0.1V <sup>[5]</sup> | (39KV)               |                                              |                            | 0.3V               |

|            | -40°C to +85°C         | -40°C to +100°C         | 3.3V                | 3.3V ± 0.3V                |                      |                                              |                            |                    |

| Industrial |                        |                         | 2.5V                | 2.5V ± 0.2V                | 1.8V±0.15V<br>(39KZ) |                                              |                            |                    |

| muusinai   |                        |                         | 1.8V                | 1.8V ± 0.15V               | (00112)              |                                              |                            |                    |

|            |                        |                         | 1.5V                | 1.5V ± 0.1V <sup>[5]</sup> |                      |                                              |                            |                    |

### **DC Characteristics**

|                                |                                                                                  |                                                               | V <sub>CCIO</sub> | = 3.3 V | V <sub>CCIO</sub> | = 2.5 V | V <sub>CCIO</sub> | = 1.8 V |      |

|--------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------|---------|-------------------|---------|-------------------|---------|------|

| Parameter                      | Description                                                                      | Test Conditions                                               | Min.              | Max.    | Min.              | Max.    | Min.              | Max.    | Unit |

| V <sub>DRINT</sub>             | Data Retention V <sub>CC</sub> Voltage<br>(config data may be lost below this)   |                                                               | 1.5               |         | 1.5               |         | 1.5               |         | V    |

| V <sub>DRIO</sub>              | Data Retention V <sub>CCIO</sub> Voltage<br>(config data may be lost below this) |                                                               | 1.2               |         | 1.2               |         | 1.2               |         | V    |

| I <sub>IX</sub>                | Input Leakage Current                                                            | $GND \le V_I \le 3.6V$                                        | -10               | 10      | -10               | 10      | -10               | 10      | μA   |

| I <sub>OZ</sub>                | Output Leakage Current                                                           | $GND \le V_O \le V_{CCIO}$                                    | -10               | 10      | -10               | 10      | -10               | 10      | μA   |

| I <sub>OS</sub> <sup>[7]</sup> | Output Short Circuit Current                                                     | V <sub>CCIO</sub> = Max.,<br>V <sub>OUT</sub> = 0.5V          |                   | -160    |                   | -160    |                   | -160    | mA   |

| I <sub>BHL</sub>               | Input Bus Hold LOW Sustaining<br>Current                                         | V <sub>CC</sub> = Min.,<br>V <sub>PIN</sub> = V <sub>IL</sub> | +40               |         | +30               |         | +25               |         | μΑ   |

| I <sub>BHH</sub>               | Input Bus Hold HIGH Sustaining<br>Current                                        | V <sub>CC</sub> = Min.,<br>V <sub>PIN</sub> = V <sub>IH</sub> | -40               |         | -30               |         | -25               |         | μΑ   |

| I <sub>BHLO</sub>              | Input Bus Hold LOW Overdrive Current                                             | V <sub>CC</sub> = Max.                                        |                   | +250    |                   | +200    |                   | +150    | μΑ   |

| I <sub>BHHO</sub>              | Input Bus Hold HIGH Overdrive Current                                            | V <sub>CC</sub> = Max.                                        |                   | -250    |                   | -200    |                   | -150    | μA   |

| Notes:                         |                                                                                  | •                                                             | •                 | •       |                   |         | •                 | •       | •    |

6. DC current into outputs is 36 mA with HSTL III, 48 mA with HSTL IV and 36 mA with GTL+ (with  $25\Omega$  pull-up resistor and  $V_{TT} = 1.5$ 7. Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second.  $V_{OUT} = 0.5V$  has been chosen to avoid test problems caused by tester ground degradation. Tested initially and after any design or process changes that may affect these parameters.

### Capacitance

| Parameter        | Description                              | Test Conditions                                   | Min. | Max. | Unit |

|------------------|------------------------------------------|---------------------------------------------------|------|------|------|

| C <sub>I/O</sub> | Input/Output Capacitance                 | V <sub>in</sub> =V <sub>CCIO</sub> @ f=1 MHz 25°C |      | 10   | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance                 | V <sub>in</sub> =V <sub>CCIO</sub> @ f=1 MHz 25°C | 5    | 12   | pF   |

| C <sub>PCI</sub> | PCI Compliant <sup>[8]</sup> Capacitance | V <sub>in</sub> =V <sub>CCIO</sub> @ f=1 MHz 25°C |      | 8    | pF   |

## DC Characteristics (IO)<sup>[9]</sup>

| Input/             | V <sub>REI</sub> | <sub>F</sub> (V) |                          | ٧c                  | <sub>он</sub> (V)        | Vo                  | _ (V)                     | V <sub>IH</sub>                              | (V)                    | V <sub>IL</sub> (V) |                       |  |

|--------------------|------------------|------------------|--------------------------|---------------------|--------------------------|---------------------|---------------------------|----------------------------------------------|------------------------|---------------------|-----------------------|--|

| Output<br>Standard | Min.             | Мах.             | v <sub>ccio</sub><br>(V) | @ I <sub>OH</sub> = | V <sub>OH</sub> (min.)   | @ I <sub>OL</sub> = | V <sub>OL</sub><br>(max.) | Min.                                         | Max.                   | Min.                | Max.                  |  |

| LVTTL              | N/               | /A               | 3.3                      | –4 mA               | 2.4                      | 4 mA                | 0.4                       | 2.0 V                                        | V <sub>CCIO</sub> +0.3 | -0.3V               | 0.8V                  |  |

| LVCMOS             |                  |                  | 3.3                      | –0.1 mA             | V <sub>CCIO</sub> -0.2v  | 0.1 mA              | 0.2                       | 2.0 V                                        | V <sub>CCIO</sub> +0.3 | -0.3V               | 0.8V                  |  |

| LVCMOS3            |                  |                  | 3.0                      | –0.1 mA             | V <sub>CCIO</sub> -0.2v  | 0.1mA               | 0.2                       | 2.0 V                                        | V <sub>CCIO</sub> +0.3 | -0.3V               | 0.8V                  |  |

|                    |                  |                  | 2.5                      | –0.1 mA             | 2.1                      | 0.1 mA              | 0.2                       | 1.7 V                                        | V <sub>CCIO</sub> +0.3 | -0.3V               | 0.7V                  |  |

| LVCMOS2            |                  |                  |                          | –1.0 mA             | 2.0                      | 1.0 mA              | 0.4                       |                                              |                        |                     |                       |  |

|                    |                  |                  |                          | –2.0 mA             | 1.7                      | 2.0 mA              | 0.7                       |                                              |                        |                     |                       |  |

| LVCMOS18           |                  |                  | 1.8                      | –0.1 mA             | V <sub>CCIO</sub> -0.2v  | 0.1mA               | 0.2                       | 0.65V <sub>CCIO</sub> V <sub>CCIO</sub> +0.3 |                        | -0.3V               | 0.35V <sub>CCIO</sub> |  |

|                    |                  |                  |                          | – 2 mA              | V <sub>CCIO</sub> -0.45v | 2.0 mA              | 0.45                      |                                              |                        |                     |                       |  |

| 3.3V PCI           |                  |                  | 3.3                      | –0.5 mA             | 0.9V <sub>CCIO</sub>     | 1.5 mA              | 0.1V <sub>CCIO</sub>      | 0.5V <sub>CCIO</sub>                         | V <sub>CCIO</sub> +0.5 | -0.5V               | 0.3V <sub>CCIO</sub>  |  |

| GTL+               | 0.9              | 1.1              | Note 10                  |                     |                          | Note 11             | 0.6                       | V <sub>REF</sub> +0.2                        |                        |                     | V <sub>REF</sub> -0.2 |  |

| SSTL3 I            | 1.3              | 1.7              | 3.3                      | –8 mA               | V <sub>CCIO</sub> -1.1v  | 8 mA                | 0.7                       | V <sub>REF</sub> +0.2                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> -0.2 |  |

| SSTL3 II           | 1.3              | 1.7              | 3.3                      | –16 mA              | V <sub>CCIO</sub> –0.9v  | 16 mA               | 0.5                       | V <sub>REF</sub> +0.2                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> 0.2  |  |

| SSTL2 I            | 1.15             | 1.35             | 2.5                      | –7.6 mA             | V <sub>CCIO</sub> -0.62v | 7.6 mA              | 0.54                      | V <sub>REF</sub> +1.8                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> 0.18 |  |

| SSTL2 II           | 1.15             | 1.35             | 2.5                      | –15.2 mA            | V <sub>CCIO</sub> -0.43v | 15.2 mA             | 0.35                      | V <sub>REF</sub> +1.8                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> 0.18 |  |

| HSTL I             | 0.68             | 0.9              | 1.5                      | –8 mA               | V <sub>CCIO</sub> -0.4v  | 8 mA                | 0.4                       | V <sub>REF</sub> +1.0                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> 0.1  |  |

| HSTL II            | 0.68             | 0.9              | 1.5                      | –16 mA              | V <sub>CCIO</sub> –0.4v  | 16 mA               | 0.4                       | V <sub>REF</sub> +1.0                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> -0.1 |  |

| HSTL III           | 0.68             | 0.9              | 1.5                      | –8 mA               | V <sub>CCIO</sub> -0.4v  | 24 mA               | 0.4                       | V <sub>REF</sub> +1.0                        | V <sub>CCIO</sub> +0.3 | -0.3V               | V <sub>REF</sub> -0.1 |  |

| HSTL IV            | 0.68             | 0.9              | 1.5                      | –8 mA               | V <sub>CCIO</sub> -0.4v  | 48 mA               | 0.4                       | V <sub>REF</sub> +1.0                        | V <sub>CCIO</sub> +0.3 | –0.3V               | V <sub>REF</sub> -0.1 |  |

#### Notes:

PCI spec (rev 2.2) requires the IDSEL pin to have capacitance less than or equal to 8 pF. Document titled "Delta39K Pin Tables" identifies all the I/O pins, in a given package, which can be used as IDSEL in a PCI design. All other I/O pins meet the PCI requirement of capacitance less than or equal to 10 pf.

The number of I/Os which can be used in each I/O bank depends on the type of I/O standards and the number of V<sub>CCIO</sub> and GND pins being used. Please refer to the application note titled "Delta39K Family Device I/O Standards and Configurations" for details.

• The source current limit per I/O bank per Vccio pin is 165 mA

• The sink current limit per I/O bank per GND pin is 230 mA 10. See "Power-up Sequence Requirements" below for  $V_{CCIO}$  requirement.

11.  $25\Omega$  resistor terminated to termination voltage of 1.5V.

### **Configuration Parameters**

| Parameter             | Description                               | Min. | Unit |

|-----------------------|-------------------------------------------|------|------|

| t <sub>RECONFIG</sub> | Reconfig pin LOW time before it goes HIGH | 200  | ns   |

#### **Power-up Sequence Requirements**

- Upon power-up, all the outputs remain three-stated until all the  $V_{CC}$  pins have powered-up to the nominal voltage and the part has completed configuration.

- The part will not start configuration until V<sub>CC</sub>, V<sub>CCIO</sub>, V<sub>CCJTAG</sub>, V<sub>CCCNFG</sub>, V<sub>CCPLL</sub> and V<sub>CCPRG</sub> have reached nominal voltage.

- $V_{CC}$  pins can be powered up in any order. This includes  $V_{CC}$ ,  $V_{CCIO}$ ,  $V_{CCJTAG}$ ,  $V_{CCCNFG}$ ,  $V_{CCPLL}$  and  $V_{CCPRG}$ .

- All  $\mathsf{V}_{\mathsf{CCIO}}\mathsf{s}$  on a bank should be tied to the same potential and powered up together.

- All V<sub>CCIO</sub>s (even the unused banks) need to be powered up to at least 1.5V before configuration has completed.

- Maximum ramp time for all  $V_{CC} s$  should be 0V to nominal voltage in 100 ms.

### Switching Characteristics - Parameter Descriptions Over the Operating Range <sup>[12]</sup>

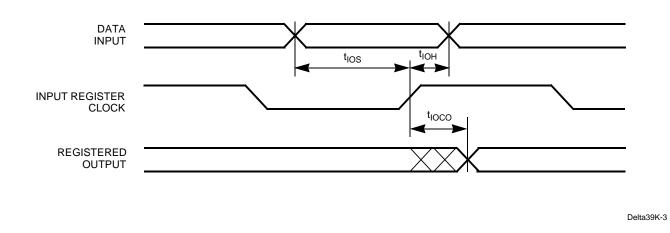

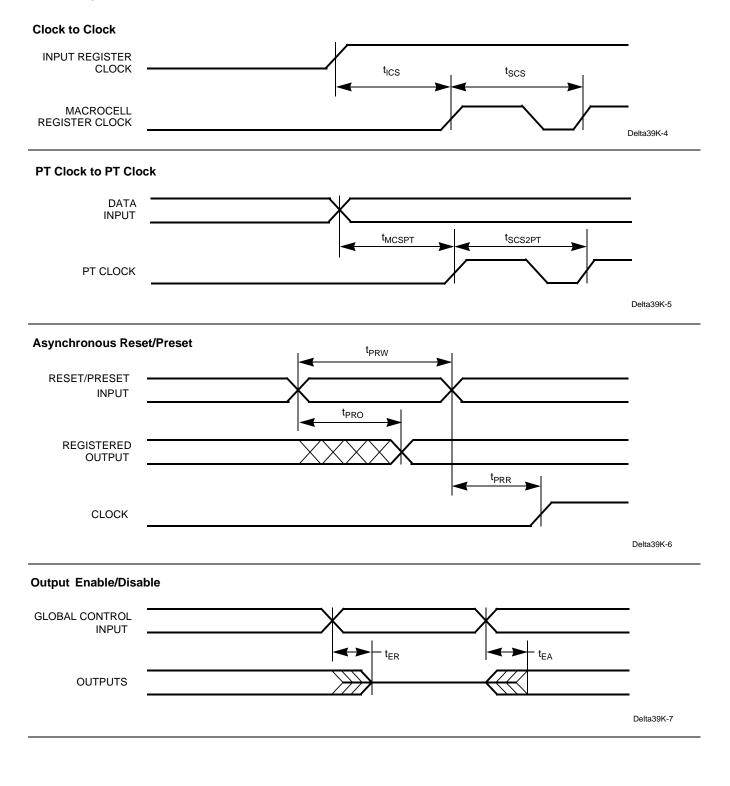

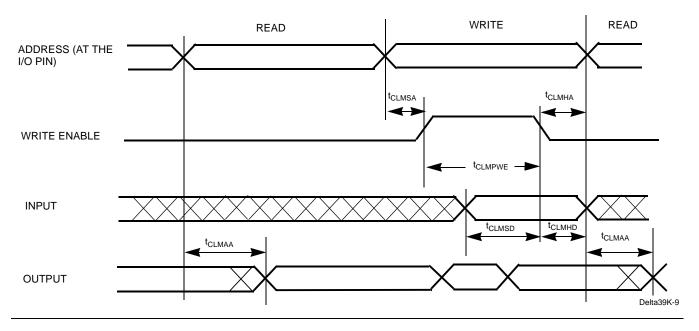

| Implementation         output on the horizontal or vertical channel associated with that cluster           te <sub>R</sub> Global control to output enable           te <sub>R</sub> Global control to output disable           te <sub>R</sub> Asynchronous macrocell RESET or PRESET recovery time from any pin input on the horizontal or vertical channel associated with the cluster the macrocell is in           term         Asynchronous macrocell RESET or PRESET remany pin input on the horizontal or vertical channel associated with the cluster that the macrocell is in to any pin output on those same channels           term         Asynchronous macrocell RESET or PRESET remany pin input on the same channels           theR         Asynchronous macrocell RESET or PRESET remany pin input on the norizontal or vertical channel associated with that input the or any control to a discover on the channel associated with that input pin relative to a global clock           Spichronous Clocking Parameters         Set-up time of any input pin to a macrocell in any cluster on the channel associated with that input pin, relative to a global clock           tucco         Global clock to output of any macrocell to any output pin on the horizontal or vertical channel associated with that pin, relative to a global clock           tucco         Global clock to output of any input pin to the I/O cell register associated with that pin, relative to a global clock trock           tucco         Global clock to macrocell clock through array logic within the same cluster           tucco         Clock to output of an V/o cell register clock on                                                                                                                                                                                                                                                                                                                    | Parameter          | Description                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD         output on the horizontal or vertical channel associated with that cluster           teA         Global control to output enable           teR         Global control to output disable           teR         Asynchronous macrocell RESET or PRESET reavery time from any pin input on the horizontal or vertical channel associated with the cluster the macrocell is in           teRO         Asynchronous macrocell RESET or PRESET from any pin input on the horizontal or vertical channel associated with the cluster that the macrocell is in to any pin output on those same channels           teRW         Asynchronous macrocell RESET or PRESET from any pin input on the same channels           Spectronous Clocking Parameters         Set-up time of any input pin to a macrocell in any cluster on the channel associated with that input pin relative to a global clock           tMCC         Global clock to output of any ancrocell to any output pin on the horizontal or vertical channel associated with that input pin, relative to a global clock to a global clock to a global clock to a global clock to clock to macrocell is in           tMCCO         Global clock to output of any input pin to the I/O cell register associated with that pin, relative to a global clock to a global clock to a global clock to clock to macrocell clock through array logic within the same cluster           tioco         Clock to output of an Vio cell register to the output pin associated with that register           tioco         Clock to output of any macrocell clock through array logic within the same cluster           tioco         Clock                                                                                                                                                                                                                                                                                                                           | Combinatorial M    |                                                                                                                                                                                               |

| ER         Global control to output disable           tPR         Asynchronous macrocell RESET or PRESET recovery time from any pin input on the horizontal or vertic channel associated with the cluster the macrocell is in on any pin input on the horizontal or vertical channel associated with the cluster that the macrocell is in to any pin output on those same channels           tPRO         Asynchronous macrocell RESET or PRESET from any pin input on the horizontal or vertical channel associated with the cluster that the macrocell is in to any pin output on those same channels           tPRW         Asynchronous macrocell RESET or PRESET minimum pulse width, from any pin input to a macrocell the faithest cluster on the horizontal or vertical channel the pin is associated with that input pin relative to a global clock           Structor         Set-up time of any input pin to a macrocell in any cluster on the channel associated with that input pin relative to a global clock           tMCH         Hold time of any input pin to a macrocell to any output pin on the horizontal or vertical channel associated with that input pin, relative to a global clock           tlogs         Set-up time of any input pin to the I/O cell register associated with that pin, relative to a global clock to output of an I/O cell register to the output pin associated with that register           tlogs         Det-up time of any input pin to the I/O cell register associated with that pin, relative to a global clock to Global clock to to acrocell clock through array logic in different clusters on the same channel           tlogs         Det-up time of any macrocell clock through array logic in different clusters on the same channel <td>t<sub>PD</sub></td> <td>Delay from any pin input, through any cluster on the channel associated with that pin input, to any pin output on the horizontal or vertical channel associated with that cluster</td> | t <sub>PD</sub>    | Delay from any pin input, through any cluster on the channel associated with that pin input, to any pin output on the horizontal or vertical channel associated with that cluster             |