#### Applications

- Low voltage, high density systems with Intermediate Bus Architectures (IBA)

- Point-of-load regulators for high performance DSP, FPGA, ASIC, and microprocessor applications

- Desktops, servers, and portable computing

- Broadband, networking, optical, and communications systems

#### **Benefits**

- Integrates digital power conversion with intelligent

power management

- Eliminates the need for external power management components

- Programmable via industry-standard I<sup>2</sup>C communication bus (DPM required)

- Reduce the number of discrete parts within a power system.

- Reduces board space, system cost, complexity and time to market

#### Features

- Input voltage range: 8V–14V

- High continuous output current: 5A

- Wide digitally programmable output voltage range: 0.7V–5.5V

- Single-wire serial communication bus between dPOL and Digital Power Manager (DPM)

- Programmable dynamic output voltage positioning for better load transient response

- Overcurrent, overvoltage, undervoltage, and overtemperature protections with programmable thresholds and hiccup or latching modes

- Programmable fixed switching frequency: 500KHz or 1.0MHz

- Programmable switching frequency phasing

- Programmable turn-on and turn-off delays

- Programmable turn-on and turn-off output voltage slew rates with tracking protection

- In-System Loop Identification (SysID) through pseudo-random noise injection

- Power Good signal with programmable threshold and delay

- Advance fault management and propagation

- Start up into pre-biased load

- Real time voltage, current, and temperature measurements, monitoring, and reporting

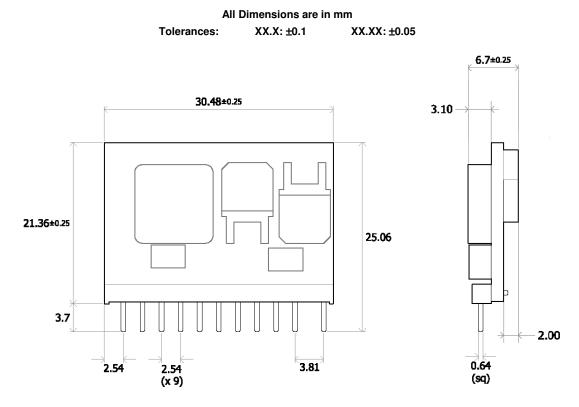

- Industry standard size through-hole single-in-line vertical package: 1.2"x0.26x0.84"

- Compatible with conventional pick-and-place equipment

- Wide operating temperature range -40 ℃ 85 ℃

- UL 60950-1/CSA 22.2 No. 60950-1-07 Second Edition, IEC 60950-1: 2005, and EN 60950-1:2006 (pending)

#### Description

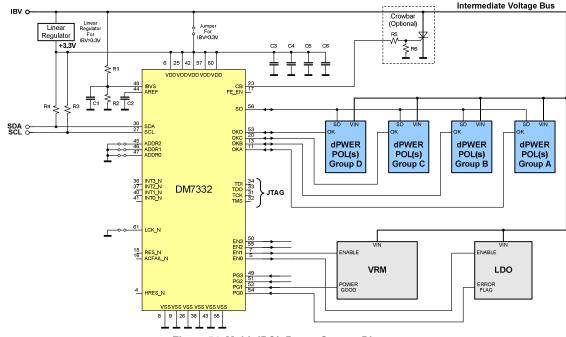

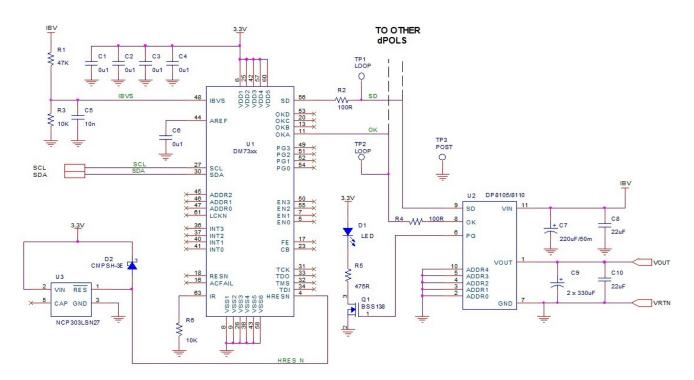

Power-One's DP8105 is an intelligent, fully programmable step-down point-of-load DC-DC converter integrating digital power conversion and intelligent power management. The dPOL is used in conjunction with DM7300 Series Digital Power Manager (DPM), and completely eliminates the need for external components for output voltage setting, sequencing, tracking, protection, monitoring, error amplifier compensation and reporting. All performance parameters of the DP8105 are programmable and managed through Digital Power Manager via the industry-standard I<sup>2</sup>C communication bus and can be changed by a user at any time during product development and operation. Telemetry data is available in real time and can be accessed over the I<sup>2</sup>C bus.

www.power-one.com

#### **Reference Documents:**

- DM7300 Digital Power Manager Data Sheet

- DM7300 Digital Power Manager Programming Manual

- Power-One I2C GEN II Graphical User Interface

- DM00056-KIT USB to I<sup>2</sup>C Adapter Kit. User Manual

#### 1. Ordering Information

| DP                 | 81                             | 05                 | G                                                                | -    | ZZ                                                 |

|--------------------|--------------------------------|--------------------|------------------------------------------------------------------|------|----------------------------------------------------|

| Product<br>family: | Series:<br>Intelligent<br>dPOL | Output<br>Current: | <b>RoHS compliance:</b><br><b>G</b> - RoHS compliant for all six | Dash | Packaging Option <sup>1</sup><br>T100 - 100pcs T&R |

| dPWER <sup>®</sup> | Converter                      | 5A                 | substances                                                       |      | <b>Q1</b> – 1pc sample for evaluation only         |

Example: **DP8105G-T100**: A 100-piece tray of RoHS compliant dPOL converters. Each dPOL converter is labeled DP8105G.

#### 2. Absolute Maximum Ratings

Stresses in excess of the absolute maximum ratings may cause performance degradation, adversely affect long-term reliability, and cause permanent damage to the converter.

| Parameter                                                 | Conditions/Description                | Min | Max | Units |

|-----------------------------------------------------------|---------------------------------------|-----|-----|-------|

| Inductor or<br>Printed Circuit Board (PCB)<br>Temperature | Input Voltage applied                 | -40 | 125 | °C    |

| Input Voltage                                             | 250ms Transient                       |     | 15  | VDC   |

| Output Current                                            | (See Output Current De-rating Curves) | -4  | 5   | ADC   |

#### 3. Environmental and Mechanical Specifications

| Parameter                  | Conditions/Description                       | Min            | Nom | Max | Units |

|----------------------------|----------------------------------------------|----------------|-----|-----|-------|

| Ambient Temperature Range  |                                              | -40            |     | 85  | °C    |

| Storage Temperature (Ts)   |                                              | -55            |     | 125 | °C    |

| Weight                     |                                              |                |     | 8   | grams |

| MTBF                       | Calculated Per Telcordia Technologies SR-332 | 6.24           |     |     | MHrs  |

| Peak Reflow Temperature    | DP8105G                                      | 245 260        |     | °C  |       |

| Lead Plating               | DP8105G                                      | 100% Matte Tin |     |     |       |

| Moisture Sensitivity Level | DP8105G                                      | 3              |     |     |       |

<sup>1</sup> Packaging option is used only for ordering and not included in the part number printed on the dPOL converter label.

#### 4. Electrical Specifications

Specifications apply at the input voltage from 8V to 14V, output load from 0 to 5A, ambient temperature from -40 °C to 85 °C. Test conditions include an output filter with 2 x  $330\mu$ F  $20m\Omega$  solid electrolytic plus 1 x  $22\mu$ F X7R ceramic output capacitors, unless otherwise noted.

#### 4.1 Input Specifications

| Parameter                        | Conditions/Description                                        | Min | Nom | Max | Units      |

|----------------------------------|---------------------------------------------------------------|-----|-----|-----|------------|

| Input voltage (V <sub>IN</sub> ) |                                                               | 8   |     | 14  | VDC        |

| Input Current (at no load)       | V <sub>IN</sub> =14.0V, V <sub>OUT</sub> =3.3V                |     | 50  |     | mADC       |

| Undervoltage Lockout             | Ramping Up<br>Ramping Down                                    | 5   |     | 7.5 | VDC<br>VDC |

| VLDO Input Current               | Current drawn from the external low voltage supply at VLDO=8V |     | 50  |     | mADC       |

#### 4.2 Output Specifications

| Parameter                                                                      | Conditions/Description                                                                                                         | Min               | Nom                              | Max    | Units                            |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------|--------|----------------------------------|

| Output Voltage Range (V <sub>OUT</sub> )                                       |                                                                                                                                | 0.7               |                                  | 5.5    | VDC                              |

| Output Voltage Setpoint<br>Resolution                                          |                                                                                                                                |                   | 2.5mV                            | (1LSB) | 1                                |

| Output Voltage Setpoint Accuracy                                               | 2 <sup>nd</sup> Vo Loop Enabled                                                                                                |                   | ±(0.6%                           | + 5mV) |                                  |

| Output Current (I <sub>OUT</sub> )                                             | $V_{\text{IN MIN}}$ to $V_{\text{IN MAX}}$                                                                                     | -5.5 <sup>2</sup> |                                  | 7      | ADC                              |

| Line Regulation                                                                | V <sub>IN MIN</sub> to V <sub>IN MAX</sub>                                                                                     |                   | ±0.3                             |        | %V <sub>OUT</sub>                |

| Load Regulation                                                                | 0 to I <sub>OUT MAX</sub>                                                                                                      |                   | ±0.2                             |        | %V <sub>OUT</sub>                |

| Dynamic Regulation<br>Peak Deviation<br>Settling Time                          | Slew rate 1A/μs, 50 -75% load step<br>F <sub>sw</sub> =500kHz<br>to 10% of peak deviation<br>See Output Load Transient Section |                   | 50<br>60                         |        | mV<br>μs                         |

| Output Voltage Peak-to-Peak<br>Ripple and Noise<br>Scope BW=20MHz<br>Full Load |                                                                                                                                |                   | 10<br>20<br>40<br>18<br>35<br>50 |        | mV<br>mV<br>mV<br>mV<br>mV<br>mV |

| Temperature Coefficient                                                        | V <sub>IN</sub> =12V, I <sub>OUT</sub> =0.5×I <sub>OUT MAX</sub>                                                               |                   | 20                               |        | ppm/℃                            |

| Switching Frequency                                                            | Default<br>Programmable to                                                                                                     |                   | 500<br>500 / 1,000               |        | kHz                              |

| Duty Cycle Limit                                                               | Default<br>Programmable, 1.56% steps                                                                                           | 3.125             | 90.5                             | 100    | %<br>%                           |

<sup>&</sup>lt;sup>2</sup> At negative (sink) output current (bus terminator mode) the efficiency of the DP8105 degrades resulting in increased internal power dissipation and switching noise. Therefore maximum allowable negative current under specific conditions is lower than the current determined from the de-rating curves shown in paragraph.

#### 4.3 **Protection Specifications**

| Parameter                                   | Conditions/Description                                                          | Min           | Nom                          | Max          | Units                                      |

|---------------------------------------------|---------------------------------------------------------------------------------|---------------|------------------------------|--------------|--------------------------------------------|

|                                             | Output Overcurrent Protection                                                   | n             |                              |              |                                            |

| Туре                                        | Default<br>Programmable                                                         |               | tching, 130m<br>hing/Non-Lat |              |                                            |

| Threshold                                   | 36                                                                              | 132           | 132                          | %юит<br>%юит |                                            |

| Threshold Accuracy                          |                                                                                 | -20           |                              | +20          | %I <sub>OCP.SET</sub>                      |

|                                             | Output Overvoltage Protection                                                   | n             |                              |              |                                            |

| Туре                                        | Default<br>Programmable                                                         |               | tching, 130m<br>hing/Non-Lat |              |                                            |

| Threshold                                   | Default<br>Programmable in 10% steps                                            | 110           | 130                          | 130          | %V <sub>O.SET</sub><br>%V <sub>O.SET</sub> |

| Threshold Accuracy                          | Measured at $V_{O.SET}=2.5V$                                                    | -2            |                              | 2            | %V <sub>OVP.SET</sub>                      |

| Delay                                       | From instant when threshold is exceeded until the turn-off command is generated |               | 6                            |              | μs                                         |

| Turn Off Behavior <sup>3</sup>              | Default                                                                         | Emergency Off |                              |              |                                            |

| Programmable to Critical Off / Emergency Of |                                                                                 |               |                              |              |                                            |

|                                             | Output Undervoltage Protectio                                                   | on            |                              |              |                                            |

| Туре                                        | Default<br>Programmable                                                         |               | tching, 130m<br>hing/Non-Lat |              |                                            |

| Threshold                                   | Default<br>Programmable in 5% steps                                             | 75            | 75                           | 90           | %V <sub>O.SET</sub><br>%V <sub>O.SET</sub> |

| Threshold Accuracy                          | Measured at $V_{O.SET}=2.5V$                                                    | -2            |                              | 2            | %V <sub>UVP.SET</sub>                      |

| Delay                                       | From instant when threshold is exceeded until the turn-off command is generated |               | 6                            |              | μs                                         |

| Turn Off Behavior <sup>3</sup>              | Default                                                                         | S             | Sequenced C                  | Off          |                                            |

| rum on Bonavor                              | Programmable to                                                                 | Sequ          | enced / Criti                | cal Off      |                                            |

|                                             | Overtemperature Protection                                                      |               |                              |              |                                            |

| Туре                                        | Default<br>Programmable                                                         |               | tching, 130m<br>hing/Non-Lat |              |                                            |

| Turn Off Threshold                          | Temperature is increasing                                                       |               | 120                          |              | °C                                         |

| Turn On Threshold                           | Temperature is decreasing after the module was shut down by OTP <sup>4</sup>    |               | 110                          |              | °C                                         |

| Threshold Accuracy                          |                                                                                 | -5            |                              | 5            | °C                                         |

| Delay                                       | From instant when threshold is exceeded until the turn-off command is generated | 6             |                              |              | μs                                         |

| Turn Off Behavior <sup>3</sup>              | Default<br>Programmable to                                                      | Sequ          | Sequenced C<br>enced / Criti |              |                                            |

|                                             | Tracking Protection (when Enab                                                  | led)          |                              |              |                                            |

<sup>3</sup> Sequenced Off: The turn-off follows the turn-off delay and slew-rate settings; Critical Off: At turn-off both low and high switches are immediately disabled; Catastrophic Off: At turn-off the high side switch is disabled and the low side switch is enabled.

<sup>4</sup> OTP clears when Overtemp Warning (Status Register TW bit) turns off.

# DP8105 5A DC-DC Intelligent dPOL Data Sheet 8V to 14V Input • 0.7V to 5.5V Output

| Туре                     | Default<br>Programmable                                                               | Latching                                            | Disabled<br>Latching/Non-Latching, 130ms            |      |                                            |

|--------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------|--------------------------------------------|

| Threshold                | Enabled during output voltage ramping up                                              |                                                     |                                                     | ±250 | mVDC                                       |

| Threshold Accuracy       |                                                                                       | -50                                                 |                                                     | 50   | mVDC                                       |

| Delay                    | From instant when threshold is exceeded until the turn-off command is generated       |                                                     | 6                                                   |      | μs                                         |

|                          | Overtemperature Warning                                                               |                                                     |                                                     |      |                                            |

| Threshold                | Always enabled, reported in Status register (TW bit) <sup>5</sup>                     |                                                     | 110                                                 |      | °C                                         |

| Threshold Accuracy       | From Nominal Set Point                                                                | -5                                                  |                                                     | +5   | °C                                         |

| Hysteresis               |                                                                                       |                                                     | 1.7                                                 |      | °C                                         |

|                          | Power Good Signal (PG pin)                                                            | )                                                   |                                                     | •    |                                            |

| Logic                    | V <sub>OUT</sub> is inside the PG window<br>V <sub>OUT</sub> is outside the PG window |                                                     | High<br>Low                                         |      |                                            |

| Lower Threshold          | Default<br>Programmable in 5% steps                                                   | 90                                                  | 90                                                  | 95   | %V <sub>O.SET</sub><br>%V <sub>O.SET</sub> |

| Upper Threshold          | Default<br>Programmable in 5% steps                                                   | 105                                                 | 110                                                 | 110  | %V <sub>O.SET</sub>                        |

| Threshold Accuracy       | Measured at $V_{O.SET}=2.5V$                                                          | -2                                                  |                                                     | 2    | %V <sub>O.SET</sub>                        |

| PG On Delay <sup>6</sup> | Default                                                                               | 0                                                   |                                                     |      | ms                                         |

|                          | Programmable at                                                                       | 0, 10, 50, 150                                      |                                                     |      |                                            |

| PG Off Delay             | Default                                                                               | PG disabled when $V_{OUT} \leq V_{UV}$<br>threshold |                                                     |      |                                            |

| FG OII Delay             | Programmable same as PG On Delay                                                      |                                                     | PG disabled at turn-off command<br>(Reset function) |      |                                            |

<sup>&</sup>lt;sup>5</sup> Temp Warning error same sign and proportional with OTP error.

<sup>6</sup> From instant when threshold is exceeded until status of PG signal changes high

#### 4.4 Feature Specifications

| Parameter                       | Conditions/Description                     | Min                   | Nom   | Max               | Units             |

|---------------------------------|--------------------------------------------|-----------------------|-------|-------------------|-------------------|

|                                 | Interleave                                 |                       |       |                   |                   |

| Interleave (Phase Shift)        | Default<br>Programmable in 22.5° steps     | 0                     | 0     | 337.5             | Degree<br>degree  |

|                                 | Sequencing <sup>7</sup>                    |                       |       |                   |                   |

| Turn ON Delay                   | Default<br>Programmable in 1ms steps       | 0                     | 0     | 255               | ms<br>ms          |

| Turn OFF Delay                  | Default<br>Programmable in 1ms steps       | 0                     | 0     | 63                | ms<br>ms          |

|                                 | Tracking                                   |                       |       |                   |                   |

| Turn ON Slew Rate               | Default<br>Programmable in 8 steps         | 0.05                  | 0.05  | 2.0 <sup>8</sup>  | V/ms<br>V/ms      |

| Turn OFF Slew Rate              | Default<br>Programmable in 8 steps         | -0.05                 | -0.05 | -2.0 <sup>8</sup> | V/ms<br>V/ms      |

|                                 | Optimal Voltage Positioning                | 9                     |       |                   |                   |

| Load Regulation                 | Default<br>Programmable in 7 steps         | 0                     | 0     | 2.45              | mV/A<br>mV/A      |

|                                 | Feedback Loop Compensati                   | on                    |       |                   |                   |

| Proportional (Kr)               | Programmable                               | 0.01                  |       | 2                 |                   |

| Integral (Ti)                   | Programmable                               | 1                     |       | 100               | μs                |

| Differential (Td)               | Programmable                               | 1                     |       | 100               | μs                |

| Differential Roll-Off (Tv)      | Programmable                               | 1                     |       | 100               | μs                |

|                                 | Monitoring                                 |                       |       |                   |                   |

| Voltage Monitoring Accuracy     | 12 Bit Resolution over 0.55.5V             | -0.5                  |       | 0.5               | %                 |

| Current Monitoring Accuracy     | 20% Iout < Iout < Iout Nom                 | -20                   |       | +20               | %I <sub>ОUT</sub> |

| Temperature Monitoring Accuracy | Junction temperature of dPOL<br>controller | -5                    |       | +5                | °C                |

|                                 | Remote Voltage Sense (+VS and -\           | /S pins) <sup>9</sup> |       |                   |                   |

| Voltage Drop Compensation       | Between +VS and VOUT                       |                       |       | 300               | mV                |

| Voltage Drop Compensation       | Between -VS and PGND                       |                       |       | 100               | mV                |

<sup>7</sup> Timing based on SD clock and subject to tolerances of SD.

<sup>8</sup> Achieving fast slew rates under specific line and load conditions may require feedback loop adjustment. See Rising and Falling Slew Rates.

<sup>9</sup> For remote sense, it is recommended to place a 0.01-0.1µF ceramic capacitor between +VS and –VS pins as close to the dPOL converter as possible.

#### 4.5 Signal Specifications

| Parameter     | Conditions/Description                            | Min           | Nom | Мах           | Units            |

|---------------|---------------------------------------------------|---------------|-----|---------------|------------------|

| VDD           | Internal supply voltage                           | 3.15          | 3.3 | 3.45          | V                |

| Logic Vin Max | Pull Up Logic max safe input                      |               |     | VDD+.5        | V                |

|               | SYNC/DATA Line (SD p                              | oin)          |     |               |                  |

| ViL_sd        | LOW level input voltage                           | -0.5          |     | 0.3 x VDD     | V                |

| ViH_sd        | HIGH level input voltage                          | 0.75 x<br>VDD |     | VDD + 0.5     | V                |

| Vhyst_sd      | Hysteresis of input Schmitt trigger               | 0.25 x<br>VDD |     | 0.45 x<br>VDD | V                |

| VoL           | LOW level sink current @ 0.5V                     | 14            |     | 60            | mA               |

| Tr_sd         | Maximum allowed rise time 10/90%VDD               |               |     | 300           | ns               |

| Cnode_sd      | Added node capacitance                            |               | 5   | 10            | pF               |

| lpu_sd        | Pull-up current source at Vsd=0V                  | 0.3           |     | 1.0           | mA               |

| Freq_sd       | Clock frequency of external SD line               | 475           |     | 525           | kHz              |

| Tsynq         | Sync pulse duration                               | 22            |     | 28            | % of clock cycle |

| то            | Data=0 pulse duration                             | 72            |     | 78            | % of clock cycle |

|               | Inputs: ADDR0ADDR4, I                             | EN, IM        |     |               |                  |

| ViL_x         | LOW level input voltage                           | -0.5          |     | 0.3 x VDD     | V                |

| ViH_x         | HIGH level input voltage                          | 0.7 x VDD     |     | VDD+0.5       | V                |

| Vhyst_x       | Hysteresis of input Schmitt trigger               | 0.1 x VDD     |     | 0.3 x VDD     | V                |

| RdnL_ADDR     | External pull down resistance<br>ADDRX forced low |               |     | 10            | kOhm             |

|               | Power Good and OK Inputs/                         | Outputs       |     |               |                  |

| lup_PG        | Pull-up current source input forced low PG        | 25            |     | 110           | μA               |

| lup_OK        | Pull-up current source input forced low OK        | 175           |     | 725           | μA               |

| ViL_x         | LOW level input voltage                           | -0.5          |     | 0.3 x VDD     | V                |

| ViH_x         | HIGH level input voltage                          | 0.7 x VDD     |     | VDD+0.5       | V                |

| Vhyst_x       | Hysteresis of input Schmitt trigger               | 0.1 x VDD     |     | 0.3 x VDD     | V                |

| loL           | LOW level sink current at 0.5V                    | 4             |     | 20            | mA               |

|               | Current Share Bus (CS                             | pin)          |     |               |                  |

| lup_CS        | Pull-up current source at VCS = 0V                | 0.84          |     | 3.1           | mA               |

| ViL_CS        | LOW level input voltage                           | -0.5          |     | 0.3 x VDD     | V                |

| ViH_CS        | HIGH level input voltage                          | 0.75 x<br>VDD |     | VDD+0.5       | V                |

| Vhyst_CS      | Hysteresis of input Schmitt trigger               | 0.25 x<br>VDD |     | 0.45 x<br>VDD | V                |

| loL           | LOW level sink current at 0.5V                    | 14            |     | 60            | mA               |

| Tr_CS         | Maximum allowed rise time 10/90% VDD              |               |     | 100           | ns               |

www.power-one.com

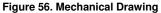

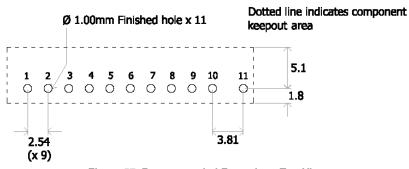

#### 5. Pin Assignments and Descriptions

| Pin<br>Name | Pin<br>Number | Pin<br>Type | Buffer<br>Type | Pin Description        | Notes                                                              |

|-------------|---------------|-------------|----------------|------------------------|--------------------------------------------------------------------|

| OK          | 8             | I/O         | PU             | Fault/Status Condition | Connect to OK pin of other dPOLs in the same<br>Group and the DPM. |

| SD          | 9             | I/O         | PU             | Sync/Data Line         | Connect to SD pin of DPM.                                          |

| PG          | 6             | I/O         | PU             | Power Good             |                                                                    |

| ADDR4       | 10            | I           | PU             | dPOL Address Bit 4     | Tie to GND for 0 or leave floating for 1                           |

| ADDR3       | 5             | I           | PU             | dPOL Address Bit 3     | Tie to GND for 0 or leave floating for 1                           |

| ADDR2       | 4             | I           | PU             | dPOL Address Bit 2     | Tie to GND for 0 or leave floating for 1                           |

| ADDR1       | 3             | I           | PU             | dPOL Address Bit 1     | Tie to GND for 0 or leave floating for 1                           |

| ADDR0       | 2             | I           | PU             | dPOL Address Bit 0     | Tie to GND for 0 or leave floating for 1                           |

| VOUT        | 1             | Р           |                | Output Voltage         |                                                                    |

| GND         | 7             | Р           |                | Power Ground           |                                                                    |

| VIN         | 11            | Р           |                | Input Voltage          |                                                                    |

Legend: I=input, O=output, I/O=input/output, P=power, A=analog, PU=internal pull-up

#### 6. Typical Performance Characteristics

#### 6.1 Thermal De-rating Curves

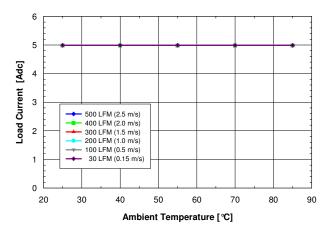

Figure 1. Available output current vs. ambient air temperature and airflow rates for converter DP8105 mounted horizontally with air flowing from input to output, MOSFET temperature ≤ 120 °C, Vin = 12 V, Vout = 5 V, and Fsw= 500KHz

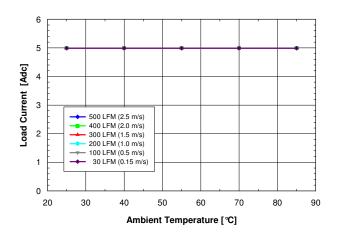

Figure 2. Available output current vs. ambient air temperature and airflow rates for converter DP8105 mounted horizontally with air flowing from input to output, MOSFET temperature ≤ 120 °C, Vin = 12 V, Vout = 5 V, and Fsw= 1MHzw

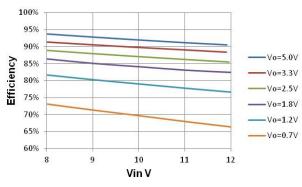

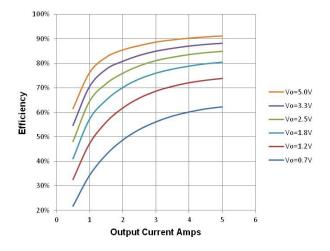

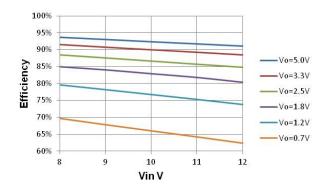

#### 6.2 Efficiency Curves

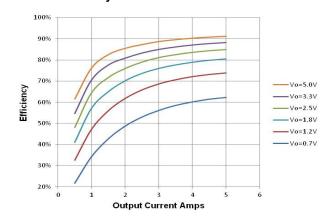

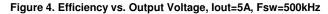

Figure 3. Efficiency vs. Load, Vin=12V, Fsw=500KHz

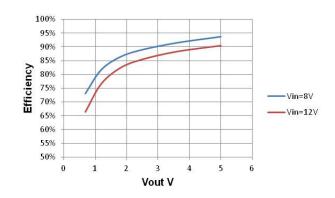

Figure 5. Efficiency vs Input Voltage at Iout=5A, Fsw=500KHz

Figure 6. Efficiency vs Load, Vin=12V, Fsw=1MHz

Figure 7. Efficiency vs Output Voltage, Iout=5A, Fsw=1MHz

Figure 8. Efficiency vs Input Voltage at Iout=5A, Fsw=1MHz

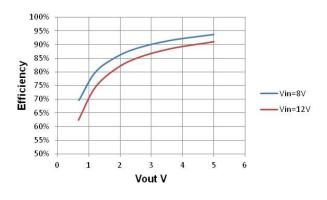

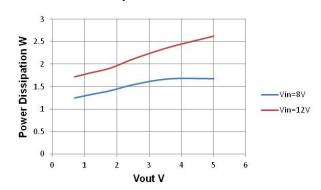

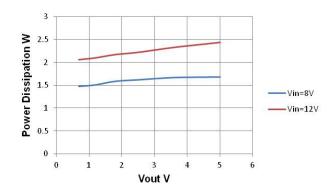

#### 6.4 Power Dissipation

DP8105 5A DC-DC Intelligent dPOL Data Sheet

8V to 14V Input • 0.7V to 5.5V Output

Figure 9. Power Dissipation vs Vout, lout=5A, Fsw=500KHz

Figure 10. Power Dissipation vs Vout, lout=5A, Fsw=1MHz

#### 7. Programmable Features

Performance parameters of DP8105 dPOL converters can be programmed via the industry standard I<sup>2</sup>C communication bus. Each parameter has a default value stored in the volatile memory registers detailed in Table 1. The setup registers 00h through 14h are programmed at the system power-up. When the user programs new performance parameters, they are stored in the DPM, which overwrites the values in the registers With the new data. Upon removal of the input voltage, the default values are restored.

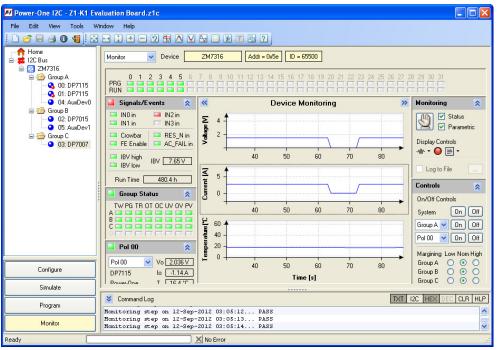

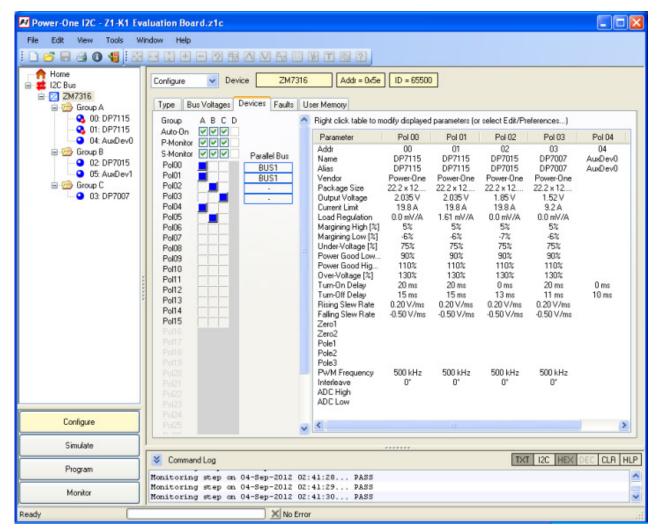

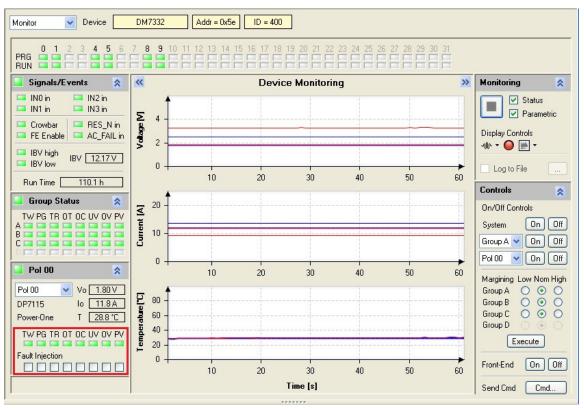

DP8105 converters can be programmed using the Graphical User Interface or directly via the I<sup>2</sup>C bus by using high and low level commands as described in the "DPM Programming Manual".

| Table 1. DP8105 Memory Registe | ers |

|--------------------------------|-----|

|--------------------------------|-----|

| CONFIGURATION REGISTERS |                                            |         |  |  |  |  |

|-------------------------|--------------------------------------------|---------|--|--|--|--|

| Name                    | Register                                   | Address |  |  |  |  |

| PC1                     | Protection Configuration 1                 | 0x00    |  |  |  |  |

| PC2                     | Protection Configuration 2                 | 0x01    |  |  |  |  |

| PC3                     | Protection Configuration 3                 | 0x02    |  |  |  |  |

| TC                      | Tracking Configuration                     | 0x03    |  |  |  |  |

| INT                     | Interleave and Frequency Configuration     | 0x04    |  |  |  |  |

| DON                     | Turn-On Delay                              | 0x05    |  |  |  |  |

| DOF                     | Turn-Off Delay                             | 0x06    |  |  |  |  |

| VLC                     | Voltage Loop Configuration                 | 0x07    |  |  |  |  |

| CLS                     | Current Limit Set-point                    | 0x08    |  |  |  |  |

| DCL                     | Duty Cycle Limit                           | 0x09    |  |  |  |  |

| PC4                     | Protection Configuration 4                 | 0x0A    |  |  |  |  |

| V1H                     | Output Voltage Setpoint 1 (Low Byte)       | 0x0B    |  |  |  |  |

| V1L                     | Output Voltage Setpoint 1 (High Byte)      | 0x0C    |  |  |  |  |

| V2H                     | Output Voltage Setpoint 2 (Low Byte)       | 0x0D    |  |  |  |  |

| V2L                     | Output Voltage Setpoint 2 (High Byte)      | 0x0E    |  |  |  |  |

| V3H                     | Output Voltage Setpoint 3 (Low Byte)       | 0x0F    |  |  |  |  |

| V3L                     | Output Voltage Setpoint 3 (High Byte)      | 0x10    |  |  |  |  |

| CP                      | Controller Proportional Coefficient        | 0x11    |  |  |  |  |

| CI                      | Controller Integral Coefficient            | 0x12    |  |  |  |  |

| CD                      | Controller Derivative Coefficient          | 0x13    |  |  |  |  |

| B1                      | Controller Derivative Roll-Off Coefficient | 0x14    |  |  |  |  |

|                         | REGISTERS                                  |         |  |  |  |  |

| Name                    | Register                                   | Address |  |  |  |  |

| RUN                     | Run enable / status                        | 0x15    |  |  |  |  |

| ST                      | Status                                     | 0x16    |  |  |  |  |

| MONITO                  | MONITORING REGISTERS                       |         |  |  |  |  |

| Name                    | Register                                   | Address |  |  |  |  |

| VOH                     | Output Voltage High Byte (Monitoring)      | 0x17    |  |  |  |  |

| VOL                     | Output Voltage Low Byte (Monitoring)       | 0x27    |  |  |  |  |

| 10                      | Output Current (Monitoring)                | 0x18    |  |  |  |  |

| TMP                     | Temperature (Monitoring)                   | 0x19    |  |  |  |  |

DP8105 parameters can be reprogrammed at any time during the system operation and service except for the digital filter coefficients, the switching frequency and the duty cycle limit, that can only be changed when the dPOL output is turned off.

#### 7.1 Output Voltage

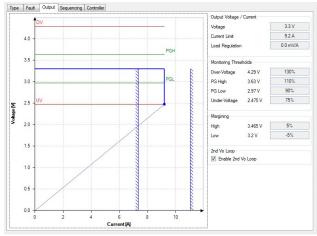

The output voltage can be programmed in the GUI Output Configuration window shown in Figure 11 or directly via the  $I^2C$  bus by writing into the VOS register shown in Figure 12.

Figure 11. Output Configuration Window

Note that the GUI shows the effect of setting PG, OV and UV limits as both values and graphical limit bars. Vertical hashed lines are error bars for the Overcurrent (OC) limit.

#### 1.1.1 Output Voltage Set-point

The output voltage programming range is from 0.7 V to 5.5 V. The resolution is constant across the range and is 2.5 mV. A Total of 3 registers are provided: one should be used for the normal setpoint voltage; the other two can be used to define a low/high margining voltage setpoint. Note that each register is 16bit wide and that the high byte needs always to be written / read first. The writing of the low byte triggers the refresh of the whole 16bit register (the high byte is written to a shadow register).

Unlike other configuration registers, the dPOL controller's VOS registers are dynamic. Changes to VOS values can be made while the output is enabled over the I2C bus through register bypass commands and the dPOL will change its output immediately.

|     | Output Voltage Set-Point<br>a: 0x0B 0x10                                  |      |      |         |

|-----|---------------------------------------------------------------------------|------|------|---------|

|     | Coefficient                                                               | Addr | Bits | Default |

| V1H | First Vo Setpoint High Byte                                               | 0x0B | 8    |         |

| V1L | First Vo Setpoint Low Byte                                                | 0x0C | 8    |         |

| V2H | Second Vo Setpoint High Byte                                              | 0x0D | 8    |         |

| V2L | Second Vo Setpoint Low Byte                                               | 0x0E | 8    |         |

| V3H | Third Vo Setpoint High Byte                                               | 0x0F | 8    |         |

| V3L | Third Vo Setpoint Low Byte                                                | 0x10 | 8    |         |

|     | <b>g:</b><br>data word, left aligned<br>= 2.5mV                           |      |      |         |

|     | isters are readable and writeable<br>s write and read the high byte first |      |      |         |

Figure 12. Output Voltage Set-point Register VOS

#### 7.1.1 Output Voltage Margining

If the output voltage needs to be varied by a certain percentage, the margining function can be utilized. The margining can be programmed in the dPOL Configuration window or directly via the l<sup>2</sup>C bus using high level commands as described in the "DM7300 Digital Power Manager Programming Manual".

#### 7.1.2 Output Load Regulation Control

If the output voltage needs to be varied by a certain percentage, the margining function can be utilized. The margining can be programmed in the dPOL Configuration window or directly via the I<sup>2</sup>C bus using high level commands as described in the "DM7300 Digital Power Manager Programming Manual".

In order to properly margin dPOLs that are connected in parallel, the dPOLs must be members of one of the Parallel Buses. Refer to the GUI System Configuration Figure 11 or directly via the  $l^2C$  bus. In the DP8105 Load Regulation can be set to one of eight values: 0, 1.48, 2.95, 4.43, 5.9, 7.38 8.85, or 10.33 mv/A.

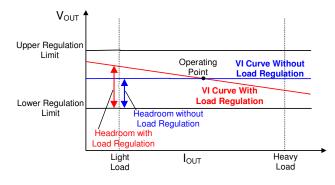

Figure 13. Optimal Voltage Positioning Concept

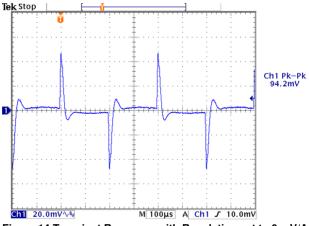

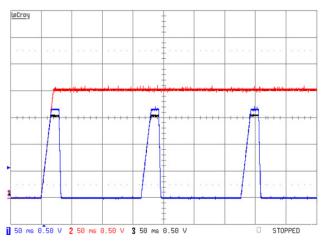

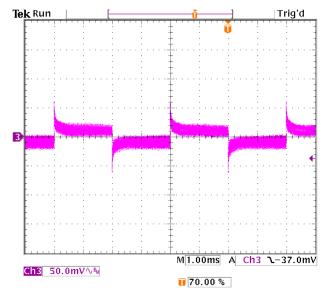

Figure 14 shows a DP8105 dPOL with 0 mv/A (load current) regulation. Alternating high and low output load currents causes large transients in Vout to appear with each change.

Figure 14 Transient Response with Regulation set to 0 mV/A.

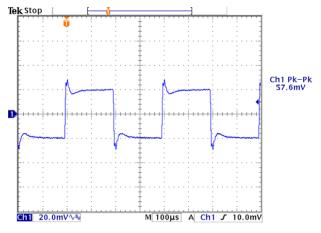

As the Load Regulation parameter is increased, step offsets in output voltage begin to appear, as shown in Figure 15.

Figure 15 Transient response with non-zero Regulation.

The Load Regulation parameter is an important part of Current Sharing. It is used to set one dPOL as a "master", by assigning a lower mV/A load regulation than all other dPOLs which share the load as "slaves". The dPOL with the lowest Regulation parameter sets the effective overall regulation. (See Current Sharing elsewhere in this document.)

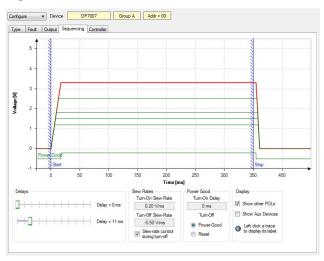

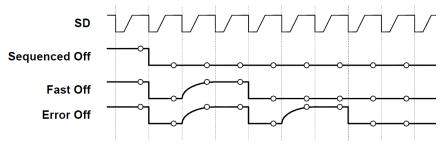

#### 7.2 Sequencing and Tracking

Turn-on delay, turn-off delay, and rising and falling output voltage slew rates can be programmed in the dPOL Configure Sequencing window shown in Figure 16 or directly via the I2C bus by writing into the DON, DOF, and TC registers, respectively. The registers are shown in Figure 17, Figure 19, and Figure 20.

Figure 16. dPOL Configure Sequencing Window

#### 7.2.1 Turn-On Delay

Turn-on delay is defined as an interval from the application of the Turn-On command until the output voltage starts ramping up.

| R/W-0                                                                                                                                                                              | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| DON7                                                                                                                                                                               | DON6  | DON5  | DON4  | DON3  | DON2  | DON1  | DON0  |  |  |

| Bit 7 Bit 0                                                                                                                                                                        |       |       |       |       |       |       |       |  |  |

| Bit 7:0 DON[7:0]: Turn-on delay time<br>00h: corresponds to 0ms delay after turn-on command has occurred<br><br>FFh: corresponds to 255ms delay after turn-on command has occurred |       |       |       |       |       |       |       |  |  |

| Figure 17. Turn-On Delay Register DON                                                                                                                                              |       |       |       |       |       |       |       |  |  |

#### 7.2.2 Turn-Off Delay

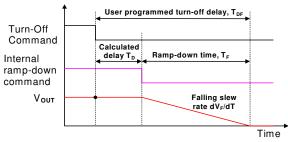

Turn-off delay is defined as an interval from the application of the Turn-Off command until the output voltage reaches zero (if the falling slew rate is programmed) or until both high side and low side switches are turned off (if the slew rate is not programmed). Therefore, for the slew rate controlled turn-off the ramp-down time is included in the turn-off delay as shown in Figure 18.

## Figure 18. Relationship between Turn-Off Delay and Falling Slew Rate

As it can be seen from the figure, the internally calculated delay  $T_{\rm D}$  is determined by the equation below.

$$T_D = T_{DF} - \frac{V_{OUT}}{dV_F}$$

For proper operation  $T_D$  shall be greater than zero. The appropriate value of the turn-off delay needs to be programmed to satisfy the condition.

If the falling slew rate control is not utilized, the turnoff delay only determines an interval from the application of the Turn-Off command until both high side and low side switches are turned off. In this case, the output voltage ramp-down process is determined by load parameters.

| DOF: Turn-Off Delay Configuration<br>Address: 0x06 |                                        |                   |              |       |       |       |       |  |  |  |

|----------------------------------------------------|----------------------------------------|-------------------|--------------|-------|-------|-------|-------|--|--|--|

| U                                                  | U                                      | R/W-0             | R/W-0        | R/W-1 | R/W-0 | R/W-1 | R/W-1 |  |  |  |

|                                                    |                                        | DOF5              | DOF4         | DOF3  | DOF2  | DOF1  | DOF0  |  |  |  |

| Bit 7                                              |                                        | Bit 0             |              |       |       |       |       |  |  |  |

| Bit 7:6<br>Bit 5:0                                 | <b>DOF[5:0</b><br>0x00 = 0<br>0x01 = 1 | lms<br>11ms (defa | f delay in r | ns    |       |       |       |  |  |  |

#### Figure 19. Turn-Off Delay Register DOF

#### 7.3 Turn-On Characteristics

Once delays are accounted for, turn-on and turn-off characteristics are simply a function of slew rates, which are selectable.

#### 7.3.1 Rising and Falling Slew Rates

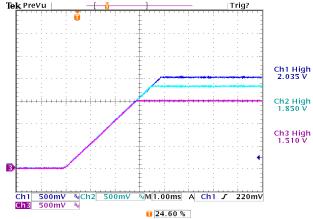

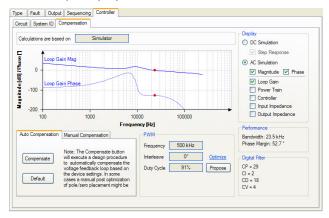

Output voltage ramp up (and down) control is accomplished by programming the rising and falling slew rates of the output voltage, supported in the GUI as shown in Figure 16, which is implemented by the DPM through writing data to the TC register, Figure 20.

To achieve programmed slew rates, the output voltage is being changed in 10mV steps where duration of each step determines the slew rate. For example, ramping up a 1.0V output with a slew rate of 0.5V/ms will require 100 steps duration of 20µs each.

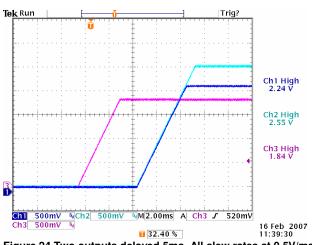

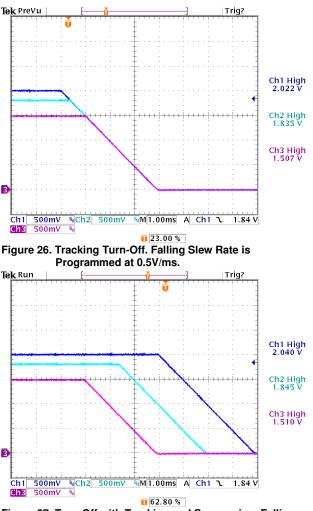

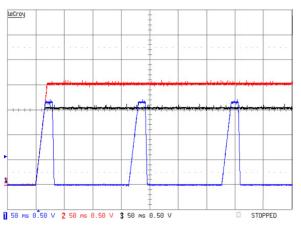

Duration of each voltage step is calculated by dividing the master clock frequency generated by the DPM. Since all dPOLs in the system are synchronized to the master clock, the matching of voltage slew rates of different outputs is very accurate as it can be seen in Figure 21 and Figure 26.

During the turn on process, a dPOL not only delivers current required by the load ( $I_{LOAD}$ ), but also charges the load capacitance. The charging current can be determined from the equation below:

$$I_{CHG} = C_{LOAD} \times \frac{dV_{R}}{dt}$$

Where,  $C_{LOAD}$  is load capacitance,  $dV_R/dt$  is rising voltage slew rate, and  $I_{CHG}$  is charging current.

| TC: Tr<br>Address: |                                                                     | Configu                                                                             | ration                 |             |             |       |       |

|--------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------|-------------|-------------|-------|-------|

| U                  | R/W-0                                                               | R/W-0                                                                               | R/W-1                  | R/W-1       | R/W-1       | R/W-0 | R/W-0 |

|                    | R2                                                                  | R1                                                                                  | R0                     | SC          | F2          | F1    | F0    |

| Bit 7              |                                                                     |                                                                                     |                        |             |             |       | Bit 0 |

| Bit 7<br>Bit 6:4   | <b>R[2:0]</b> : \<br>0 = 0.05                                       | //ms (defai<br>//ms<br>V/ms<br>//ms<br>//ms                                         | ew rate<br>ault when i | in bus term | ninator moo | de)   |       |

| Bit 3              | 0 = disat                                                           | n-off slew r<br>bled<br>bled (defau                                                 |                        | l           |             |       |       |

| Bit 2:0            | <b>F[2:0]</b> : V<br>0 = -0.05<br>1 = -0.1<br>2 = -0.2<br>3 = -0.25 | /o faÌling sl<br>5 V/ms<br>V/ms<br>V/ms (de<br>5 V/ms (defa<br>V/ms<br>V/ms<br>V/ms | ew rate<br>fault when  | in bus terr | ninator mc  | ode)  |       |

#### Figure 20. Tracking Configuration Register TC

When selecting the rising slew rate, a user needs to ensure that

$$I_{LOAD} + I_{CHG} < I_{OCP}$$

Where  $I_{OCP}$  is the overcurrent protection threshold of the dPOL. If the condition is not met, then the overcurrent protection will be triggered during the turn-on process. To avoid this,  $dV_R/dt$  and the overcurrent protection threshold should be programmed to meet the condition above.

#### 7.3.2 Delay and Slew Rate Combination

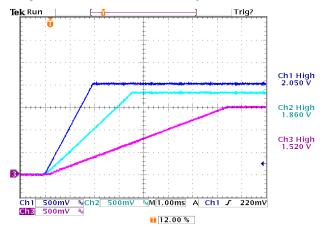

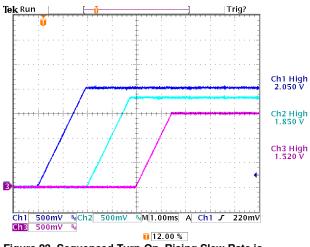

The effect of setting slew rates and turn on/off delays is illustrated in the following sets of figures.

Figure 22. Turn-On with Different Rising Slew Rates. Rising Slew Rates are V1-1V/ms, V2-0.5V/ms, V3-0.2V/ms.

### Figure 24 Two outputs delayed 5ms. All slew rates at 0.5V/ms.

#### 7.3.2.1 Pre-Bias

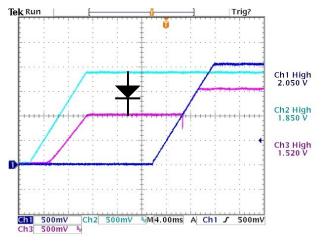

In some applications, power may "leak" from a powered circuit to an unpowered bus, typically through ESD protection diodes. The dPWER<sup>®</sup> controller in the DP8105 holds off turn on its output until the desired ramp up point crosses the pre-bias point, as seen in Figure 25.

## Figure 25. Turn On into Prebiased Load. V3 is Prebiased by V2 via a Diode.

This figure was captured with an actual system where a diode was added to pre-bias a 1.5V bus from a 1.85V bus in order to simulate the effect of current leakage through protection circuits of unpowered logic connected to powered logic outputs (a common source of pre-bias in power systems).

www.power-one.com

#### 1.1 Turn-Off Characteristics

Turn of captures show that combining turn off delays and ramp rates. Note that while turnoff delays have a lower upper time limit as compared to turn on delays, all ramp down rates are available independently to turn on and off.

Figure 27. Turn-Off with Tracking and Sequencing. Falling Slew Rate is Programmed at 0.5V/ms.

#### 7.4 Faults Errors and Warnings

All dPOL series converters have a comprehensive set of programmable fault and error protection functions that can be classified into three groups based on their effect on system operation: warnings, faults, and errors. These are *warnings*, *errors* and *faults*. Warnings include Thermal (Overtemperature limit near) and Power Good (a warning in a negative sense.) Faults in DP8000 dPOLs include overcurrent protection, overvoltage, overtemperature and tracking failure detection. Errors include only undervoltage. Control of responses to Faults and Errors are distributed between different dPOL registers and are configurable in the GUI.

Thresholds of overcurrent, over- and undervoltage detection, and Power Good limits can be programmed in the GUI Output Configuration window (Figure 11) or directly via the  $l^2C$  bus by writing into the PC2 registers shown in Figure 28.

| PC2:<br>Address                                                                                                      |                                 | on Cont                                                                                                        | iguratio    | n Regis    | ter 2 1)     |          |         |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|-------------|------------|--------------|----------|---------|--|--|

| U                                                                                                                    | U                               | R/W-0                                                                                                          | R/W-0       | R/W-1      | R/W-0        | R/W-0    | R/W-0   |  |  |

|                                                                                                                      |                                 | PGHL                                                                                                           | PGLL        | OVPL1      | OVPL0        | UVPL1    | UVPL0   |  |  |

| Bit 7                                                                                                                |                                 |                                                                                                                |             |            |              |          | Bit 0   |  |  |

| Bit7:6 Unimplemented: read as '0'<br>Bit 5 PGHL: Power Good High Level<br>1 = 105% of Vo<br>0 = 110% of Vo (default) |                                 |                                                                                                                |             |            |              |          |         |  |  |

| Bit 4                                                                                                                | <b>PGLL</b> : F<br>1 = 95%      | PGLL: Power Good Low Level           1 = 95% of Vo           0 = 90% of Vo (default)                           |             |            |              |          |         |  |  |

| Bit 3:2                                                                                                              | OVPL: 0<br>00 = 110<br>01 = 120 | <b>OVPL</b> : Over Voltage Protection Level<br>00 = 110% of Vo<br>01 = 120% of Vo<br>10 = 130% of Vo (default) |             |            |              |          |         |  |  |

| Bit 1:0                                                                                                              | UVPL: U                         | Jnder Volta<br>% of Vo (de<br>% of Vo<br>% of Vo                                                               |             | tion Level |              |          |         |  |  |

| <sup>1)</sup> This re                                                                                                | egister can                     | only be w                                                                                                      | ritten wher | n PWM is n | ot active (I | RUN[RUN] | is '0') |  |  |

Figure 28. Protection Configuration Register PC2

Note that the overvoltage and undervoltage protection thresholds and Power Good limits are defined as percentages of the output voltage. Therefore, the absolute levels of the thresholds change when the output voltage setpoint is changed either by output voltage adjustment or by margining.

Overcurrent limits are set either in the GUI dPOL Output configuration dialog or in the dPOL's CLS register as shown Figure 29

Note that the CLS register includes bits which control the Regulation option settings. When writing into this register be careful to not change Regulation by accident.

| CLS: (<br>Address |                                                                                                                                                                                                                                                       | Limit Se                 | etting |             |             |             |       |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|-------------|-------------|-------------|-------|--|--|--|

| R/W-0             | R/W-0                                                                                                                                                                                                                                                 | R/W-0                    | R/W-1  | R/W-1       | R/W-0       | R/W-1       | R/W-1 |  |  |  |

| LR2               | LR1                                                                                                                                                                                                                                                   | LR0                      | TCE    | CL3         | CL2         | CL1         | CL0   |  |  |  |

| Bit 7             | . 5/2 41                                                                                                                                                                                                                                              |                          |        |             |             |             | Bit 0 |  |  |  |

| Bit 7:5           | Bit 7:5       LR[2:0]: Load Regulation setting $0 = 0 \ V/A/\Omega$ (default) $1 = 0.39 \ V/A/\Omega$ $2 = 0.78 \ V/A/\Omega$ $3 = 1.18 \ V/A/\Omega$ $4 = 1.57 \ V/A/\Omega$ $5 = 1.96 \ V/A/\Omega$ $6 = 2.35 \ V/A/\Omega$ $7 = 2.75 \ V/A/\Omega$ |                          |        |             |             |             |       |  |  |  |

| Bit 4             | 0 = disat                                                                                                                                                                                                                                             | bled                     |        | ation for C | urrent Limi | itation Ena | ble   |  |  |  |

| Bit 3:0           | 1 = enabled (default)<br><b>CLS[3:0]</b> : Current Limit set-point when Vo Stationary or Falling<br>0x0 = 37%<br>0x1 = 47%<br>                                                                                                                        |                          |        |             |             |             |       |  |  |  |

|                   |                                                                                                                                                                                                                                                       | 10% (defau<br>igher than |        | anslated to | 0xB (140    | %)          |       |  |  |  |

Figure 29. Current Limit Setpoint Register CLS

#### 7.4.1 Warnings

This group includes Overtemperature Warning and Power Good Signal. Warnings do not turn off dPOLs but rather generate signals that can be transmitted to a host controller via the I<sup>2</sup>C bus.

#### 7.4.1.1 Overtemperature Warning

The Overtemperature Warning is generated when temperature of the controller exceeds 120 ℃. The Overtemperature Warning changes the TW bit of the status register ST. When the temperature falls below 117 ℃, the PT bit is cleared and the Overtemperature Warning is removed.

#### 7.4.1.2 Power Good

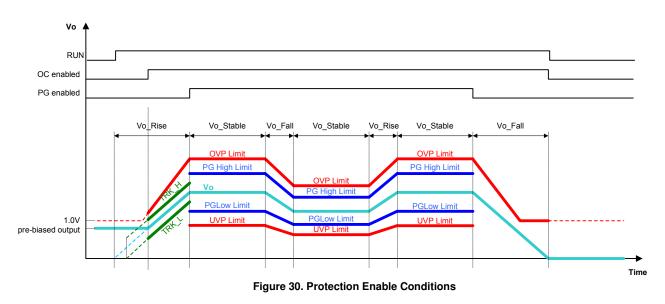

Power Good (PG) is an open collector output that is pulled low, if the output voltage is outside of the Power Good window. The window is formed by the Power Good High threshold that is programmable at 105 or 110% of the output voltage and the Power Good Low threshold that can be programmed at 90 or 95% of the output voltage.

Power Good protection is only enabled after the output voltage reaches its steady state level. A programmable delay can be set between 0 and 150ms to delay the release of the PG pin after the voltage has reached the steady state level (see Figure 16). This allows using the PG pin to reset load

circuits properly. The Power Good protection remains active during margining voltage transitions. The threshold will vary proportionally to the voltage change (see Figure 30).

The Power Good Warning pulls the PG pin low and changes the PG bit of the status register ST to 0. When the output voltage returns within the Power Good window, the PG pin is released high, the PG bit is cleared and the Power Good Warning is removed. The Power Good pin can also be pulled low by an external circuit to initiate the Power Good Warning.

At turn-off the PG pin can be programmed to either be pulled low immediately following the turn-off command, or then when the voltage actually starts to ramp down (Reset vs. Power Good functionality in Figure 16).

Note: To retrieve status information, Status Monitoring in the GUI DPM Configure Devices window should be enabled (refer to Digital Power Manager Data Sheet). The DPM will retrieve the status information from each dPOL on a continuous basis.

#### 7.4.2 Faults

This group includes overcurrent, overtemperature, undervoltage, and tracking protections. Triggering any protection in this group will turn off the dPOL.

#### 7.4.2.1 Overcurrent Protection

Overcurrent protection is active whenever the output voltage of the dPOL exceeds the prebias voltage (if any). When the output current reaches the OC threshold, the POL control chip asserts an OC fault. The dPOL sets the OC bit in the register ST to 0. Both high side and low side switches of the dPOL are turned off instantly (fast turn-off).

Current sensing is across the dPOLs choke. To compensate for copper winding  $T_{C}$ , compensation is added to keep the OC threshold approximately constant at temperatures above room temperature. Note that the temperature compensation can be disabled in the dPOL Configure Output window or directly via the I<sup>2</sup>C by writing into the CLS register. However, it is recommended to keep the temperature compensation enabled.

#### 7.4.2.2 Undervoltage Protection

The undervoltage protection is only active during steady state operation of the dPOL to prevent nuisance tripping. If the output voltage decreases below the UV threshold and there is no OC fault, the UV fault signal is generated, the dPOL turns off, and the UV bit in the register ST is changed to 0. The output voltage is ramped down according to sequencing and tracking settings (regular turn-off).

#### 7.4.2.3 Overtemperature Protection

Overtemperature protection is active whenever the dPOL is powered up. If temperature of the controller exceeds 130 °C, the OT fault is generated, dPOL turns off, and the OT bit in the register ST is changed to 0. The output voltage is ramped down according to sequencing and tracking settings (regular turn-off).

If non-latching OTP is programmed, the dPOL will restart as soon as the temperature of the controller decreases below the Overtemperature Warning threshold of  $120^{\circ}$ C.

#### 7.4.2.4 Tracking Protection

Ramp up and down operations are under control by the dPOL. Tracking protection, however, is active only when the output voltage is ramping up. The purpose of the protection is to ensure that the voltage differential between multiple rails being tracked does not exceed 250mV. This protection eliminates the need for external clamping diodes between different voltage rails which are frequently recommended by ASIC manufacturers.

When the tracking protection is enabled, the dPOL continuously compares actual value of the output voltage to its programmed value as defined by the output voltage and its rising slew rate. If absolute value of the difference exceeds 250mV, the tracking fault signal is generated, the dPOL turns off, and the TR bit in the register ST is changed to 0. Both high side and low side switches of the dPOL are turned off instantly (fast turn-off).

The tracking protection can be disabled, if it contradicts requirements of a particular system (for example turning into high capacitive load where rising slew rate is not important). It can be disabled in the dPOL Configure Fault window or directly via the  $l^2C$  bus by writing into the PC1 register.

#### 1.1.1 Faults and Margining

As noted earlier, UV and OV protection settings are a percentage of Vout. As Vout ramps between nominal, low or high margin values, UVP and OVP limits adjust accordingly. This is illustrated in Figure 30. The middle plot of Vo (Vout) level is the result of a Low Margining command. Note that Tracking is not re-enabled during changes to Vout from margining commands. It shuts off when PG is asserted.

#### 7.4.3 Errors

This protection group includes only overvoltage protection.

#### 7.4.3.1 Overvoltage Protection

The overvoltage protection is active whenever the output voltage of the dPOL exceeds the pre-bias voltage (if any). If the output voltage exceeds the overvoltage protection threshold, the overvoltage error signal is generated, the dPOL turns off, and the OV bit in the register ST is changed to 0. The high side switch is turned off instantly, and simultaneously the low side switch is turned on to ensure reliable protection of sensitive loads. The low side switch provides low impedance path to guickly dissipate energy stored in the output filter and achieve effective voltage limitation. The OV threshold can be programmed from 110% to 130% of the output voltage setpoint, but not lower than 0.5V. Also the OV threshold will always be at least 0.25V above the setpoint.

#### 7.4.4 Fault and Error Latching

The user has the option of setting up any protection option as either latching/non-latching and propagating or non-propagating.

Propagation and Latching for each dPOL is set in the GUI (Figure 31 below) or directly via the  $I^2C$  by writing into the PC1 register shown in

| R/W-0             | R/W-1                                          | R/W-0            | R/W-0       | R/W-0       | R/W-0      | R/W-1 | R/W-1 |  |  |  |  |

|-------------------|------------------------------------------------|------------------|-------------|-------------|------------|-------|-------|--|--|--|--|

| TRE               | PVE                                            | TRC              | OTC         | 000         | UVC        | OVC   | PVC   |  |  |  |  |

| Bit 7             |                                                |                  |             |             |            |       | Bit 0 |  |  |  |  |

|                   |                                                |                  |             |             |            |       |       |  |  |  |  |

| Bit 7             | TRE: Tracking fault enable                     |                  |             |             |            |       |       |  |  |  |  |

|                   | 1 = enabled                                    |                  |             |             |            |       |       |  |  |  |  |

| D'1 0             | 0 = disabled                                   |                  |             |             |            |       |       |  |  |  |  |

| Bit 6             | PVE: Phase voltage error enable<br>1 = enabled |                  |             |             |            |       |       |  |  |  |  |

|                   |                                                | 0 = disabled     |             |             |            |       |       |  |  |  |  |

|                   |                                                |                  |             |             |            |       |       |  |  |  |  |

| Bit 5             | TRC: Tracking Fault Protection Configuration   |                  |             |             |            |       |       |  |  |  |  |

|                   | 1 = latching<br>0 = non-latching               |                  |             |             |            |       |       |  |  |  |  |

| Bit 4             |                                                | •                | roturo Drot | ection Cor  | figuration |       |       |  |  |  |  |

| DIL 4             | 1 = latch                                      |                  | Ialule FIU  |             | Ingulation |       |       |  |  |  |  |

|                   | 0 = non-                                       |                  |             |             |            |       |       |  |  |  |  |

| Bit 3             |                                                | 0                | t Protectio | n Configura | ation      |       |       |  |  |  |  |

| Dito              | 1 = latch                                      |                  |             | ii ooniigun |            |       |       |  |  |  |  |

|                   |                                                | 0 = non-latching |             |             |            |       |       |  |  |  |  |

| Bit 2             |                                                |                  | e Protecti  | on Configu  | ration     |       |       |  |  |  |  |

|                   | 1 = latch                                      |                  | ,           |             |            |       |       |  |  |  |  |

|                   | 0 = non- latching                              |                  |             |             |            |       |       |  |  |  |  |

| Bit 1             |                                                |                  | Protectio   | n Configura | ation      |       |       |  |  |  |  |

|                   | 1 = latching                                   |                  |             |             |            |       |       |  |  |  |  |

|                   | 0 = non-                                       | latching         |             |             |            |       |       |  |  |  |  |

| Bit 0             | PVC: Ph                                        | ase Voltag       | ge Protecti | on Configu  | ration     |       |       |  |  |  |  |

|                   | 1 = latch                                      |                  |             | -           |            |       |       |  |  |  |  |

| 0 = non- latching |                                                |                  |             |             |            |       |       |  |  |  |  |

Type Fault Output Sequencing Controller Enable Latching Propagate Turn-Off Trigger Critical Tracking Differential 1 Sequenced Over-Temperature 1 Critical Over-Current Under-Voltage 1 Sequenced V 1 Over-Voltage Emergency

Figure 31. GUI dPOL Fault Latching and Propagation Option Window

If the non-latching protection is selected, a dPOL will attempt to restart every 130ms until the condition that triggered the protection is removed. When restarting, the output voltages follow tracking and sequencing settings.

If the latching type is selected, a dPOL will turn off and stay off. The dPOL can be turned on after 130ms, if the condition that caused the fault is removed and the respective bit in the ST register was cleared, or the Turn On command was recycled, or the input voltage was recycled.

| ST: Status register<br>Address: 0x16                                                                                           |                                                                                                                                                                                                                            |         |         |         |         |         |         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--|--|

| R-1                                                                                                                            | R-0                                                                                                                                                                                                                        | R/W-11) | R/W-11) | R/W-11) | R/W-11) | R/W-11) | R/W-11) |  |  |

| TW                                                                                                                             | PG                                                                                                                                                                                                                         | TR      | OT      | 00      | UV      | OV      | PV      |  |  |

| Bit 7                                                                                                                          |                                                                                                                                                                                                                            |         |         |         |         |         | Bit 0   |  |  |

| Bit 7<br>Bit 6<br>Bit 5<br>Bit 4<br>Bit 3<br>Bit 2<br>Bit 1<br>Bit 0                                                           | <ul> <li>PG: Power Good Warning (high and low)</li> <li>TR: Tracking Fault</li> <li>OT: Over Temperature Fault</li> <li>OC: Over Current Fault</li> <li>UV: Under Voltage Fault</li> <li>OV: Over Voltage Error</li> </ul> |         |         |         |         |         |         |  |  |

| Note: an activated fault is encoded as '0'<br><sup>1)</sup> Writing a '1' into a fault/error bit clears a latching fault/error |                                                                                                                                                                                                                            |         |         |         |         |         |         |  |  |

Figure 32. Protection Configuration Register PC1

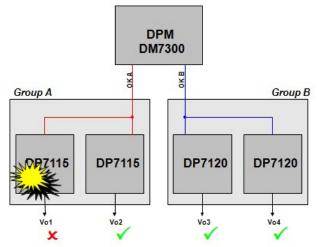

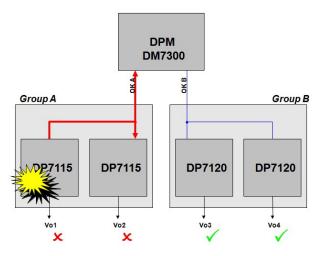

#### 7.4.5 Fault and Error Turn Off Control

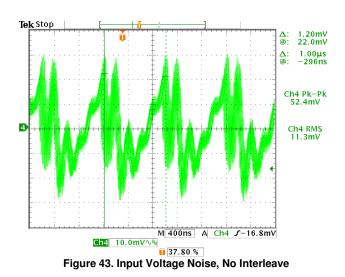

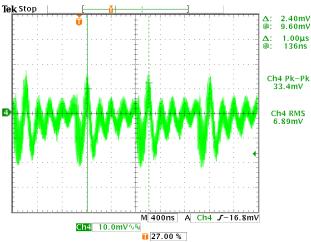

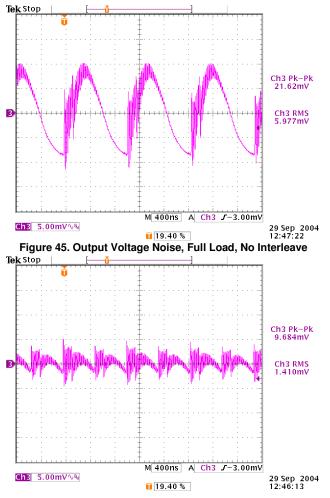

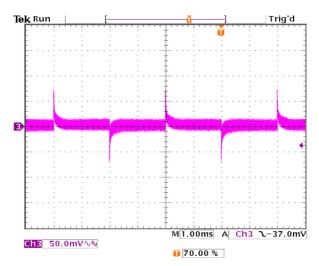

In the GUI dPOL Fault dialog is a column of spin controls which set the Turn-Off style OT, UV and OV