### Freescale Semiconductor Technical Data

MC144110/D Rev. 2, 1/2005

# MC144110

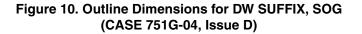

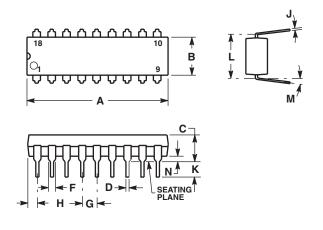

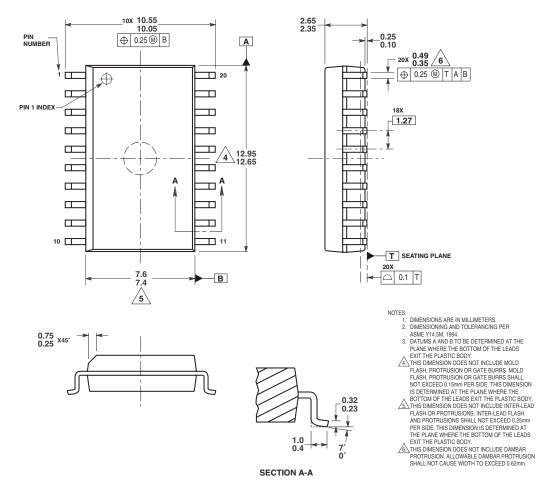

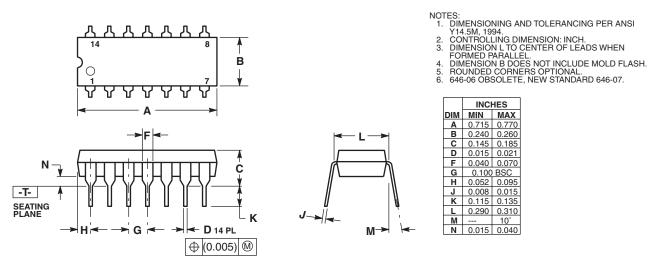

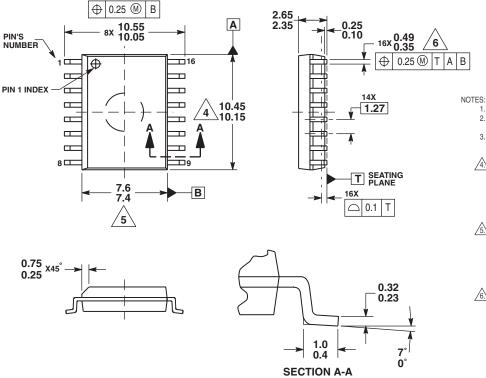

Package Information P Suffix Plastic DIP Case 707 Package Information DW Suffix SOG Package Case 751D

# MC144111

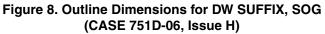

Package Information P Suffix Plastic DIP Case 646 Package Information DW Suffix SOG Package Case 751G

### **Ordering Information**

| Device     | Package     |

|------------|-------------|

| MC144110P  | Plastic DIP |

| MC144110DW | SOG         |

| MC144111P  | Plastic DIP |

| MC144111DW | SOG         |

### Contents

| 1 | Introduction              | 3-45 |

|---|---------------------------|------|

| 2 | Electrical Specifications | 3-48 |

| 3 | Switching Characteristics | 3-49 |

| 4 | Pin Descriptions          | 3-52 |

5 Packaging ..... 3-54

# MC144110 and MC144111

Digital-to-Analog Converters with Serial Interface CMOS LSI

# 1 Introduction

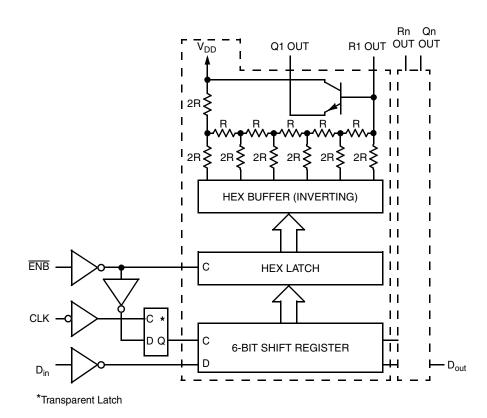

The MC144110 and MC144111 are low-cost 6-bit D/A converters with serial interface ports to provide communication with CMOS microprocessors and microcomputers. The MC144110 contains six static D/A converters; the MC144111 contains four converters.

Due to a unique feature of these DACs, the user is permitted easy scaling of the analog outputs of a system. Over a 5 to 15 V supply range, these DACs may be directly interfaced to CMOS MPUs operating at 5 V.

- Direct R-2R Network Outputs

- Buffered Emitter-Follower Outputs

- Serial Data Input

- Digital Data Output Facilitates Cascading

- Direct Interface to CMOS µP

- Wide Operating Voltage Range: 4.5 to 15 V

- Wide Operating Temperature Range: 0 to 85°C

- Software Information is Contained in Document M68HC11RM/AD

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Figure 1. Block Diagram

MC144110

#### Introduction

| MC144110P         |       |                  |  |  |

|-------------------|-------|------------------|--|--|

| D <sub>in</sub>   | 1• 18 | V <sub>DD</sub>  |  |  |

| Q1 Out            | 2 17  | D <sub>out</sub> |  |  |

| R1 Out            | 3 16  | R6 Out           |  |  |

| Q2 Out            | 4 15  | Q6 Out           |  |  |

| R2 Out            | 5 14  | R5 Out           |  |  |

| Q3 Out            | 6 13  | Q5 Out           |  |  |

| R3 Out            | 7 12  | R4 Out           |  |  |

| ENB               | 8 11  | Q4 Out           |  |  |

| V <sub>SS</sub> [ | 9 10  | CLK              |  |  |

|                   |       |                  |  |  |

#### MC144110DW

| D <sub>in</sub> [1● 20] V <sub>D</sub> | D     |

|----------------------------------------|-------|

|                                        |       |

| Q1 Out 2 19 D <sub>o</sub>             | ut    |

| R1 Out 3 18 R6                         | Out   |

| Q2 Out 4 17 Q6                         | 6 Out |

| R2 Out 5 16 R5                         | Out   |

| Q3 Out 6 15 Q5                         | 5 Out |

| R3 Out 7 14 R4                         | Out   |

| ENB 8 13 Q4                            | Out   |

| V <sub>SS</sub> 9 12 CL                | K     |

|                                        | )     |

#### MC144111P

| D <sub>in</sub> | 1 • | 14 | V <sub>DD</sub>  |

|-----------------|-----|----|------------------|

| Q1 Out          | 2   | 13 | D <sub>out</sub> |

| R1 Out          | 3   | 12 | R4 Out           |

| Q2 Out          | 4   | 11 | Q4 Out           |

| R2 Out          | 5   | 10 | R3 Out           |

| ENB             | 6   | 9  | Q3 Out           |

| $V_{SS}$        | 7   | 8  | CLK              |

#### MC144111DW

| D <sub>in</sub>   | 1. | 16 | V <sub>DD</sub>  |

|-------------------|----|----|------------------|

| Q1 Out            | 2  | 15 | D <sub>out</sub> |

| R1 Out            | 3  | 14 | R4 Out           |

| Q2 Out            | 4  | 13 | Q4 Out           |

| R2 Out            | 5  | 12 | R3 Out           |

| ENB               | 6  | 11 | Q3 Out           |

| V <sub>SS</sub> [ | 7  | 10 | CLK              |

| ۵                 | 8  | 9  | NC               |

NC = No Connection

Figure 2. Pin Assignments

# 2 Electrical Specifications

#### Table 1. Maximum Ratings

| (Voltages | referenced | to | V <sub>SS</sub> ) |

|-----------|------------|----|-------------------|

|-----------|------------|----|-------------------|

|                                                              | Ratings                                                           | Symbol           | Value                          | Unit |

|--------------------------------------------------------------|-------------------------------------------------------------------|------------------|--------------------------------|------|

| DC Supply Volt                                               | age                                                               | V <sub>DD</sub>  | - 0.5 to + 18                  | V    |

| Input Voltage,                                               | All Inputs                                                        | V <sub>in</sub>  | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Input Curre                                               | nt, per Pin                                                       | I                | ± 10                           | mA   |

|                                                              | ion (Per Output)<br>MC144110<br>MC144111<br>MC144110<br>MC144111  | P <sub>OH</sub>  | 30<br>50<br>10<br>20           | mW   |

| Power Dissipat<br>$T_A = 70^{\circ}C$<br>$T_A = 85^{\circ}C$ | ion (Per Package)<br>MC144110<br>MC144111<br>MC144110<br>MC144111 | P <sub>D</sub>   | 100<br>150<br>25<br>50         | mW   |

| Storage Tempe                                                | rature Range                                                      | T <sub>stg</sub> | - 65 to + 150                  | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields; however, it is advised that precautions be taken to avoid application of voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>).

#### Table 2. Electrical Characteristics

(Voltages referenced to  $V_{SS}$ ,  $T_A = 0$  to  $85^{\circ}C$  unless otherwise indicated)

| Symbol            | Parameter                                             | Test Conditions                          | V <sub>DD</sub> | Min             | Max               | Unit |

|-------------------|-------------------------------------------------------|------------------------------------------|-----------------|-----------------|-------------------|------|

| V <sub>IH</sub>   | High-Level Input Voltage (D <sub>in</sub> , ENB, CLK) |                                          | 5<br>10<br>15   | 3.0<br>3.5<br>4 | -<br>-<br>-       | V    |

| V <sub>IL</sub>   | Low-Level Input Voltage (D <sub>in</sub> , ENB, CLK)  |                                          | 5<br>10<br>15   | -<br>-<br>-     | 0.8<br>0.8<br>0.8 | V    |

| I <sub>OH</sub>   | High-Level Output Current (D <sub>out</sub> )         | $V_{out} = V_{DD} - 0.5 V$               | 5               | - 200           | -                 | μA   |

| I <sub>OL</sub>   | Low-Level Output Current (D <sub>out</sub> )          | $V_{out} = 0.5 V$                        | 5               | 200             | -                 | μA   |

| I <sub>DD</sub>   | Quiescent Supply Current MC144110<br>MC144111         | I <sub>out</sub> = 0 μA                  | 15<br>15        | -               | 12<br>8           | mA   |

| I <sub>in</sub>   | Input Leakage Current (D <sub>in</sub> , ENB, CLK)    | V <sub>in</sub> = V <sub>DD</sub> or 0 V | 15              | -               | ± 1               | μA   |

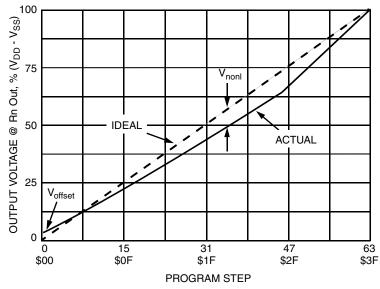

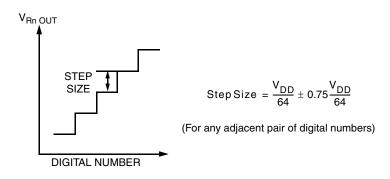

| V <sub>nonl</sub> | Nonlinearity Voltage (Rn Out)                         | See Figure 3                             | 5<br>10<br>15   | -<br>-<br>-     | 100<br>200<br>300 | mV   |

**Switching Characteristics**

### Table 2. Electrical Characteristics (continued)

| Symbol              | Parameter                           | Test Conditions                                          | V <sub>DD</sub> | Min            | Max               | Unit |

|---------------------|-------------------------------------|----------------------------------------------------------|-----------------|----------------|-------------------|------|

| V <sub>step</sub>   | Step Size (Rn Out)                  | See Figure 4                                             | 5<br>10<br>15   | 19<br>39<br>58 | 137<br>274<br>411 | mV   |

| V <sub>offset</sub> | Offset Voltage from V <sub>SS</sub> | D <sub>in</sub> = \$00, See Figure 3                     | -               | -              | 1                 | LSB  |

| Ι <sub>Ε</sub>      | Emitter Leakage Current             | V <sub>Rn Out</sub> = 0 V                                | 15              | -              | 10                | μA   |

| h <sub>FE</sub>     | DC Current Gain                     | I <sub>E</sub> = 0.1 to 10.0 mA<br>T <sub>A</sub> = 25°C | -               | 40             | -                 | -    |

| V <sub>BE</sub>     | Base-to-Emitter Voltage Drop        | I <sub>E</sub> = 1.0 mA                                  | -               | 0.4            | 0.7               | V    |

(Voltages referenced to  $V_{SS}$ ,  $T_A = 0$  to 85°C unless otherwise indicated)

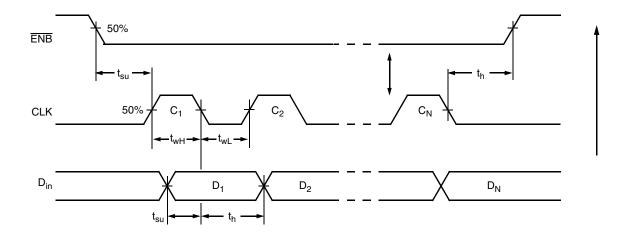

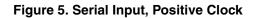

# 3 Switching Characteristics

### **Table 3. Switching Characteristics**

(Voltages referenced to V<sub>SS</sub>,  $T_A = 0$  to 85°C,  $C_L = 50$  pF, Input  $t_r = t_f = 20$  ns unless otherwise indicated)

| Symbol                          | Parameter                                            | V <sub>DD</sub> | Min  | Мах | Unit |

|---------------------------------|------------------------------------------------------|-----------------|------|-----|------|

| t <sub>wH</sub>                 | Positive Pulse Width, CLK (Figures 5 and 6)          | 5               | 2    | -   | μS   |

|                                 |                                                      | 10              | 1.5  | -   |      |

|                                 |                                                      | 15              | 1    | -   |      |

| t <sub>wL</sub>                 | Negative Pulse Width, CLK (Figure 5 and 6)           | 5               | 5    | -   | μs   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>su</sub>                 | Setup Time, ENB to CLK (Figures 5 and 6)             | 5               | 5    | -   | μs   |

| 04                              |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>su</sub>                 | Setup Time, D <sub>in</sub> to CLK (Figures 5 and 6) | 5               | 1000 | -   | ns   |

| 04                              |                                                      | 10              | 750  | -   |      |

|                                 |                                                      | 15              | 500  | -   |      |

| t <sub>h</sub>                  | Hold Time, CLK to ENB (Figures 5 and 6)              | 5               | 5    | -   | μs   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>h</sub>                  | Hold Time, CLK to D <sub>in</sub> (Figures 5 and 6)  | 5               | 5    | -   | μs   |

|                                 |                                                      | 10              | 3.5  | -   |      |

|                                 |                                                      | 15              | 2    | -   |      |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise and Fall Times                            | 5 - 15          | -    | 2   | μS   |

| C <sub>in</sub>                 | Input Capacitance                                    | 5 - 15          | -    | 7.5 | pF   |

Figure 4. Definition of Step Size

Figure 6. Serial Input, Negative Clock

| Table 4. Number of | f Channels vs | <b>Clocks Required</b> |

|--------------------|---------------|------------------------|

|--------------------|---------------|------------------------|

| Number of Channels<br>Required | Number of<br>Clock Cycles | Outputs Used on MC144110                 | Outputs Used on MC144111   |

|--------------------------------|---------------------------|------------------------------------------|----------------------------|

| 1                              | 6                         | Q1/R1                                    | Q1/R1                      |

| 2                              | 12                        | Q1/R1, Q2/R2                             | Q1/R1, Q2/R2               |

| 3                              | 18                        | Q1/R1, Q2/R2, Q3/R3                      | Q1/R1, Q2/R2, Q3/R3        |

| 4                              | 24                        | Q1/R1, Q2/R2, Q3/R3, Q4/R4               | Q1/R1, Q2/R2, Q3/R3, Q4/R4 |

| 5                              | 30                        | Q1/R1, Q2/R2, Q3/R3, Q4/R4, Q5/R5        | Not Applicable             |

| 6                              | 36                        | Q1/R1, Q2/R2, Q3/R3, Q4/R4, Q5/R5, Q6/R6 | Not Applicable             |

# 4 Pin Descriptions

# 4.1 INPUTS

# D<sub>in</sub> Data Input

Six-bit words are entered serially, MSB first, into digital data input, D<sub>in</sub>. Six words are loaded into the MC144110 during each D/A cycle; four words are loaded into the MC144111.

The last 6-bit word shifted in determines the output level of pins Q1 Out and R1 Out. The next-to-last 6-bit word affects pins Q2 Out and R2 Out, etc.

# ENB

### **Negative Logic Enable**

The  $\overline{\text{ENB}}$  pin must be low (active) during the serial load. On the low-to-high transition of  $\overline{\text{ENB}}$ , data contained in the shift register is loaded into the latch.

# CLK Shift Register Clock

Data is shifted into the register on the high-to-low transition of CLK. CLK is fed into the D-input of a transparent latch, which is used for inhibiting the clocking of the shift register when  $\overline{\text{ENB}}$  is high.

The number of clock cycles required for the MC144110 is usually 36. The MC144111 usually uses 24 cycles. See Table 4 for additional information.

# 4.2 OUTPUTS

# D<sub>out</sub> Data Output

The digital data output is primarily used for cascading the DACs and may be fed into D<sub>in</sub> of the next stage.

# R1 Out through Rn Out Resistor Network Outputs

These are the R-2R resistor network outputs. These outputs may be fed to high-impedance input FET op amps to bypass the on-chip bipolar transistors. The R value of the resistor network ranges from 7 to 15 k $\Omega$ .

# Q1 Out through Qn Out NPN Transistor Outputs

Buffered DAC outputs utilize an emitter-follower configuration for current-gain, thereby allowing interface to low-impedance circuits.

### 4.3 SUPPLY PINS

### V<sub>SS</sub> Negative Supply Voltage

This pin is usually ground.

### V<sub>DD</sub> Positive Supply Voltage

The voltage applied to this pin is used to scale the analog output swing from 4.5 to 15 V p-p.

# 5 Packaging

NOTES:

1. POSITIONAL TOLERANCE OF LEADS (D). SHALL BE WITHIN 0.25 (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

| 4. CONTROLLING DIMENSION: INCH. |

|---------------------------------|

|---------------------------------|

|     | INCHES    |       | MILLIMETERS |       |

|-----|-----------|-------|-------------|-------|

| DIM | MIN       | MAX   | MIN         | MAX   |

| Α   | 0.875     | 0.915 | 22.22       | 23.24 |

| в   | 0.240     | 0.260 | 6.10        | 6.60  |

| С   | 0.140     | 0.180 | 3.56        | 4.57  |

| D   | 0.014     | 0.022 | 0.36        | 0.56  |

| F   | 0.050     | 0.070 | 1.27        | 1.78  |

| G   | 0.100 BSC |       | 2.54 BSC    |       |

| Н   | 0.040     | 0.060 | 1.02        | 1.52  |

| L   | 0.008     | 0.012 | 0.20        | 0.30  |

| κ   | 0.115     | 0.135 | 2.92        | 3.43  |

| L   | 0.300 BSC |       | 7.62 BSC    |       |

| Μ   | 0°        | 15°   | 0°          | 15°   |

| Ν   | 0.020     | 0.040 | 0.51        | 1.02  |

Figure 7. Outline Dimensions for P SUFFIX, PLASTIC DIP (CASE 707-02, Issue C)

Figure 9. Outline Dimensions for P SUFFIX, PLASTIC DIP (CASE 646-07, Issue P)

1.

- DIMENSIONS ARE IN MILLIMETERS. DIMENSIONING AND TOLERANCING PER ASME 2. Y14.5M, 1994.

- DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS 3. EXIT THE PLASTIC BODY.

- 4. THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- INTER-LEAD FLASH OR PROTRUSIONS. SHALL NOT EXCEED 0.25mm PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

6. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62mm.