# Contents

| Page | Section     | Title                                 |

|------|-------------|---------------------------------------|

| 4    | 1.          | Introduction                          |

| 4    | 1.1.        | Features                              |

| 5    | 2.          | <b>Functional Description</b>         |

| 5    | 2.1.        | CPU                                   |

| 5    | 2.2.        | ROM                                   |

| 5    | 2.3.        | RAM                                   |

| 5    | 2.4.        | Clock Generator                       |

| 6    | 2.5.        | Control Register                      |

| 6    | 2.6.        | Reset Function                        |

| 8    | 2.7.        | Watchdog                              |

| 9    | 2.8.        | Ports P0–0 to P3–7                    |

| 10   | 2.9.        | 6-bit DACs PWM0 to PWM5               |

| 10   | 2.10.       | 14-bit DAC PWM6                       |

| 11   | 2.11.       | I <sup>2</sup> C and IM-Bus Interface |

| 16   | 2.12.       | A/D Converter                         |

| 17   | 2.13.       | Closed Caption Acquisition            |

| 17   | 2.13.1.     | Video Input                           |

| 18   | 2.13.2.     | Closed Caption Data Detection         |

| 21   | 2.13.3.     | Gate and Window Logic                 |

| 25   | 2.14.       | OSD                                   |

| 25   | 2.14.1.     | Summary of OSD Features               |

| 25   | 2.14.2.     | Fonts                                 |

| 25   | 2.14.3.     | OSD Window                            |

| 26   | 2.14.4.     | Colors                                |

| 26   | 2.14.4.1.   | OSD Attribute 'COLOR'                 |

| 26   | 2.14.4.1.1. | Attribute 'Transparent'               |

| 26   | 2.14.4.2.   | Available Colors                      |

| 27   | 2.14.4.3.   | Color Palette Programming             |

| 27   | 2.14.4.4.   | Color Palette Hardware                |

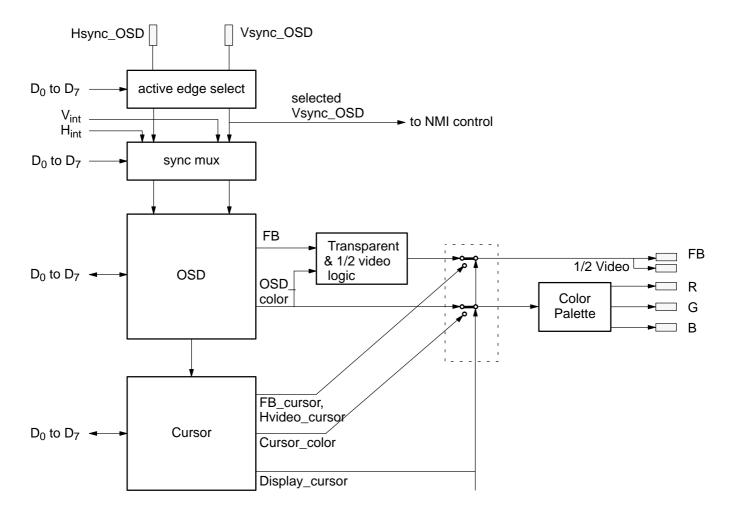

| 28   | 2.14.5.     | Fast Blank Output                     |

| 28   | 2.14.6.     | Half-Video Output                     |

| 29   | 2.14.7.     | Using OSD                             |

| 31   | 2.14.8.     | OSD Attributes                        |

| 32   | 2.14.9.     | Font Definition                       |

| 32   | 2.14.10.    | Soft-Scroll                           |

| 33   | 2.15.       | Cursor                                |

| 33   | 2.15.1.     | Cursor Definition                     |

| 34   | 2.15.2.     | Cursor Position                       |

| 34   | 2.15.3.     | Moving and Changing the Cursor        |

| 34   | 2.15.4.     | Cursor Control Bits                   |

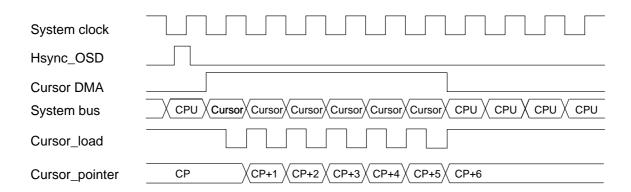

| 35   | 2.15.5.     | Cursor DMA                            |

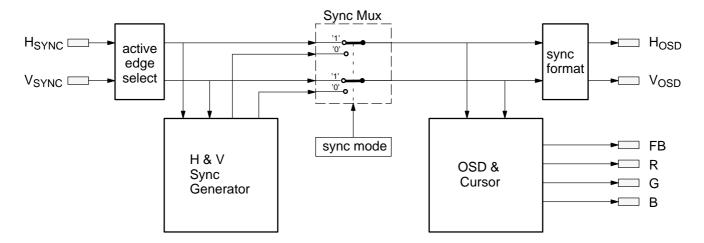

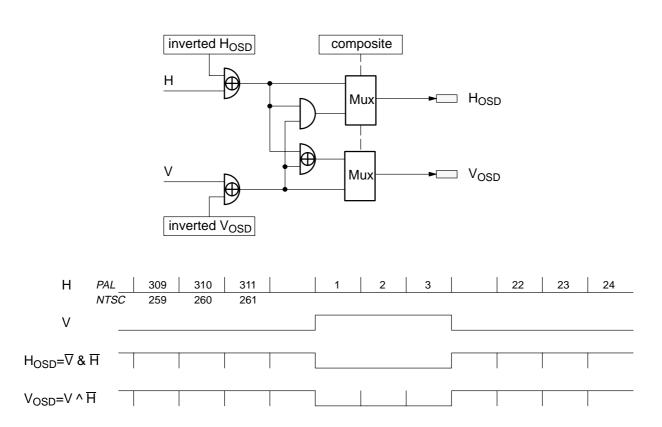

| 36   | 2.16.       | H&V Sync Generator                    |

| 38   | 2.17.       | Infrared Input                        |

| 40   | 2.17.1.     | Infrared Detection Status             |

| 40   | 2.17.2.     | Infrared Detection Control            |

| 40   | 2.17.3.     | Sample Times                          |

|      |             |                                       |

# Contents, continued

| Page | Section  | Title                                               |

|------|----------|-----------------------------------------------------|

| 41   | 2.18.    | Timer                                               |

| 41   | 2.19.    | Interrupt System                                    |

| 42   | 3.       | Specifications                                      |

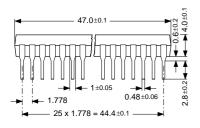

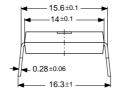

| 42   | 3.1.     | Outline Dimensions                                  |

| 42   | 3.2.     | Pin Connections and Short Descriptions              |

| 45   | 3.3.     | Pin Descriptions                                    |

| 47   | 3.4.     | Pin Configuration                                   |

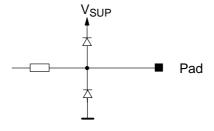

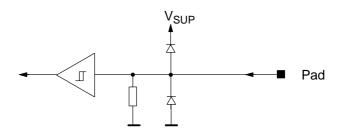

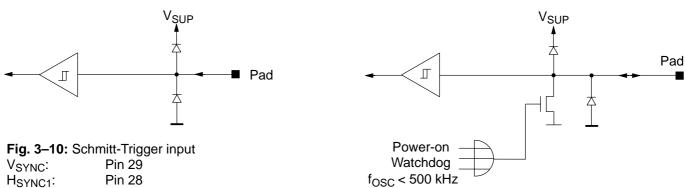

| 48   | 3.5.     | Pin Circuits                                        |

| 50   | 3.6.     | Electrical Characteristics                          |

| 50   | 3.6.1.   | Absolute Maximum Ratings                            |

| 51   | 3.6.2.   | Recommended Operating Conditions                    |

| 52   | 3.6.3.   | Recommended Crystal Characteristics                 |

| 53   | 3.6.4.   | DC Characteristics                                  |

| 54   | 3.6.5.   | DC Parameters I <sup>2</sup> C-Bus Master Interface |

| 54   | 3.6.6.   | A/D Converter Characteristics                       |

| 55   | 4.       | Definitions                                         |

| 55   | 4.1.     | I/O Definitions                                     |

| 56   | 5.       | Register Description                                |

| 74   | 6.       | Appendix A: Closed Caption                          |

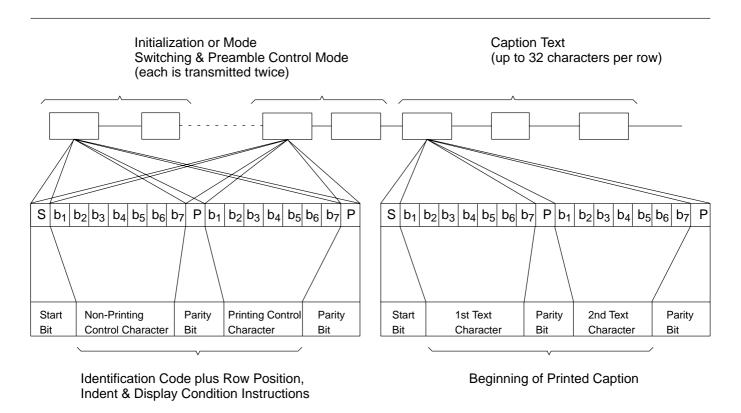

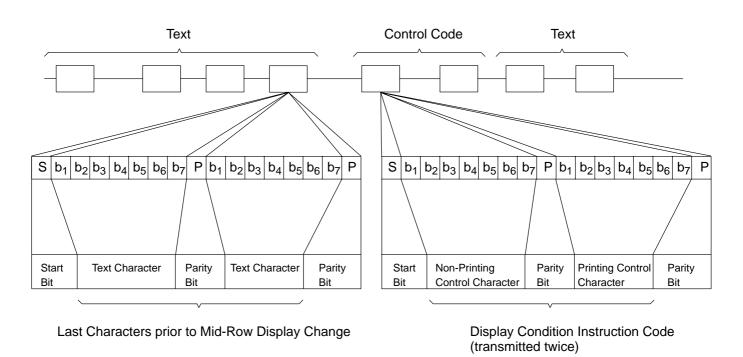

| 74   | 6.1.     | The Closed Caption Standard                         |

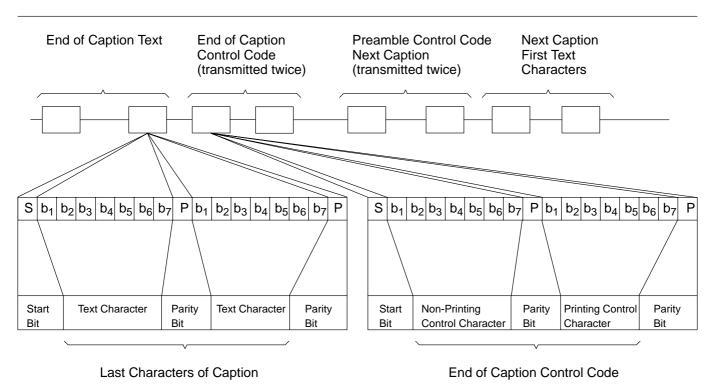

| 74   | 6.1.1.   | Data Transmission Format                            |

| 76   | 6.2.     | Closed Caption Decoder                              |

| 76   | 6.2.1.   | Operating Modes                                     |

| 76   | 6.2.2.   | Screen Format                                       |

| 76   | 6.2.2.1. | Text Mode                                           |

| 77   | 6.2.2.2. | Caption Mode                                        |

| 79   | 6.2.3.   | Presentation Format                                 |

| 79   | 6.2.4.   | Character Format                                    |

| 80   | 6.2.5.   | Character Attributes                                |

| 80   | 6.2.6.   | Control Codes                                       |

| 85   | 6.2.7.   | Data Rejection                                      |

| 85   | 6.2.8.   | Automatic Display Enable/Disable                    |

| 85   | 6.2.8.1. | Enable Logic and Timing                             |

| 85   | 6.2.8.2. | Disable Logic and Timing                            |

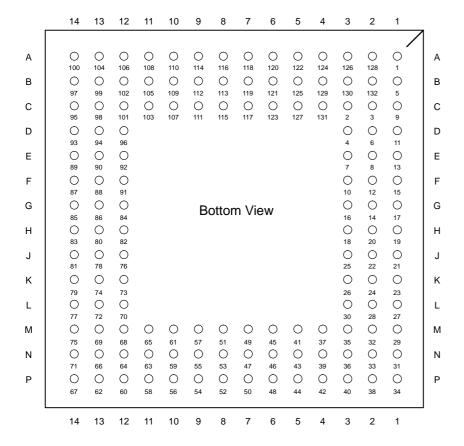

| 86   | 7.       | Appendix B: Pin Configuration of PGA Package        |

| 87   | 7.1.     | Pin Connections in CPGA132F Package                 |

| 88   | 8.       | Data Sheet History                                  |

# Central Control Unit Single Chip Microcontroller with Embedded Closed Caption Decoder

#### 1. Introduction

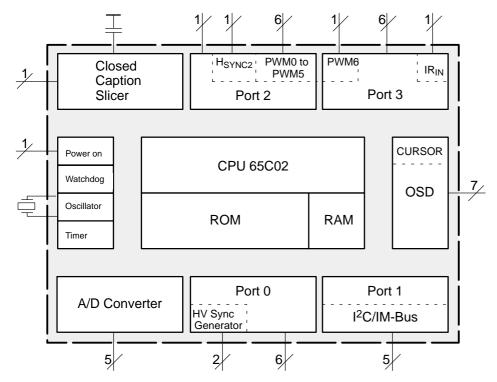

The Central Control Unit CCZ 3005K is an integrated circuit designed in CMOS technology and housed in a 52-pin Plastic Shrink Dual-In-Line Package. It is used as a single-chip TV controller with embedded Closed Caption Decoder and On-Screen Display.

#### 1.1. Features

- 6 MHz 65C02 CPU, 12 MHz crystal

- 52-pin PSDIP package

- on-chip oscillator

- clock generator with programmable frequency

- 62 KBytes internal ROM

- 1536 Bytes internal RAM

- Closed Caption Decoder

- programmable TV-line detector

- 2 selectable H<sub>SYNC</sub> inputs

- 2 programmable H & V sync outputs

- free running H & V sync generator for stable OSD

- full-screen OSD with separate 24\*24 pixel Cursor controls RGB and Fast Blank outputs

- color palette: 8 out of 64 different colors programmable

- soft-scroll, underline, flash, italics

- Half-Video control output

- I<sup>2</sup>C/IM-bus master interface

- six 6-bit D/A converters (PWM)

- single 14-bit D/A converter (PWM) for voltage synthesizer

- up to 29 port lines

- 8-bit A/D converter (6-bit precision) with 5 multiplexed inputs

- infrared input hardware supporting software decoding

- free-running timer generating interrupts

- power-on and clock supervision

- watchdog

Fig. 1-1: Block Diagram of the CCZ 3005K

## 2. Functional Description

# 2.1. CPU

The CPU is a standard 65C02 core.

#### 2.2. ROM

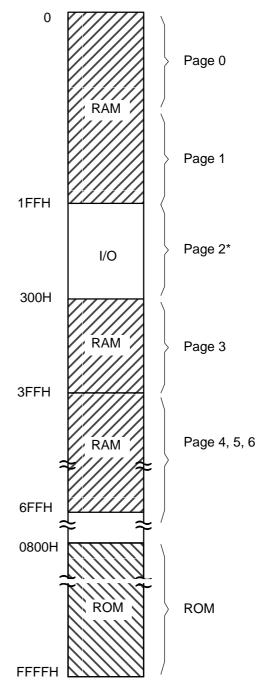

The CCZ 3005K has 62 kBytes of mask-programmable ROM on chip. It covers the addresses from 0800H to FFFFH.

## 2.3. RAM

1536 Bytes RAM are integrated as two portions:

Table 2-1: RAM configurations

| Page    | Start | Stop  | Length<br>in Bytes |

|---------|-------|-------|--------------------|

| 0 and 1 | 0000H | 01FFH | 512                |

| 3 – 6   | 0300H | 06FFH | 1024               |

Page 0 offers particularly fast access for the CPU and is therefore very valuable for fast, compact programs. Page 1 contains the stack area. Page 3 and following are used as display memory for CCD (Closed Caption Decoding) and OSD (On-Screen Display). Page 2 is reserved as I/O page (the 65C02 has memory-mapped I/O).

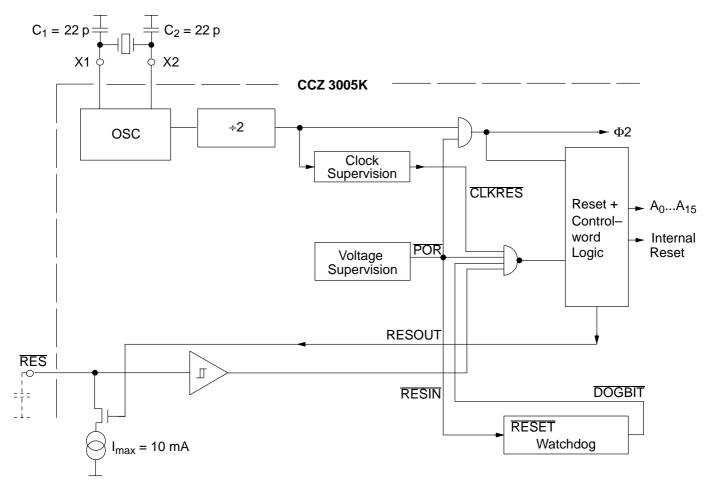

# 2.4. Clock Generator

An integrated two-pin oscillator, accompanied by a programmable divider, generates the clock for the microcontroller. The divider is expressed by the equation

$$f_{\text{system}} = f_{\text{XTAL}} / 2*(n+1)$$

where n is a value from 0 to 255. After reset n is set to 0.  $f_{system}$  can be modified by writing a new 'n' value to address 200H.

Important: Any kind of display mode (OSD or CCD) requires a system speed of  $f_{XTAL/2}$  (n = 0). All timings in the CCZ are based on  $f_{system}$ . Other timings than  $f_{system} = f_{XTAL/2}$  are not recommended.

Fig. 2-1: Address map

\* With the exception of addr. 02E0H to 02E7H all register addresses of page 2 are internal. With 02E0H to 02E7H external hardware access is possible. These addresses are used for emulation purposes.

#### 2.5. Control Register

This is a combination of control switches in an 8-bit register. During reset it is loaded with the contents of the address FFF9H, but it can also be read and written via software (address 0201H). The switches have the following functions:

bit 0 CPU: '0' = disabled, '1' = enabled bit 1 RAM; '0' = disabled, '1' = enabled<sup>1)</sup> bit 2 ROM: '0' = disabled, '1' = enabled bit 3 to 7 set them to 1

Set bit 4 to '0'. This enables the additional address and data lines. If bit 1 of the control register is set to '1', addresses 0 to 1FFH and 300H to 7FFH are assumed to be inside the CCZ emulator chip. Thus the data bus may not access external devices (RAM) located in this address range. With the control byte "%11101001" = "E9H" the emulator chip can access almost 64 kBytes of exter-

nal memory. Only the addresses for the internal I/O registers stay internal (page 2 without 2E0H to 2E7H).

The logical level at the TEST-pin during RESET decides whether the control byte is read from internal or external memory. For operation without external memory test pin = low-level is used, with the (internal) control byte set to FFH

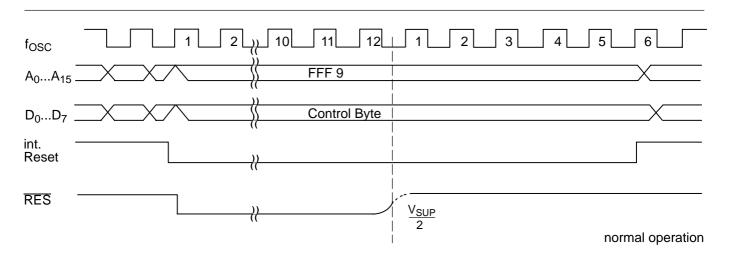

#### 2.6. Reset Function

The internal reset provides a correct basic setup of the complete hardware on the chip. An internal control register (adr. 201H) is loaded during reset with the byte out of address FFF9H. The internal voltage supervision resets the IC if the voltage is too low. If the frequency is too low, the same function is effected by the clock supervision. Once activated and not refreshed correctly, the watchdog also generates a reset (see chapter 2.7. for details). These internal reset sources (watchdog, voltage detector and clock supervision) use the reset pin as output. Internal resistors limit the maximum current.

Fig. 2-2: Oscillator and reset

<sup>1)</sup> To use the emulator chip version:

CCZ 3005K

Fig. 2–3: External reset sequence

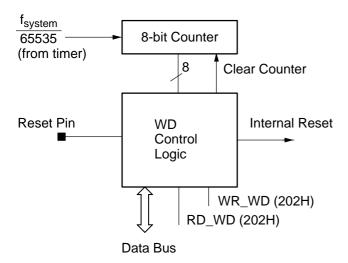

## 2.7. Watchdog

This counter circuit offers hardware support for software problems. It is disabled after reset and enabled with the first write of the desired time value into its register. The value to program is calculated by:

(1)

$$n = (T_{WD} * f_{system} / 65536) - 1$$

with n = watchdog counter value to be programmed for  $T_{WD}$  = the desired watchdog time and  $f_{system}$  = system frequency.

## Remarks:

- a) To prevent the generation of a "RESET" by the watchdog before it could be retriggered by the software, watchdog counter values of less than 2 should not be programmed.

- b) The system clock as input of the watchdog counter is influenced by the system clock prescaler, determining the CPU speed (register addr. 200H).

The software cannot stop this counter, but has to retrigger it by writing the inverted value (one's complement) of the preceding written pattern into its register, which makes unwanted retrigger loops of disturbed software unlikely. These writes have to occur within the time frame (32 ms to 2 s at 6 MHz system clock), defined with the first write. If no write with the expected pattern occurs within the programmed time period, the watchdog circuit resets the CCZ at the end of the time period.

The software can detect if a reset was generated by the watchdog: bit 0 of the watchdog register is '0' if the last reset was generated by the watchdog. This bit is preset (set to '1') only by power-on or writing to the watchdog register. Thus checking it has to occur before the first watchdog register write access.

Fig. 2-4: Watchdog

#### Examples:

To set a cycle time of 1 s with a 6MHz system clock, the value is 91. This value is calculated as follows:

```

system frequency: 6MHz,

watchdog cycle time: 65536 / 6MHz = 10.92ms,

counter value: 1s/10.92ms = 91.55.

```

The nearest integer value is 92. As a 0 loaded into the counter divides by 1, already, the watchdog counter has to be programmed with 92 - 1 = 91. Using the above-mentioned equation (1):

```

n = 91 = 1s * 6MHz/65536 - 1

```

the software sequences in Assembler could look like this:

#### Definitions:

# Example 1:

During initialization the watchdog is filled with the desired time-value:

```

LDA #WATCHDOG_TIME

STA watchdog_address

STA watchdog_value ; memorize pattern

```

In the main loop of the program the watchdog has to be retriggered cyclically

```

LDA watchdog_value

EOR #FFH

STA watchdog_address ; invert bits

STA watchdog_value ; memorize new pattern

```

### Example 2:

If an interrupt function occurs cyclically, one value may be programmed in the interrupt service routine, while the other is written in the main loop. So both, the continuity of executing the interrupt service and the main loop are checked.

During initialization the watchdog is filled with the desired time value:

```

LDA #WATCHDOG_TIME

STA watchdog_value; memorize pattern

```

## Sequence in the interrupt function:

```

LDA watchdog_value

CMP #WATCHDOG_TIME

BEQ SKIP_IRQ_WD

;

STA watchdog_address

EOR #$FF

STA watchdog_value

SKIP_IRQ_WD:

```

#### Sequence in the main loop:

```

LDA watchdog_value

CMP #WATCHDOG_TIME

BNE SKIP_WD

;

STA watchdog_address

EOR #$FF

STA watchdog_value

SKIP_WD:

```

#### Remark:

It is important to program the watchdog register with the new value **before** this value is memorized in the shadow variable, because this procedure could be interrupted by the interrupt which programs the watchdog with the complementary value.

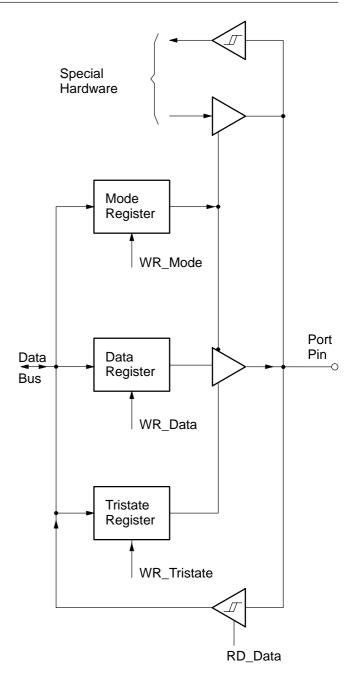

### 2.8. Ports P0-0 to P3-7

Up to 29 port lines grouped in 4 ports (3 \* 8bit, 1\*5bit) are available:

| P0-0 to P0-7 | 8 bits |

|--------------|--------|

| P1-0 to P1-4 | 5 bits |

| P2-0 to P2-7 | 8 bits |

| P3-0 to P3-7 | 8 bits |

Some of the port lines can be moved into the 'special mode'. Three registers in the I/O-page belong to each port:

```

mode register write only

(defines each line as port or special mode pin)

'0' = port mode = reset value

```

```

tristate register write only

(disables or enables the port output stage for each line)

'1' = tristate = reset value

```

```

data register read/write

(reads pin levels or writes port data)

'0' = reset value

```

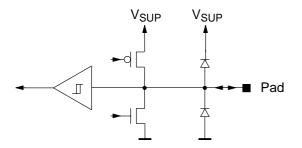

Fig. 2-5: Port logic

After Reset all Ports are in the Port and the output drivers in the tristate mode. The port output drivers have push-pull characteristics. This may be different in the special modes (see description of special mode blocks).

#### 2.9. 6-bit DACs PWM0 to PWM5

Six digital-to-analog converters belong to the CCZ 3005K. The push-pull outputs of the 6-bit PWM-converters are active if in the corresponding port registers the special mode flag is set *and* the tristate flag is reset (output=conducting):

Table 2-2: 6-bit DAC ports

| DAC  | Port Pin | Data Register<br>Address |

|------|----------|--------------------------|

| PWM0 | P20      | 250H                     |

| PWM1 | P21      | 251H                     |

| PWM2 | P22      | 252H                     |

| PWM3 | P23      | 253H                     |

| PWM4 | P24      | 254H                     |

| PWM5 | P25      | 255H                     |

By writing a 6-bit value to the converter's data register (D0 to D5 = value, D6, D7 = 0) the software can control the DACs. The minimum position (00H) generates a constant low output signal, the max. value (3FH) a 1/64 low signal. The clock of the PWM-converters is 1/8th of the system clock.

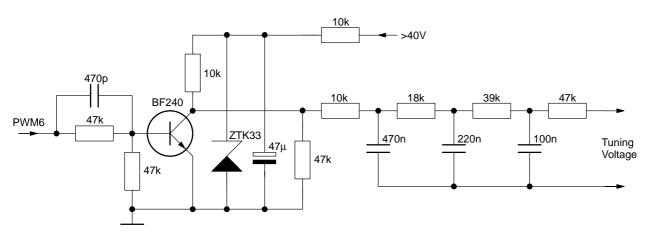

#### 2.10. 14-bit DAC PWM6

The CCZ 3005K is equipped with one 14-bit digital-toanalog converter for tuning voltage synthesis. The pushpull output of the 14-bit PWM-converter is active if in the corresponding port register the special mode flag is set and the tristate flag is reset (output=conducting):

Table 2-3: 14-bit DAC port

| DAC  | Port Pin | Data Register<br>Address       |  |  |

|------|----------|--------------------------------|--|--|

| PWM6 | P37      | 256H (6 LSBs)<br>257H (8 MSBs) |  |  |

By writing a 14-bit value to the converter's 2 data registers the software can control the 14-bit DAC. The minimum position (0000H) generates a constant low output signal, the max. value (FF3FH) a 1/16384 low signal. Writing into the MSB register (257H) starts the transfer of the complete 14-bit value into the internal PWM6 logic. This register should therefore be written after the LSB register (256H). The clock of the PWM6 converter is the system clock divided by 2.

The PWM6 output needs external circuitry to generate a stable tuning voltage. Fig. 2–6 shows the necessary components.

Fig. 2-6: Application circuit to generate tuning voltage

10

PRELIMINARY DATA SHEET CCZ 3005K

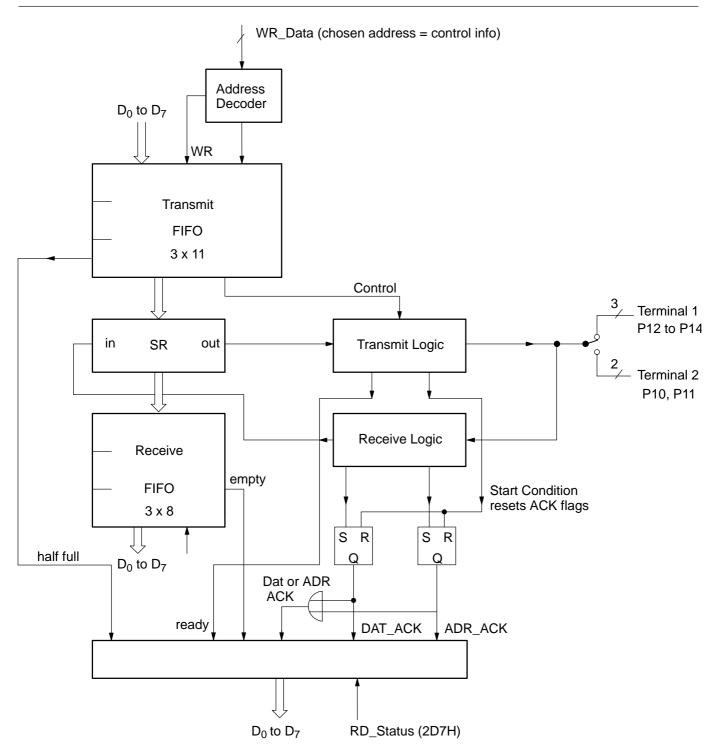

## 2.11. I<sup>2</sup>C and IM-Bus Interface

In special mode (conducting), port 1 works as a master bus interface. It can generate two different kinds of format:

- I<sup>2</sup>C format

- IM format

Two terminals are available: 3 pins (special mode of P12 to P14) as IM or  $I^2C$  lines and 2 pins (special mode of P10, P11) as  $I^2C$ . Terminal 2 can only operate as  $I^2C$  interface because of the missing third line. The MSBit of the bus prescaler registers (address 2DBH) is used to switch between terminals. The remaining 7 bits can be used to set the bit rate.

bit 7 0= terminal 1, 1= terminal 2 bit 6 to 0 bit rate= $f_{\text{system}}/(4 * n)$

where n is the value of bits 0 to 6 and the setting value (0 = reset state means n = 128). A complete telegram is assembled by the software out of individual sections. Each section contains an 8-bit data. This data is written into one of the nine possible Control-Data registers. Depending on the chosen address, a certain part of an  $I^2C$  or IM-bus cycle is generated. By means of corresponding calling sequences it is therefore possible to join even very long telegrams (e.g. long data files for auto increment addressing of  $I^2C$  slaves).

The software interface contains a 3 word deep FIFO for the control-data registers as well as for the received data. Thus all IM and most of the I<sup>2</sup>C telegrams can be transmitted to the hardware without the software having to wait for empty space in the FIFO.

All address and data fields appearing on the bus are constantly read and written into the Read-FIFO. The software can then check these data in comparison with the scheduled data. If a read instruction is handled, the interface must set the data word FFH so that the responding slave can insert its data. In this case the Read-FIFO contains the read-in data.

If telegrams longer than 3 bytes (1 address, 2 data bytes) are received, the software must check the filling condition of the control data FIFO and, if necessary, fill it up (or read out the Read-FIFO). A variety of status flags is available for this purpose.

Moreover, in the  $I^2C$  mode the ACK-bit is recorded separately on the bus lines for the address and the data fields. However, the interface itself can set the address ACK=0. In any case the two ACK flags show the actual bus condition. These flags remain until the next  $I^2C$  start condition is generated.

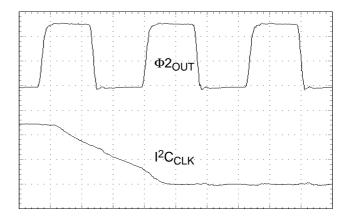

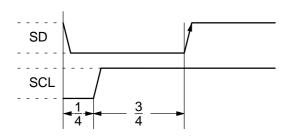

To minimize disturbances generated by the I $^2$ C signals, the fall times of both the I $^2$ C-SCL and I $^2$ C-SDA outputs on both I $^2$ C terminals are increased to one f<sub>SYSTEM</sub> cycle while its output currents are decreased to one third of its maximum. Thus by switching from high to low, it takes one f<sub>SYSTEM</sub> cycle until the maximum driver current is switched on. It depends on the sizes of the (external) load capacitance and pull-up resistor when the low level is reached (see Fig. 2–8 ). This feature is only active when the port output buffers are current-controlled, i.e., bit 5 of the "Hardware Control Register", address 209H. is set to '1'.

Capacities on any of the  $I^2C$  pins should not exceed 100 pF. Bigger capacitors could effect higher disturbances.  $R_{LOAD}$  should be equal to or greater than 2  $k\Omega.$

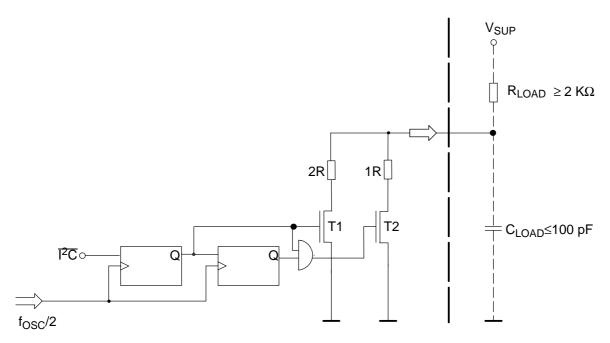

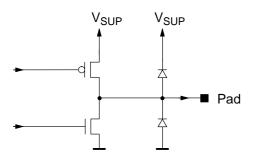

Fig. 2-7: I<sup>2</sup>C/IM-Bus Interface

Fig. 2–8: Principle of I<sup>2</sup>C signal outputs current reduction, during first T<sub>OSC</sub>, after switching from high to low

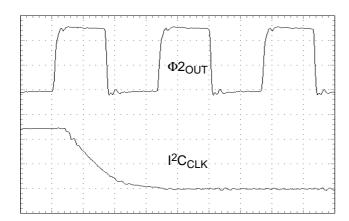

**Fig. 2–9:** Current reduction active, bit 5 of 'Hardware Control Register' set to '1'  $R_{LOAD} = 2 \ K\Omega$ ,  $C_{LOAD} = 100 \ pF$ , recommended

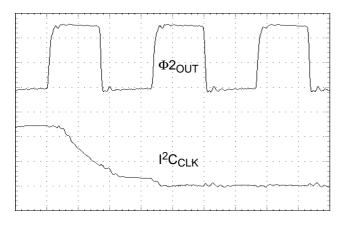

**Fig. 2–10:** Current reduction active, bit 5 of 'Hardware Control Register' set to '1',  $R_{LOAD} = 1 \text{ K}\Omega$ ,  $C_{LOAD} = 100 \text{ pF}$ , not recommended

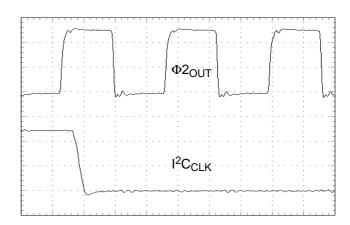

Fig. 2–11: Current reduction inactive, bit 5 of 'Hardware Control Register' set to '0',  $R_{LOAD} = 2 \text{ K}\Omega$ ,  $C_{LOAD} = 100 \text{ pF}$

**Fig. 2–12:** Current reduction active, bit 5 of 'Hardware Control Register' set to '1',  $R_{LOAD} = 2 \ K\Omega$ ,  $C_{LOAD} = 350 \ pF$ , not recommended

CCZ 3005K PRELIMINARY DATA SHEET

Table 2-4: I<sup>2</sup>C and IM-bus interface registers

| Address | Function                                                                                                            |                                  |  |

|---------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| 2D0H(w) | generates I <sup>2</sup> C start condition,<br>transfers Data as I <sup>2</sup> C address<br>and sets address ACK=1 |                                  |  |

| 2D1H(w) | same as above                                                                                                       | , ACK=0                          |  |

| 2D2H(w) | output 8 I <sup>2</sup> C Da<br>set ACK=1                                                                           | ıta bits,                        |  |

| 2D3H(w) | same as above                                                                                                       | , set ACK=0                      |  |

| 2D4H(w) | output 8 I <sup>2</sup> C Data bits,<br>sets ACK=1,<br>generates I <sup>2</sup> C stop condition                    |                                  |  |

| 2D5H(w) | same as above<br>sets ACK=0                                                                                         |                                  |  |

| 2D6H(r) | receives FIFO                                                                                                       |                                  |  |

| 2D7H(r) | status flags:                                                                                                       |                                  |  |

|         | bit 0                                                                                                               | not used                         |  |

|         | bit 1                                                                                                               | 1= receive<br>FIFO empty         |  |

|         | bit 2                                                                                                               | 1= contr-data-<br>FIFO half full |  |

|         | bit 3                                                                                                               | 1= Bus busy                      |  |

|         | bit 4                                                                                                               | I <sup>2</sup> C data ACK        |  |

|         | bit 5                                                                                                               | I <sup>2</sup> C adr ACK         |  |

|         | bit 6                                                                                                               | "OR"ed ACK                       |  |

|         | bit 7                                                                                                               | not used                         |  |

| 2D8H(w) | generates IM-address field                                                                                          |                                  |  |

| 2D9H(w) | generates 8 IM-data bits                                                                                            |                                  |  |

| 2DAH(w) | generates 8 IM-data bits and the IM-stop condition                                                                  |                                  |  |

| 2DBH(w) | terminal select & speed                                                                                             |                                  |  |

For example, the software has to work off the following sequence (ACK = 1) to read a 16-bit word from an  $I^2C$  device address 10H (on condition that the bus is not active):

| –write 21H to     | 2D0H   |                   |

|-------------------|--------|-------------------|

| -write 0FFH to    | 2D2H   | check             |

| -write 0FFH to    | 2D4H   | receive           |

| -read dev. addres | ss2D6H | FIFO empty flag   |

| -read 1st databyt |        | (bit 1, 2D7H) be- |

| -read 2nd databy  |        | fore read         |

The value 21H in the first step results from the device address in the 7 MSBs and the R/W-bit (read=1) in the LSB. If the telegrams are longer, the software has to ensure that neither the Control-Data-FIFO nor the Read-FIFO can overflow.

To write data to this device:

| -write 20H to           | 2D0H |

|-------------------------|------|

| -write 1st data byte to | 2D2H |

| -write 2nd data byte to | 2D4H |

The bus activity starts immediately after the first write to the Control-Data-FIFO. In the  $I^2C$  mode the transmission can be synchronized by an artificial extension of the Low phase of the clock line. Transmission is not continued until the state of the clock line is High once again. Thus a slave (software slave!) can adjust the transmission rate to its own abilities.

The PC/IM-bus interface is a pure Master system, Multimaster busses are not realizable.

The clock and data terminal pins have open-drain outputs. The IM-Bus-Ident Line (terminal 1 only) is a push-pull output stage (see chapter 3.6.5. on page 54).

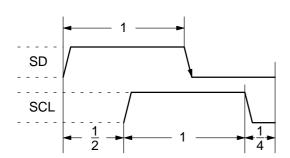

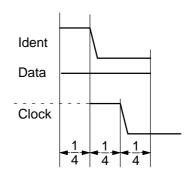

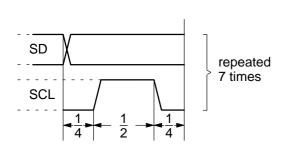

# UNIT = Bit-Period

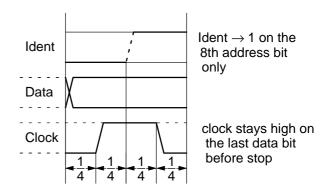

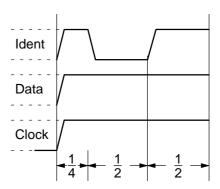

Fig. 2-13: Start condition I<sup>2</sup>C-bus

Fig. 2-16: IM-bus start condition

Fig. 2–14: Single bit on I<sup>2</sup>C-bus

Fig. 2-17: Single bit on IM-bus

Fig. 2–15: Stop condition I<sup>2</sup>C-bus

Fig. 2-18: Stop condition IM-bus

#### 2.12. A/D Converter

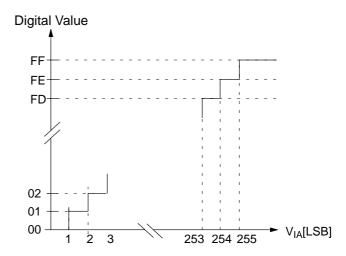

The analog voltages at 5 pins of the CCZ can be converted to an 8-bit digital value. With an input multiplexer one of these five inputs is selected. The input voltage is 'sampled and held' during conversion time. Conversion gets started with writing the number of the desired analog input pin into the 'Analog Input Select and Status' register (address 2A8H). After waiting until the 'End of Conversion' ('EOC') flag in this register (bit 7) is set to '1', the result is available in the 'A/D Converter Output' value register (address 2A9H).

The byte representing the analog voltage at the chosen ADC input pin is evaluated by

digital value = integer value of (256 x  $V_{IA}/V_{SUPA}$ ).  $V_{IA}$  = Analog Input Voltage  $V_{SUPA}$  = Analog Supply Voltage

The result of this equation is valid for  $GND_A < V_{IA} < V_{SUPA}$ . For  $V_{IA} \ge V_{SUPA}$  the digital value is its maximum: FFH.

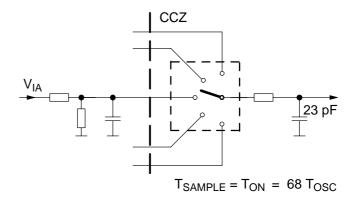

The converter needs 68 oscillator clock cycles to sample an input, so with a 12 MHz crystal it takes  $5.67\,\mu s$  to convert an analog value. During this time the input voltage should be kept as stable as possible (see Fig. 2–19).

The 'EOC' flag is comparable with a busy signal and only readable. It is reset (set to '0') by writing into the 'Analog Input Select' register and choosing one of the 5 analog inputs that starts conversion. A CCZ Reset also resets the 'EOC' flag and selects the ADC0 input pin.

# Analog Input Select and Status Register (Address 2A8H):

Bit 7: EOC-flag

(read only)

Bits 2 to 0: Number of analog input pin (0 to 4)

(write only)

# Important:

The ADC hardware must be enabled before the first conversion after RESET can be started, by setting bit 3 of the 'Hardware Control' register (addr. 209H) to '1'. Then it is necessary to wait for 68 oscillator clock cycles before the first conversion can be started, by writing the desired ADC input number into the 'Analog Input Select' register. Any conversion started earlier delivers useless results.

#### **Application Tips:**

The input capacitance of an analog input is about 23 pF. The maximum input current depends on the voltage step at the input capacitance and has to be considered when calculating the signal voltage divider. An external capacity between the ADC pin and GND should have a value of at least 10 nF. V<sub>IA</sub> should be as stable as possible during sample time.

V<sub>SUPA</sub> must not exceed V<sub>SUP</sub>!

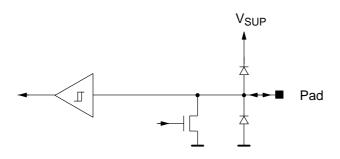

Fig. 2-19: A/D converter input

Fig. 2-20: A/D converter diagram

CCZ 3005K

#### 2.13. Closed Caption Acquisition

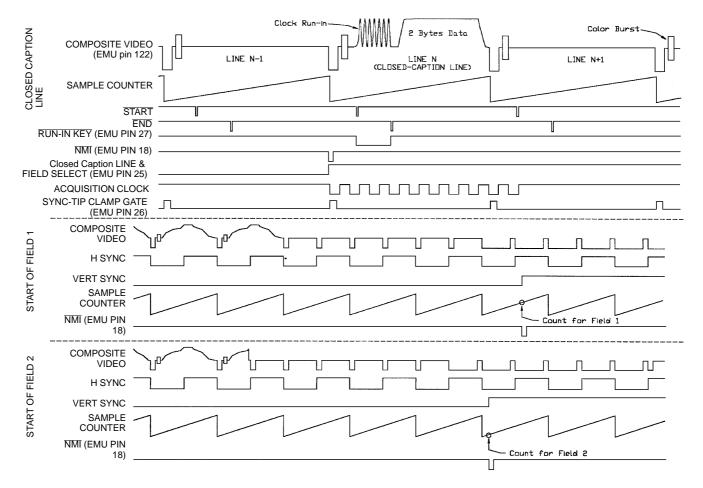

### 2.13.1. Video Input

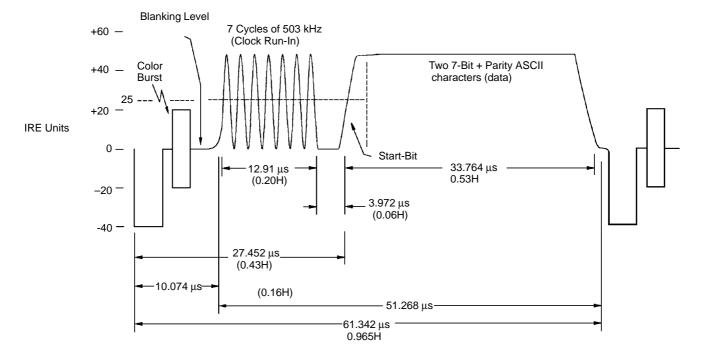

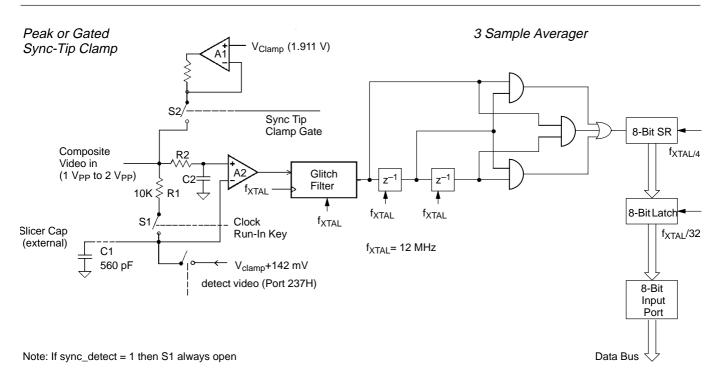

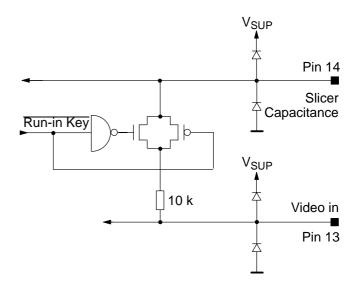

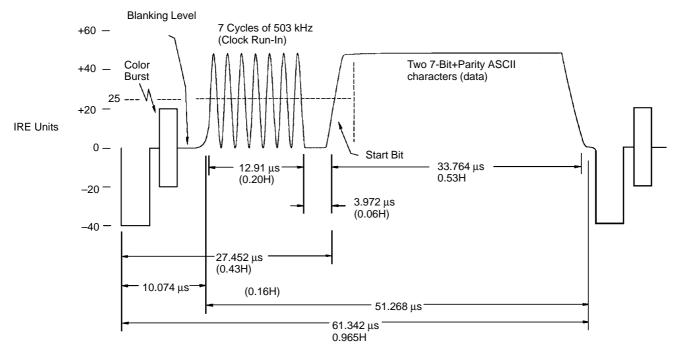

The AC-coupled composite video input signal is applied to the VIDEO IN pin where the negative horizontal sync tip is clamped to a value of 1.911V DC via A1. The gated sync tip clamp circuit is designed to work with a  $0.1 \mu F$ coupling capacitor. The run-in clock of the Closed Caption signal is averaged by R1 and C1. C1 is an external capacitor with a value of 560 pF. The resulting average level is taken as the optimum level for slicing the digital data which follows the run-in clock. It is important for C1 to hold the slicing level for a whole frame (33.2 ms). The best slice level, in terms of common mode range for the chip, is one half of the minimum supply voltage for the CCZ: 4.75V: 2= 2.375V. Since a 1 Vpp video input signal is nominal the clamp level should set the 25 IRE point (data slice level) for the 1 Vpp case to 2.375V. This is done by clamping the sync tips to 1.911 V (2.375 V-0.464 V).

Table 2–5: Video Input Levels, Clamped, in Volts

| Video<br>Signal<br>Input<br>Level<br>[IRE] | Clamp<br>Level at<br>Video<br>Signal<br>Input<br>1.0 V <sub>pp</sub><br>[V] | Clamp<br>Level at<br>Video<br>Signal<br>Input<br>2.0 V <sub>pp</sub><br>[V] | Remarks         |

|--------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|

| 100                                        | 2.911                                                                       | 3.911                                                                       | (white)         |

| 50                                         | 2.554                                                                       | 3.196                                                                       | _               |

| 25                                         | 2.375                                                                       | 2.839                                                                       | (slice)         |

| 7.5                                        | 2.250                                                                       | 2.589                                                                       | (black)         |

| 0                                          | 2.196                                                                       | 2.482                                                                       | (back<br>porch) |

| -40                                        | 1.911                                                                       | 1.911                                                                       | (sync)          |

The data slicer consists of an on-chip low-pass filter and a high-speed comparator. The sliced data passes through a glitch filter which ignores spikes of less than three  $f_{XTAL}$  (12 MHz) periods in duration. The data is then conditioned in a preprocessor stage and transferred to the CPU. The software reads the data from the selected caption line(s) and decodes the caption data further.

Fig. 2-21: Line 21 Field 1 Data Signal Format

Fig. 2-22: Principle of video input for the detection of Closed Caption Data

# 2.13.2. Closed Caption Data Detection

The sliced data are shifted serially into an 8-bit register with the  $f_{XTAL}/4$  as clock signal. The  $f_{XTAL}/32$  latches these 8 bits so that, as byte, they are available for the processor at register 23FH. As every  $f_{XTAL}/32$  period overwrites the previous latched data, the CPU has to read this register fast enough to get all data. The software part doing so could look like this:

| ;Capture data port add capture_data_ EQU \$       |                                               |                    |                                                                     |   |                                              |

|---------------------------------------------------|-----------------------------------------------|--------------------|---------------------------------------------------------------------|---|----------------------------------------------|

| ; variables:<br>capt_buffer_EQU<br>no_of_data_EQU | \$50<br>capt_buffer_+26                       |                    | ytes caption data buffer<br>counter                                 |   |                                              |

| CAPTURE LDX<br>LDA<br>STA<br>CAPTURE LOOP         | #0<br>#26<br>no_of_data_                      |                    | ointer to captured data in RAM ire 26 samples                       |   |                                              |

| LDA<br>STA<br>INX<br>CPX                          | capture_data_<br>capt_buffer_,X<br>no of data | ; store<br>; point | sliced data e it in RAM t to next location in RAM e 26 samples yet? | ; | 4 cycles<br>4 cycles<br>2 cycles<br>3 cycles |

| BNE<br>;                                          | CAPTURE_LOOP                                  |                    | so keep looping                                                     | ; | 3 cycles<br>———<br>16 cycles                 |

It is important to have all variables used here defined in the address space of the zero page, and not to cross a page boundary with the loop, as otherwise the execution time increases. With 16 processor cycles the sliced data scan rate of this sequence is 12 MHz/2/16 = 375 kHz at a crystal frequency of 12 MHz. This is exactly the clock of the 8-bit slice data latch of f<sub>XTAL</sub>/32. Caption data are now in the CCZ memory and have to be decoded. The caption data rate is 503 kHz. The shift rate of the slice data register is  $f_{XTAL}/4 = 12 \text{ MHz}/4 = 3 \text{ MHz}$ . This is almost 6 times the caption data rate of 6\*503 kHz = 3.018 MHz. Thus, in the received bit stream, a bit of the caption data is represented by 6 successive sample bits of the same value (the levels of the clock run-ins represented by 3 bits). As the caption data rate is higher than the scan rate and the phases of both clocks are not synchronized, it may occur that a caption data bit is detected as 5 sample bits only:

clock-drift = (503 kHz- 500 kHz)/500 kHz = 0.6%.

The software to decode the captured data has to consider this item. The decoding of the data can be done by several methods: either by comparing the bit-pattern for the last clock run-ins, the start condition and the data bits, or by searching the start condition first, the last clock run-ins next, and then the data, by checking one or several adjacent bits in the center of the six bit portions. The following example shows what the bit pattern of captured data in the CCZ memory could look like:

### Captured data in memory:

```

capt_buffer_:

FCB 00H, 00H, FEH, E7H, 3DH, 8FH, E3H, 00H

FCB F0H, FFH, C0H, 0FH, 00H, C0H, 0FH, FCH

FCB 00H, 00H, 00H, C0H, FFH, 03H, 00H, 00H

FCB 00H, 00H

```

These data are gathered from the following bit stream (as the reception starts with the least significant bits, the notation starts with them, from left to right):

```

00000000

00000000

01111111

11100111

10111100

11110001

11000111

00000000

00001111

11111111

00000011

11110000

00000000

00000001

11110000

00111111

00000000

00000000

00000000

00000001

1111111

11000000

00000000

00000000

00000000

00000000

00000000

```

## The start-bits begin in the eighth byte:

In the 6th and 7th byte the last clock run-ins may be detected:

# The data start in the 10th byte:

```

00000000 00000000 01111111 11100111

10111100 11110001 11000111 00000000

00001111 11111111 00000011 11110000

< \1'>

< \ 0 ' >

< \ 1 ' >

0000000 00000011 11110000 00111111

<'1'> <'0'>

> <'0'>

< \ 0 ' >

< \1'>

00000000 00000000 00000000 00000011

<'0'> <'0'>

<'0'> < '0' > <'0'><

11111111 11000000 00000000 00000000

11'> <11'>

```

The detected bit stream is:

```

1010001010000011

```

or

1010 0010 1000 0011

without parity bits (odd parity) and with the most significant bits notices on the left side:

## 1000101 1000001

i.e.:

1000101B = 45H = 'E'1000001B = 41H = 'A'

So "EA" is received.

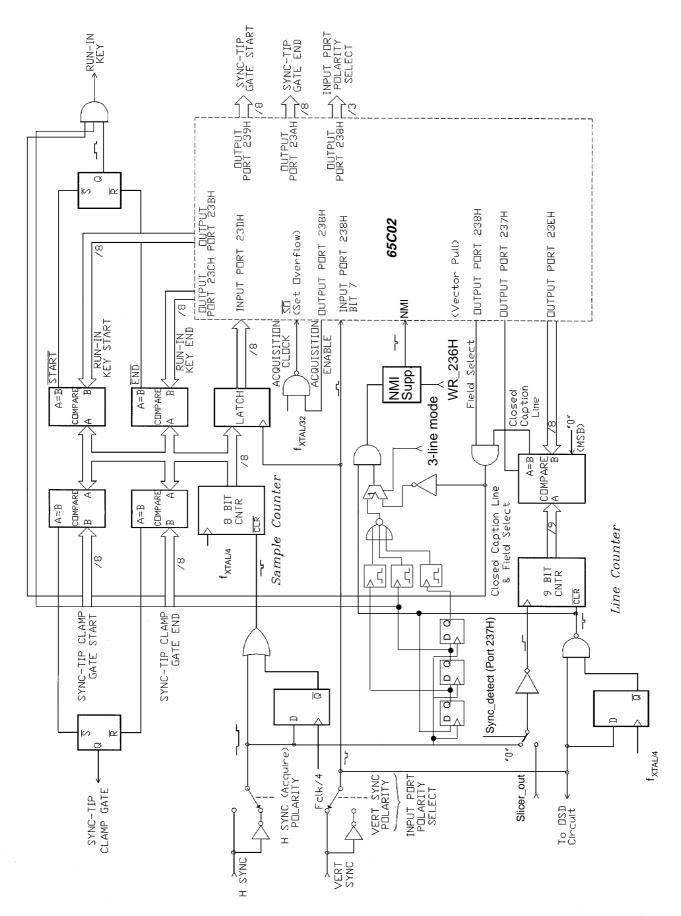

Fig. 2-23: Gate and Window Logic

## 2.13.3. Gate and Window Logic

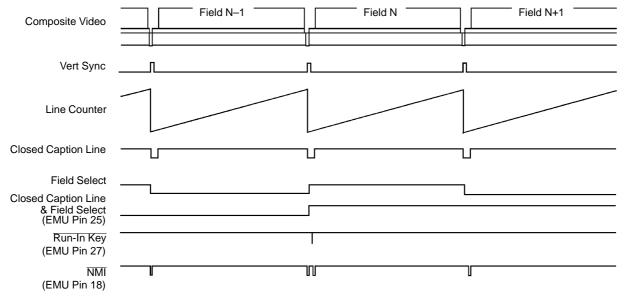

The Gate & Window logic is responsible for keeping track of which video field is present at any given time (odd or even field, also known as "Field 1" or "Field 2"), which video line is present (1 to 262 for NTSC, 1 to 312 for PAL/SECAM) and where we are within the line. By keeping track of these three values the Gate & Window logic is able to produce the Run-in-key pulse, which is used by the front-end hardware to determine the best slicing level and to inform the CPU when it is time to start acquiring data from the closed caption video line. The Gate & Window Logic requires a horizontal sync input in addition to the vertical sync input. The active horizontal and vertical pulse width must be at least 6  $T_{\rm OSC,}$  i.e., with a crystal frequency of 6 MHz, it must be greater than or equal to 1  $\mu s$ .

## Vertical Timing

Every TV video frame is made up of two video fields, an odd field and an even field. The CCZ 3005K must be able to distinguish an odd field from an even field because the telecaption data can appear on either or both fields. The CCZ is able to distinguish between odd and even fields, taking advantage of the fact that there is a half-line offset between fields (since 525 & 625 are odd numbers). The difference is measured and used as a basis for determining which field is which. Note that the position of the Vert Sync and Hor Sync is also a function of the sync processor circuit used to provide Vert and Hor Sync. The phasing of Vert Sync can change from one type of Sync processor to another; but there will always be a measurable difference between the fields. Therefore it is up to the user of the CCZ to determine what phasing is suitable for his particular sync processor.

The Gate & Window logic measures the difference in phasing between Vert Sync and Hor Sync with an 8-bit "Sample" counter ('Vertical Sync Phase Value' register,

addr. 23DH). This counter is clocked at f<sub>XTAI</sub> /4 (3 MHz) and is cleared by the Hsync signal, either derived from the Hsync pin or the COMPOSITE VIDEO, determined with bit 1 in the 'Window Logic Control Register2', (addr. 237H). The active edge of VertSync latches the contents of the counter and generates an interrupt request (NMI). The CPU reads the contents of the latched sample counter and determines whether the new field is odd or even. The logic keeps track of lines with a 9-bit line counter which is clocked each horizontal line and cleared by Vert Sync. The desired closed caption line is provided from a loadable register to a comparator as 8 bits. The 9th bit is hardwired "low", so the closed caption line must be in the first 256 lines of the field. The closed captioning decode is combined with the "Field Select" line to generate an interrupt to the CPU. The Field line select is provided by the CPU since it knows what field it is trying to find data on. The closed captioning decode also enables the Run-in key.

The acquisition clock is enabled by the CPU at the beginning of the acquisition interrupt routine. The program keeps the acquisition clock enabled for a few cycles beyond the closed caption line to ensure that all of the data has been read from the shift register in the front end. The acquisition clock, f<sub>XTAL</sub>/32, is combined with the closed caption line decode. The CPU– $\overline{\text{SO}}$  input is active after RESET.

The CPU needs to know what causes the interrupt (NMI) since the VertSync pulse also generates an NMI. This is accomplished by feeding the Vert Sync pulse directly into a status register. If this bit is high during the interrupt then the CPU assumes this is a Vert Sync interrupt. This leads to the constraint that the Vert Sync signal must remain high for at least one horizontal line period and must be low during the closed caption line. This is normally the case for sync processors anyway. Also, the Vert Sync interrupt routine must be completed before the acquisition interrupt occurs (see Fig. 2–25).

Fig. 2-24: Vertical timing

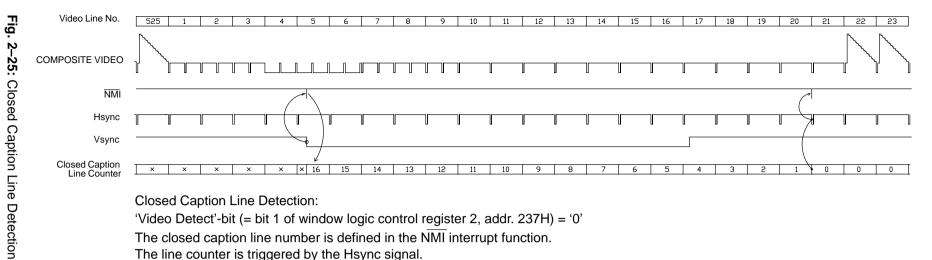

**Closed Caption Line Detection:**

'Video Detect'-bit (= bit 1 of window logic control register 2, addr. 237H) = '0'

The closed caption line number is defined in the NMI interrupt function.

The line counter is triggered by the Hsync signal.

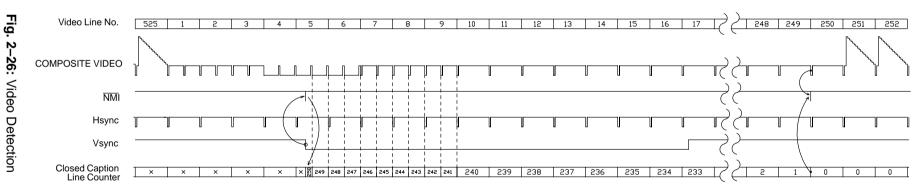

Video Detection:

'Video Detect'-bit (= bit 1 of window logic control register 2, addr. 237H) = '1'

The closed caption line number is defined in the NMI interrupt function.

The line counter is triggered by the Hsync-clamped composite video signal.

### Horizontal Timing

The horizontal timing is based on the Hsync input derived from the Hsync<sub>1</sub>-pin (default) or the Hsync<sub>2</sub> pin (P27 in special mode), defined with bit 3 in the 'Window Logic Control' Register (addr. 237H). The critical horizontal rate job performed by the CCZ's Gate & Window Logic is to generate the run-in key pulse during the telecaption line. The run-in key signal may be measured on pin 27 of the emulator chip. Its start time is programmable in register 23BH, while its stop time is determined in register 23CH. An optimized timing of the run-in key referred to the composite video signal delivering the caption data on pin 122 of the CCZ 3005K emulator chip is given in figure 2–28.

The key pulse is used by the front-end circuit to establish the optimum data slicing level. The key pulse start and stop points along the horizontal line are decoded from the sample counter. The decodes are programmable. The start/stop points are combined with the "Closed Caption Line" signal to form a Run-in key that occurs only during the closed caption line.

Fig. 2-27: Horizontal timing

Fig. 2–28: Optimized Run-In Key and Sync-Tip Clamp

A sync tip clamp gate is also decoded from the sample counter. This gate will start a few counts after the leading edge of Hsync and will end a few counts before the trailing edge of the Hsync portion of the video signal. The start and stop counts are programmable. The sync tip clamp gate signal may be measured on pin 26 of the emulator chip. Its start time is programmable in register 239H, while its stop time is determined in register 23AH. An optimized timing of the sync tip clamp gate referred to the composite video signal delivering the caption data on pin 122 is given in figure 2–28. The sync tip clamp gate is used by the front-end circuit to clamp the incoming video to a known reference level.

# 3-line mode

The use of certain video sources (for example VCRs) may cause problems in finding the caption lines (Time Base Jitter). However, owing to the 3-line-mode the wandering of the caption line can be noticed without loosing data. In the 3-line mode 3 consecutive lines are sampled and saved in a RAM-buffer via software. Normally the data line lies in the middle, that is, the second recorded line. In this line only the Run-in key control signal is generated. If the software cannot detect any caption data there, the line before and the line after are searched for data. If data is to be found there, it is decoded as usual. Also, the software corrects the caption counter ((23EH) so that the caption line lies in the middle of the three lines again. Thus the caption decoder can follow the deviations of the caption line. Naturally this method uses up more RAM space and, in that case, more computing power.

# Video-detect mode (see Fig. 2-26)

For Fade and Mute it is necessary for the software to recognize the presence of a video signal. The hardware of the caption decoder can achieve this.

The interrupt service routine for data capture can define a line by writing its number into the caption line register

(23EH), and setting the window logic control unit to "video detect mode" by programming bit 1 = '1' of the window logic control register (237H). The processor will receive an interrupt (NMI) at the occurrence of the specified line. The time delayed up to this interrupt is given by evaluating the system counter word in registers 203H and 204H. If no line interrupt occurs, the detection of the next  $V_{\rm SYNC}$  that is not derived from the video signal indicates the non-existing video signal. If the time up to the occurrence of the line-interrupt is too short, this also means that no stable video signal is available. To detect the correct sync-level on the VIDEO\_{IN} pin a low-pass filter to ignore the color burst should be applied. The video detection circuitry is designed for an input signal of 1  $V_{\rm pp}$ .

| Software In   | terface                                      |                                              |  |

|---------------|----------------------------------------------|----------------------------------------------|--|

| Address       | Function                                     |                                              |  |

| 237H(w)       | Window logic control                         |                                              |  |

| ` ,           | bit 3                                        | H <sub>sync</sub> select:                    |  |

|               |                                              | '0' = H <sub>SYNC1</sub> -pin                |  |

|               |                                              | '1 '= H <sub>SYNC2</sub> -pin                |  |

|               | bit 2,                                       | '1'= gated clamp                             |  |

|               | on z,                                        | '0'= peak clamp                              |  |

|               | bit 1,                                       | '1'= video det. mode                         |  |

|               | Dit 1,                                       | (sync detect)                                |  |

|               | hit O                                        |                                              |  |

| 220H/r/w/     | bit 0, '1'= 3-line mode Window logic control |                                              |  |

| 238H(r/w)     |                                              |                                              |  |

|               | bit 7                                        | level Vsync pin (read only) line counter NMI |  |

|               | bit 6                                        |                                              |  |

|               |                                              | '0'= disabled                                |  |

|               | L 10 E                                       | '1'= enabled                                 |  |

|               | bit 5                                        | '1'= CPU-SO input enabled                    |  |

|               | bit 4                                        | '1'= half-dot rounding on                    |  |

|               | bit 3                                        | OSD active (read only)                       |  |

|               | bit 2                                        | active edge of V <sub>SYNC</sub> :           |  |

|               |                                              | '0': rising, '1': falling                    |  |

|               | bit 1                                        | active edge of Hsync for ac-                 |  |

|               |                                              | quisition:                                   |  |

|               |                                              | '0': rising, '1': falling                    |  |

|               | bit 0                                        | active edge of Hsync for                     |  |

|               |                                              | OSD:                                         |  |

|               |                                              | '1': rising, '0': falling                    |  |

| 239H(r/w)     | Sync Tip C                                   |                                              |  |

|               | bit 7 to 0 st                                | art pos.                                     |  |

|               |                                              | pos.*4/ fxtal                                |  |

| 23AH(r/w)     | Sync Tip C                                   | lamp End                                     |  |

| , ,           | bit 70 end                                   |                                              |  |

|               |                                              | oos.*4/ fxtal                                |  |

| 23BH(r/w)     | Run In Key                                   |                                              |  |

| , ,           | bit 7 to 0 s                                 |                                              |  |

|               |                                              | pos.*4/ fxtal                                |  |

| 23CH(r/w)     | Run In Key                                   |                                              |  |

|               | bit 7 to 0 er                                |                                              |  |

|               |                                              | oos.*4/ fxtal                                |  |

| 23DH(r/w)     |                                              | c Phase (odd/even field detect)              |  |

| 23EH(r/w)     | Caption Lin                                  |                                              |  |

| _OLI I(I/ W/) |                                              | bled before this register is                 |  |

|               |                                              | he first time                                |  |

| 23FH(r)       | Captured D                                   |                                              |  |

| 23111(1)      | Capitiled L                                  | vala                                         |  |

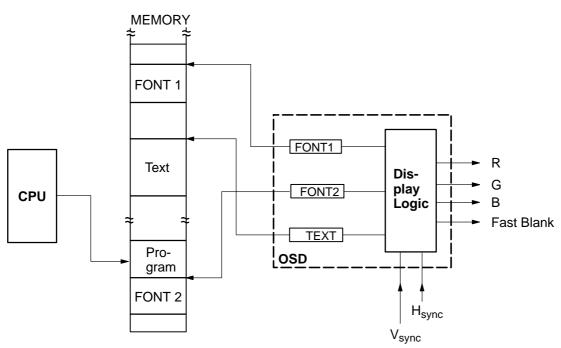

## 2.14. OSD

A powerful on-screen display (OSD) is provided on the CCZ 3005K. Many novel approaches were made to save chip area. The most important area saving technique was to eliminate the redundant storage of displayed data. Traditional display devices transfer fixed text data (such as prompts, menus, graphics etc.) from program ROM to the display RAM. The CCZ's OSD, however, is able to display text directly from program ROM. Additionally, the character font table may be located in the program ROM. This offers the ability to size the table exactly as required. Furthermore, specific characters and symbols can be defined. A second character font may be defined in unused portions of RAM which would allow you to create characters "on-the-fly".

The ability of the OSD hardware to access font and display data directly from program ROM was facilitated by incorporating direct memory access (DMA) hardware on chip. A minor slow-down of the processor occurs when the DMA hardware is active. The slow-down of the processor is related to how many characters are on screen and how many color changes occur from character to character.

# 2.14.1. Summary of OSD Features

- 2 character sizes: 13 H x 8 W or 15 H x 8 W

- soft-scroll

- unlimited numbers of fonts, with any two active at a time

- attributes: flash, italics, transparent, underline

- 8 foreground and 8 background colors

- color palette (8 of 64 colors)

- line-locked display clock

- second color for one text line definable

- very effective for pull-down structures

- half-dot rounding

# 2.14.2. Fonts

Two different fonts may be defined: one in ROM and one in RAM. The RAM font can be changed by software. This makes it easy to provide foreign language character sets. The basic character set, which is common to all Latin-based languages, for example, can be programmed in the ROM font, containing all characters in the range from ASCII 32 to 127 – i.e., the "printable" ASCII characters. The extensions of the character set that are specific to a language may be contained in the RAM font. These characters can be accessed with offsets to the ROM font or by translating unique ASCII characters with a table.

### 2.14.3. OSD Window

Start positions of the display are determined and changed (moved) by setting just two register values: Y\_Start and X\_Start. There is no restriction on text and window size.

Fig. 2-29: Pointer Model OSD

#### 2.14.4. Colors

# 2.14.4.1. OSD Attribute 'COLOR'

'COLOR' is a control byte that prefixes the data stream for the OSD. It resides anywhere in the CCZ memory, in ROM or RAM.

# Example:

FDB COLOR ; define color

FCC "String" ; display 'String'

The byte 'COLOR' defines the foreground and background color of the characters that follow, until the next 'COLOR' attribute is encountered.

### OSD attribute 'COLOR':

bits 0 to 2: value 0 to 7 defining foreground color

(color 0 to color 7)

bits 3 to 5: value 0 to 7 defining background color

(color 0 to color 7)

bit 6: '0' or '1', if '1': color 0 is replaced by

transparent

bit 7: '1': marks color attribute. All other data

(characters) have bit 7 = 0.

# 2.14.4.1.1. Attribute 'Transparent'

If OSD attribute 'COLOR' bit 6 = '1' and background color = '000' but the foreground color is different from '000', the (foreground) character(s) that follow are displayed on a transparent background, i.e., the video source signal is visible instead of the background color. Also the foreground color 0 becomes transparent with OSD attribute 'COLOR' bit 6 = '1'.

#### 2.14.4.2. Available Colors

The CCZ 3005K has 8 programmable colors. These colors are selectable out of a palette of 64 different values. Each color consists of the 3 components red, green and blue. Each of these components has 1 out of 4 different intensities.

For example, the eight colors could be programmed to be compatible to those of the CCU 3005 C and CCU 3005 D.

Color 0 = black

Color 1 = blue

Color 2 = green

Color 3 = green/blue = cyan

Color 4 = red

Color 5 = red/blue = magenta Color 6 = red/green = yellow

Color 7 = white

Table 2–6: Color component intensity values

| Intensity | MSB | LSB |

|-----------|-----|-----|

| Off       | 0   | 0   |

| 1/3       | 0   | 1   |

| 2/3       | 1   | 0   |

| Maximum   | 1   | 1   |

With 4 different intensity values of 3 different colors,  $4 \cdot 4 \cdot 4 = 64$  different colors are possible.

Table 2-7: Color palette register

| R<br>(267H) | G<br>(268H) | B<br>(269H) | Address<br>(Color) | Reset Value               |

|-------------|-------------|-------------|--------------------|---------------------------|

| 0           | 0           | 0           | 0                  | Red=Green=Blue=00         |

| 0           | 0           | 1           | 1                  | Red=Green=00; Blue=11     |

| 0           | 1           | 0           | 2                  | Red=00; Green=11; Blue=00 |

| 0           | 1           | 1           | 3                  | Red=00; Green=Blue=11     |

| 1           | 0           | 0           | 4                  | Red=11; Green=Blue=00     |

| 1           | 0           | 1           | 5                  | Red=11; Green=00; Blue=11 |

| 1           | 1           | 0           | 6                  | Red=Green=11; Blue=00     |

| 1           | 1           | 1           | 7                  | Red=Green=Blue=11         |

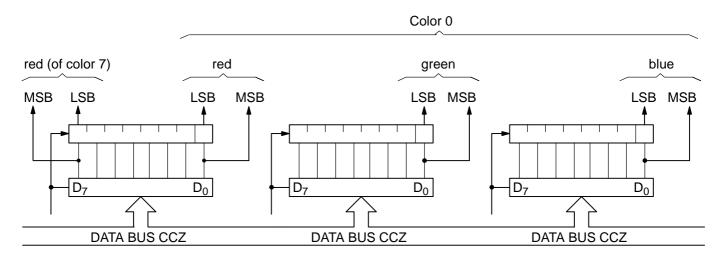

## 2.14.4.3. Color Palette Programming

6 register write accesses are necessary for the 3 palette registers to define the 8 possible colors. To program the 16 bits of each of these 3 registers, every register has to be accessed twice. The first write access programs the least significant 8 bits, and the second write access programs the most significant 8 bits. Each of the 8 programmable colors is defined by three 2-bit intensity values: 2 bits for the red component, 2 bits for green and 2 bits for blue. All least significant bits of these 2 bit values form the first byte to be written (low byte), all MSBs form the second byte (high byte). The bits at location 0 of the low and high byte correspond to color 0, bits at location 1 to color 1, bits at location 2 to color 2, ... and bits at location 7 to color 7.

Example: To get color 0 as light grey, choose 1/3 intensity for each component:

```

1/3 red = 01

1/3 green = 01

1/3 blue = 01

```

It is not possible to program a single color on its own, thus all 8 selectable colors have to be programmed together. The other 7 color values have to be defined before ('x' is used instead of any '0' or '1' defining the other colors 1 to 7 in this example).

The programming looks as follows:

The value for 1/3 intensity red = '01'. The least significant bit of this value becomes bit 0 (for color 0) of color palette register red, low byte:

```

LDA #%xxxxxxx1

STA color_palette_register_red

```

The most significant bit of intensity red becomes bit 0 (for color 0) of color palette register red, high byte:

```

LDA #%xxxxxxx0

STA color_palette_register_red

```

Intensity green = '01', least significant bit becomes bit 0, green, low byte:

```

LDA #%xxxxxxx1

STA color_palette_register_green

```

The most significant bit becomes bit 0, green, high byte:

```

LDA #%xxxxxxx0

STA color_palette_register_green

```

The same procedure applies to blue:

```

LDA #%xxxxxxx1 ;the '1' of '01'

STA color_palette_register_blue

LDA #%xxxxxxx0 ;the '0' of '01'

STA color_palette_register_blue

```

A reset changes the color palette to the corresponding colors of the CCU 3005 C and CCU 3005 D (see palette register description in chapter 'Registers').

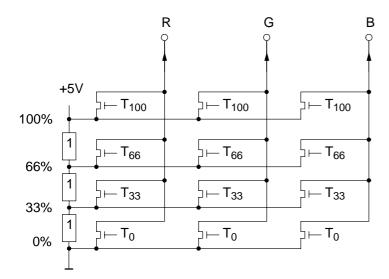

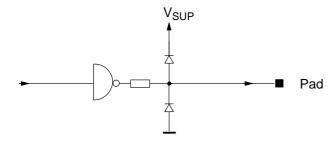

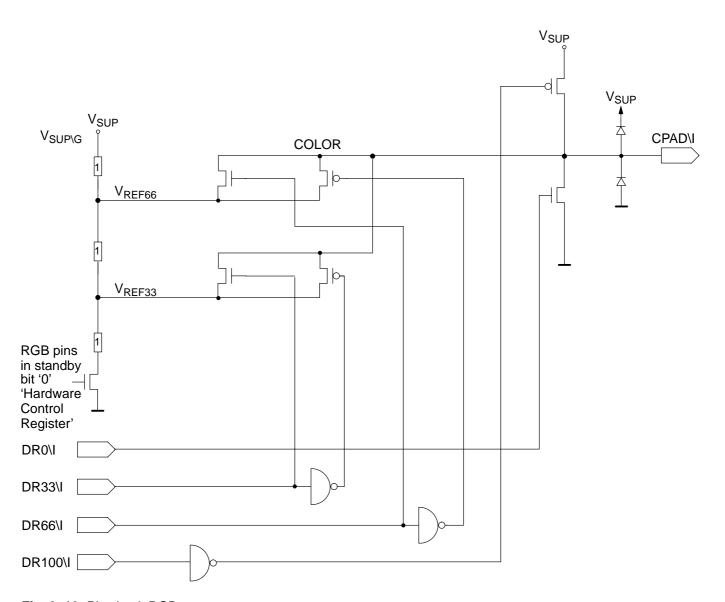

# 2.14.4.4. Color Palette Hardware

A common resistor network is used for the generation of the different intensity levels. The output impedance is maximum 2 kOhms. The following diagram shows the working principle. The color palette controls the 12 transistors of the RGB intensity matrix. Only one transistor per output is active at a time.

Fig. 2-30: Color map, 3 x 2 bytes

CCZ 3005K

| Half-Video<br>Level | FB <sup>1)</sup> | RGB Level | at V <sub>SUP</sub> = 4.75V | at V <sub>SUP</sub> = 5V | at V <sub>SUP</sub> = 5.25V |

|---------------------|------------------|-----------|-----------------------------|--------------------------|-----------------------------|

| '1'                 | off              | 0 %       | 0V                          | 0V                       | 0V                          |

| '0'                 | off              | 0 %       | 0V                          | 0V                       | 0V                          |

| '0'                 | on               | 0 %       | 0V                          | 0V                       | 0V                          |

| '0'                 | on               | 33 %      | 1,58V                       | 1,66V                    | 1,75V                       |

| '0'                 | on               | 66 %      | 3,16V                       | 3,33V                    | 3,5V                        |

| '0'                 | on               | 100 %     | 4,75V                       | 5V                       | 5,25V                       |

<sup>1)</sup> The active level of the Fast Blank output is programmable with bit 7 of the 'OSD Separate Color Definition Register' (addr. 266H).

# 2.14.5. Fast Blank Output

The 'Fast Blank' output is active during any OSD activities, i.e.,: the display hardware controlled by the 'Fast Blank' must only evaluate the CCZ RGB outputs with 'Fast Blank' = active. The polarity of the 'Fast Blank' is programmable ('0' or '1' active).

# 2.14.6. Half-Video Output

The OSD generates a 'Half-Video' output signal to control external hardware and subdue the video signal. This effects better readability of the OSD, in particular if the video signal's color and contrast are similar to the OSD signal's. The 'Half-Video' is active instead of 'color 1', no matter whether this color 1 is the background or foreground color. Whatever the value of color 1 is defined to be (palette values), the 'Half-Video' output becomes '1'-level and the RGB outputs become inactive ('0'-level). The 'Half-Video' output can be switched off (set to '0' throughout) by setting bit 0 of the 'OSD Half-Video Control' register to '1'. After reset, this bit is cleared ('0') and the Half-Video Output is active.

Fig. 2-31: Principle of color palette

PRELIMINARY DATA SHEET CCZ 3005K

## 2.14.7. Using OSD

The OSD is organized to display character streams (strings), i.e., data streams in the memory are interpreted as OSD attributes or display characters. Via font data the display characters are converted into display pixels. A number of registers offer a convenient method of telling the OSD 'where' and 'what' shall be displayed. As only 8 bits can be handled at a time, parameters with more than 8 bits in size require multiple writes to the same register, with the MSByte written first. The (unused) high bits of such registers should be set to '1'.<sup>1)</sup> So, for example, to program 12CH as 'Last Active scan line', an "FFH" would first be written into address 261H and then a "2CH".

To avoid a flickering display, writing to the OSD register should occur synchronized with the vertical synchronization signal.

The active horizontal and vertical pulse width must be at least 6  $T_{OSC,}$  i.e., with a crystal frequency of 6 MHz, it must be greater than or equal to 1  $\mu$ s.

<sup>1)</sup> Disturbing effects caused by internal compare evaluations may appear if unused high bits of values with more than 8 bits are set to '0', and these values are programmed without being synchronized to the horizontal synchronization signal.

Explanation of register functions:

| 238H(r/w) | ) Window Logic Control Register 1: |                              |  |

|-----------|------------------------------------|------------------------------|--|

| ` ,       | bit 7                              | level Vsync pin (read only)  |  |

|           | bit 6                              | line counter NMI             |  |

|           |                                    | '0'= disabled                |  |

|           |                                    | '1'= enabled                 |  |

|           | bit 5                              | '1'= CPU-SO input enabled    |  |

|           | bit 4                              | '1'= halfdot rounding *) on  |  |

|           | bit 3                              | OSD active **) (read only)   |  |

|           | bit 2                              | active edge of Vsync:        |  |

|           |                                    | '0': rising, '1': falling    |  |

|           | bit 1                              | active edge of Hsync for ac- |  |

|           |                                    | quisition:                   |  |

|           |                                    | '0': rising, '1': falling    |  |

|           | bit 0                              | active edge of Hsync for     |  |

|           |                                    | OSD:                         |  |

|           |                                    | '1': rising, '0': falling    |  |

- \*) Halfdot rounding is not defined for Horizontal Start position (Reg. 0262H) less than 6 and greater than 46.

- \*\*) The OSD active bit is set to '0' at the beginning of the 'First Active Scan Line'. It is set to '1' either after the access to the last scan line of the active display part, de-

fined in 'Last Active Scan Line', or after the access to the TEXT-END character.

260H(w) 'OSD First Active Scan Line'

9 bits:

Specifies the Start Scan Line of the OSD

window.

261H(w) 'OSD Last Active Scan Line'

9 bits:

Determines the last Scan Line of the OSD

window to be displayed.

Note that it is

possible to set this value to a number that causes the last character lines to be "cut off". This is a desirable feature when smooth scrolling is in operation.

262H(w) 'OSD Horizontal Start Position'

6 bits:

Determines horizontal start position of the

OSD window in character steps.

(must be greater than 1!).

Don't use values less than 6 or greater than 46 if 'Halfdot Rounding' is enabled ('Halfdot Rounding' is enabled if bit 4 in register 0238H = 'Window Logic

Control Register 1' is set to '1').

The size of one horizontal character step is 8 pixels. (Fine adjust in pixels is possible with 'OSD Horizontal Start Fine Adjust',

address 26FH).

Remark: The horizontal stop position of the OSD

window is determined in the OSD data

stream with the attribute

'CR' (= 0DH) or 'END' (= 0CH).

263H(w) 'OSD Control Register', 8 bits:

bit 7 '1' = caption mode

'0' = OSD mode

must be set to '1' for

caption data.

bit 6 '1' = display active

bit 5 '1' = flash off '0' = flash on

all characters between the attributes 'FLASH ON' and 'FLASH OFF' are displayed only

if this bit is set to '0' bit 4 '1' = 13x8 font

'0' = 15x8 font

bit 3..0 first active character Scan Line:

determines the start scan line of

the first character row of the OSD

window. This ability allows the

smooth scrolling feature to look

correct at the top of the window.

CCZ 3005K

Remark:

264H(w) 'OSD Text Start Address Register', 16 bits:

Points to the first character of an OSD data stream. All subsequent characters are encountered until either the OSD attribute 'END' or the 'Vertical Stop Position' determined in the specific register

(address 261H) limits the OSD window. The horizontal expansion of the OSD

window is determined in character rows which are terminated with 'CR' (=0DH).

265H(w) 'OSD Separate Colored Line', 9 bits: Start scan line value for a single character

line to be displayed with a separate color.

Color attributes as part of the OSD

data stream (display string) have no effects

on the one character high scan lines

selected by this register. The color is defined in the

'Separate Color Definition Register'.

Thus an entire character line may be highlighted by simply writing its start scan line into this register. This highlighted character line may overlap the boundary of two

neighbored ordinary character lines. Thus it can be soft-scrolled through the OSD

window.

266H(w) 'OSD Separate Color Definition Register' and two more control bits, 8 bits:

bit 7: fast blank output level:

'1'= active high

'0'= active low

bit 6: '1'= replace black by transparent

'0'= don't replace black by

transparent

separate color definition:

bits 5 to 3: background color

(color no. 0 to 7)

bits 2 to 0: foreground color

(color no. 0 to 7)

26AH(w) 'OSD Half-Video Control Register':

bit 0: '0'= disable half-video (default after RESET), half-video output pin

NESET), Hall-video odipui j

level='0'

'1'=enable half-video

26EH(w) 'OSD Font 1, Font 2, Start Addresses',

32 bits: write in the order

MSB font1 (first access)

LSB font 1 MSB font 2

LSB font 2 (last access)

Two pointers to the start of character fonts. Font 1 displays all characters in the range of 0 to 15H, and Font 2 displays all characters in the range

between 20H to 7FH. The OSD assumes the address of the first character (= 00H) as

font pointer.

26FH(w) 'OSD Horizontal Start Fine Adjust and

Display Modes':

bit 7 '1'= horizontal shadow active

bit 6 '1'= blank display bits 5..3 not used, set to '0'

bits 2..0 horizontal start fine adjust

#### 2.14.8. OSD Attributes

The OSD receives control information from attribute bytes which are part of the OSD data stream. They reside in the CCZ memory (RAM or ROM) together with the text characters to be displayed.

80H to FFH: 'COLOR'

bit 7 '1'= color code (to distinguish this attribute from ASCII or

control codes). bit 6 '1'= color 0 replaced by transparent

bit 5,4,3= background color (color no. 0 to 7)

bit 2,1,0= foreground color (color no. 0 to 7)

01H: 'UNDERLINE ON'

All subsequent characters

are underlined until the OSD attribute 'UNDERLINE\_OFF' or 'END' is

encountered

02H: 'UNDERLINE OFF'

See 'UNDERLINE\_ON'.

03H: 'FLASH ON'

> The following characters up to the attribute 'FLASH\_OFF' or 'END' are displayed only if the 'FLASH' bit in the 'OSD Control Register' is set to '0' (= bit 5, addr. 263H). The flashing occurs only when the flash bit is toggled. This could be done in the interrupt timer function, for example.

04H: 'FLASH OFF'

See 'FLASH ON'.

05H: 'ITALICS ON'

> All subsequent characters are displayed in italics format

until the OSD attribute 'ITALICS\_OFF' or

'END'is encountered.

06H: 'ITALICS OFF'

See 'ITALICS ON'.

07H: 'TRANSPARENT'

For this character space the underlying

video image is shown.

(in standard OSD mode only) 08H:

> 'DOUBLE\_UNDERLINE\_ON' like 'UNDERLINE\_ON' (01H) but

the last two character scan lines are used

instead of only the last one.

'UNDERLINE\_OFF' (02H) or 'END' turns

this mode off again.

09H: (in standard OSD mode only)

FONT 1 AND 2

automatic change of FONT\_pointers

depending on ASCII-value

(default mode, initialized by RESET and

the active V<sub>SYNC</sub> edge)

OAH: (in standard OSD mode only)

> 'FONT 1 ONLY' OSD uses only FONT\_1

0BH: (in standard OSD mode only)

'FONT\_2\_ONLY'

OSD uses only FONT 2

0CH: 'END'

End of the OSD. Your text must end with this code.

ODH: 'CR'

> Carriage return. The following characters are displayed in the next text line.

The OSD insertion must be terminated with CR (0DH) or

END (0CH) before the next Hsync!

Micronas

31

CCZ 3005K

#### 2.14.9. Font Definition

The OSD has no separate character generator, but the definitions of the characters reside in ROM and/or RAM of the CCZ. Each character is defined by 16 bytes. One byte corresponds to the pixels in the scan line on the screen, the MSB being the first (leftmost) output. The following 15 addresses contain the pixel information for the remaining scan lines of the character. Three bytes for the 13x8 characters and one byte for the 15x8 characters are left unused. For example, the definition of the letter "A" in the 13x8 matrix could look as follows:

|      | bit | 76543210                 |      |

|------|-----|--------------------------|------|

| n    |     |                          | =00H |

| n+1  |     | <b>x</b>                 | =10H |

| n+2  |     | x-x                      | =28H |

| n+3  |     | x-x                      | =28H |

| n+4  |     | - x x                    | =44H |

| n+5  |     | - x x                    | =44H |

| n+6  |     | x x -                    | =82H |

| n+7  |     | x x x x x x x -          | =FEH |

| n+8  |     | x x -                    | =82H |

| n+9  |     | x x -                    | =82H |

| n+10 |     | $\mathbf{x}\mathbf{x} -$ | =82H |

| n+11 |     |                          | =00H |

| n+12 |     |                          | =00H |

| n+13 |     | 0000000                  | =00H |

| n+14 |     | 0000000                  | =00H |

| n+15 |     | 0000000                  | =00H |

OSD insertion must be terminated with 'CR' (0DH) or 'END' (0CH) before the next Hsync!

The addressing of the pixel pattern to be displayed is given by:

address= font pointer+ASCII\*16+scan line

with scan line= 0...12

If the font table does not start with the ASCII character 00H, the font pointer has to be programmed with the corresponding offset. If, for example, the font table starts with the letter "A" (ASCII 65) at address "n", the the following value results for the font pointer:

font pointer = n-(65\*16)

This assumes, of course, that the ASCII representation is used. Font pointer 1 is used to access ASCII characters 00H..1FH, Font pointer 2 is used to access ASCII characters 20H...7FH. A single continuous font table results when font pointer 1 and font pointer 2 are set to the same address.

### 2.14.10. Soft-Scroll

To produce soft-scroll, the software regularly changes the start-scan line of the display (263H, bits 3 to 0). The display of the text line designated by the text pointer starts with this scan line. When the value reaches the last scan line, the text pointer is set to the beginning of the next text line and to the start scan line. Thus the text slowly seems to move upwards. The lower edge is defined by the parameter Y\_END. The scroll speed and the direction are determined by how fast the software increments (or decrements) the start scan line register.

To avoid flickering, the change should be effected during the Vsync Interrupt routine.

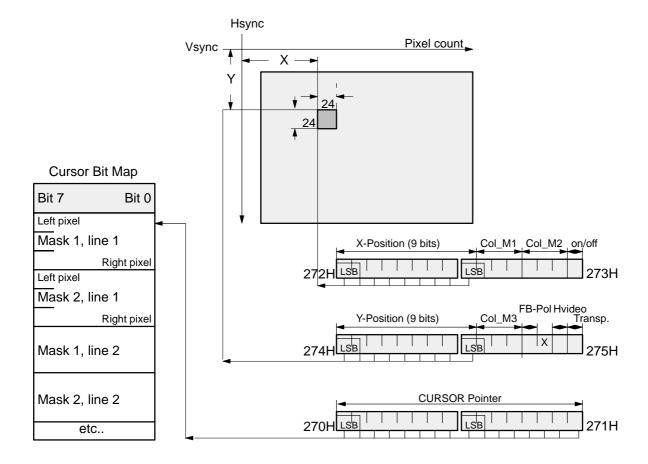

#### 2.15. Cursor

A cursor can be displayed independently from the OSD output . This cursor is always displayed at the top. It can be of any shape within a field of 24×24 pixels. The logic needs a pointer to a cursor definition bit map. This bit map must be defined somewhere in the CPU address space. The other control registers define the three selected colors, the position of the upper left corner, the fast blank polarity and the half-video or transparent mode. There can be multiple cursor bit maps in memory. Changing the cursor shape just needs a new cursor pointer content.

#### 2.15.1. Cursor Definition

Two masks of 24×24 pixels define the shape. This gives 2 bits per pixel for color definition. If both mask-bits of a cursor pixel are zero, the background (OSD or video) is displayed instead of a cursor pixel. Every other mask-bit combination (01b, 10b and 11b) has a 3-bit color definition register (Col\_M1 to Col\_M3). The content of the selected register will be used as address for the color palette.

| Mask 1<br>Pixel | Mask 2<br>Pixel | Dis-<br>played<br>Color | Spec.<br>Mode               |

|-----------------|-----------------|-------------------------|-----------------------------|

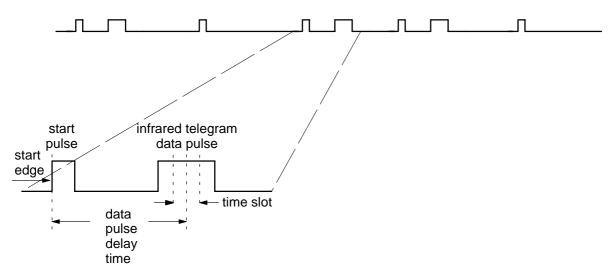

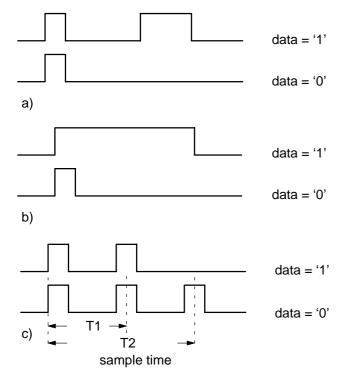

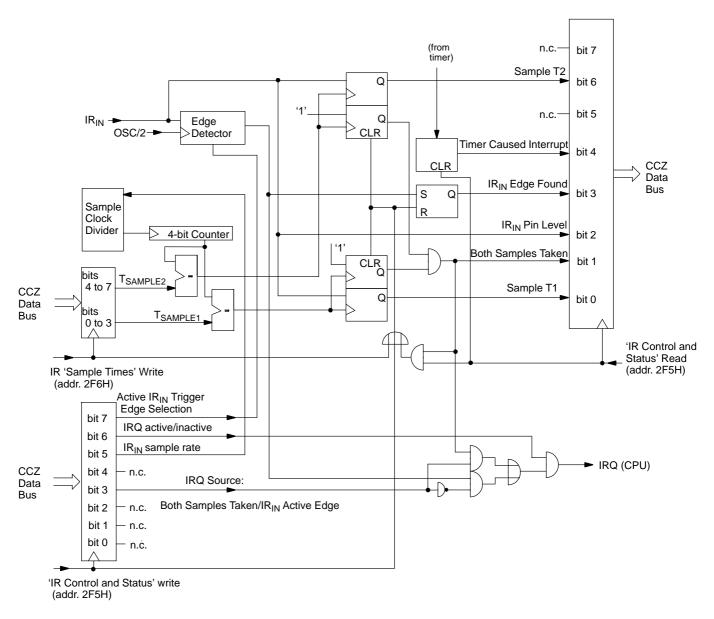

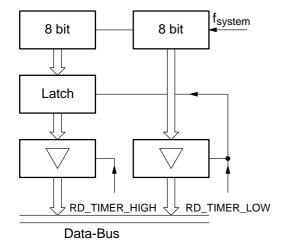

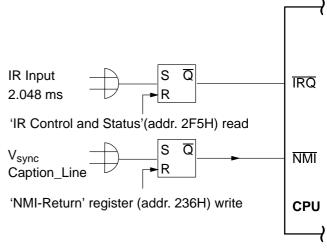

| 0               | 0               | back-<br>ground         |                             |