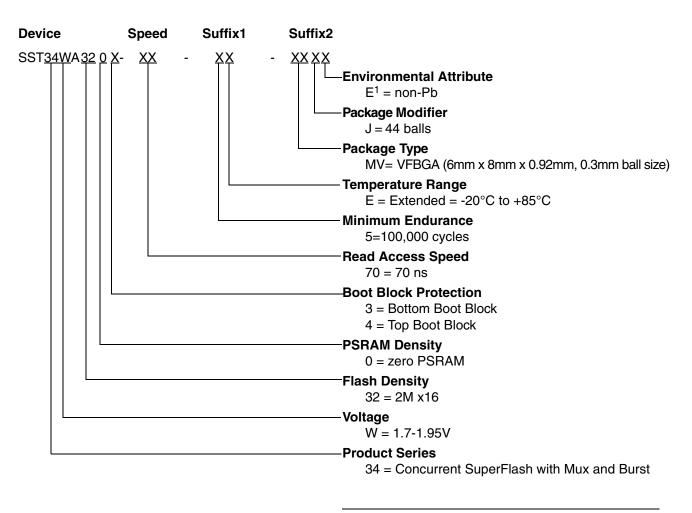

**Preliminary Specification**

#### **FEATURES:**

- Organized as 2M x 16

- Single Voltage Read and Write Operations

- V<sub>DD</sub> = 1.7V 1.95V for Program, Erase and Read

- Top or Bottom Boot Block Protection

- Bottom Boot Protection SST34WA3203

- Top Boot Protection SST34WA3204

- Multiplexed Data and Address for reduced I/O count

- A<sub>15</sub>–A<sub>0</sub> multiplexed as DQ<sub>15</sub>–DQ<sub>0</sub>

- Addresses are latched by AVD# control input when BEF# is low

- Low Power Consumption (Typical)

- Standby Current: 4µA

- Auto Low Power Mode: 4 μA

- Flexible Memory Organization

- 4 Banks (512 KW)

- 63 Uniform 32 KWord blocks

- Uniform Sectors (2KWord) for entire memory array

- Concurrent Memory Operation

- Read While Program (RWP)

- Read While Erase (RWE)

- Erase-Suspend/Erase-Resume Capability

- Read while Erase-Suspend

- Program while Erase-Suspend

- Read while Program during Erase-Suspend

#### Synchronous Burst Mode Read (54 MHz/66 MHz)

- Continuous, Sequential Linear Burst

- 8/16/32-words with Wrap-Around Burst

- 8/16/32-words without Wrap-Around Burst

- Burst Access Time: 13.5 ns/11.5 ns

- Asynchronous Random Address Access: 70 ns

- Industry Standard CFI interface compatible

- Fast Program and Erase (Typical)

- Word Program Time: 10 μs

- Sector/Block Erase Time: 15 ms

- Chip Erase Time: 30 ms

- Expanded Block Locking

- All blocks locked at Power-up

- Any block can be locked/unlocked by software

- Flash Security ID

- 128-bit unique ID factory preset

- 128-word non-erasable, lockable User-programmed ID bits ("OTP-like")

- End-of-Write Detection

- Data# Polling

- Toggle bit

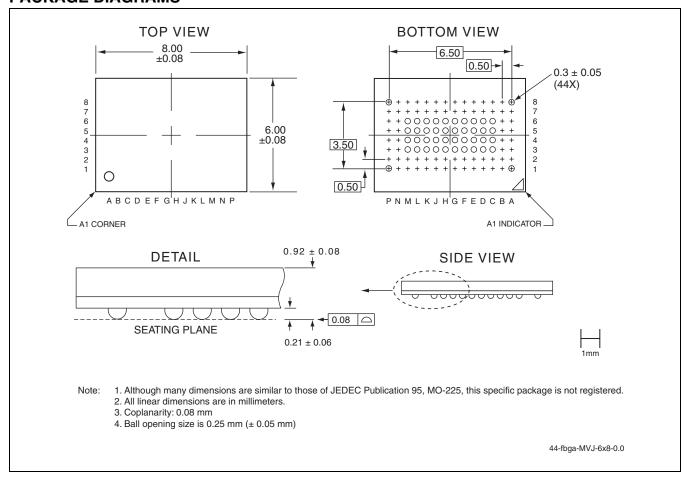

- Packages Available

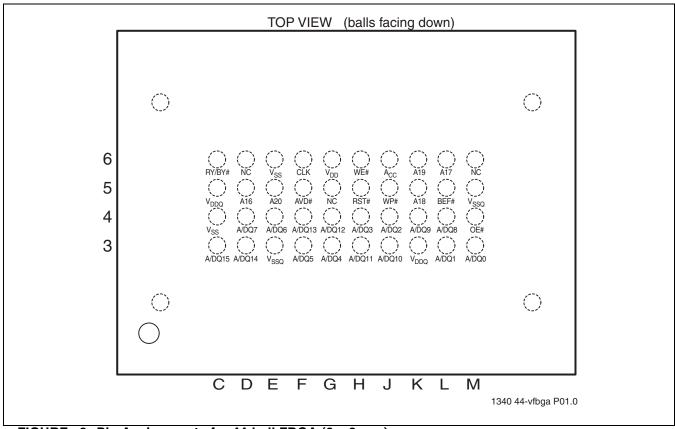

- 44-ball VFBGA (6 x 8mm)

- Superior Reliability

- Endurance per sector: 1,000,000 cycles (typical)

- Greater than 100 years Data Retention

- All non-Pb (lead-free) devices are RoHS compliant

#### PRODUCT DESCRIPTION

The SST34WA3203 and SST34WA3204 are 32 Mbit (2 Mbit x16) Flash memory devices with Burst Mode data access that utilize a single 1.8 V supply. When super voltage VH (11.4V to 12V) is applied to the ACC pin, eight word programming is enabled for faster manufacturing-environment programming.

The devices feature a 512 KWord uniform multi-bank architecture that consists of four banks. The boot block, either the top or bottom block, consists of 15 standard 32 KWord blocks and four parameter 8 KWord blocks for added granularity. The remaining two banks each contain uniform 32 KWord blocks. Each 32 KWord block is further divided into sixteen uniform 2 KWord sectors. Blocks and sectors are individually erasable for increased flexibility. Any bank can be read while another bank is being erased or programmed, with zero latency.

The SST34WA3203/3204 support an Erase-Suspend mode during which data can be programmed to, or read from, any sector or block that is not being erased.

SST34WA3203/3204 support synchronous Burst mode Read from any address location of the memory array. The Burst mode allows sequential data set reading with significantly shorter latency delays than during a random read, including 8-, 16-, 32-words or continuous or without wrap-around.

The devices offer an expanded Block Locking scheme for data protection against any writes. Each block can be individually locked. Additionally, the top or bottom 8 KWord parameter blocks can be individually locked for finer granularity of the top or bottom boot blocks.

A 136-words Security ID, included on the devices, increases system design security. The Security ID is divided into two segments: an 8-word, 128-bit segment factory programmed with a SST Unique ID, and a 128-word segment that can be programmed and locked by the user. When not locked, the user programmable bits can be programmed but never erased.

Designed, manufactured, and tested for applications requiring low power and small form factor the SST34WA3203/3204 is offered in an extended temperature with a small footprint package to meet board space constraints requirement. See Figure 3 for pin assignments.

**Preliminary Specification**

## **Device Operation**

Commands are used to initiate the memory operation functions of the device. Commands are written to the device using standard microprocessor write sequences.

The SST34WA3203/3204 device also has an Auto Low Power mode which puts the device in a "near standby" mode after data has been accessed with a valid Read operation. This reduces the I<sub>DD</sub> active read current. The Auto Low Power mode reduces the typical I<sub>DD</sub> to Stand-By level. The device exits the Auto Low Power mode with any address or control signal transition; therefore, there is no access time penalty for Read cycles.

**TABLE 1: Critical Parameters**

| Critical Parameters                  | Values | Units |

|--------------------------------------|--------|-------|

| Max Random Address Access Time       | 70     | ns    |

| Max Synchronous Access Time (54 MHz) | 13.5   | ns    |

| Max Synchronous Access Time (66 MHz) | 11.5   | ns    |

T1.0 1340

## **Concurrent Read/Write Operation**

The multi-bank architecture of this device allows zero latency Concurrent Read/Write operation whereby the user can read from one bank while programming or erasing in another bank. With this operation a user can read system code in one bank while updating data in another bank. A unique feature of the SST34WA3203/3204 is ability to Read during an Erase-Suspend even while Programming in another bank. This feature is designed to respond to interrupt requests during concurrent operation. See Table 2, Current Read/Write State.

**TABLE 2: Concurrent Read/Write State**

| Current Operation in One Bank | Possible Operation in Any<br>Other Bank |  |  |  |

|-------------------------------|-----------------------------------------|--|--|--|

| Read                          | No Operation                            |  |  |  |

| Read                          | Write                                   |  |  |  |

| Write                         | Read                                    |  |  |  |

| Write                         | No Operation                            |  |  |  |

| No Operation                  | Read                                    |  |  |  |

| No Operation                  | Write                                   |  |  |  |

T2.0 1340

Note: For the purposes of this table, "Write" means to perform Sector/Block or Word-Program operations as applicable to the appropriate bank.

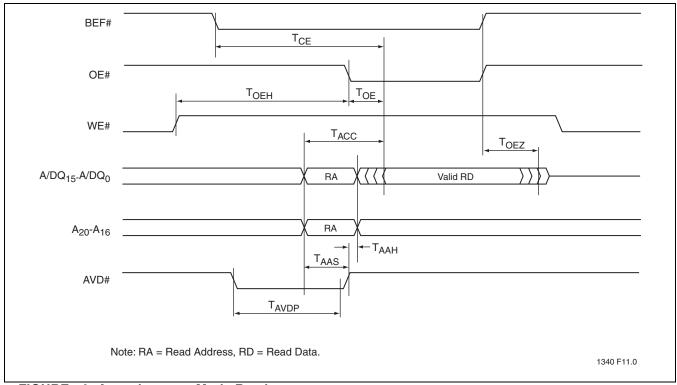

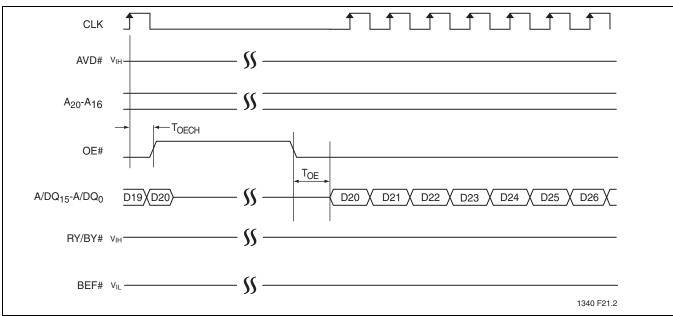

### **Asynchronous Read**

The default configuration on power-up, or after a hardware reset via the RST# pin, is Asynchronous Read. To read data from the memory array, the system must assert a valid address on A/DQ $_{15}$ –A/DQ $_{0}$  and A $_{20}$ –A $_{16}$ , while AVD# and BEF# are at V $_{IL}$ . During the read, WE# remains at V $_{IH}$  and CLK is X for Asynchronous Read, the rising edge of AVD# latches the address, and OE# is driven to V $_{IL}$ . The data appears on A/DQ $_{15}$ –A/DQ $_{0}$ . For details, see Figure 4. Since the memory array is divided into four banks, each bank remains enabled for read access until the command register contents are altered.

Address access time ( $T_{ACC}$ ) is equal to the delay from stable addresses to valid output data. The chip enable access time ( $T_{CE}$ ) is the delay from the stable addresses and stable BEF# to valid data at the outputs. The output enable access time ( $T_{OE}$ ) is the delay from the falling edge of OE# to valid data at the output.

The internal state machine is set to read array data upon device power-up or after a hardware reset. This ensures that no spurious alteration of the memory content occurs during the power transition.

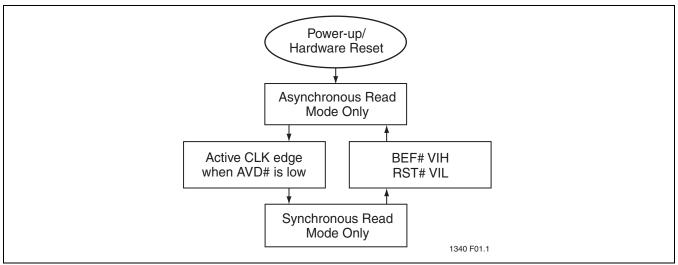

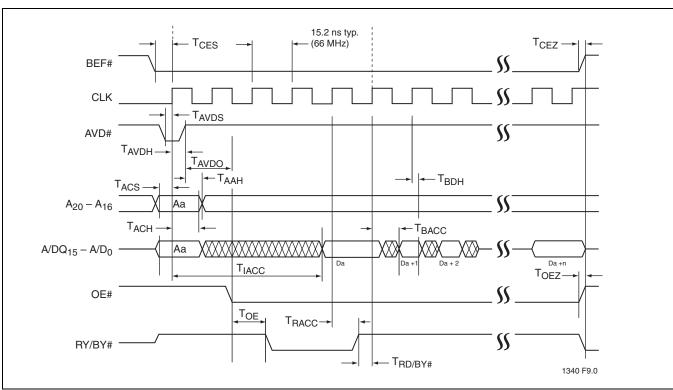

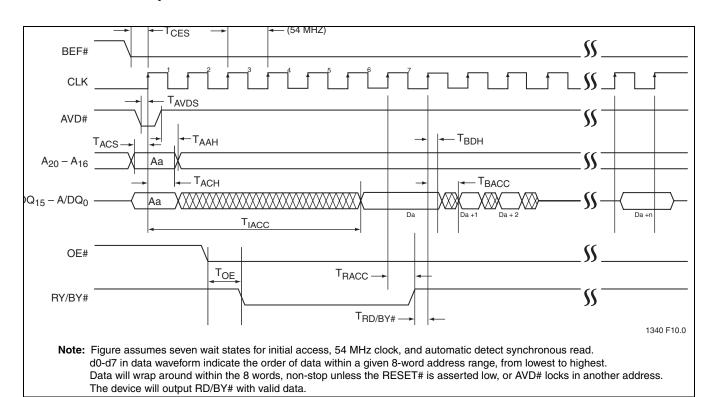

## **Burst Mode Read (Synchronous)**

The SST34WA3203/3204 default configuration on powerup or after reset is Asynchronous Read. However, it can be configured to operate in a Synchronous Read mode with a continuous, sequential linear burst operation or a linear burst operation of 8-, 16-, or 32-words length with wraparound.

Before setting the device configuration to Burst Mode, determine the number of wait states for the initial word access time (T<sub>IACC</sub>) and the desired Burst mode—continuous with, or without, wrap-around.

**Preliminary Specification**

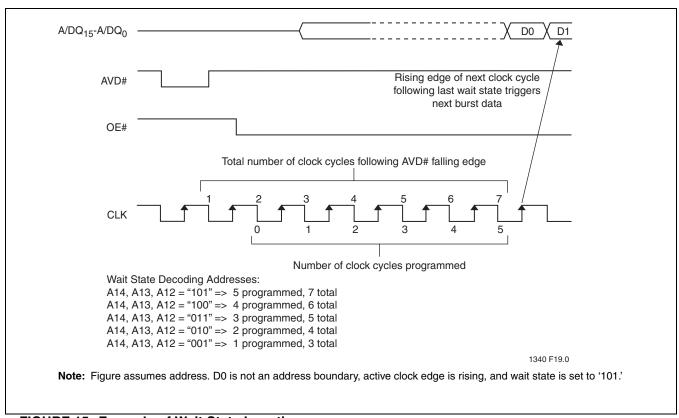

#### **Wait States**

On power up, the SST34WA3203/3204 defaults to asynchronous read operation. The device is automatically enabled for burst mode on the first rising edge on the CLK input, while the AVD# is held low for one clock cycle and the address is latched on the first rising edge of the CLK. Prior to activating the clock signal, the system determines how many wait states are desired for the initial word ( $T_{IACC}$ ) of each burst session. The system then writes the Set Configuration Register command sequence.

The device automatically delays RY/BY# by the needed

number of clock cycles if data is not ready. Refer to the details in "Handshaking Feature" section.

The initial word is output on the Data Bus  $T_{IACC}$  after the active edge of the first CLK cycle. Each successive clock cycle automatically increments the addresses counter. Subsequent words are output on the Data Bus  $T_{BACC}$  after the active edge of each successive clock cycle.

To return the device to Asynchronous Read mode, either drive BEF# to  $V_{IH}$  or drive RST# to  $V_{IL}$ .

FIGURE 1: Synchronous/Asynchronous State Diagram

#### 8-, 16-, 32-Words Linear Burst Mode with Wrap-Around

The SST34WA3203/3204 device supports a synchronous read operation with a Linear Burst mode of a predetermined word length with wrap-around. Groups of 8, 16, and 32 words can be read in this way as defined in Table 3.

In 8, 16, and 32-words Linear Burst mode operation, the starting address of the linear burst sequence is the address written to the device. Each successive clock cycle automatically increments the address counter until the top address of the group is reached. Once the top address is

reached, the address wraps back to the first address of the selected group and continues incrementing from there.

An example of an 8-word linear Burst mode with Wrap-Around is as follows: if the starting address in the 8-word mode is 11H (8 words group start = 10H, group end = 17H), the address range to be read would be 10H-17H, and the burst sequence would be 11H -12H -13H - 14H - 15H - 16H - 17H - 10H - and so on.

The RY/BY# pin will indicate when valid data is present on the data bus.

TABLE 3: 8-, 16-, 32-Words Linear Burst Mode Wrap-Around Groups

| Group Size | Address Ranges  |                 |                 |  |                             |

|------------|-----------------|-----------------|-----------------|--|-----------------------------|

| 8 words    | 00000H - 00007H | 00008H - 0000FH | 00010H - 00017H |  | $(A)^1 - (A + 7H)$          |

| 16 words   | 00000H - 0000FH | 00010H - 0001FH | 00020H - 0002FH |  | (B) <sup>1</sup> - (B + FH) |

| 32 words   | 00000H - 0001FH | 00020H - 0003FH | 00040H - 0005FH |  | $(C)^1 - (C + 1FH)$         |

T3.0 1340

1. A is a multiple of 00008H, B is a multiple of 00010H, and C is a multiple of 00020H.

**Preliminary Specification**

#### 8-16-32-Words Linear Burst Mode without Wrap-Around

The SST34WA3203/3204 device supports a synchronous read operation without a Linear Burst mode. A fixed number of words predefined as 8-, 16-, or 32-words are read from consecutive addresses starting with the initial word, which is written to the device. Once the fixed number of words are read completely, the Burst Read operation stops and the RY/BY# output goes low. There is no group limitation as there is with Linear Burst with Wrap-Around. See Table 3 for group definitions.

An example of an 8-word linear Burst mode without Wrap-Around is as follows: for an 8-word length Burst Read, if the starting address written to the device is 39h, the burst sequence would be 39-3A-3B-3C-3D-3E-3F-40h, and the read operation will be terminated at 40h. In a similar fashion, the 16-word and 32-word modes begin their burst sequence on the starting address written to the device, and Continuously Read to the predefined word length, of 16 or 32 words.

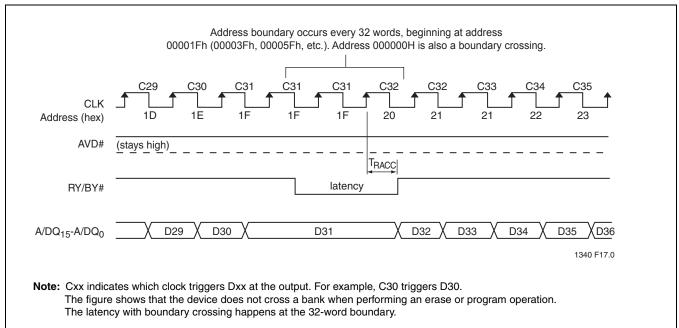

The operation is similar to the Continuous Burst, but will stop the operation at fixed word length. If the device crosses the first 32-word address boundary during burst read, a latency may occur before data appears for the next address and RY/BY# is pulsing low. If the burst read start address is 8-word boundary aligned (AO = A1 = A2 = 0), the latency does not occur. If the host system crosses the bank boundary, the device will react in the same manner as in the Continuous Burst.

#### **Continuous Linear Burst Mode**

The SST34WA3203/3204 device supports a synchronous read operation with a continuous, sequential linear Burst mode read. When in this mode, the Addresses are automatically incriminated linearly with every successive clock active edge. If the device reaches the Highest Memory Location Address (FFFFH), it will continue the continuous, sequential linear Burst read operation by wrapping around to Address 00000H. The Burst operation will continue sequentially until another address is latched via the AVD# pin, until BEF# is driven to  $V_{\rm IH}$ , or until RST# is driven to  $V_{\rm IL}$ .

When an address is latched via AVD# pin with active edge of CLK, a new burst read will start with a new initial address.

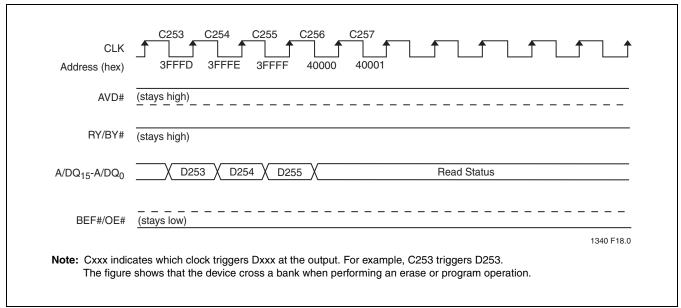

If the continuous, sequential linear burst read sequence crosses a bank boundary into a bank that is performing a Programming or Erasing operation, the device will provide status information. Once the system has completed the status read operation, or the device has completed the Program/Erase Operation, the system is allowed to start a new burst read operation. In this case a new address needs to be latched via the AVD# pin.

In synchronous, continuous, sequential, linear read array, a latency in output data may occur when a burst sequence crosses the first 32-word address boundary. If the burst read start address is 8-word boundary aligned ( $A_0 = A_1 = A_2 = 0$ ), the delay does not occur. If the burst read start address is mis-aligned to an 8-word boundary, the delay occurs once per burst-mode read sequence. The RY/BY# signal will indicate this delay to the system.

### **Burst Register**

The SST34WA3203/3204 defaults to Asynchronous Read on power-up. However, it can be configured to operate in a Synchronous Read Mode with continuous, sequential linear burst operation and linear burst operation of 8-, 16-, 32- words length with wrap-around.

The Burst Register is used to configure the type of read bus access the memory will perform by setting the desired Mode of Burst (continuous or wrap-around) and the number of wait states for the initial word access time  $(T_{IACC})$ .

The user can set the Burst Register with the Set Burst Register Command. The Burst Register will retain its information until it is reset via the RST# pin or after Power-Un

The Set Burst Register Command is initiated by executing a three-cycle command sequence. On the last bus cycle, Data is C0H, address bits  $A_{11}$ – $A_0$  are 555H, and address bits  $A_{17}$ – $A_{12}$  set the code to be latched, as shown in Table 4.

Upon power-up or hardware reset using the RST# pin, the device will be in the default state. The Burst Register can only be changed in Read and Erase Suspend mode.

Preliminary Specification

**TABLE 4: Burst Mode Configuration Command**

| Function                                                                                | Address         | Value                                                      |

|-----------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------|

| Programmable A <sub>12</sub> A <sub>14</sub> - A <sub>13</sub> - A <sub>12</sub> values |                 | A <sub>14</sub> - A <sub>13</sub> - A <sub>12</sub> values |

| Initial Wait                                                                            | A <sub>13</sub> | 0 - 0 - 1 = 3 wait states for initial word                 |

| State                                                                                   | A <sub>14</sub> | 0 - 1 - 0 = 4 wait states for initial word                 |

|                                                                                         |                 | 0 - 1 - 1 = 5 wait states for initial word                 |

|                                                                                         |                 | 1 - 0 - 0 = 6 wait states for initial word                 |

|                                                                                         |                 | 1 - 0 - 1 = 7 wait states for initial word (default)       |

|                                                                                         |                 | 1 - 1 - 0 = Reserved                                       |

|                                                                                         |                 | 1 - 1 - 1 = Reserved                                       |

| Burst Mode                                                                              | A <sub>15</sub> | A <sub>16</sub> - A <sub>15</sub> values                   |

| Type                                                                                    | A <sub>16</sub> | 0 - 0 = Continuous burst (default)                         |

|                                                                                         |                 | 0 - 1 = 8-word linear burst                                |

|                                                                                         |                 | 1 - 0 = 16-word linear burst                               |

|                                                                                         |                 | 1 - 1 = 32-word linear burst                               |

|                                                                                         | A <sub>17</sub> | 0 = linear burst with wrap-around (default)                |

|                                                                                         |                 | 1 = linear burst without wrap-around                       |

Note: The Device will be in the default state after Hardware Reset (via RST# pin) or after Power-Up.

T4.0 1340

## **Burst Suspend/Resume**

The Burst Suspend / Resume feature allows the system to temporarily suspend a synchronous burst operation during the initial access, before data is available, or after the device is reading data. When the burst operation is suspended, previously latched internal data and the current state are retained.

Burst Suspend occurs when BEF# is asserted, WE# is deasserted, and OE# is de-asserted. CLK must be halted at  $V_{\text{IH}}$  or  $V_{\text{IL}}$ . To resume the burst access, OE# is reasserted, and afterwards CLK can be restarted. Subsequent CLK edges resume the burst sequence where it was suspended.

When the Burst Suspend is enabled the device will enter a low power mode, in which the current consumption is reduced to typically 1mA. The RY/BY# pin, which is controlled by BEF#, will remain active and is not placed into a high-impedance state when OE# is de-asserted.

**Preliminary Specification**

## **Writing Commands**

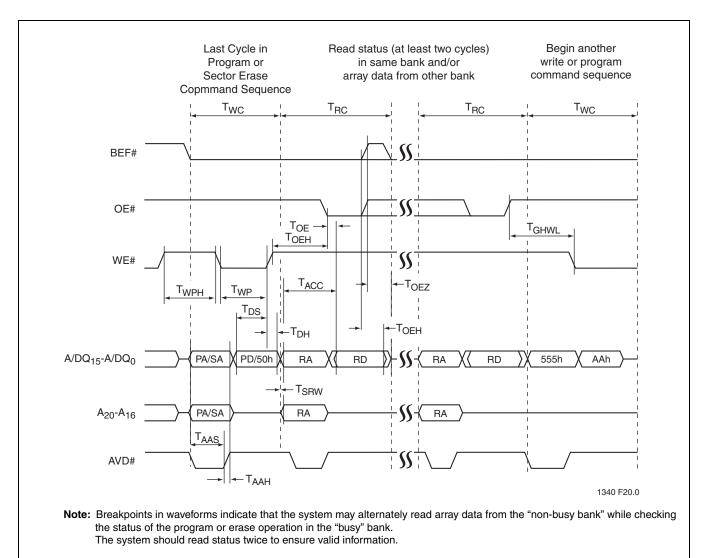

The SST34WA3203/3204 accept address and data information in the form of program commands. To write a command, the system needs to drive BEF#, and WE# to  $V_{IL}$ . The addresses are latched on the rising edge of AVD# while keeping OE# at  $V_{IH}$ , and data is latched on the rising edge of WE# while keeping OE# at  $V_{IH}$ .

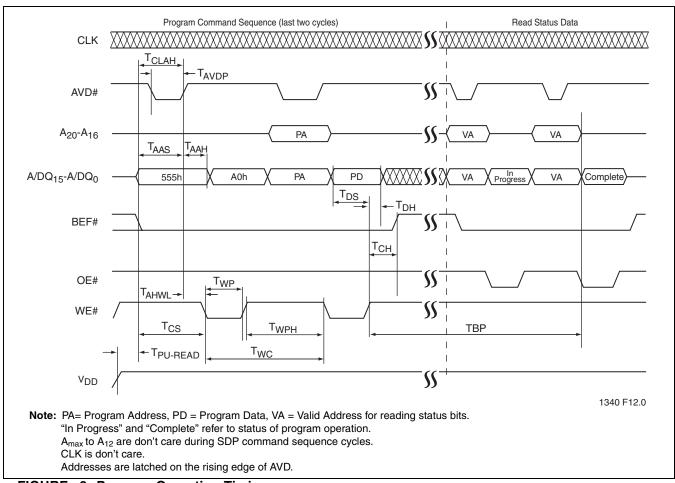

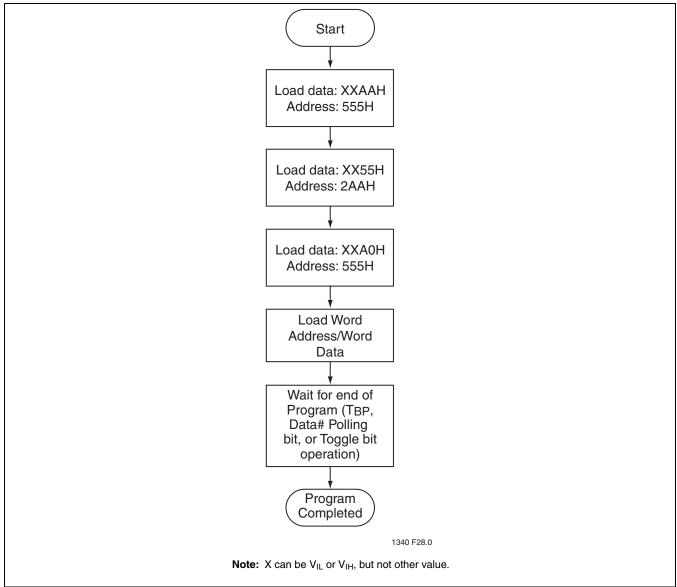

## **Word-Program Operation**

The SST34WA3203/3204 are programmed on a word-byword basis. Before programming, erase the sector to be programmed.

A Program operation is accomplished in three phases. First, the Software Data Protection is initiated using the three-word load sequence. Next, the word address and word data are loaded. Finally, the internal Program operation initiates after the rising edge of the fourth WE#. The Program operation completes within 12  $\mu$ s.

The SST34WA3203/3204 features an programming acceleration mode for faster programming. Once the device enters the programming acceleration mode, only two write cycles are required to program a word, instead of the four cycles required in the standard program command sequence.

During the Program operation, the only valid reads within the bank being programmed are status reads (DQ<sub>7</sub> Data# Polling and DQ<sub>2</sub>/DQ<sub>6</sub> Toggle Bits). Any commands issued during an internal Program operation are ignored.

When the Program Operation is complete, the bank will return to Read Array Mode. For Program operation timing diagram and flowchart, see Figure 8 and Figure 22.

## **Programming Acceleration Operation**

The programming acceleration makes programing faster than using a standard program command sequence because it reduces the standard four-cycle process to two cycles. Two unlock cycles initiates the programming acceleration command sequence which is followed by a third write cycle containing 20H as the programming acceleration command. The chip enters the programming acceleration mode. To program in this mode, a two-cycle programming acceleration program command sequence is all that is required. The first cycle contains the programming acceleration command, A0h; the second cycle contains the program address and data. Likewise, additional data is programmed. The initial two unlock cycles required in the standard program command sequence is eliminated. This reduces the total programming time. See Table 15 for programming acceleration command sequence requirements.

The system issues a two-cycle programming acceleration reset command sequence to exit the programming

acceleration mode and return to the read mode. The first cycle contains the data 90h, and the second cycle contains the data 00h.

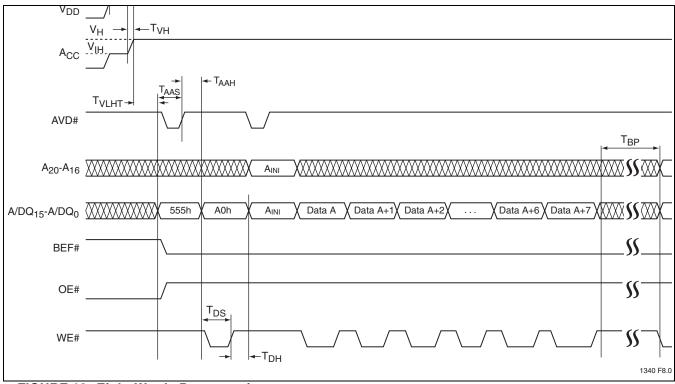

## **Eight-Word Program**

An Eight Word Program command is provided for fast data programming. At room temperature and normal V<sub>DD</sub>, the command is only enabled when the ACC pin is at Supervoltage VH (11.4V to 12V). The Eight Word Program Operation is initiated with the A0H command and then the host provides eight consecutive data words. The Eight Word program is an Asynchronous operation and the CLK signal is ignored. The system drives BEF# low to V<sub>II</sub> and the Initial address is latched on the rising edge of the first AVD# pulse while keeping OE# high. Data is latched on the rising edge of each WE# pulse while keeping OE# high. See Figure 10 for AC timings. The Initial address AINI must be 8-words boundary aligned  $(A_0 = A_1 = A_2 = 0)$ , otherwise the part will force the boundary alignment. Each subsequent WE# pulse will automatically increment the address of one word from AINI to AINI + 7. The user must issue 8 data words to be programmed when in Eight Word Program Mode.

## Standby Mode

The SST34WA3203/3204 enter the Standby mode when both the BEF# and RST# inputs are held at  $V_{DD} \pm 0.2 \text{ V}$ . The device requires standard access time ( $T_{CE}$ ) for read access before it is ready to read data.

### **Auto Low Power Mode**

These devices have the Auto Lower Power mode which puts it in a near standby mode. In Asynchronous read mode, this happens when addresses remain stable within  $T_{ACC}$  + 60 ns after data is accessed with a valid Read operation. This reduces the  $I_{DD}$  active Read current to 3  $\mu A$ , typically.

While BEF# is low, the device exits Auto Low Power mode with any address transition or control signal transition used to initiate another Read cycle, with no access time penalty. While in Auto Low Power mode, output data is latched and always available to the system.

In synchronous read mode, after the AVD# falling edge, the device automatically enters the Auto Low Power mode when there is no active CLK edge within  $T_{ACC}$ + 60ns. The device exits Auto Low Power mode with an active CLK edge.

**Preliminary Specification**

## **Memory Architecture**

The SST34WA3203/3204 features a 4-bank,512 KWord uniform multi-bank architecture. Of the four banks, the top or bottom banks contain 15 standard 32 KWord blocks and four parameter 8 KWord blocks for added granularity. The remaining three banks each contain uniform 32 KWord blocks. All 8 and 32 KWord blocks are further divided into 4 or 16 uniform 2 KWord sectors, respectively.

Each block and sector can be individually erased for greater flexibility. The device's unique bank architecture, allows reads from any bank while another bank is being erased (RWE) or programmed (RWP). The device also supports an Erase-Suspend mode that allows programming data in any other sector or block other than the one being erase-suspended. It can also read data at any memory sector or block other than the one being erased during the Erase-Suspend operation. Suspend operations cannot be nested because the system needs to complete or resume any previously suspended operation before a new operation can be suspended.

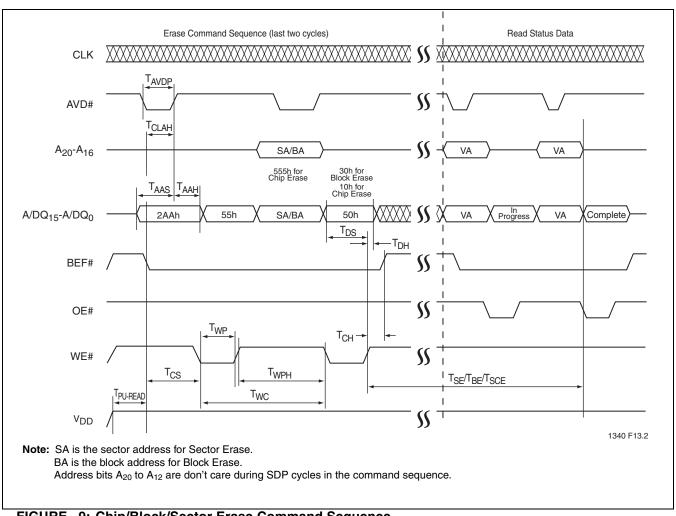

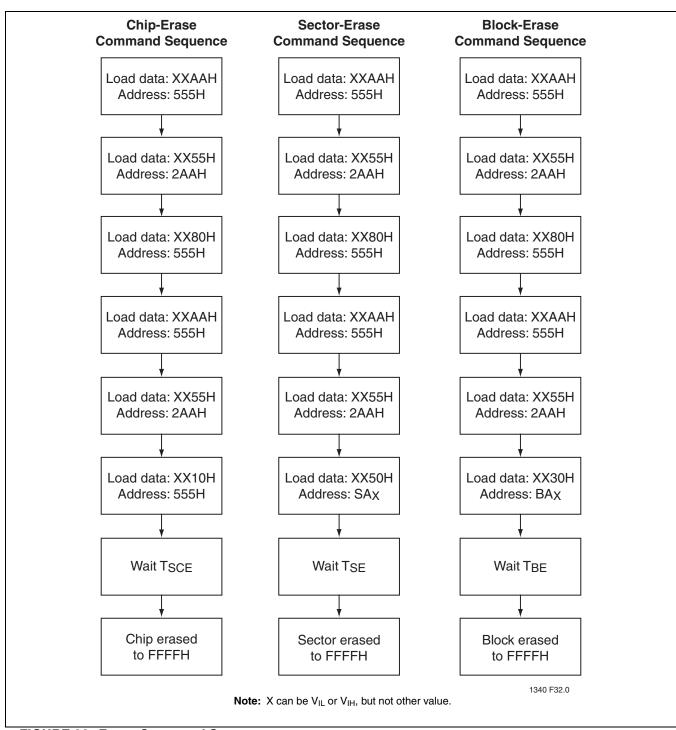

## **Sector/Block-Erase Operation**

The Sector/Block-Erase operation allows the system to erase the device on a sector-by-sector or block-by-block basis. The SST34WA3203/3204 offers Sector-Erase and Block-Erase modes. The sector architecture is based on uniform sector size of 2 KWord. The Block-Erase mode erases either the regular 32 KWord blocks or the smaller 8 KWord Parameter Blocks. The Sector-Erase operation is initiated by executing a six-word command sequence with Sector-Erase command (50H) and sector address (SA) in the last bus cycle. The Block-Erase operation is initiated by executing a six-word command sequence with Block-Erase command (30H) and block address (BA) in the last bus cycle. The Sector or Block address is latched during the sixth cycle, either on the rising edge of AVD# or on the falling edge of WE# cycle, whichever occurs last, while the command (30H/50H) is latched on the rising edge of the sixth WE# pulse. The internal Erase operation begins after the sixth WE# pulse. The End-of-Erase operation can be determined using either Data# Polling or Toggle Bit methods. See Figure 9 for timing waveforms and Figure 26 for the flowchart.

## **Erase-Suspend, Erase-Resume Operations**

The Erase-Suspend command temporarily suspends a Sector/Block-Erase operation which allows data to be read from any memory location, or to be programmed into any sector or block that is not suspended for an Erase operation. The operation is executed by issuing the Erase-Suspend one-word command, B0H. The device automatically enters the Erase-Suspend Read Mode within TES. 15 us. after the Erase-Suspend command is issued. Valid data is read from any sector or block that is not suspended from an Erase operation. Reading at an address location within erase-suspended sectors or blocks will output DQ2 toggling and DQ6 at '1'. See Table 6, Write Operation Status, for details. While in Erase-Suspend mode, a Word-Program operations are allowed for all sectors and blocks, with the exception of the sector or block selected for Erase-Suspend. If a Word Program operation is attempted in the suspended sector or block, the command is rejected and the Program operation is not performed.

The system can also issue the Software ID Entry command during the Erase-Suspend. After the system has issued the Software ID Exit command, the device automatically reverts to Read Mode.

To resume the Sector/Block-Erase operation that is suspended, the system must issue the Erase-Resume command. The operation is executed by issuing the Erase-Resume one-word command, 30H, at any address in the last word sequence.

For an erase operation being suspended or re-suspended after resume, the cumulative erase time needed is greater than the erase time of a non-suspended erase operation. The accumulative erase time needed may become very long if the hold time from Erase-Resume to the next Erase-Suspend operation,  $T_{ERH}$ , is less than 330 $\mu$ s.

The Erase-Resume command will be ignored until any program operations initiated during Erase-Suspend are complete. The Erase-Suspend and Program Resume operations have no influence on the program operation.

See Table 5 for details of Suspend-Resume and Concurrent operations.

**Preliminary Specification**

**TABLE** 5: Erase-Suspend and Concurrent Banks State

| Current Operation in One Bank | Possible Operation in The Same Bank                 | Possible Operation in Any Other<br>Concurrent Bank |

|-------------------------------|-----------------------------------------------------|----------------------------------------------------|

| Sector/Block-Erase-Suspend    | Read any other Sector/Block within the same Bank    | No Operation                                       |

| Sector/Block-Erase-Suspend    | Read any other Sector/Block within the same Bank    | Program any Sector/Block                           |

| Sector/Block-Erase-Suspend    | Program any other Sector/Block within the same Bank | No Operation                                       |

| Sector/Block-Erase-Suspend    | Program any other Sector/Block within the same Bank | Read any Sector/Block                              |

| Sector/Block-Erase-Suspend    | No Operation                                        | Read any Sector/Block                              |

| Sector/Block-Erase-Suspend    | No Operation                                        | Program any Sector/Block                           |

T5.0 1340

## **Chip-Erase Operation**

The SST34WA3203/3204 provides a Chip-Erase operation which allows the user to erase the entire memory array to the '1' state. This is a quick way to erase the entire device. To initiate the Chip-Erase execute a six-word command sequence with the Chip-Erase command, 10H, at address 555H in the last word sequence. The Erase operation begins with the rising edge of the sixth WE#. During the Erase operation, the only valid reads are Toggle Bit or Data# Polling. See Table 15 for the command sequence, Figure 9 for timing diagram, and Figure 26 for the flowchart. Any commands issued during the Chip-Erase operation are ignored, including the Erase-Suspend Command. If WP# pin is held to  $V_{\rm IL}$ , or one or more blocks are locked, the Chip Erase Operation is disabled.

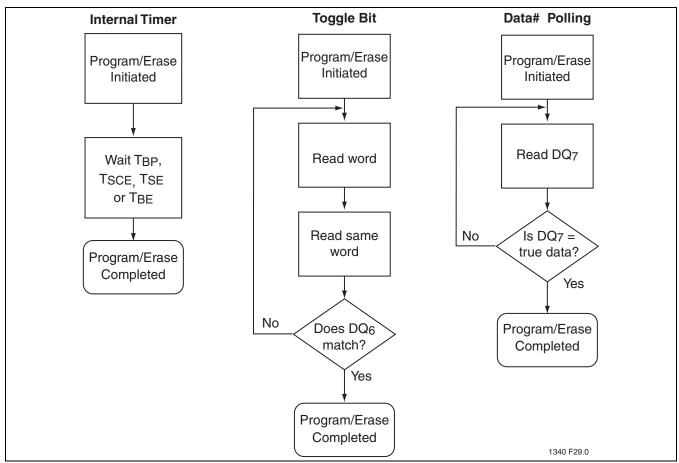

## **Write Operation Status Detection**

The SST34WA3203/3204 optimizes the system Write cycle time by providing two software means to detect the completion of a Program Write cycle or an Erase Write cycle. The software detection includes two status bits: Data# Polling (DQ7) and Toggle Bit (DQ6). The End-of-Write detection mode, which is enabled after the rising edge of WE#, initiates the internal Program or Erase operation. The actual completion of the nonvolatile write is asynchronous with the system; therefore, either a Data# Polling (DQ7), or Toggle Bit (DQ6) Read may be simultaneous with the completion of the Write cycle. If this occurs, the system will get an erroneous result. For example, valid data may appear to conflict with either DQ7 or DQ6. In order to prevent spurious rejection when an erroneous result occurs, the software routine must include a loop to read the accessed location an additional time. If both Reads indicate the completion, then the Write cycle has completed.

## Ready (RY/BY#)

The RY/BY# pin is a dedicated status output that indicates valid output data on A/DQ15–A/DQ0 during synchronous burst reads. When RY/BY# is asserted (RY/BY# = VOH), the output data is valid and can be read. When RY/BY# is de-asserted (RY/BY# = VOL), the system will wait until RY/BY# is re-asserted before expecting the next word of data.

Two conditions cause the RY/BY# output to be low: during the initial access while in burst mode, and when the device is set to Continuous Burst Mode and the address crosses the first 32 word boundary.

In asynchronous, non-burst mode, the RY/BY# pin does not indicate valid or invalid output data. Instead, RY/BY# =  $V_{OH}$  when BEF# =  $V_{IL}$ , and RY/BY# is Hi-Z when BEF# =  $V_{IH}$ .

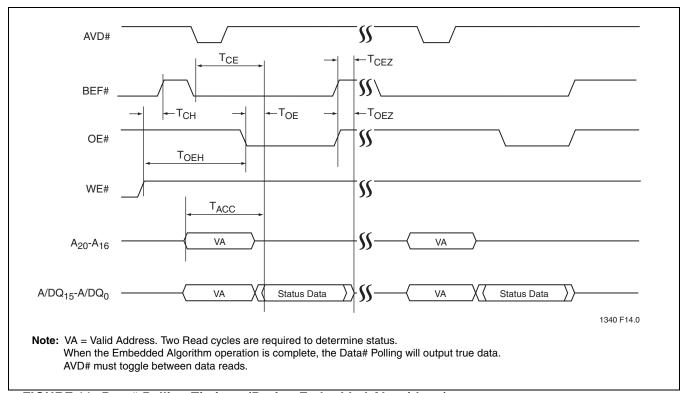

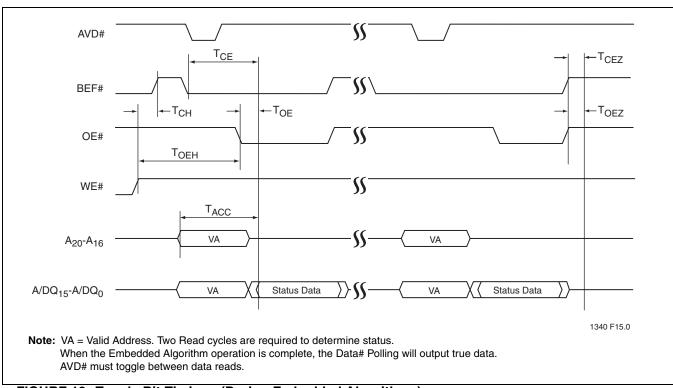

#### Data# Polling (DQ7)

When the SST34WA3203/3204 is in the internal Program operation, any attempt to read DQ7 will produce the complement of the true data. Once the Program operation is completed, DQ7 will produce true data. During internal Erase operation, any attempt to read DQ7 will produce a '0'. Once the internal Erase operation is completed, DQ7 will produce a '1'. The Data# Polling is valid after the rising edge of fourth WE# pulse for Program operation. For Sector/ Block or Chip-Erase, the Data# Polling is valid after the rising edge of sixth WE# pulse. See Figure 11 for Data# Polling timing diagram and Figure 23 for a flowchart.

Preliminary Specification

## Toggle Bits (DQ6 and DQ2)

During the internal Program or Erase operation, any consecutive attempts to read DQ6 will produce alternating '1's and '0's. For example, toggling between '1' and '0'. When the internal Program or Erase operation is complete, the DQ6 bit will stop toggling. The device is then ready for the next operation. For Sector-, Block-, or Chip-Erase, the toggle Bit (DQ6) is valid after the rising edge of sixth WE# pulse. DQ6 will be set to '1' if a Read operation is attempted on an Erase-Suspended Sector/Block. If the Program operation is initiated in a sector/block not selected for Erase-Suspend mode, DQ6 will toggle. An additional Toggle Bit is available on DQ2, which can be used in conjunction with DQ6 to check whether a particular sector is being actively erased or erase-suspended. Table 6 shows detailed status bit information. The Toggle Bit (DQ2) is valid after the rising edge of the last WE# pulse of the Write operation. See Figure 12 for Toggle Bit the timing diagram and Figure 23 for a flowchart.

**TABLE 6: Write Operation Status**

| Status                    |                                                       | DQ7  | DQ6    | DQ5  | DQ2          |

|---------------------------|-------------------------------------------------------|------|--------|------|--------------|

| Normal<br>Operation       | Standard<br>Program                                   | DQ7# | Toggle | 0    | No<br>Toggle |

|                           | Standard<br>Erase                                     | 0    | Toggle | 0    | Toggle       |

| Erase-<br>Suspend<br>Mode | Read from<br>Erase-Sus-<br>pended Sec-<br>tor/Block   | 1    | 1      | 0    | Toggle       |

|                           | Read from<br>Non- Erase-<br>Suspended<br>Sector/Block | Data | Data   | Data | Data         |

|                           | Program                                               | DQ7# | Toggle | 0    | N/A          |

T6.0 1340

Note: Note: DQ7, DQ6 and DQ2 require a valid address when reading status information. When in Erase-Suspend Mode the system can read either synchronously (Burst) or asynchronously.

#### **Data Protection**

The SST34WA3203/3204 provides both hardware and software features to protect nonvolatile data from inadvertent writes.

#### **Hardware Data Protection**

The devise provides the following protection features to prevent inadvertent writes:

- Noise/Glitch Protection: A WE# or BEF# pulse of less than 5 ns will not initiate a write cycle.

- V<sub>DD</sub> Power Up/Down Detection: The Write operation is inhibited when V<sub>DD</sub> is less than 0.9V.

- Write Inhibit Mode: Forcing OE# low, BEF# high, or WE# high will inhibit the Write operation. This prevents inadvertent writes during power-up or powerdown.

#### A<sub>CC</sub> Pin

When the  $A_{CC}$  pin is brought to the Supervoltage VH the Eight Word Program command is enabled. In this case, all blocks are temporarily unprotected regardless of the Block Locking Register. The only device operation available when  $A_{CC}$  pin is at  $V_H$  is Eight Word Programming, the  $A_{CC}$  pin must not be held above  $V_{IH}$  during other operations. Eight Word Programming is provided for fast data programming in the manufacturing environment. The device will return to normal operations when voltage is set to  $V_{IH}$  on  $A_{CC}$  pin and each block locking status will depend on the Block Locking Register value (this is the value that each block had before the application of  $V_H$  on  $A_{CC}$ ). The  $A_{CC}$  pin must not be left floating or unconnected.

When the  $A_{CC}$  pin is brought to  $V_{IL}$  the device is locked. The  $A_{CC}$  pin should be at  $V_{IH}$  for normal operations.

#### WP# Pin

The SST34WA3203/3204 provides a hardware block protection which protects the 8 KWords for Blocks BA0 and BA1 (SST34WA3203), and/or BA65 and BA66 (SST34WA3204). BAx stands for Block Address as specified in Table 10 and 11.

The 8 KWord blocks, located in the top or bottom blocks, are protected when WP# is held to  $V_{\rm IL}$ . The Program and Erase operation in these blocks is disabled independently using the Block Locking Register Status. The user can disable the hardware protection for the outermost blocks by driving WP# to  $V_{\rm IH}$ . In this case, the Protection Status of the two outermost Blocks will revert to what is indicated by the corresponding Block Locking Registers. WP# will be latched at a specific time in the program or erase sequence. To prevent a write to the outermost blocks, WP# must be held to  $V_{\rm IL}$  on the last write cycle of the sequence. For example, the 4th write cycle in the program sequence and the 6th write cycle in the erase sequence. If using the programming acceleration feature, on the 2nd program

#### **Preliminary Specification**

cycle after the programming acceleration command is written, WP# must be held to  $V_{II}$  on the 2nd cycle. If the WP# pin is held to V<sub>IL</sub> the Chip Erase Operation is disabled. WP# should be pulled into high state if it is not used.

#### Software Block Locking

To prevent accidental data programming or erasing, the Block Lock command is used. All 32 KWord main blocks and 8KW parameter blocks can be independently locked. A locked block can not be able to be programmed or erased. After Power-Up, all blocks are locked.

Changing the state-of-lock for a block is done by using the Block Lock/Unlock Command (60H). See Table 15.

In the third cycle the address must point to the Block to be locked/unlocked. The status of the A6 Address bit will specify if the block must be locked (A6=VIL) or unlocked (A<sub>6</sub>=V<sub>IH</sub>). After the third cycle, the state-of-lock of additional Blocks in the same Bank can be modified.

Reading the state-of-lock for each block is achieved using the Read Block Locking Register command with the address parameter that is within the block address space For details, see Table 15. This command will read the Block Locking Register. If the Block Locking Register is 0000H the Block is Unlocked, if it is 0001H the Block is Locked.

The Read Block Locking Register command can be written to a bank which is either in Read Mode or in Erase-Suspend-Read mode. Only one bank at a time can be switched to Read Block Locking Register mode. To return the selected bank to Read Mode, or Erase-Suspend Read Mode, the Software ID Exit/Block Locking Exit Command must be issued by the system. see Table 15.

WP# is internally ORed with the Block Locking register. When WP# is low, the blocks are hardware write protected regardless of the state of the Write-Lock bit for the corresponding Block Locking registers. Clearing the Write-Protect bit in any register when WP# is low will have no functional effect, even though the register may indicate that the block is no longer locked.

After the third cycle, the state-of-lock for additional Blocks in the same Bank can be modified.

TABLE 7: Block Locking Register Data

| Reserved Bits BLR[15:1] | Write-Lock bit: BLR[0] | Hex Code | Lock Status                              |

|-------------------------|------------------------|----------|------------------------------------------|

| 00000000000000          | 0                      | 0000H    | Full Access                              |

| 000000000000000         | 1                      | 0001H    | Write Locked (Default State at Power-Up) |

Note: The default read status of all blocks upon power-up is write-locked ("01H"). After power-up, when the power supply  $(V_{DD})$  is valid, the register is alterable.

**Preliminary Specification**

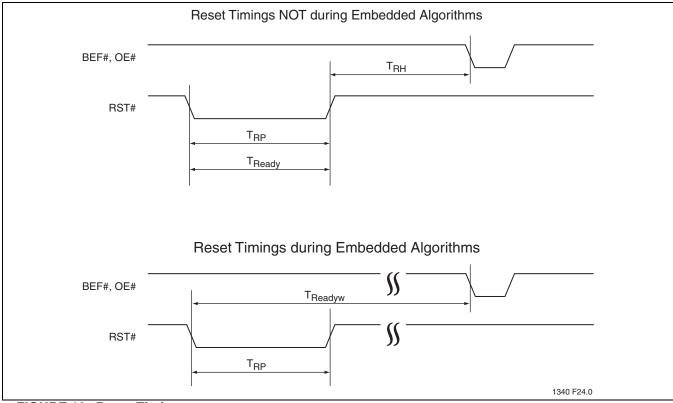

## **Hardware Reset (RST#)**

The RST# pin provides a hardware method of resetting the devices to read array data. When the RST# pin is held low for at least  $T_{RB}$  any in-progress operation will terminate and the device will return to Read Array mode. When no internal Program/Erase operation is in progress, a minimum period of  $T_{RH}$  is required after RST# is driven high before a valid Read can take place.

The interrupted Erase operation must to be reinitiated after the device resumes normal operation mode to ensure data integrity.

The RST# pin is an asynchronous input signal which aborts an on-going Erase or Program operation and resets the device to Read Array mode within a time  $T_{Readyw}$ . If RST# pin is asserted during a Read Operation, the required time to reset the device is  $T_{Ready}$ . At this point all outputs are tri-stated, and the device ignores any Read/ Write operations for the duration of the RST# low pulse. The RST# reset operation will also reset the Burst Configuration register to Asynchronous Read Mode and set the part in Read Array mode. The current consumption when RST# is held at VSS +/- 0.2V, is reduced to  $I_{DD}$  Stand-By values.

## **Software Data Protection (SDP)**

The SST34WA3203/3204 provides the JEDEC approved Software Data Protection scheme for all data alteration operations, such as Program and Erase. Any single word Program operation requires the inclusion of the three-word sequence. The three-word load sequence is used to initiate the Program operation, providing optimal protection from inadvertent Write operations; for instance, during the system power-up or power-down. Any Erase operation requires the inclusion of six-word sequence. These devices are shipped with the Software Data Protection permanently enabled. See Table 15 for the specific software command codes. During SDP command sequence, invalid commands will abort the device to read mode within  $T_{\rm RC}$ . The contents of DQ15- DQ8 can be  $V_{\rm IL}$  or  $V_{\rm IH}$ , but no other value, during any SDP command sequence.

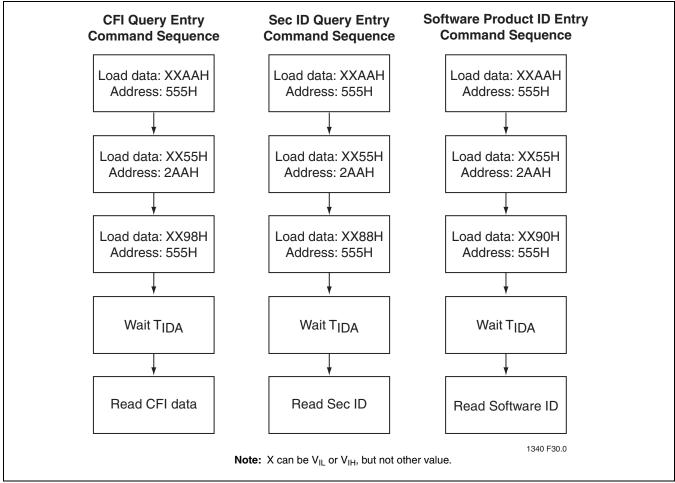

## **Common Flash Memory Interface (CFI)**

The SST34WA3203/3204 contains the CFI information to describe the characteristics of the device. In order to enter the CFI Query mode, the system must write a one word command or a three-word sequence, with 98H— the CFI Query command—to address 555H in the last word sequence. Once the device enters the CFI Query mode, the system can read the CFI data at the addresses given in Tables 18 through 22. The System can write the CFI entry command when the device is in Read Array mode and also when the device is in Product Identification Mode. The system must write the CFI Exit command to return to Read

mode or Erase-Suspend Read mode from the CFI Query mode.

## **Security ID**

The SST34WA3203/3204 device offers a 136-word Security ID space. The Secure ID space is divided into two segments—one 8-word, 128-bit factory programmed segment and one 128-word user programmed segment. The first segment is programmed and locked at SST with a unique 128-bit number. The user segment is left unprogrammed for the customer to program as desired.

To program the user segment of the Security ID, the Security ID Word-Program command is required. Check the end-of-write status of the Security ID by reading the toggle bits. Do not use Data# Polling to detect the end-of-write. Once the programming is complete, the Sec ID must be locked using the User Sec ID Program Lock-Out, which disables any future corruption of this space. Neither SEC ID segment—user nor factory programmed—can be erased, regardless of whether or not the Sec ID is locked. The Secure ID space can be queried by executing a three-word command sequence with Enter Sec ID command (88H) at address 555H in the last byte sequence. To exit this mode, the Exit Sec ID command should be executed. Refer to Table 8 for more details.

The Security ID space is located at addresses 000000H to 0000FFH. The Factory programmed segment is located at addresses 000000H to 000007H. The User segment is located at address 000080H to 0000FFH. The Security ID Locked/Unlocked status can be read at Address 000007FH. See Table 15. If  $DQ_3$  = '1' the User Segment of the Security ID is Unlocked. When  $DQ_3$  = '0', the User Segment of the Security ID is Locked. Once the Query Security ID Command is executed, the system can read the Security ID space with normal Read cycles using the valid address range 0000000H to 00000FFH. See Table 8 for more details.

**TABLE 8: Security ID Valid Range**

| Security ID Segment               | Start Address | End Address |

|-----------------------------------|---------------|-------------|

| Factory Programmed                | 000000H       | 000007H     |

| User Programmed                   | 000080H       | 0000FFH     |

| Sec ID Locked/<br>Unlocked Status | 00007FH       |             |

T8.0 1340

**Preliminary Specification**

### **Product Identification**

The Product Identification mode identifies the devices and the manufacturer. For software operation details see Table 15, for Software ID Entry command sequence flowchart see Figure 24. The Product Identification Mode (PIM) is entered by issuing two unlock cycles. This must be followed by a third cycle that contains the Bank Address (BA using A<sub>20</sub> to A<sub>19</sub>) and the Product Identification Mode command. After this third cycle, the addressed Bank enters the Product Identification Mode. The system can read the manufacturer ID or the Device ID any number of times without re-issuing the PIM command sequence. The Product Identification command may be written to a bank that is either in Read Mode or in Erase-Suspend Read Mode. The Product Identification Command cannot be written while the device is Programming or Erasing another bank. If the system addresses a different Bank, memory array data is read from the device following normal Asynchronous Read operation. No subsequent data will be made available if the device is in Synchronous Mode. The system must issue the Software ID Exit command in order to return the Bank previously set in Product Identification Mode into Read mode or Erase-Suspend Read mode.

**TABLE 9: Product Identification**

|                   | Address               | Data  |

|-------------------|-----------------------|-------|

| Manufacturer's ID | BK <sub>X</sub> 0000H | 00BFH |

| Device ID         |                       |       |

| SST34WA3203       | BK <sub>X</sub> 0001H | 975BH |

| SST34WA3204       | BK <sub>X</sub> 0001H | 975AH |

T9.0 1340

**Note:**  $BK_X = Bank Address$ , using  $A_{20}$  to  $A_{19}$ .

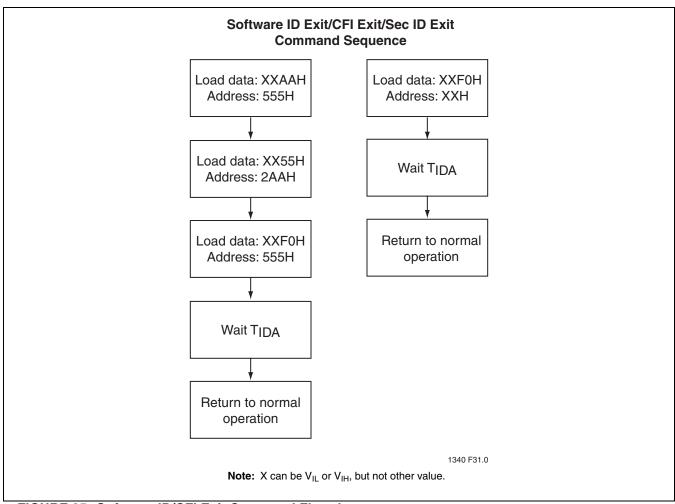

## Product Identification Mode / CFI Mode / Security ID / Block Locking Exit

In order to return the device to the standard Read Array Mode, the Software Product Identification / CFI / Security ID / Block Locking Modes must be exited. Exit is accomplished by issuing the Software Product Identification / CFI / Security ID / Block Locking Modes Exit command sequence, which returns the device to the Read mode. This command may also be used to reset the device to the Read Array Mode after any inadvertent transient condition that apparently causes the device to behave abnormally, e.g., not read correctly. The Software Product Identification / CFI / Security ID / Block Locking Query/Exit command cannot be executed concurrent to Program/ Erase operations. See Table 15 for the software command code, Figure 25 for a flowchart.

## **Handshaking Feature**

The device is equipped with a handshaking feature that brings out the fastest initial latency of this burst mode flash memory by simply monitoring the RY/BY# signal from the device to determine when the initial word of burst data is ready to be read. In this handshaking mode, the microprocessor does not need to set its register the number of initial wait clocks. The device will indicate when the initial word of burst data is valid by the rising edge of RY/BY# after OE goes low. If the handshaking feature is not used for burst mode performance optimization, then the host system must set the appropriate number of wait states in the flash device depending on clock frequency. See Table 4 for more information.

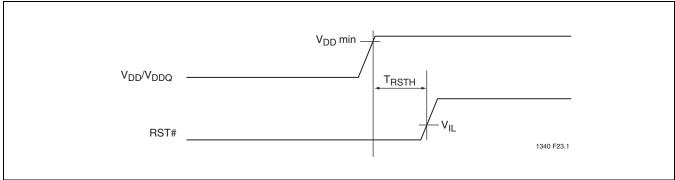

## V<sub>DD</sub> Power-up/Power-down Sequencing

There are no restrictions on  $V_{DD}$  sequencing during power-up or power-down. Setting RST# to  $V_{IL}$  level is required during the entire  $V_{DD}$  power sequence until the respective supplies reach their operating voltages. Once  $V_{DD}$  reach their respective operating voltages, setting RST# to  $V_{IH}$  level is allowed.

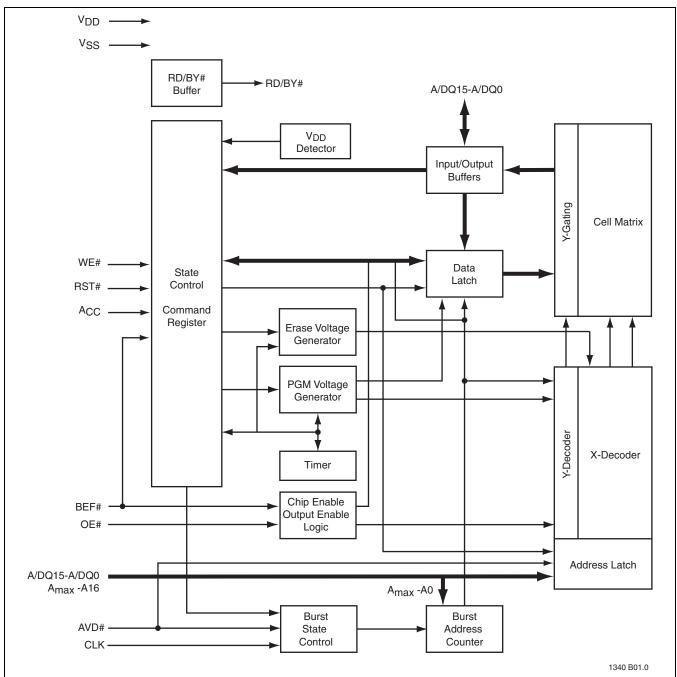

FIGURE 2: Logic Diagram

TABLE 10: SST34WA3203, 8 Mbit x4 Concurrent SuperFlash Multi-Bank Memory Organization (1 of 2)

| Bank | Block | Block Size | Address Range   |

|------|-------|------------|-----------------|

| Α    | BA0   | 8 Kwords   | 000000h-001FFFh |

|      | BA1   | 8 Kwords   | 002000h-003FFFh |

|      | BA2   | 8 Kwords   | 004000h-005FFFh |

|      | BA3   | 8 Kwords   | 006000h-007FFFh |

|      | BA4   | 32 Kwords  | 008000h-00FFFFh |

|      | BA5   | 32 Kwords  | 010000h-017FFFh |

|      | BA6   | 32 Kwords  | 018000h-01FFFFh |

|      | BA7   | 32 Kwords  | 020000h-027FFFh |

|      | BA8   | 32 Kwords  | 028000h-02FFFFh |

|      | BA9   | 32 Kwords  | 030000h-037FFFh |

|      | BA10  | 32 Kwords  | 038000h-03FFFFh |

|      | BA11  | 32 Kwords  | 040000h-047FFFh |

|      | BA12  | 32 Kwords  | 048000h-04FFFFh |

|      | BA13  | 32 Kwords  | 050000h-057FFFh |

|      | BA14  | 32 Kwords  | 058000h-05FFFFh |

|      | BA15  | 32 Kwords  | 060000h-067FFFh |

|      | BA16  | 32 Kwords  | 068000h-06FFFFh |

|      | BA17  | 32 Kwords  | 070000h-077FFFh |

|      | BA18  | 32 Kwords  | 078000h-07FFFFh |

| В    | BA19  | 32 Kwords  | 080000h-087FFFh |

|      | BA20  | 32 Kwords  | 088000h-08FFFFh |

|      | BA21  | 32 Kwords  | 090000h-097FFFh |

|      | BA22  | 32 Kwords  | 098000h-09FFFFh |

|      | BA23  | 32 Kwords  | 0A0000h-0A7FFFh |

|      | BA24  | 32 Kwords  | 0A8000h-0AFFFFh |

|      | BA25  | 32 Kwords  | 0B0000h-0B7FFFh |

|      | BA26  | 32 Kwords  | 0B8000h-0BFFFFh |

|      | BA27  | 32 Kwords  | 0C0000h-0C7FFFh |

|      | BA28  | 32 Kwords  | 0C8000h-0CFFFFh |

|      | BA29  | 32 Kwords  | 0D0000h-0D7FFFh |

|      | BA30  | 32 Kwords  | 0D8000h-0DFFFFh |

|      | BA31  | 32 Kwords  | 0E0000h-0E7FFFh |

|      | BA32  | 32 Kwords  | 0E8000h-0EFFFFh |

|      | BA33  | 32 Kwords  | 0F0000h-0F7FFFh |

|      | BA34  | 32 Kwords  | 0F8000h-0FFFFh  |

| С    | BA35  | 32 Kwords  | 100000h-107FFFh |

|      | BA36  | 32 Kwords  | 108000h-10FFFFh |

|      | BA37  | 32 Kwords  | 110000h-117FFFh |

|      | BA38  | 32 Kwords  | 118000h-11FFFFh |

|      | BA39  | 32 Kwords  | 120000h-127FFFh |

|      | BA40  | 32 Kwords  | 128000h-12FFFFh |

|      | BA41  | 32 Kwords  | 130000h-137FFFh |

|      | BA42  | 32 Kwords  | 138000h-13FFFFh |

TABLE 10: SST34WA3203, 8 Mbit x4 Concurrent SuperFlash Multi-Bank Memory Organization (2 of 2)

| Bank | Block | Block Size | Address Range   |

|------|-------|------------|-----------------|

|      | BA43  | 32 Kwords  | 140000h-147FFFh |

|      | BA44  | 32 Kwords  | 148000h-14FFFFh |

|      | BA45  | 32 Kwords  | 150000h-157FFFh |

|      | BA46  | 32 Kwords  | 158000h-15FFFFh |

|      | BA47  | 32 Kwords  | 160000h-167FFFh |

|      | BA48  | 32 Kwords  | 168000h-16FFFFh |

|      | BA49  | 32 Kwords  | 170000h-177FFFh |

|      | BA50  | 32 Kwords  | 178000h-17FFFFh |

| D    | BA51  | 32 Kwords  | 180000h-187FFFh |

|      | BA52  | 32 Kwords  | 188000h-18FFFFh |

|      | BA53  | 32 Kwords  | 190000h-197FFFh |

|      | BA54  | 32 Kwords  | 198000h-19FFFFh |

|      | BA55  | 32 Kwords  | 1A0000h-1A7FFFh |

|      | BA56  | 32 Kwords  | 1A8000h-1AFFFFh |

|      | BA57  | 32 Kwords  | 1B0000h-1B7FFFh |

|      | BA58  | 32 Kwords  | 1B8000h-1BFFFFh |

|      | BA59  | 32 Kwords  | 1C0000h-1C7FFFh |

|      | BA60  | 32 Kwords  | 1C8000h-1CFFFFh |

|      | BA61  | 32 Kwords  | 1D0000h-1D7FFFh |

|      | BA62  | 32 Kwords  | 1D8000h-1DFFFFh |

|      | BA63  | 32 Kwords  | 1E0000h-1E7FFFh |

|      | BA64  | 32 Kwords  | 1E8000h-1EFFFFh |

|      | BA65  | 32 Kwords  | 1F0000h-1F7FFFh |

|      | BA66  | 32 Kwords  | 1F8000h-1FFFFFh |

T10.0 1340

TABLE 11: SST34WA3204, 8 Mbit x4 Concurrent SuperFlash Multi-Bank Memory Organization (1 of 2)

| Bank | Block | Block Size | Address Range   |

|------|-------|------------|-----------------|

| Α    | BA0   | 32 Kwords  | 000000h-007FFFh |

|      | BA1   | 32 Kwords  | 008000h-00FFFFh |

|      | BA2   | 32 Kwords  | 010000h-017FFFh |

|      | BA3   | 32 Kwords  | 018000h-01FFFFh |

|      | BA4   | 32 Kwords  | 020000h-027FFFh |

|      | BA5   | 32 Kwords  | 028000h-02FFFFh |

|      | BA6   | 32 Kwords  | 030000h-037FFFh |

|      | BA7   | 32 Kwords  | 038000h-03FFFFh |

|      | BA8   | 32 Kwords  | 040000h-047FFFh |

|      | BA9   | 32 Kwords  | 048000h-04FFFFh |

|      | BA10  | 32 Kwords  | 050000h-057FFFh |

|      | BA11  | 32 Kwords  | 058000h-05FFFFh |

|      | BA12  | 32 Kwords  | 060000h-067FFFh |

|      | BA13  | 32 Kwords  | 068000h-06FFFFh |

|      | BA14  | 32 Kwords  | 070000h-077FFFh |

|      | BA15  | 32 Kwords  | 078000h-07FFFFh |

|      | BA16  | 32 Kwords  | 080000h-087FFFh |

|      | BA17  | 32 Kwords  | 088000h-08FFFFh |

|      | BA18  | 32 Kwords  | 090000h-097FFFh |

| В    | BA19  | 32 Kwords  | 098000h-09FFFFh |

|      | BA20  | 32 Kwords  | 0A0000h-0A7FFFh |

|      | BA21  | 32 Kwords  | 0A8000h-0AFFFFh |

|      | BA22  | 32 Kwords  | 0B0000h-0B7FFFh |

|      | BA23  | 32 Kwords  | 0B8000h-0BFFFFh |

|      | BA24  | 32 Kwords  | 0C0000h-0C7FFFh |

|      | BA25  | 32 Kwords  | 0C8000h-0CFFFFh |

|      | BA26  | 32 Kwords  | 0D0000h-0D7FFFh |

|      | BA27  | 32 Kwords  | 0D8000h-0DFFFFh |

|      | BA28  | 32 Kwords  | 0E0000h-0E7FFFh |

|      | BA29  | 32 Kwords  | 0E8000h-0EFFFFh |

|      | BA30  | 32 Kwords  | 0F0000h-0F7FFFh |

|      | BA31  | 32 Kwords  | 0F8000h-0FFFFh  |

|      | BA32  | 32 Kwords  | 100000h-107FFFh |

|      | BA33  | 32 Kwords  | 108000h-10FFFFh |

|      | BA34  | 32 Kwords  | 110000h-117FFFh |

| С    | BA35  | 32 Kwords  | 118000h-11FFFFh |

|      | BA36  | 32 Kwords  | 120000h-127FFFh |

|      | BA37  | 32 Kwords  | 128000h-12FFFFh |

|      | BA38  | 32 Kwords  | 130000h-137FFFh |

|      | BA39  | 32 Kwords  | 138000h-13FFFFh |

|      | BA40  | 32 Kwords  | 140000h-147FFFh |

|      | BA41  | 32 Kwords  | 148000h-14FFFFh |

|      | BA42  | 32 Kwords  | 150000h-157FFFh |

TABLE 11: SST34WA3204, 8 Mbit x4 Concurrent SuperFlash Multi-Bank Memory Organization (2 of 2)

| Bank | Block | Block Size | Address Range   |

|------|-------|------------|-----------------|

|      | BA43  | 32 Kwords  | 158000h-15FFFFh |

|      | BA44  | 32 Kwords  | 160000h-167FFFh |

|      | BA45  | 32 Kwords  | 168000h-16FFFFh |

|      | BA46  | 32 Kwords  | 170000h-177FFFh |

|      | BA47  | 32 Kwords  | 178000h-17FFFFh |

|      | BA48  | 32 Kwords  | 180000h-187FFFh |

|      | BA49  | 32 Kwords  | 188000h-18FFFFh |

|      | BA50  | 32 Kwords  | 190000h-197FFFh |

| D    | BA51  | 32 Kwords  | 198000h-19FFFFh |

|      | BA52  | 32 Kwords  | 1A0000h-1A7FFFh |

|      | BA53  | 32 Kwords  | 1A8000h-1AFFFFh |

|      | BA54  | 32 Kwords  | 1B0000h-1B7FFFh |

|      | BA55  | 32 Kwords  | 1B8000h-1BFFFFh |

|      | BA56  | 32 Kwords  | 1C0000h-1C7FFFh |

|      | BA57  | 32 Kwords  | 1C8000h-1CFFFFh |

|      | BA58  | 32 Kwords  | 1D0000h-1D7FFFh |

|      | BA59  | 32 Kwords  | 1D8000h-1DFFFFh |

|      | BA60  | 32 Kwords  | 1E0000h-1E7FFFh |

|      | BA61  | 32 Kwords  | 1E8000h-1EFFFFh |

|      | BA62  | 32 Kwords  | 1F0000h-1F7FFFh |

|      | BA63  | 8 Kwords   | 1F8000h-1F9FFFh |

|      | BA64  | 8 Kwords   | 1FA000h-1FBFFFh |

|      | BA65  | 8 Kwords   | 1FC000h-1FDFFFh |

|      | BA66  | 8 Kwords   | 1FE000h-1FFFFFh |

T11.0 1340

## **PIN DESCRIPTION**

FIGURE 3: Pin Assignments for 44-ball FBGA (6 x 8 mm)

**Preliminary Specification**

**TABLE 12: Pin Descriptions**

| Symbol                                | Name                           | Functions                                                                                                                                                                |

|---------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>20</sub> -A <sub>16</sub>      | Address Inputs                 | To provide memory addresses.                                                                                                                                             |

| A/DQ <sub>15</sub> -A/DQ <sub>0</sub> | Multiplexed Address/Data       | Sixteen least-significant bit Addresses are multiplexed with Data Input/output. The outputs are in tri-state when OE# or BEF# is high.                                   |

| BEF#                                  | Chip Enable                    | To activate the device when BEF# is low.                                                                                                                                 |

| OE#                                   | Output Enable                  | To gate the data output buffers                                                                                                                                          |

| WE#                                   | Write Enable                   | To control the Write operations                                                                                                                                          |

| RST#                                  | Hardware Reset                 | To reset and return the device to Read mode                                                                                                                              |

| RY/BY#                                | Ready Output                   | To output the status of a Burst Read. "Low" = Data Not Valid, "High" = Data Valid                                                                                        |

| CLK                                   | Clock                          | To increment the internal address counter (after the initial output delay) when the part is in Burst Mode. CLK is not required in asynchronous mode.                     |

| AVD#                                  | Address Valid Input            | To indicate to the device that a valid Address is present on the Address Bus                                                                                             |

| WP#                                   | Write Protect                  | To protect and unprotect top or bottom 8 KWord (4 outermost sectors) from Erase or Program operation.                                                                    |

| A <sub>CC</sub>                       | Vpp Power Supply               | Supervoltage VH (11.4V to 12V) input to enable eight word programming. When at $V_{\text{IL}}$ locks all sectors. Should be at $V_{\text{IH}}$ for all other conditions. |

| $V_{DDQ}$                             | I/O Power Supply               | To provide power for Input/Output Buffers.                                                                                                                               |

| $V_{DD}$                              | Power Supply                   | To provide 1.7-1.95V power supply voltage. $V_{DD}$ and $V_{DDQ}$ need to be shorted together in the application circuit.                                                |

| V <sub>SS</sub>                       | Ground                         |                                                                                                                                                                          |

| V <sub>SSQ</sub>                      | Ground for I/O Power<br>Supply | $V_{\text{SS}}$ and $V_{\text{SSQ}}$ need to be shorted together in the application circuit.                                                                             |

| NC                                    | No Connection                  | Unconnected pins                                                                                                                                                         |

T12.1 1340

## **TABLE 13: Operation Mode Selection**

| Mode                                       | BEF#            | OE#             | WE#             | AVD#            | CLK <sup>1</sup> | A/DQ15-0                       | A <sub>20 -16</sub>                                            | RST#            |

|--------------------------------------------|-----------------|-----------------|-----------------|-----------------|------------------|--------------------------------|----------------------------------------------------------------|-----------------|

| Asynchronous Read                          | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Pulse<br>Low    | X <sup>2</sup>   | I/O                            | AIN                                                            | V <sub>IH</sub> |

| Program                                    | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Pulse<br>Low    | Х                | I/O                            | AIN                                                            | V <sub>IH</sub> |

| Erase                                      | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Pulse<br>Low    | Х                | I/O                            | Sector or block<br>address, XXH <sup>2</sup><br>for Chip-Erase | V <sub>IH</sub> |

| Standby                                    | V <sub>IH</sub> | Х               | Х               | Х               | Х                | High Z                         | Х                                                              | V <sub>IH</sub> |

| Write Inhibit                              | Х               | V <sub>IL</sub> | Х               | Х               | Х                | I/O/ DOUT                      | Х                                                              | V <sub>IH</sub> |

|                                            | X               | Х               | V <sub>IH</sub> | Х               | Х                | High Z / DOUT                  | Х                                                              | V <sub>IH</sub> |

| Hardware Reset                             | Х               | Х               | Х               | Х               | Х                | High Z                         | Х                                                              | V <sub>IL</sub> |

| Product Identification Mode (Manufacturer) | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Х                | Manufacturer's ID (00BFH)      | See Table 9                                                    | See Table 9     |

| Product Identification Mode (Device)       | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Х                | Device ID <sup>3</sup> (xxxxH) | See Table 9                                                    | See Table 9     |

T13.0 1340

- 1. Default Clock Active edge is the rising edge.

- 2. X can be  $V_{\text{IL}}$  or  $V_{\text{IH}},$  but no other value.

- 3. Device ID for SST34WA3203 is 975BH and for SST34WA3204 is 975AH.

**Preliminary Specification**

### **TABLE 14: Burst Mode Selection**

| Mode                                                    | BEF#            | OE#             | WE#             | AVD#            | CLK <sup>1</sup> | DQ         | Address | RST#            |

|---------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------|---------|-----------------|

| Load Starting Burst Address                             | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Pulse<br>Low    | Active Edge      | Х          | AIN     | V <sub>IH</sub> |

| Automatic Address Advance during Burst Read             | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Active Edge      | DOUT       | Х       | V <sub>IH</sub> |

| Terminate Current Burst Read (with BEF#)                | V <sub>IH</sub> | Х               | V <sub>IH</sub> | Х               | Active Edge      | High Z     | Х       | V <sub>IH</sub> |

| Terminate Current Burst Read with RST#                  | Х               | Х               | V <sub>IH</sub> | Х               | Х                | High Z     | Х       | V <sub>IL</sub> |

| Terminate Current Burst Read and Start a New Burst Read | V <sub>IL</sub> | Х               | V <sub>IH</sub> | Pulse<br>Low    | Active Edge      | High Z / X | AIN     | V <sub>IH</sub> |

| Burst Suspend                                           | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х                | High Z     | Х       | V <sub>IH</sub> |

<sup>1.</sup> The Address Latch is reset by BEF# going high, there is no need to wait for the CLK pulse to reset it.

T14.0 1340

**Preliminary Specification**

**TABLE 15: Software Command Sequence**

| Command<br>Sequence                                           | 1st Bus Write<br>Cycle |                   | 2nd Bus Write<br>Cycle                |                                       | 3rd Bus<br>Write Cycle                 |      |                   | 4th Bus Write<br>Cycle |      | 5th Bus<br>Write Cycle |                              | Bus<br>Cycle |

|---------------------------------------------------------------|------------------------|-------------------|---------------------------------------|---------------------------------------|----------------------------------------|------|-------------------|------------------------|------|------------------------|------------------------------|--------------|

|                                                               | Addr <sup>1</sup>      | Data <sup>2</sup> | Addr                                  | Data                                  | Addr                                   | Data | Addr              | Data                   | Addr | Data                   | Addr                         | Data         |

| Word-Program                                                  | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | A0H  | WA <sup>3</sup>   | Data                   |      |                        |                              |              |

| Sector-Erase                                                  | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | 80H  | 555H              | AAH                    | 2AAH | 55H                    | SA <sub>X</sub> <sup>4</sup> | 50H          |

| Block-Erase                                                   | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | 80H  | 555H              | AAH                    | 2AAH | 55H                    | BA <sub>X</sub> <sup>4</sup> | 30H          |

| Chip-Erase                                                    | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | 80H  | 555H              | AAH                    | 2AAH | 55H                    | 555H                         | 10H          |

| Erase-Suspend                                                 | XXXH                   | B0H               |                                       |                                       |                                        |      |                   |                        |      |                        |                              |              |

| Erase-Resume                                                  | XXXH                   | 30H               |                                       |                                       |                                        |      |                   |                        |      |                        |                              |              |

| Block Lock/<br>Unlock <sup>5</sup>                            | XXXH                   | 60H               | XXXH                                  | 60H                                   | BLA <sub>X</sub> <sup>6</sup>          | 60H  |                   |                        |      |                        |                              |              |

| Read Block Lock-<br>ing Register                              | 555H                   | AAH               | 2AAH                                  | 55H                                   | BK <sub>X</sub> 55<br>5H <sup>4</sup>  | 90H  | See<br>Table 17   | See<br>Table 17        |      |                        |                              |              |

| Entry/Query<br>Security ID <sup>7</sup>                       | 555H                   | AAH               | 2AAH                                  | 55H                                   | BK <sub>X</sub> <sup>8</sup><br>555H   | 88H  |                   |                        |      |                        |                              |              |

| User Security ID<br>Program                                   | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | А5Н  | SIWA <sup>9</sup> | Data                   |      |                        |                              |              |

| User Security ID<br>Program Lock-<br>Out                      | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | 85H  | xx                | 0000H                  |      |                        |                              |              |

| Software ID<br>Entry <sup>10, 11</sup>                        | 555H                   | AAH               | 2AAH                                  | 55H                                   | BK <sub>X</sub> 55<br>5H <sup>12</sup> | 90H  | See<br>Table 17   | See<br>Table 17        |      |                        |                              |              |

| CFI Query Entry                                               | BK <sub>X</sub> X55H   | 98H               |                                       |                                       |                                        |      |                   |                        |      |                        |                              |              |

| Software ID Exit <sup>8,</sup> <sup>13,11</sup> /CFI Exit/Sec | XXH                    | F0H               |                                       |                                       |                                        |      |                   |                        |      |                        |                              |              |

| ID Exit  CFI Query Entry (3 cycles)                           | 555H                   | AAH               | 2AAH                                  | 55H                                   | BK <sub>X</sub> 55<br>5H               | 98H  |                   |                        |      |                        |                              |              |

| Software ID Exit/<br>CFI Exit/ Security<br>ID Exit (3 cycles) | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | F0H  |                   |                        |      |                        |                              |              |

| Set Burst Mode<br>Configuration<br>Register                   | 555H                   | AAH               | 2AAH                                  | 55H                                   | CR <sub>X</sub> 55<br>5H <sup>14</sup> | C0H  |                   |                        |      |                        |                              |              |

| Eight Word Pro-<br>gram                                       | XXH                    | A0H <sup>15</sup> | See Table<br>16 for Bus<br>Cycle Seq. | See Table<br>16 for Bus<br>Cycle Seq. |                                        |      |                   |                        |      |                        |                              |              |

| Programming<br>Acceleration<br>Mode Entry                     | 555H                   | AAH               | 2AAH                                  | 55H                                   | 555H                                   | 20H  |                   |                        |      |                        |                              |              |

| Programming<br>Acceleration Pro-<br>gram <sup>16</sup>        | XXH                    | A0H               | WA                                    | Data                                  |                                        |      |                   |                        |      |                        |                              |              |

| Programming<br>Acceleration Program Reset <sup>17</sup>       | XXH                    | 90H               | XXH                                   | 00H                                   |                                        |      |                   |                        |      |                        |                              |              |

T15.0 1340

<sup>1.</sup> Address format  $A_{11}$ - $A_0$  (Hex) Addresses  $A_{12}$ - $A_{20}$  can be  $V_{IL}$  or  $V_{IH}$ , but no other value, for Command sequence of SST34WA3203/3204.

#### Preliminary Specification

- 2.  $DQ_{15}$ - $DQ_{8}$  can be  $V_{IL}$  or  $V_{IH}$ , but no other value, for Command sequence

- 3. WA = Program Word address.

- 4. SA<sub>X</sub> for Sector-Erase; uses A<sub>20</sub>-A<sub>11</sub> address lines BA<sub>X</sub> for Block-Erase; uses A<sub>20</sub>-A<sub>13</sub> address lines

- 5. BLR indicates Block Locking Register Data: 0000H = Block Unlocked, 0001H = Block Locked.

- BLA<sub>X</sub> indicates the Address of the Block to be Locked/Unlocked; uses A<sub>20</sub> -A<sub>13</sub> address lines. This is composed by the Block Address (BA) and either  $A_6 = 1$  to Unlock or  $A_6 = 0$  to Lock.

- 7. With  $A_{20}$ - $A_8$  = 0; Security ID information is read with  $A_7$ - $A_0$

- SST Factory Unique Id is read at Address Range: 000000H to 000007H (128-bit). This segment is always locked by SST. User ID is read at Address range: 000080H to 0000FFH (128-words).

- Lock Status of User Segment is read with A7 to A0 = 00007FH. Unlocked: DQ3 = 1 / Locked: DQ3 = 0.

- 8. BK<sub>X</sub> indicates the Bank Address: uses A<sub>20</sub> -A<sub>19</sub> address lines.

- 9. SIWA: Security ID Program Word Address: User ID can be written at Address range: 000080H to 0000FFH (128-words).

- 10. The device does not remain in Software Product Identification mode if Powered Down.

- 11. With A<sub>18</sub>-A<sub>1</sub> = 0 and A<sub>20</sub>-A<sub>19</sub> = BK (Bank Address), address of the Bank that is being switched to Software ID Mode: SST Manufacturer ID = 00BFH, is read with A1 = 0 and A0 = 0 SST34WA3203 Device ID = 975BH, is read with A1 = 0 and A0 = 1

- SST34WA3204 Device ID = 975AH, is read with A1 = 0 and A0 = 1

- 12. If users never lock after programming, Sec ID can be programmed over the previously unprogrammed bits (data=1) using the Sec ID mode again (the programmed "0" bits cannot be reversed to "1"). Valid Word-Addresses for User Security ID are from 000080H to

- 13. Both Software ID Exit operations are equivalent.

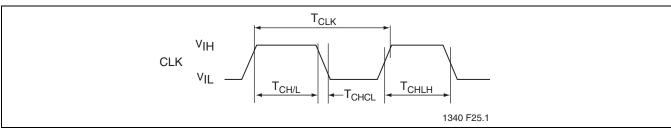

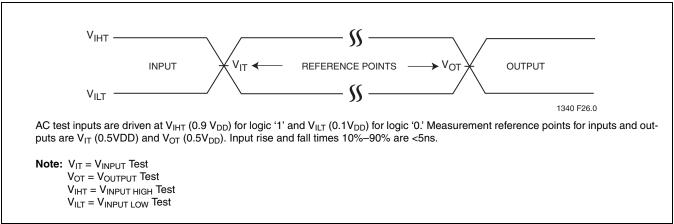

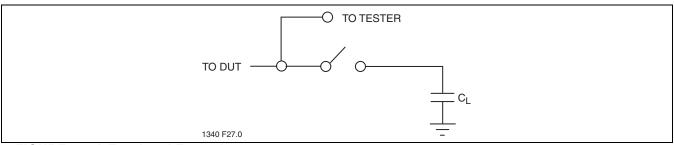

- 14. CR = Burst Mode Configuration Register Value on A<sub>17</sub>-A<sub>12</sub> (see Programmable Wait State Configuration Section).