# HD66702 (LCD-II/E20)

(Dot Matrix Liquid Crystal Display Controller/Driver)

# **HITACHI**

# **Description**

The HD66702 LCD-II/E20 dot-matrix liquid crystal display controller and driver LSI displays alphanumerics, Japanese kana characters, and symbols. It can be configured to drive a dot-matrix liquid crystal display under the control of a 4- or 8-bit microprocessor. Since all the functions required for driving a dot-matrix liquid crystal display are internally provided on one chip, a minimal system can be interfaced with this controller/driver.

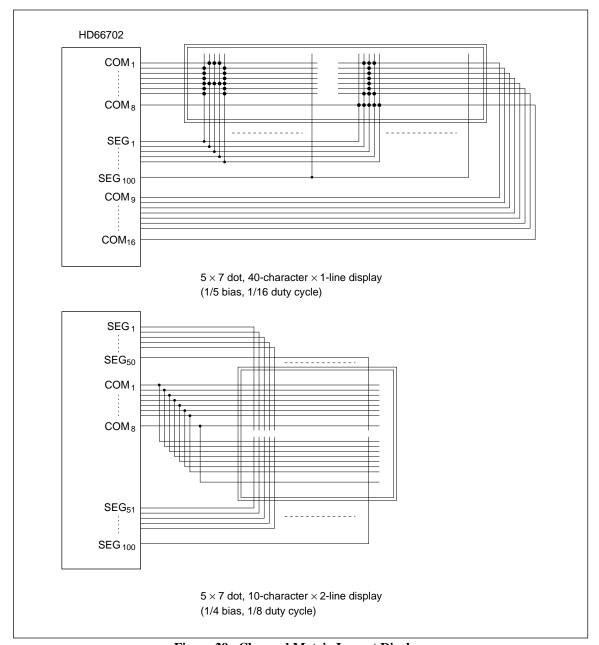

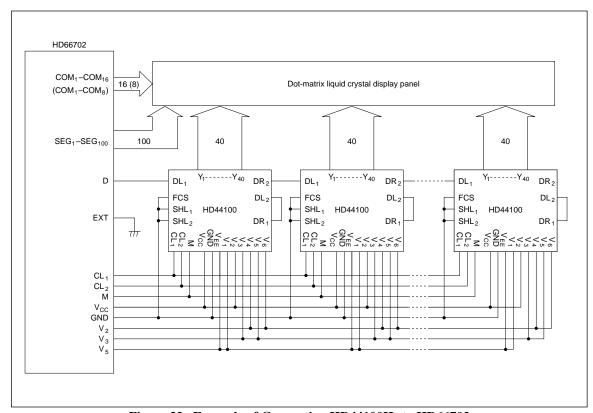

A single LCD-II/E20 can display up to two 20-character lines. However, with the addition of HD44100 drivers, a maximum of up to two 40-character lines can be displayed.

The low 3-V power supply of the LCD-II/E20 under development is suitable for any portable battery-driven product requiring low power dissipation.

#### **Features**

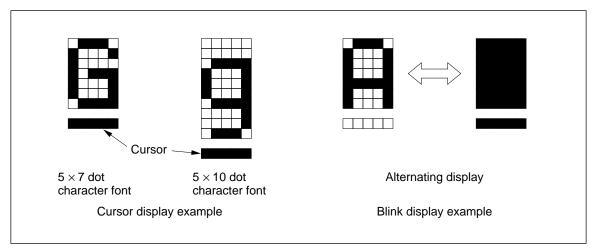

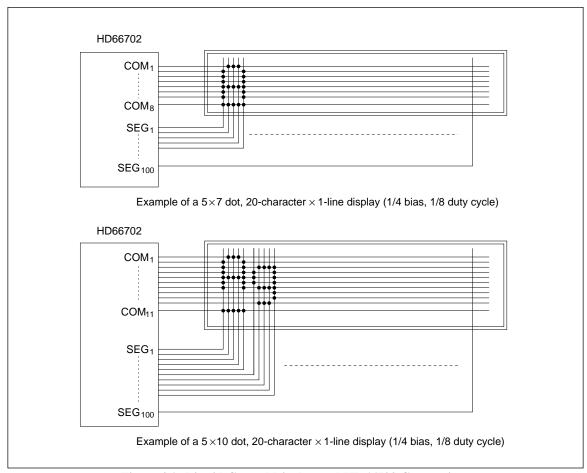

- $5 \times 7$  and  $5 \times 10$  dot matrix possible

- 80 × 8-bit display RAM (80 characters max.)

- 7,200-bit character generator ROM

- 160 character fonts ( $5 \times 7$  dot)

- 32 character fonts ( $5 \times 10 \text{ dot}$ )

- 64 × 8-bit character generator RAM

- 8 character fonts (5 × 7 dot)

- 4 character fonts  $(5 \times 10 \text{ dot})$

- 16-common × 100-segment liquid crystal display driver

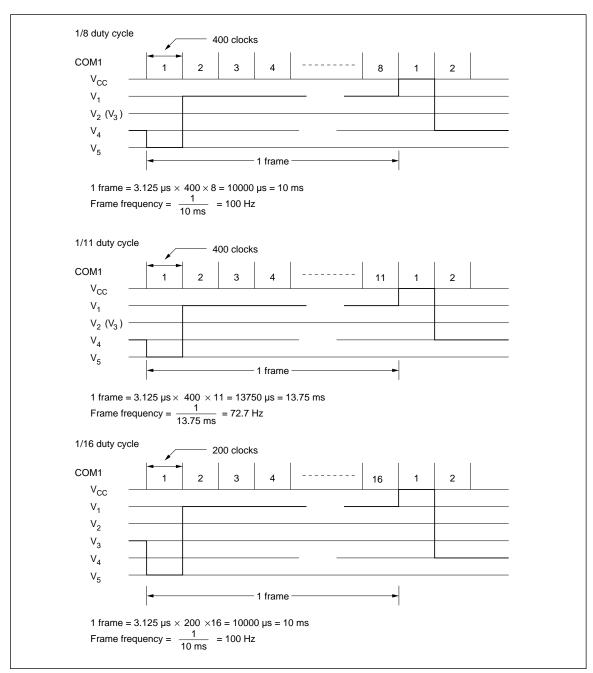

- Programmable duty cycles

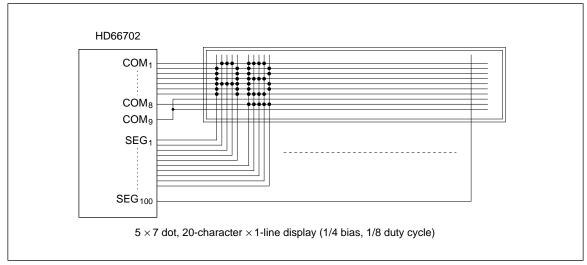

- 1/8 for one line of  $5 \times 7$  dots with cursor

- 1/11 for one line of  $5 \times 10$  dots with cursor

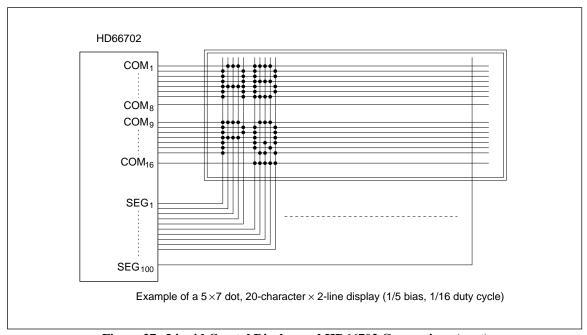

- 1/16 for two lines of  $5 \times 7$  dots with cursor

- Maximum display characters

- One line

- 1/8 duty cycle, 20-char. × 1-line (no extension), 28-char. × 1-line (extended with one HD44100R), 80-char. × 1-line (max. extension with eight HD44100s). 1/11 duty cycle, 20-char. × 1-line (no extension), 28-char. × 1-line (extended with one HD44100R), 80-char. × 1-line (max. extension with eight HD44100Rs)

- Two lines

- 1/16 duty cycle, 20-char. × 2-line (no extension), 28-char. × 2-line (extended with one HD44100R), 40-char. × 2-line (max. extension with eight HD44100Rs)

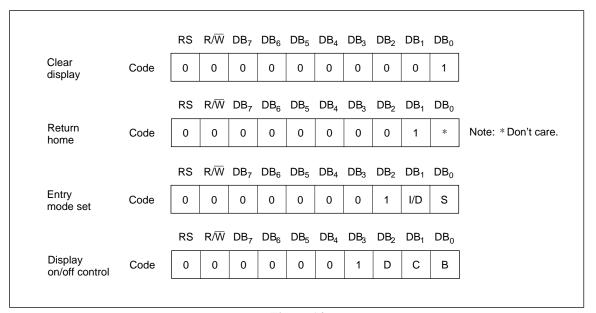

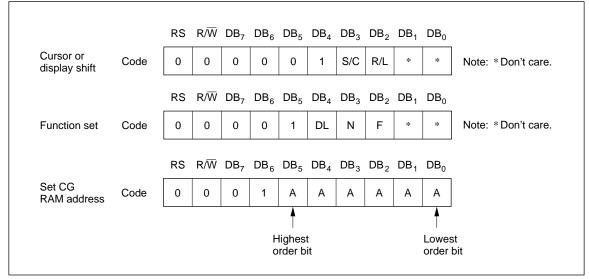

- · Wide range of instruction functions

- Display clear, cursor home, display on/off, cursor on/off, display character blink, cursor shift, display shift

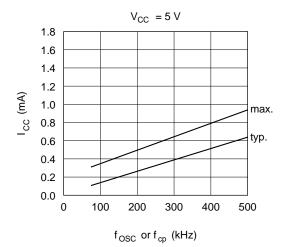

- Choice of power supply (V<sub>CC</sub>): 4.5 to 5.5 V (standard), 2.7 to 5.5 V (low voltage)

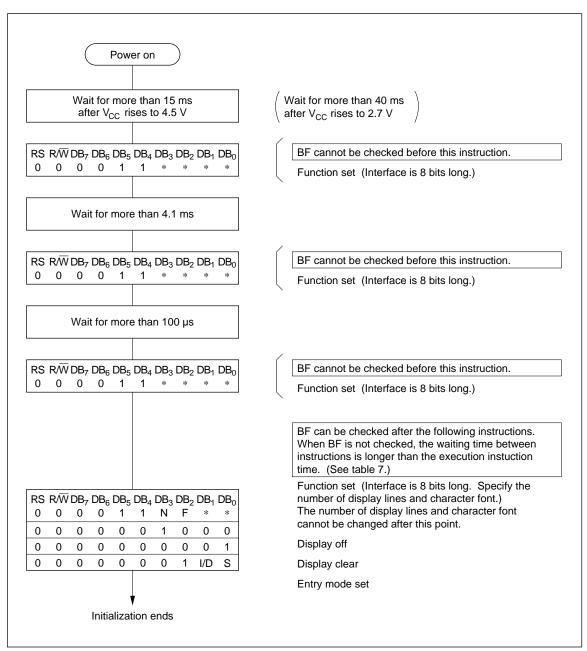

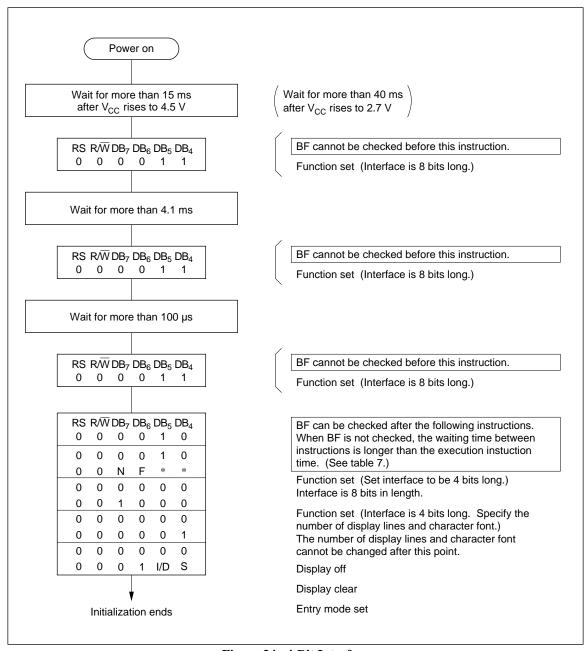

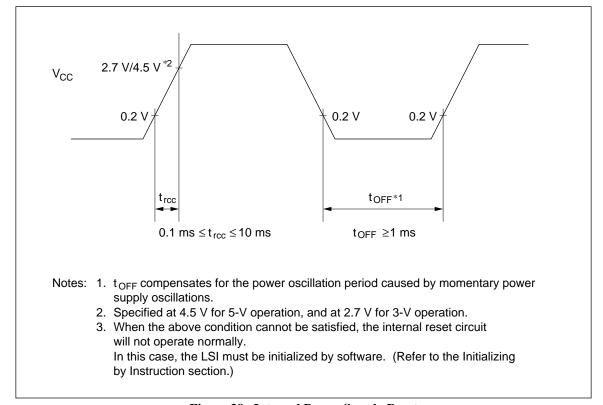

- Automatic reset circuit that initializes the controller/driver after power on (standard version only)

- Independent LCD drive voltage driven off of the logic power supply (V<sub>CC</sub>): 3.0 to 8.3 V

# **Ordering Information**

| Type No.      | Package                       | Operating Voltage | ROM Font                              |

|---------------|-------------------------------|-------------------|---------------------------------------|

| HCD66702RA00L | Chip                          | 2.7 to 5.5 V      | Standard Japanese                     |

| HD66702RA00F  | 144-pin plastic QFP (FP-144A) | 4.5 to 5.5 V      | font                                  |

| HD66702RA00FL | 144-pin plastic QFP (FP-144A) | 2.7 to 5.5 V      |                                       |

| HD66702RA01F  | 144-pin plastic QFP (FP-144A) | 4.5 to 5.5 V      | Japanese font for comunication system |

| HD66702RA02F  | 144-pin plastic QFP (FP-144A) | 4.5 to 5.5 V      | European font                         |

| HCD66702RBxxL | Chip                          | 2.7 to 5.5 V      | Custom font                           |

| HD66702RBxxF  | 144-pin plastic QFP (FP-144A) | 4.5 to 5.5 V      | _                                     |

| HD66702RBxxFL | 144-pin plastic QFP (FP-144A) | 2.7 to 5.5 V      |                                       |

Note: xx: ROM code No.

# **LCD-II Family Comparison**

| Item                                                      |          | LCD-II (HD44780U)                                                                                              | LCD-II/E20 (HD66702)                                                                                  |

|-----------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Power supply voltage                                      |          | 2.7 to 5.5 V                                                                                                   | 5 V ±10% (standard)<br>2.7 to 5.5 V (low voltage)                                                     |

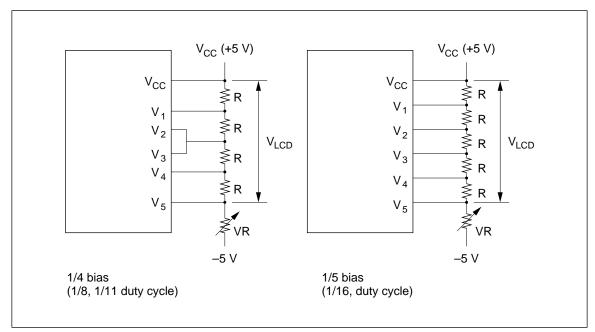

| Liquid crystal drive                                      | 1/4 bias | 3.0 to 11 V                                                                                                    | 3.0 to 8.3 V                                                                                          |

| voltage V <sub>LCD</sub>                                  | 1/5 bias | 3.0 to 11 V                                                                                                    | 3.0 to 8.3 V                                                                                          |

| Maximum display digits per chip                           |          | 16 digits<br>(8 digits × 2 lines)                                                                              | 40 digits<br>(20 digits × 2 lines)                                                                    |

| Display duty cycle                                        |          | 1/8, 1/11, and 1/16                                                                                            | 1/8, 1/11, and 1/16                                                                                   |

| CGROM                                                     |          | 9,600 bits<br>(208 character fonts<br>for $5 \times 8$ dot and<br>32 character fonts<br>for $5 \times 10$ dot) | 7,200 bits<br>(160 character fonts for $5 \times 7$ dot and 32 character fonts for $5 \times 10$ dot) |

| CGRAM                                                     |          | 64 bytes                                                                                                       | 64 bytes                                                                                              |

| DDRAM                                                     |          | 80 bytes                                                                                                       | 80 bytes                                                                                              |

| Segment signals                                           |          | 40                                                                                                             | 100                                                                                                   |

| Common signals                                            |          | 16                                                                                                             | 16                                                                                                    |

| Liquid crystal drive wa                                   | aveform  | A                                                                                                              | В                                                                                                     |

| Ladder resistor for LC power supply                       | D        | External                                                                                                       | External                                                                                              |

| Clock source                                              |          | External resistor or external clock                                                                            | External resistor or external clock                                                                   |

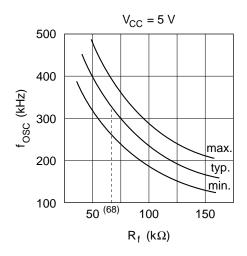

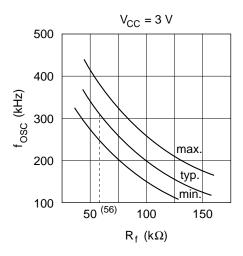

| R <sub>f</sub> oscillation frequency<br>(frame frequency) | ру       | 270 kHz ±30%<br>(59 to 110 Hz for 1/8 and<br>1/16 duty cycles; 43 to 80 Hz<br>for 1/11 duty cycle)             | 320 kHz ±30%<br>(69 to 128 Hz for 1/8 and<br>1/16 duty cycles; 50 to 93 Hz<br>for 1/11 duty cycle)    |

| R <sub>f</sub> resistance                                 |          | 91 kΩ ±2% (5 V)<br>75 kΩ ±2% (3 V)                                                                             | 68 kΩ ±2% (5 V)<br>56 kΩ ±2% (3 V)                                                                    |

| Instructions                                              |          | Fully compatible within the LCD                                                                                | 9-II family                                                                                           |

| CPU bus timing                                            |          | 1 MHz                                                                                                          | 1 MHz                                                                                                 |

| Package                                                   |          | FP-80B, TFP-80, and 80-pin bare chip (no package)                                                              | 144-pin bare chip (no package)<br>and FP-144A                                                         |

270

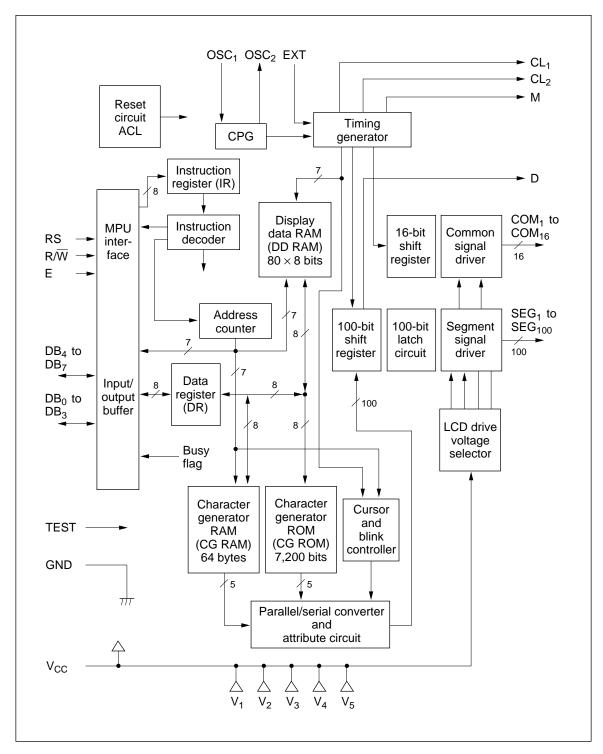

# LCD-II/E20 Block Diagram

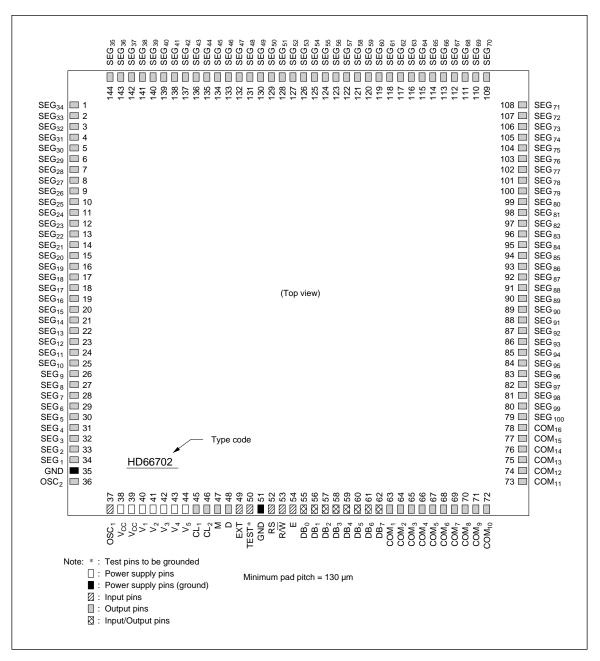

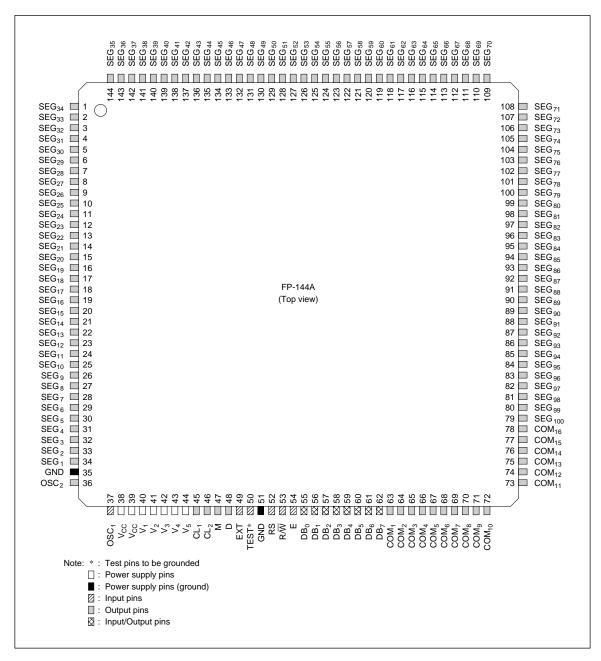

# LCD-II/E20 Pad Arrangement

# **HCD66702 Pad Location Coordinates**

| Pad | Pad               |        |                  |

|-----|-------------------|--------|------------------|

| No. | Name              | Χ (μm) | Υ (μm)           |

| 1   | SEG <sub>34</sub> | -2475  | 2350             |

| 2   | SEG <sub>33</sub> | -2475  | 2205             |

| 3   | SEG <sub>32</sub> | -2475  | 2065             |

| 4   | SEG <sub>31</sub> | -2475  | 1925             |

| 5   | SEG <sub>30</sub> | -2475  | 1790             |

| 6   | SEG <sub>29</sub> | -2475  | 1655             |

| 7   | SEG <sub>28</sub> | -2475  | 1525             |

| 8   | SEG <sub>27</sub> | -2475  | 1395             |

| 9   | SEG <sub>26</sub> | -2475  | 1265             |

| 10  | SEG <sub>25</sub> | -2475  | 1135             |

| 11  | SEG <sub>24</sub> | -2475  | 1005             |

| 12  | SEG <sub>23</sub> | -2475  | 875              |

| 13  | SEG <sub>22</sub> | -2475  | 745              |

| 14  | SEG <sub>21</sub> | -2475  | 615              |

| 15  | SEG <sub>20</sub> | -2475  | 485              |

| 16  | SEG <sub>19</sub> | -2475  | 355              |

| 17  | SEG <sub>18</sub> | -2475  | 225              |

| 18  | SEG <sub>17</sub> | -2475  | 95               |

| 19  | SEG <sub>16</sub> | -2475  | <b>–</b> 35      |

| 20  | SEG <sub>15</sub> | -2475  | -165             |

| 21  | SEG <sub>14</sub> | -2475  | -295             |

| 22  | SEG <sub>13</sub> | -2475  | -425             |

| 23  | SEG <sub>12</sub> | -2475  | <b>-</b> 555     |

| 24  | SEG <sub>11</sub> | -2475  | -685             |

| 25  | SEG <sub>10</sub> | -2475  | <del>-</del> 815 |

| 26  | SEG <sub>9</sub>  | -2475  | -945             |

| 27  | SEG <sub>8</sub>  | -2475  | -1075            |

| 28  | SEG <sub>7</sub>  | -2475  | -1205            |

| 29  | SEG <sub>6</sub>  | -2475  | -1335            |

| 30  | SEG <sub>5</sub>  | -2475  | -1465            |

|     |                   |        |                  |

| 31         SEG <sub>4</sub> -2475         -1600           32         SEG <sub>3</sub> -2475         -1735           33         SEG <sub>2</sub> -2475         -1870           34         SEG <sub>1</sub> -2475         -2010           35         GND         -2475         -2180           36         OSC <sub>2</sub> -2475         -2325           37         OSC <sub>1</sub> -2445         -2475           38         V <sub>CC</sub> -2305         -2475           40         V <sub>1</sub> -2025         -2475           40         V <sub>1</sub> -2025         -2475           40         V <sub>1</sub> -2025         -2475           41         V <sub>2</sub> -1875         -2475           42         V <sub>3</sub> -1745         -2475           43         V <sub>4</sub> -1595         -2475           44         V <sub>5</sub> -1465         -2475           45         CL <sub>1</sub> -1335         -2475           46         CL <sub>2</sub> -1185         -2475           48         D         -905         -2475           49         EXT         -775         -2475 | Pad<br>No. | Pad<br>Name      | Χ (μm)      | Υ (μm) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-------------|--------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31         | SEG <sub>4</sub> | -2475       | -1600  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32         | SEG <sub>3</sub> | -2475       | -1735  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33         | SEG <sub>2</sub> | -2475       | -1870  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34         | SEG <sub>1</sub> | -2475       | -2010  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35         | GND              | -2475       | -2180  |

| 38         V <sub>CC</sub> -2305         -2475           39         V <sub>CC</sub> -2165         -2475           40         V <sub>1</sub> -2025         -2475           41         V <sub>2</sub> -1875         -2475           42         V <sub>3</sub> -1745         -2475           43         V <sub>4</sub> -1595         -2475           44         V <sub>5</sub> -1465         -2475           45         CL <sub>1</sub> -1335         -2475           46         CL <sub>2</sub> -1185         -2475           47         M         -1055         -2475           48         D         -905         -2475           49         EXT         -775         -2475           50         TEST         -625         -2475           51         GND         -495         -2475           52         RS         -345         -2475           53         R/W         -195         -2475           54         E         -45         -2475           55         DB <sub>0</sub> 85         -2475           56         DB <sub>1</sub> 235         -2475           58                           | 36         | OSC <sub>2</sub> | -2475       | -2325  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37         | OSC <sub>1</sub> | -2445       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38         | V <sub>CC</sub>  | -2305       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39         | V <sub>CC</sub>  | -2165       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40         |                  | -2025       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41         | $V_2$            | -1875       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42         | $V_3$            | -1745       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43         | $V_4$            | -1595       | -2475  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44         | $V_5$            | -1465       | -2475  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45         | CL <sub>1</sub>  | -1335       | -2475  |

| 48 D -905 -2475 49 EXT -775 -2475 50 TEST -625 -2475 51 GND -495 -2475 52 RS -345 -2475 53 R/W -195 -2475 54 E -45 -2475 55 DB <sub>0</sub> 85 -2475 56 DB <sub>1</sub> 235 -2475 57 DB <sub>2</sub> 365 -2475 58 DB <sub>3</sub> 515 -2475 59 DB <sub>4</sub> 645 -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46         | CL <sub>2</sub>  | -1185       | -2475  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47         | M                | -1055       | -2475  |

| 50       TEST       -625       -2475         51       GND       -495       -2475         52       RS       -345       -2475         53       R/W       -195       -2475         54       E       -45       -2475         55       DB <sub>0</sub> 85       -2475         56       DB <sub>1</sub> 235       -2475         57       DB <sub>2</sub> 365       -2475         58       DB <sub>3</sub> 515       -2475         59       DB <sub>4</sub> 645       -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48         | D                | -905        | -2475  |

| 51       GND       -495       -2475         52       RS       -345       -2475         53       R/W       -195       -2475         54       E       -45       -2475         55       DB <sub>0</sub> 85       -2475         56       DB <sub>1</sub> 235       -2475         57       DB <sub>2</sub> 365       -2475         58       DB <sub>3</sub> 515       -2475         59       DB <sub>4</sub> 645       -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49         | EXT              | <b>–775</b> | -2475  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50         | TEST             | -625        | -2475  |

| 53     R/W     -195     -2475       54     E     -45     -2475       55     DB <sub>0</sub> 85     -2475       56     DB <sub>1</sub> 235     -2475       57     DB <sub>2</sub> 365     -2475       58     DB <sub>3</sub> 515     -2475       59     DB <sub>4</sub> 645     -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51         | GND              | -495        | -2475  |

| 54     E     -45     -2475       55     DB <sub>0</sub> 85     -2475       56     DB <sub>1</sub> 235     -2475       57     DB <sub>2</sub> 365     -2475       58     DB <sub>3</sub> 515     -2475       59     DB <sub>4</sub> 645     -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52         | RS               | -345        | -2475  |

| 55     DB <sub>0</sub> 85     -2475       56     DB <sub>1</sub> 235     -2475       57     DB <sub>2</sub> 365     -2475       58     DB <sub>3</sub> 515     -2475       59     DB <sub>4</sub> 645     -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53         | $R/\overline{W}$ | -195        | -2475  |

| 56     DB <sub>1</sub> 235     -2475       57     DB <sub>2</sub> 365     -2475       58     DB <sub>3</sub> 515     -2475       59     DB <sub>4</sub> 645     -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54         | E                | <b>-45</b>  | -2475  |

| 57     DB <sub>2</sub> 365     -2475       58     DB <sub>3</sub> 515     -2475       59     DB <sub>4</sub> 645     -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55         | $DB_0$           | 85          | -2475  |

| 58     DB <sub>3</sub> 515     -2475       59     DB <sub>4</sub> 645     -2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56         | DB <sub>1</sub>  | 235         | -2475  |

| 59 DB <sub>4</sub> 645 –2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57         | DB <sub>2</sub>  | 365         | -2475  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58         | DB <sub>3</sub>  | 515         | -2475  |

| 60 DB <sub>5</sub> 795 –2475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59         | DB <sub>4</sub>  | 645         | -2475  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60         | DB <sub>5</sub>  | 795         | -2475  |

| Pad<br>No. | Pad<br>Name                           | Χ (μm) | Υ (μm)           | Pad<br>No.            | Pad<br>Name       | X (μm) | Y (µm) |

|------------|---------------------------------------|--------|------------------|-----------------------|-------------------|--------|--------|

| 61         | DB <sub>6</sub>                       | 925    | —2475            | 91                    | SEG <sub>88</sub> | 2475   | 95     |

| 62         | DB <sub>7</sub>                       | 1075   | -2475<br>-2475   | - <del>91</del><br>92 | SEG <sub>88</sub> | 2475   | 225    |

| 63         | COM <sub>1</sub>                      | 1205   | -2475<br>-2475   | - <del>92</del><br>93 | SEG <sub>86</sub> | 2475   | 355    |

|            | · · · · · · · · · · · · · · · · · · · |        |                  | - <del>93</del><br>94 |                   |        |        |

| 64         | COM <sub>2</sub>                      | 1335   | -2475<br>        |                       | SEG <sub>85</sub> | 2475   | 485    |

| 65         | COM <sub>3</sub>                      | 1465   | -2475<br>-2475   | 95                    | SEG <sub>84</sub> | 2475   | 615    |

| 66         | COM <sub>4</sub>                      | 1595   | -2475<br>-2475   | - <u>96</u>           | SEG <sub>83</sub> | 2475   | 745    |

| 67         | COM <sub>5</sub>                      | 1725   | -2475            | _ 97                  | SEG <sub>82</sub> | 2475   | 875    |

| 68         | COM <sub>6</sub>                      | 1855   | -2475            | _ 98                  | SEG <sub>81</sub> | 2475   | 1005   |

| 69         | COM <sub>7</sub>                      | 1990   | -2475            | 99                    | SEG <sub>80</sub> | 2475   | 1135   |

| 70         | COM <sub>8</sub>                      | 2125   | <del>-2475</del> | 100                   | SEG <sub>79</sub> | 2475   | 1265   |

| 71         | COM <sub>9</sub>                      | 2265   | -2475            | 101                   | SEG <sub>78</sub> | 2475   | 1395   |

| 72         | COM <sub>10</sub>                     | 2410   | -2475            | 102                   | SEG <sub>77</sub> | 2475   | 1525   |

| 73         | COM <sub>11</sub>                     | 2475   | -2290            | 103                   | SEG <sub>76</sub> | 2475   | 1655   |

| 74         | COM <sub>12</sub>                     | 2475   | -2145            | 104                   | SEG <sub>75</sub> | 2475   | 1790   |

| 75         | COM <sub>13</sub>                     | 2475   | -2005            | 105                   | SEG <sub>74</sub> | 2475   | 1925   |

| 76         | COM <sub>14</sub>                     | 2475   | -1865            | 106                   | SEG <sub>73</sub> | 2475   | 2065   |

| 77         | COM <sub>15</sub>                     | 2475   | -1730            | 107                   | SEG <sub>72</sub> | 2475   | 2205   |

| 78         | COM <sub>16</sub>                     | 2475   | -1595            | 108                   | SEG <sub>71</sub> | 2475   | 2350   |

| 79         | SEG <sub>100</sub>                    | 2475   | -1465            | 109                   | SEG <sub>70</sub> | 2320   | 2475   |

| 80         | SEG <sub>99</sub>                     | 2475   | -1335            | 110                   | SEG <sub>69</sub> | 2175   | 2475   |

| 81         | SEG <sub>98</sub>                     | 2475   | -1205            | 111                   | SEG <sub>68</sub> | 2035   | 2475   |

| 82         | SEG <sub>97</sub>                     | 2475   | -1075            | 112                   | SEG <sub>67</sub> | 1895   | 2475   |

| 83         | SEG <sub>96</sub>                     | 2475   | -945             | 113                   | SEG <sub>66</sub> | 1760   | 2475   |

| 84         | SEG <sub>95</sub>                     | 2475   | -815             | 114                   | SEG <sub>65</sub> | 1625   | 2475   |

| 85         | SEG <sub>94</sub>                     | 2475   | -685             | - <u></u><br>115      | SEG <sub>64</sub> | 1495   | 2475   |

| 86         | SEG <sub>93</sub>                     | 2475   | <b>–</b> 555     | - <u></u><br>116      | SEG <sub>63</sub> | 1365   | 2475   |

| 87         | SEG <sub>92</sub>                     | 2475   | <b>–425</b>      | 117                   | SEG <sub>62</sub> | 1235   | 2475   |

| 88         | SEG <sub>91</sub>                     | 2475   | -295             | 118                   | SEG <sub>61</sub> | 1105   | 2475   |

| 89         | SEG <sub>90</sub>                     | 2475   |                  | 119                   | SEG <sub>60</sub> | 975    | 2475   |

| 90         | SEG <sub>89</sub>                     | 2475   | <b>–35</b>       | 120                   | SEG <sub>59</sub> | 845    | 2475   |

| Pad<br>No. | Pad<br>Name       | Χ (μm)           | Υ (μm) | Pad<br>No. | Pad<br>Name       | Χ (μm) | Υ (μm) |

|------------|-------------------|------------------|--------|------------|-------------------|--------|--------|

| 121        | SEG <sub>58</sub> | 715              | 2475   | 133        | SEG <sub>46</sub> | -845   | 2475   |

| 122        | SEG <sub>57</sub> | 585              | 2475   | 134        | SEG <sub>45</sub> | -975   | 2475   |

| 123        | SEG <sub>56</sub> | 455              | 2475   | 135        | SEG <sub>44</sub> | -1105  | 2475   |

| 124        | SEG <sub>55</sub> | 325              | 2475   | 136        | SEG <sub>43</sub> | -1235  | 2475   |

| 125        | SEG <sub>54</sub> | 195              | 2475   | 137        | SEG <sub>42</sub> | -1365  | 2475   |

| 126        | SEG <sub>53</sub> | 65               | 2475   | 138        | SEG <sub>41</sub> | -1495  | 2475   |

| 127        | SEG <sub>52</sub> | -65              | 2475   | 139        | SEG <sub>40</sub> | -1625  | 2475   |

| 128        | SEG <sub>51</sub> | -195             | 2475   | 140        | SEG <sub>39</sub> | -1760  | 2475   |

| 129        | SEG <sub>50</sub> | -325             | 2475   | 141        | SEG <sub>38</sub> | -1895  | 2475   |

| 130        | SEG <sub>49</sub> | -455             | 2475   | 142        | SEG <sub>37</sub> | -2035  | 2475   |

| 131        | SEG <sub>48</sub> | -585             | 2475   | 143        | SEG <sub>36</sub> | -2175  | 2475   |

| 132        | SEG <sub>47</sub> | <del>-</del> 715 | 2475   | 144        | SEG <sub>35</sub> | -2320  | 2475   |

Notes: 1. Coordinates originate from the chip center.

<sup>2.</sup> The above are preliminary specifications, and may be subject to change.

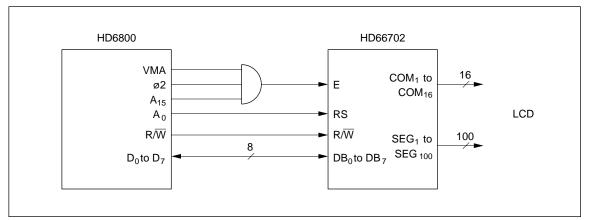

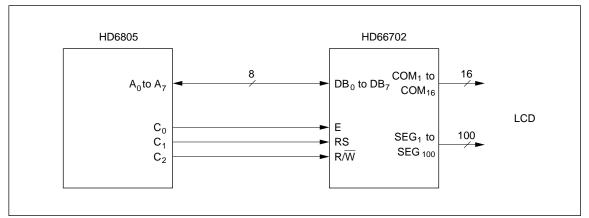

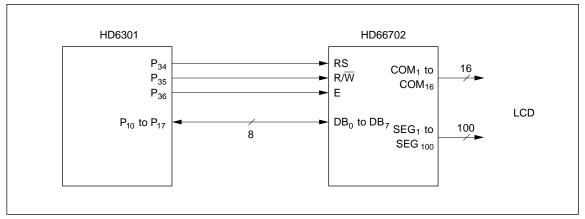

# **HD66702 Pin Arrangement**

# **Pin Functions**

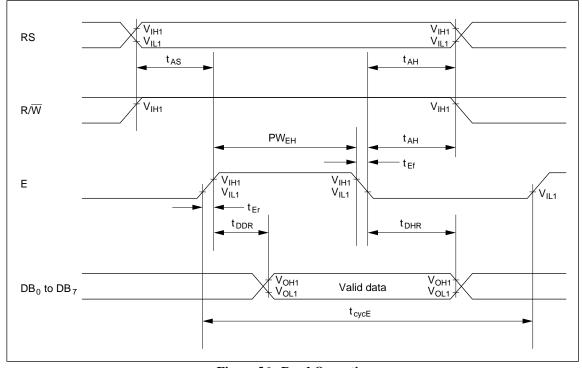

Table 1

Pin Functional Description

| Signal                                 | I/O | Device<br>Interfaced with | Function                                                                                                                                                                                                                                                |

|----------------------------------------|-----|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS                                     | I   | MPU                       | Selects registers 0: Instruction register (for write) Busy flag: address counter (for read) 1: Data register (for write and read)                                                                                                                       |

| R/W                                    | I   | MPU                       | Selects read or write 0: Write 1: Read                                                                                                                                                                                                                  |

| E                                      | I   | MPU                       | Starts data read/write                                                                                                                                                                                                                                  |

| DB <sub>4</sub> to DB <sub>7</sub>     | I/O | MPU                       | Four high order bidirectional tristate data bus pins. Used for data transfer between the MPU and the LCD-II/E20. DB <sub>7</sub> can be used as a busy flag.                                                                                            |

| DB <sub>0</sub> to DB <sub>3</sub>     | I/O | MPU                       | Four low order bidirectional tristate data bus pins. Used for data transfer between the MPU and the LCD-II/E20. These pins are not used during 4-bit operation.                                                                                         |

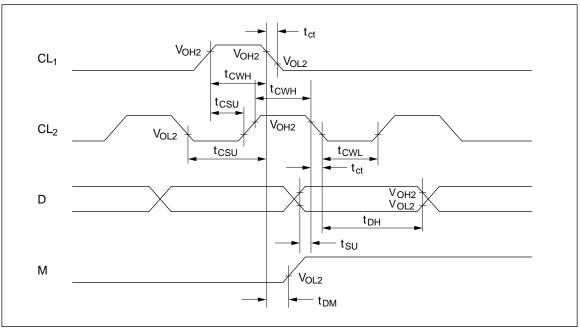

| CL <sub>1</sub>                        | 0   | HD44100                   | Clock to latch serial data D sent to the HD44100H driver                                                                                                                                                                                                |

| CL <sub>2</sub>                        | 0   | HD44100                   | Clock to shift serial data D                                                                                                                                                                                                                            |

| M                                      | 0   | HD44100                   | Switch signal for converting the liquid crystal drive waveform to AC                                                                                                                                                                                    |

| D                                      | 0   | HD44100                   | Character pattern data corresponding to each segment signal                                                                                                                                                                                             |

| COM <sub>1</sub> to COM <sub>16</sub>  | 0   | LCD                       | Common signals that are not used are changed to non-selection waveforms. ${\rm COM_9}$ to ${\rm COM_{16}}$ are non-selection waveforms at 1/8 duty factor and ${\rm COM_{12}}$ to ${\rm COM_{16}}$ are non-selection waveforms at 1/11 duty factor.     |

| SEG <sub>1</sub> to SEG <sub>100</sub> | 0   | LCD                       | Segment signals                                                                                                                                                                                                                                         |

| $V_1$ to $V_5$                         | _   | Power supply              | Power supply for LCD drive                                                                                                                                                                                                                              |

| V <sub>CC</sub> , GND                  | _   | Power supply              | V <sub>CC</sub> : +5 V or +3 V, GND: 0 V                                                                                                                                                                                                                |

| TEST                                   | ı   | _                         | Test pin, which must be grounded                                                                                                                                                                                                                        |

| EXT                                    | I   | _                         | <ul> <li>0: Enables extension driver control signals CL<sub>1</sub>, CL<sub>2</sub>, M, and D to be output from its corresponding pins.</li> <li>1: Drives CL<sub>1</sub>, CL<sub>2</sub>, M, and D as tristate, lowering power dissipation.</li> </ul> |

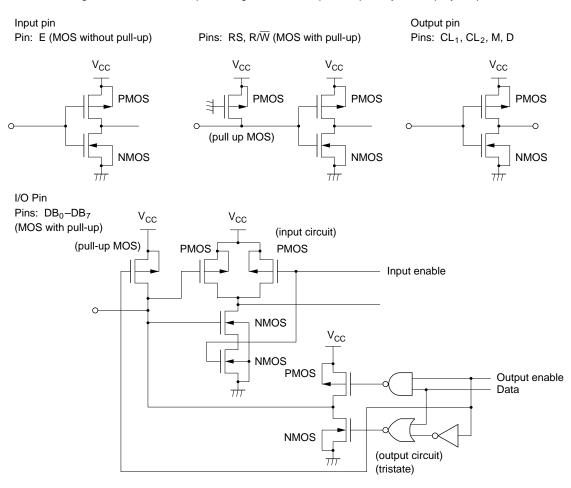

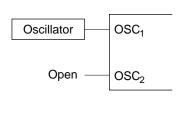

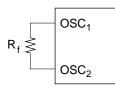

| OSC <sub>1</sub> , OSC <sub>2</sub>    | _   | _                         | Pins for connecting the registers of the internal clock oscillation. When the pin input is an external clock, it must be input to OSC <sub>1</sub> .                                                                                                    |

# **Function Description**

## Registers

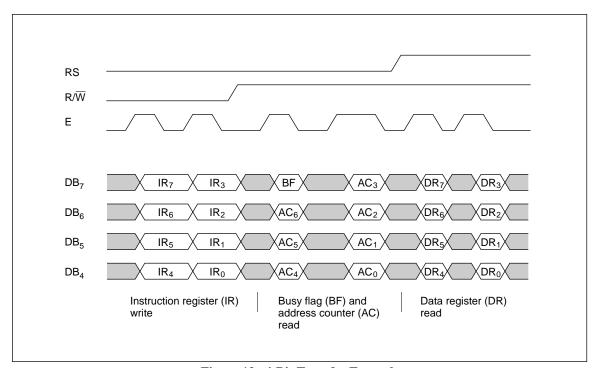

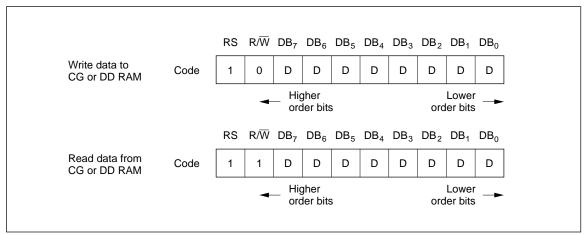

The HD66702 has two 8-bit registers, an instruction register (IR) and a data register (DR).

The IR stores instruction codes, such as display clear and cursor shift, and address information for display data RAM (DD RAM) and character generator RAM (CG RAM). The IR can only be written from the MPU.

The DR temporarily stores data to be written into DD RAM or CG RAM. Data written into the DR from the MPU is automatically written into DD RAM or CG RAM by an internal operation. The DR is also used for data storage when reading data from DD RAM or CG RAM. When address information is written into the IR, data is read and then stored into the DR from DD RAM or CG RAM by an internal operation. Data transfer between the MPU is then completed when the MPU reads the DR. After the read, data in DD RAM or CG RAM at the next address is sent to the DR for the next read from the MPU. By the register selector (RS) signal, these two registers can be selected (table 2).

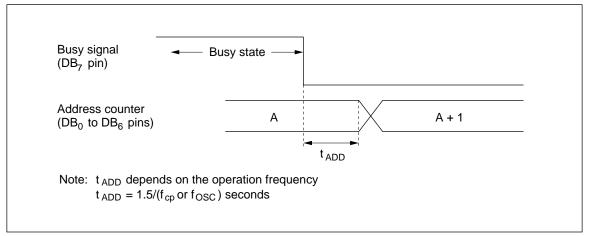

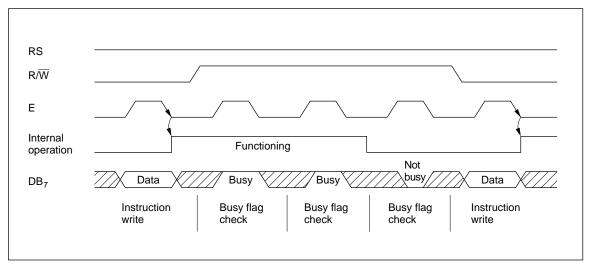

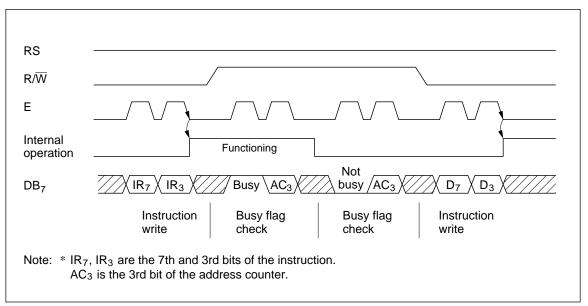

## Busy Flag (BF)

When the busy flag is 1, the HD66702 is in the internal operation mode, and the next instruction will not be accepted. When RS = 0 and R/W = 1 (table 2), the busy flag is output to  $DB_7$ . The next instruction must be written after ensuring that the busy flag is 0.

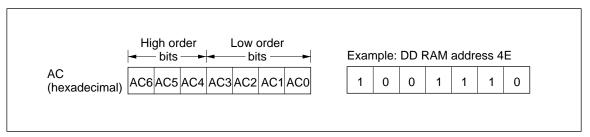

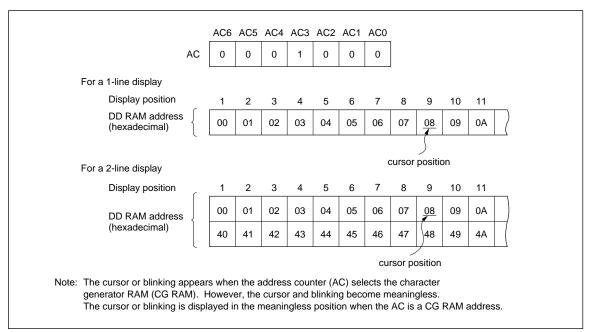

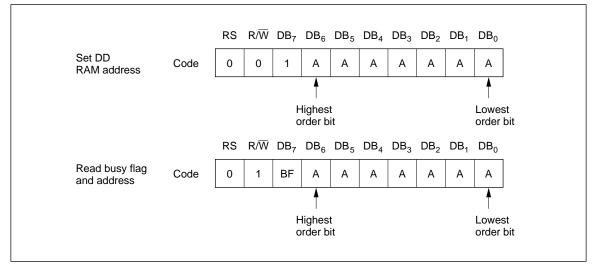

#### Address Counter (AC)

The address counter (AC) assigns addresses to both DD RAM and CG RAM. When an address of an instruction is written into the IR, the address information is sent from the IR to the AC. Selection of either DD RAM or CG RAM is also determined concurrently by the instruction.

After writing into (reading from) DD RAM or CG RAM, the AC is automatically incremented by 1 (decremented by 1). The AC contents are then output to DB<sub>0</sub> to DB<sub>6</sub> when RS = 0 and  $R/\overline{W} = 1$  (table 2).

Table 2

Register Selection

| RS | R/W | Operation                                                                                   |

|----|-----|---------------------------------------------------------------------------------------------|

| 0  | 0   | IR write as an internal operation (display clear, etc.)                                     |

| 0  | 1   | Read busy flag (DB <sub>7</sub> ) and address counter (DB <sub>0</sub> to DB <sub>6</sub> ) |

| 1  | 0   | DR write as an internal operation (DR to DD RAM or CG RAM)                                  |

| 1  | 1   | DR read as an internal operation (DD RAM or CG RAM to DR)                                   |

#### Display Data RAM (DD RAM)

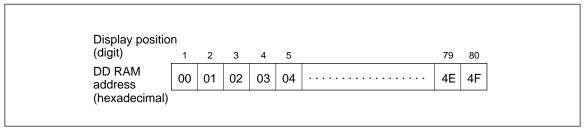

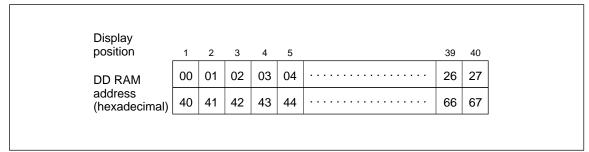

Display data RAM (DD RAM) stores display data represented in 8-bit character codes. Its extended capacity is  $80 \times 8$  bits, or 80 characters. The area in display data RAM (DD RAM) that is not used for display can be used as general data RAM. See figure 1 for the relationships between DD RAM addresses and positions on the liquid crystal display.

The DD RAM address  $(A_{DD})$  is set in the address counter (AC) as hexadecimal.

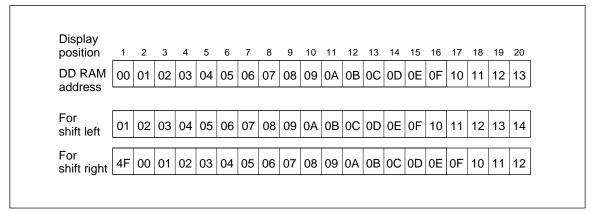

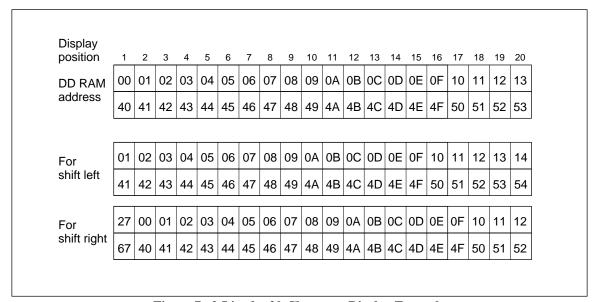

- 1-line display (N = 0) (figure 2)

- Case 1: When there are fewer than 80 display characters, the display begins at the head position. For example, if using only the HD66702, 20 characters are displayed. See figure 3.

When the display shift operation is performed, the DD RAM address shifts. See figure 3.

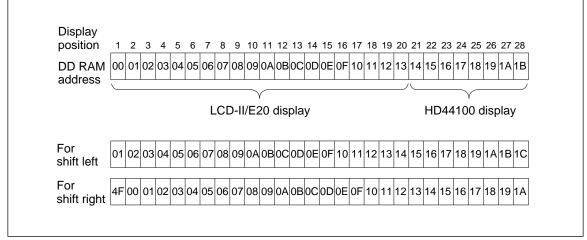

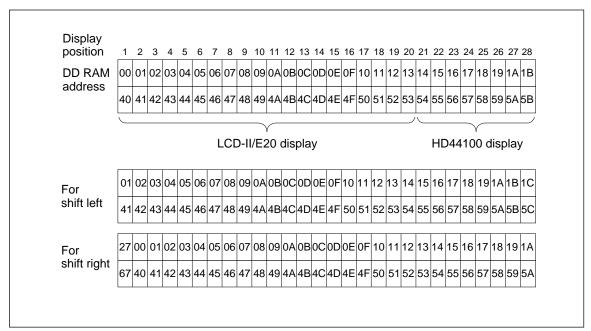

Case 2: For a 28-character display, the HD66702 can be extended using one HD44100 and displayed. See figure 4.

When the display shift operation is performed, the DD RAM address shifts. See figure 4.

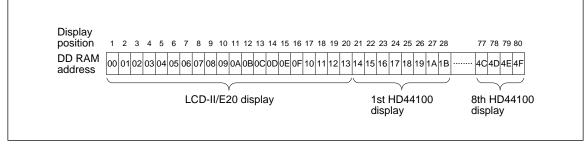

— Case 3: The relationship between the display position and DD RAM address when the number of display digits is increased through the use of two or more HD44100s can be considered as an extension of case #2.

Since the increase can be eight digits per additional HD44100, up to 80 digits can be displayed by externally connecting eight HD44100s. See figure 5.

Figure 1 DD RAM Address

Figure 2 1-Line Display

Figure 3 1-Line by 20-Character Display Example

Figure 4 1-Line by 28-Character Display Example

Figure 5 1-Line by 80-Character Display Example

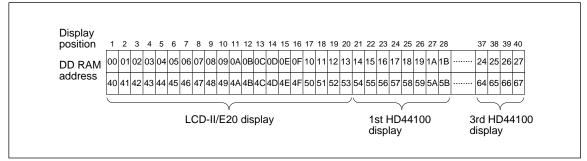

- 2-line display (N = 1) (figure 6)

- Case 1: When the number of display characters is less than 40 × 2 lines, the two lines are displayed from the head. Note that the first line end address and the second line start address are not consecutive. For

example, when just the HD66702 is used, 20 characters  $\times$  2 lines are displayed. See figure 7

When display shift operation is performed, the DD RAM address shifts. See figure 7.

Figure 6 2-Line Display

Figure 7 2-Line by 20-Character Display Example

Case 2: For a 28-character × 2-line display, the HD66702 can be extended using one HD44100. See figure 8.

When display shift operation is performed, the DD RAM address shifts. See figure 8.

Case 3: The relationship between the display position and DD RAM address when the number of display digits is increased by using two or more HD44100s, can be considered as an extension of case #2. See figure 9.

Since the increase can be 8 digits  $\times$  2 lines for each additional HD44100, up to 40 digits  $\times$  2 lines can be displayed by externally connecting three HD44100s.

Figure 8 2-Line by 28-Character Display Example

Figure 9 2-Line by 40-Character Display Example

#### Character Generator ROM (CG ROM)

The character generator ROM generates  $5 \times 7$  dot or  $5 \times 10$  dot character patterns from 8-bit character codes (table 5). It can generate  $160.5 \times 7$  dot character patterns and  $32.5 \times 10$  dot character patterns. User-defined character patterns are also available by mask-programmed ROM.

#### **Character Generator RAM (CG RAM)**

In the character generator RAM, the user can rewrite character patterns by program. For  $5 \times 7$  dots, eight character patterns can be written, and for  $5 \times 10$  dots, four character patterns can be written.

Write the character codes at the addresses shown as the left column of table 5 to show the character patterns stored in CG RAM.

See table 6 for the relationship between CG RAM addresses and data and display patterns.

Areas that are not used for display can be used as general data RAM.

#### **Modifying Character Patterns**

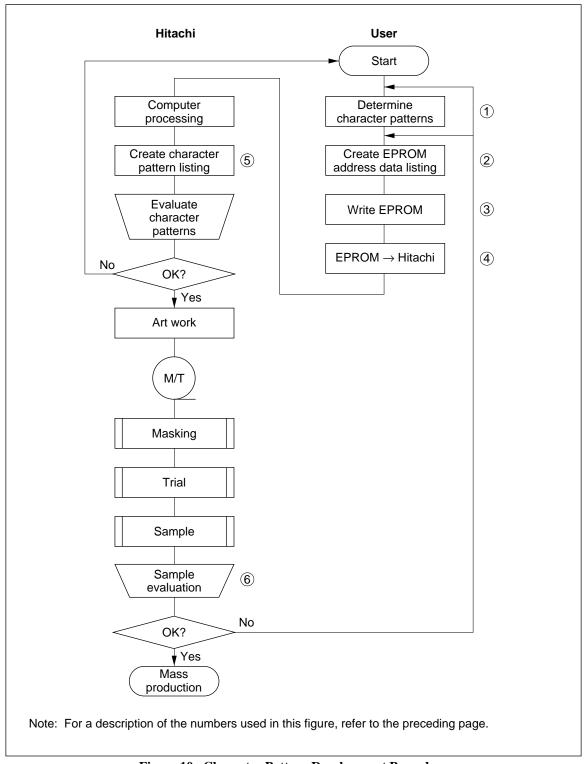

· Character pattern development procedure

The following operations correspond to the numbers listed in figure 10:

- 1. Determine the correspondence between character codes and character patterns.

- 2. Create a listing indicating the correspondence between EPROM addresses and data.

- 3. Program the character patterns into the EPROM.

- 4. Send the EPROM to Hitachi.

- 5. Computer processing on the EPROM is performed at Hitachi to create a character pattern listing, which is sent to the user.

- 6. If there are no problems within the character pattern listing, a trial LSI is created at Hitachi and samples are sent to the user for evaluation. When it is confirmed by the user that the character patterns are correctly written, mass production of the LSI proceeds at Hitachi.

283

Figure 10 Character Pattern Development Procedure

## · Programming character patterns

This section explains the correspondence between addresses and data used to program character patterns in EPROM. The LCD-II/E20 character generator ROM can generate  $160.5 \times 7$  dot character patterns and  $32.5 \times 10$  dot character patterns for a total of 192 different character patterns.

$-5 \times 7$  dot character pattern

EPROM address data and character pattern data correspond with each other to form a  $5 \times 7$  dot character pattern (table 3).

Table 3 Example of Correspondence between EPROM Address Data and Character Pattern  $(5 \times 7 \text{ dots})$

|   |                 |    |      | EPI  | RON            | ΛA             | ddre           | ess |    |                |                |                |                | Data | а |                      |                               |

|---|-----------------|----|------|------|----------------|----------------|----------------|-----|----|----------------|----------------|----------------|----------------|------|---|----------------------|-------------------------------|

|   | A <sub>10</sub> | Α9 | Α8   | Α,   | Α <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | Α3  | Α2 | A <sub>1</sub> | A <sub>0</sub> | O <sub>4</sub> | Ο <sub>3</sub> | 02   |   | SB<br>O <sub>0</sub> |                               |

|   | 0               | 1  | 0    | 1    | 0              | 0              | 1              | 0   | 0  | 0              | 0              | 1              | 1              | 1    | 1 | 0                    |                               |

|   |                 |    |      |      |                |                |                |     | 0  | 0              | 1              | 1              | 0              | 0    | 0 | 1                    |                               |

|   |                 |    |      |      |                |                |                |     | 0  | 1              | 0              | 1              | 0              | 0    | 0 | 1                    |                               |

|   |                 |    |      |      |                |                |                |     | 0  | 1              | 1              | 1              | 1              | 1    | 1 | 0                    |                               |

|   |                 |    |      |      |                |                |                |     | 1  | 0              | 0              | 1              | 0              | 1    | 0 | 0                    |                               |

|   |                 |    |      |      |                |                |                |     | 1  | 0              | 1              | 1              | 0              | 0    | 1 | 0                    |                               |

|   |                 |    |      |      |                |                |                |     | 1  | 1              | 0              | 1              | 0              | 0    | 0 | 1                    |                               |

|   |                 |    |      |      |                |                |                |     | 1  | 1              | 1              | 0              | 0              | 0    | 0 | 0                    | Fill line 8 (cursor position) |

| _ |                 | C  | Char | acte | er co          | de             |                |     |    | ine<br>osit    | ion            | •              |                |      |   |                      | with 0s                       |

Notes: 1. EPROM addresses  $A_{10}$  to  $A_3$  correspond to a character code.

- 2. EPROM addresses  $A_2$  to  $A_0$  specify a line position of the character pattern.

- 3. EPROM data O<sub>4</sub> to O<sub>0</sub> correspond to character pattern data.

- 4. A lit display position (black) corresponds to a 1.

- 5. Line 8 (cursor position) of the character pattern must be blanked with 0s.

- 6. EPROM data O<sub>5</sub> to O<sub>7</sub> are not used.

$-5 \times 10$  dot character pattern

EPROM address data and character pattern data correspond with each other to form a  $5 \times 10$  dot character pattern (table 4).

- Handling unused character patterns

- 1. **EPROM data outside the character pattern area:** Ignored by the character generator ROM for display operation so 0 or 1 is arbitrary.

- 2. **EPROM data in CG RAM area:** Ignored by the character generator ROM for display operation so 0 or 1 is arbitrary.

- 3. **EPROM data used when the user does not use any HD66702 character pattern:** According to the user application, handled in one of the two ways listed as follows.

- a. When unused character patterns are not programmed: If an unused character code is written into DD RAM, all its dots are lit. By not programing a character pattern, all of its bits become lit. (This is due to the EPROM being filled with 1s after it is erased.)

- b. When unused character patterns are programmed as 0s: Nothing is displayed even if unused character codes are written into DD RAM. (This is equivalent to a space.)

Table 4 Example of Correspondence between EPROM Address Data and Character Pattern  $(5 \times 10 \text{ dots})$

|                |                |          | EP   | ROI  | M A             | ddr  | ess   |                  |     |                  |                |                | Dat | а |                       |                        |

|----------------|----------------|----------|------|------|-----------------|------|-------|------------------|-----|------------------|----------------|----------------|-----|---|-----------------------|------------------------|

| A <sub>1</sub> | <sub>0</sub> A | 9 A      | 8 A  | 7 A  | <sub>6</sub> А, | 5 A. | 4 A 3 | 3 A <sub>2</sub> | Α.  | 1 A <sub>0</sub> | Ο <sub>4</sub> | O <sub>3</sub> | Ο2  |   | LSB<br>O <sub>0</sub> |                        |

|                |                |          |      |      |                 |      |       | 0                | 0   | 0                | 0              | 0              | 0   | 0 | 0                     |                        |

|                |                |          |      |      |                 |      |       | 0                | 0   | 1                | 0              | 0              | 0   | 0 | 0                     |                        |

|                |                |          |      |      |                 |      |       | 0                | 1   | 0                | 0              | 1              | 1   | 0 | 1                     |                        |

| 1              | _1_            | 1        | , 1  | 0    | 0               | 0    | 1     | 0                | 1   | 1                | 1              | 0              | 0   | 1 | 1                     |                        |

|                |                | r<br>I   |      |      |                 |      |       | 1                | 0   | 0                | 1              | 0              | 0   | 0 | 1                     |                        |

|                |                |          |      |      |                 |      |       | 1                | 0   | 1                | 1              | 0              | 0   | 0 | 1                     |                        |

|                |                |          |      |      |                 |      |       | 1                | 1   | 0                | 0              | 1              | 1   | 1 | 1                     |                        |

|                |                | <b>†</b> |      |      |                 |      |       | 1                | 1   | 1                | 0              | 0              | 0   | 0 | 1                     |                        |

| 1              | 0              | 0        | ` 1  | 0    | 0               | 0    | 1     | 0                | 0   | 0                | 0              | 0              | 0   | 0 | 1                     |                        |

| 1              | 0              | 0        | 1    | 0    | 0               | 0    | 1     | 0                | 0   | 1                | 0              | 0              | 0   | 0 | 1                     |                        |

| 1              | 0              | 0        | 1    | 0    | 0               | 0    | 1     | 0                | 1   | 0                | 0              | 0              | 0   | 0 | 0                     | Fill line 11 (cursor p |

|                |                | Cha      | ract | er c | ode             |      |       | L                | ine |                  |                |                |     |   |                       | with 0s                |

Notes: 1. EPROM addresses  $A_{10}$  to  $A_3$  correspond to a character code. Set  $A_8$  and  $A_9$  of character pattern lines 9, 10, and 11 to 0s.

2. EPROM addresses A<sub>2</sub> to A<sub>0</sub> specify a line position of the character pattern.

position

- 3. EPROM data  $O_4$  to  $O_0$  correspond to character pattern data.

- 4. A lit display position (black) corresponds to a 1.

- 5. Blank out line 11 (cursor position) of the character pattern with 0s.

- 6. EPROM data O<sub>5</sub> to O<sub>7</sub> are not used.

Table 5 Correspondence between Character Codes and Character Patterns (ROM code: A00)

| Upper 4<br>Lower Bits<br>4 Bits | 0000             | 0010 | 0011     | 0100 | 0101 | 0110 | 0111        | 1010 | 1011        | 1100    | 1101        | 1110      | 1111 |

|---------------------------------|------------------|------|----------|------|------|------|-------------|------|-------------|---------|-------------|-----------|------|

| xxxx0000                        | CG<br>RAM<br>(1) |      |          |      |      | *•   | ====        |      |             |         |             |           |      |

| xxxx0001                        | (2)              |      |          |      |      |      | -==         |      |             |         | <b>:</b>    |           |      |

| xxxx0010                        | (3)              |      |          |      |      |      | <b>!-"-</b> |      |             | • • • • | .::         |           |      |

| xxxx0011                        | (4)              |      |          |      |      | :    |             |      |             |         |             |           |      |

| xxxx0100                        | (5)              |      | 4        |      |      |      | -           | ••   |             |         |             |           |      |

| xxxx0101                        | (6)              |      |          |      |      |      |             | ==   |             |         |             |           |      |

| xxxx0110                        | (7)              |      |          |      |      |      | i.,.i       |      |             |         |             |           | -    |

| xxxx0111                        | (8)              | :    |          |      |      |      |             |      |             |         |             |           |      |

| xxxx1000                        | (1)              |      |          |      | ×    | -    | <b>:</b> :: | -:   |             |         | Ļ           |           |      |

| xxxx1001                        | (2)              |      |          |      |      |      |             |      | - 1         |         |             |           |      |

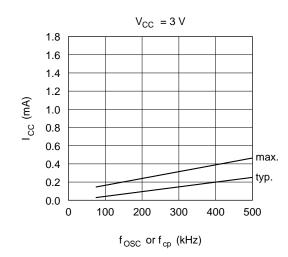

| xxxx1010                        | (3)              | #:   | ##<br>## |      |      |      |             |      |             | •       | <b>.</b>    |           |      |