#### **Features**

Single chip solution with only a few external 3wire bus serial control interface components FSK/ASK mode selection Stand-alone fixed-frequency user mode FSK for digital data or FM for analog signal ☐ Programmable multi-channel user mode reception □ Low current consumption in active mode and RSSI output for signal strength indication and very low standby current ASK reception ☐ PLL-stabilized RF VCO (LO) with internal Peak detector for ASK detection varactor diode ☐ Switchable LNA gain for improved dynamic □ Lock detect output in programmable Automatic PA turn-on after PLL lock user mode On-chip AFC for extended input frequency ☐ ASK modulation achieved by PA on/off keying

## **Ordering Information**

acceptance range

| Part Number                                                  | Temperature Code    | Package Code | Delivery Form              |

|--------------------------------------------------------------|---------------------|--------------|----------------------------|

| TH7122.1 (only for existing designs, not for new design-ins) | E (-40 °C to 85 °C) | NE (LQFP32)  | 250 pc/tray<br>2000 pc/T&R |

| TH7122.2<br>(for new design-ins)                             | E (-40 °C to 85 °C) | NE (LQFP32)  | 250 pc/tray<br>2000 pc/T&R |

## Application Examples

□ General bi-directional half duplex digital data RF signaling or analog signal communication

□ Tire Pressure Monitoring Systems (TPMS)

□ Remote Keyless Entry (RKE)

□ Low-power telemetry systems

□ Alarm and security systems

□ Wireless access control

□ Garage door openers

□ Networking solutions

□ Active RFID tags

□ Remote controls

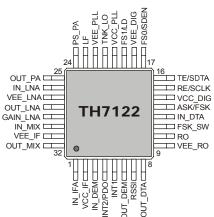

## Pin Description

☐ 32-pin Low profile Quad Flat Package (LQFP)

## General Description

Home and building automation

The TH7122 is a single chip FSK/FM/ASK transceiver IC. It is designed to operate in low-power multichannel programmable or single-channel stand-alone, half-duplex data transmission systems. It can be used for applications in automotive, industrial-scientific-medical (ISM), short range devices (SRD) or similar applications operating in the frequency range of 300 MHz to 930 MHz. In programmable user mode, the transceiver can operate down to 27 MHz by employing an external VCO varactor diode.

## **Document Content**

| 1 | The   | ory of Operation                        | 4  |

|---|-------|-----------------------------------------|----|

|   | 1.1   | General                                 | 4  |

|   | 1.2   | Technical Data Overview                 | 4  |

|   | 1.3   | Note on ASK Modulation                  | 4  |

|   |       | Block Diagram                           |    |

|   |       | User Mode Features                      |    |

|   |       |                                         |    |

| 2 | Pin I | Definitions and Descriptions            | 6  |

| 3 | Fund  | ctional Description                     | 10 |

|   | 3.1   | PLL Frequency Synthesizer               | 10 |

|   | 3.1.1 | Reference Oscillator (XOSC)             | 11 |

|   | 3.1.2 | Reference Divider                       | 11 |

|   | 3.1.3 |                                         |    |

|   | 3.1.4 | , , , , , , , , , , , , , , , , , , , , |    |

|   | 3.1.5 | , ,                                     |    |

|   | 3.1.6 |                                         |    |

|   | 3.1.7 | •                                       |    |

|   | 3.1.8 | Loop Filter                             | 13 |

|   | 3.2   | Receiver Part                           | 13 |

|   | 3.2.1 | LNA                                     |    |

|   | 3.2.2 | Mixer                                   |    |

|   | 3.2.3 | ,                                       |    |

|   | 3.2.4 |                                         |    |

|   | 3.2.5 | FSK Demodulator                         | 15 |

|   | 3.3   | Transmitter Part                        | 15 |

|   | 3.3.1 | Power Amplifier                         | 15 |

|   | 3.3.2 | Output Power Adjustment                 | 16 |

|   | 3.3.3 | Modulation Schemes                      | 16 |

|   | 3.3.4 |                                         |    |

|   | 3.3.5 |                                         |    |

|   | 3.3.6 | Crystal Tuning                          | 17 |

| 4 | Des   | cription of User Modes                  | 18 |

|   | 4.1   | Stand-alone User Mode Operation         | 18 |

|   | 4.1.1 | Frequency Selection                     |    |

|   | 4.1.2 | • •                                     |    |

|   | 4.1.3 | Modulation Type                         | 19 |

|   | 4.1.4 | LNA Gain Mode                           | 19 |

|   | 4.2   | Programmable User Mode Operation        | 19 |

|   | 4.2.1 |                                         |    |

| _ | _     | ·                                       |    |

| 5 | Rea   | ister Description                       | 20 |

## TH7122 27 to 930MHz FSK/FM/ASK Transceiver

|    | 5.1            | Register Overview                                                          | 21 |

|----|----------------|----------------------------------------------------------------------------|----|

|    | 5.1.1          | Default Register Settings for FS0, FS1                                     | 21 |

|    | 5.1.2          |                                                                            |    |

|    | 5.1.3<br>5.1.4 |                                                                            |    |

|    | 5.1.5<br>5.1.5 |                                                                            |    |

| 6  | Tec            | hnical Data                                                                | 26 |

|    | 6.1            | Absolute Maximum Ratings                                                   | 26 |

|    | 6.2            | Normal Operating Conditions                                                | 26 |

|    | 6.3            | DC Characteristics                                                         | 27 |

|    | 6.4            | PLL Synthesizer Timings                                                    | 29 |

|    | 6.5            | AC Characteristics of the Receiver Part                                    | 29 |

|    | 6.6            | AC Characteristics of the Transmitter Part                                 | 30 |

|    | 6.7            | Serial Control Interface                                                   | 30 |

|    | 6.8            | Crystal Parameters                                                         | 30 |

| 7  | Арр            | olication Circuit Examples                                                 | 31 |

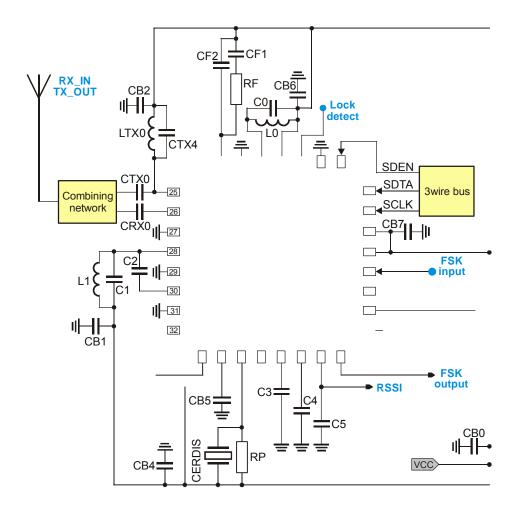

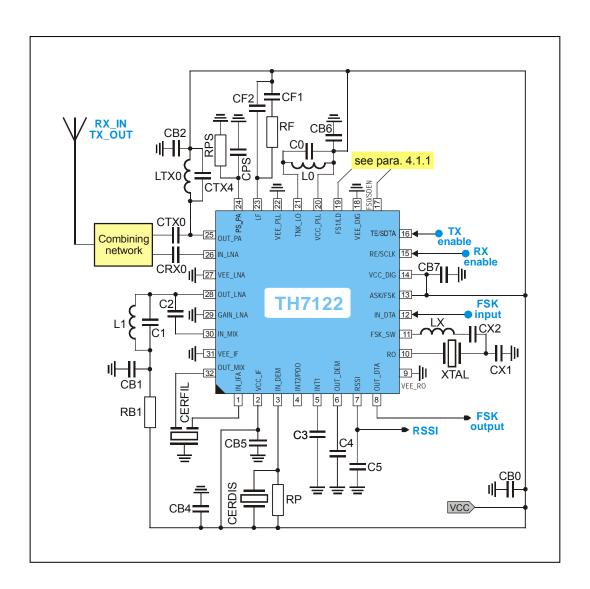

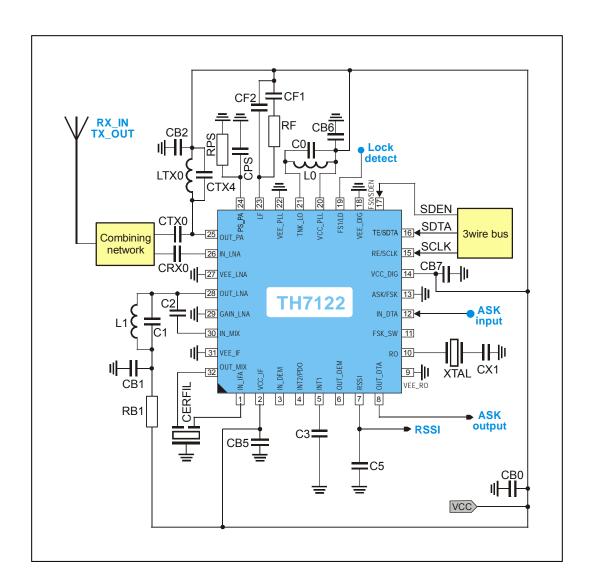

|    | 7.1            | FSK Application Circuit Programmable User Mode (internal AFC option)       | 31 |

|    | 7.2            | FSK Application Circuit Stand-alone User Mode                              | 32 |

|    | 7.3            | FSK Test Circuit Component List (Fig. 14 and Fig. 15)                      | 33 |

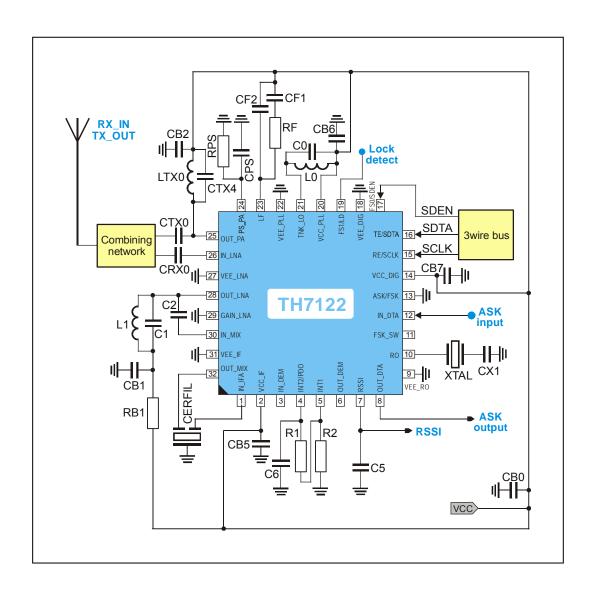

|    | 7.4            | ASK Application Circuit Programmable User Mode (normal data slicer option) | 34 |

|    | 7.5            | ASK Test Circuit Component List (Fig. 16)                                  | 35 |

|    | 7.6            | ASK Application Circuit Programmable User Mode (peak detector option)      | 36 |

|    | 7.7            | ASK Test Circuit Component List (Fig. 17)                                  | 37 |

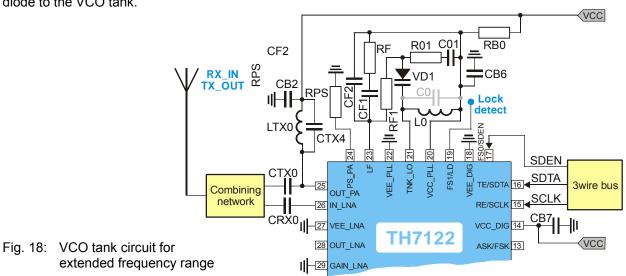

| 8  | Ext            | ended Frequency Range                                                      | 38 |

|    | 8.1            | Board Component List (Fig. 18)                                             | 38 |

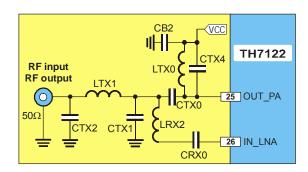

| 9  | TX/            | RX Combining Network                                                       | 39 |

|    | 9.1            | Board Component List (Fig. 19)                                             | 39 |

|    | 9.2            | Typical LNA S-Parameters in Receive Mode                                   | 39 |

|    | 9.3            | LNA Input Impedances in Transmit Mode                                      | 40 |

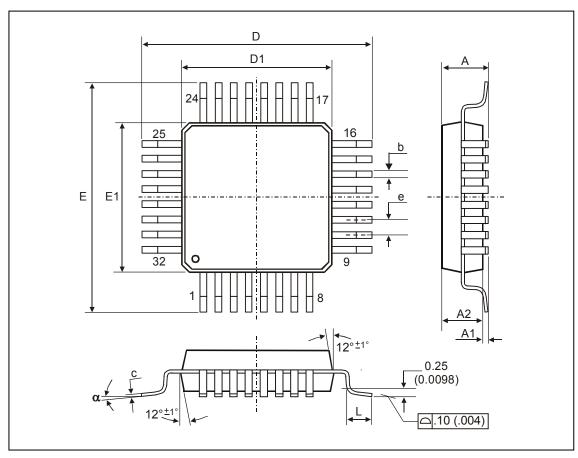

| 1  | 0 Pac          | kage Description                                                           | 41 |

|    | 10.1           | Soldering Information                                                      |    |

| 1  | 1 Rel          | ability Information                                                        | 42 |

| 1: |                | ) Precautions                                                              |    |

| 1. | 3 Dis          | claimer                                                                    | 44 |

## TH7122 27 to 930MHz FSK/FM/ASK Transceiver

## 1 Theory of Operation

#### 1.1 General

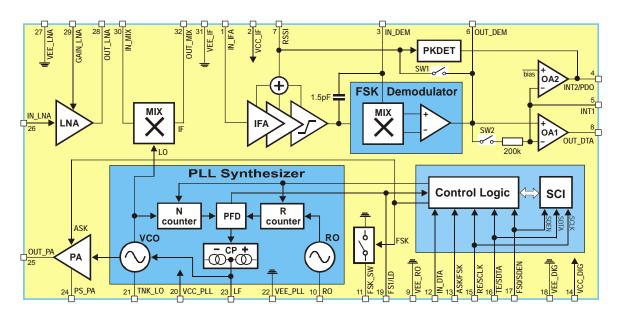

The main building block of the transceiver is a programmable PLL frequency synthesizer that is based on an integer-N topology. The PLL is used for generating the carrier frequency during transmission and for generating the LO signal during reception. The carrier frequency can be FSK-modulated either by pulling the crystal or by modulating the VCO directly. ASK modulation is done by on/off keying of the power amplifier. The receiver is based on the principle of a single conversion superhet. Therefore the VCO frequency has to be changed between transmit and receive mode. In receive mode, the default LO injection type is low-side injection.

The TH7122 transceiver IC consists of the following building blocks:

- Low-noise amplifier (LNA) for high-sensitivity RF signal reception with switchable gain

- Mixer (MIX) for RF-to-IF down-conversion

- IF amplifier (IFA) to amplify and limit the IF signal and for RSSI generation

- Phase-coincidence FSK demodulator with external ceramic discriminator or LC tank

- Operational amplifier (OA1), connected to demodulator output

- Operational amplifier (OA2), for general use

- Peak detector (PKDET) for ASK detection

- Control logic with 3wire bus serial control interface (SCI)

- Reference oscillator (RO) with external crystal

- Reference divider (R counter)

- Programmable divider (N/A counter)

- Phase-frequency detector (PFD)

- Charge pump (CP)

- Voltage controlled oscillator (VCO) with internal varactor

- Power amplifier (PA) with adjustable output power

#### 1.2 Technical Data Overview

| J | Frequency range: 300 MHz to 930 MHz in           | Sensitivity: -107 dBm at ASK with 180 kHz             |

|---|--------------------------------------------------|-------------------------------------------------------|

|   | programmable user mode                           | IF filter BW                                          |

| J | Extended frequency range with external VCO       | Max. data rate with crystal pulling: 20 kbps NRZ      |

|   | varactor diode: 27 MHz to 930 MHz                | Max. data rate with direct VCO modulation:            |

| J | 315 MHz, 433 MHz, 868 MHz or 915 MHz fixed-      | 115 kbps NRZ                                          |

|   | frequency settings in stand-alone mode           | Max. input level: -10 dBm at FSK                      |

| J | Power supply range: 2.2 V to 5.5 V               | and -20 dBm at ASK                                    |

| J | Temperature range: -40 °C to +85 °C              | Input frequency acceptance: $\pm$ 10 to $\pm$ 150 kHz |

| J | Standby current: 50 nA                           | (depending on FSK deviation)                          |

| J | Operating current in receive: 6.5 mA (low gain)  | FM/FSK deviation range: ±2.5 to ±80 kHz               |

| J | Operating current in transmit: 12 mA (at -2 dBm) | Analog modulation frequency: max. 10 kHz              |

| J | Adjustable RF power range: -20 dBm to +10dBm     | Crystal reference frequency: 3 MHz to 12 MHz          |

| J | Sensitivity: -105 dBm at FSK with 180 kHz        | External reference frequency: 1 MHz to 16 MHz         |

|   | IF filter BW                                     | ,                                                     |

#### 1.3 Note on ASK Operation

Optimum ASK performance can be achieved by using an 8-MHz crystal for operation at 315 MHz, 434 MHz and 915 MHz. For details please refer to the software settings shown in sections 7.4 and 7.6. FSK operation is the preferred choice for applications in the European 868MHz band.

39010 07122 Page 4 of 44 Data Sheet Rev. 010 Feb/09

### 1.4 Block Diagram

Fig. 1: TH7122 block diagram

#### 1.5 User Mode Features

The transceiver can operate in two different user modes. It can be used either as a 3wire-bus-controlled programmable or as a stand-alone fixed-frequency device. After power up, the transceiver is set to Stand-alone User Mode (SUM). In this mode, pins FS0/SDEN and FS1/LD must be connected to  $V_{\text{EE}}$  or  $V_{\text{CC}}$  in order to set the desired frequency of operation. There are 4 pre-defined frequency settings: 315MHz, 433.92MHz, 868.3MHz and 915MHz. The logic level at pin FS0/SDEN must not be changed after power up in order to remain in fixed-frequency mode.

After the first logic level change at pin FS0/SDEN, the transceiver enters into Programmable User Mode (PUM). In this mode, the user can set any PLL frequency or mode of operation by the SCI. In SUM pins FS0/SDEN and FS1/LD are used to set the desired frequency, while in PUM pin FS0/SDEN is part of the 3-wire serial control interface (SCI) and pin FS1/LD is the look detector output signal of the PLL synthesizer.

A mode control logic allows several operating modes. In addition to standby, transmit and receive mode, two idle modes can be selected to run either the reference oscillator only or the whole PLL synthesizer. The PLL settings for the PLL idle mode are taken over from the last operating mode which can be either receive or transmit mode.

The different operating modes can be set in SUM and PUM as well. In SUM the user can program the transceiver via control pins RE/SCLK and TE/SDTA. In PUM the register bits OPMODE are used to select the modes of operation while pins RE/SCLK and TE/SDTA are part of the SCI.

# 2 Pin Definitions and Descriptions

| Pin No. | Name     | I/O Type   | Functional Schematic | Description                                                                                        |

|---------|----------|------------|----------------------|----------------------------------------------------------------------------------------------------|

| 1       | IN_IFA   | input      | IN_IFA 50 140µA VEE  | IF amplifier input, approx.<br>2 kΩ single-ended                                                   |

| 2       | VCC_IF   | supply     |                      | positive supply of LNA, MIX, IFA, FSK Demodulator, PA, OA1 and OA2                                 |

| 3       | IN_DEM   | analog I/O | 90k 90k 100µA VEE    | IF amplifier output and demodulator input, connection to external ceramic discriminator or LC tank |

| 4       | INT2/PDO | output     | INT2/PDO VCC IIII    | OA2 output or peak detector output, high impedance in transmit and idle mode                       |

| 5       | INT1     | input      | VCC 200k VCC OUT_DEM | inverting inputs of OA1 and OA2                                                                    |

| 6       | OUT_DEM  | analog I/O | VEE VCC 6            | demodulator output and<br>non-inverting OA1 input,<br>high impedance in transmit<br>and idle mode  |

| 7       | RSSI     | output     | RSSI 120 7           | RSSI output, approx. 31 kΩ                                                                         |

| Pin No. | Name    | I/O Type   | Functional Schematic | Description                                                                                 |

|---------|---------|------------|----------------------|---------------------------------------------------------------------------------------------|

| 8       | OUT_DTA | output     | OUT_DTA VCC OUT_DTA  | OA1 output, high impedance in transmit and idle mode                                        |

| 9       | VEE_RO  | ground     | <del>-</del>         | ground of RO                                                                                |

| 10      | RO      | analog I/O | RO 36ρ 36ρ 36ρ VEE   | RO input, base of bipolar transistor                                                        |

| 11      | FSK_SW  | analog I/O | FSK_SW TO VCC        | FSK pulling pin, switch to ground or OPEN The switch is open in receive and idle mode       |

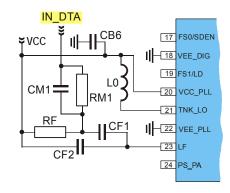

| 12      | IN_DTA  | input      | IN_DTA 120 120k VEE  | ASK/FSK modulation data input, pull down resistor 120kΩ                                     |

| 13      | ASK/FSK | input      | ASK/FSK 120 VEE      | ASK/FSK mode select input                                                                   |

| 14      | VCC_DIG | supply     |                      | positive supply of serial port and control logic                                            |

| 15      | RE/SCLK | input      | RE/SCLK 120 120k VEE | receiver enable input / clock input for the shift register, pull down resistor $120k\Omega$ |

| 16      | TE/SDTA | input      | TE/SDTA 120 120k VEE | transmitter enable input / serial data input, pull down resistor 120k $\Omega$              |

| Pin No. | Name     | I/O Type          | Functional Schematic              | Description                                                              |

|---------|----------|-------------------|-----------------------------------|--------------------------------------------------------------------------|

| 17      | FS0/SDEN | input             | FS0/SDEN 120 VEE                  | frequency select input / se-<br>rial data enable input                   |

| 18      | VEE_DIG  | ground            |                                   | ground of serial port and control logic                                  |

| 19      | FS1/LD   | input /<br>output | FS1/LD 120 VEE                    | frequency select input / lock detector output                            |

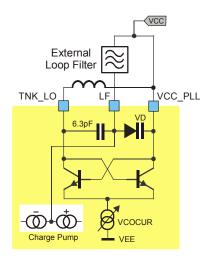

| 20      | VCC_PLL  | analog I/O        | TNK_LO VCC_PLL 21 VCC II 20       | VCO open-collector output,<br>connection to VCC or exter-<br>nal LC tank |

| 21      | TNK_LO   | analog I/O        | VEE VEE VCOCUR                    | VCO open-collector output, connection to external LC tank                |

| 23      | LF       | analog I/O        | VEE VEE                           | charge pump output, con-<br>nection to external loop filter              |

| 22      | VEE_PLL  | ground            |                                   | ground of PLL frequency synthesizer                                      |

| 24      | PS_PA    | analog I/O        | PS_PA 120 VEE VEE                 | power-setting input                                                      |

| 25      | OUT_PA   | output            | OUT_PA  VCC   1k  VEE   VEE   VEE | power amplifier open-<br>collector output                                |

| Pin No. | Name     | I/O Type | Functional Schematic    | Description                                                           |

|---------|----------|----------|-------------------------|-----------------------------------------------------------------------|

| 27      | VEE_LNA  | ground   |                         | ground of LNA and PA                                                  |

| 28      | OUT_LNA  | output   | OUT_LNA  bias  28  3.8k | LNA open-collector output,<br>connection to external LC<br>tank at RF |

| 26      | IN_LNA   | input    | IN_LNA 26 VEE  VEE  VEE | LNA input, single-ended                                               |

| 29      | GAIN_LNA | input    | GAIN_LNA 120 VEE        | LNA gain control input                                                |

| 30      | IN_MIX   | input    | IN_MIX 210 210 bias VEE | mixer input, approx. $200\Omega$ single-ended                         |

| 31      | VEE_IF   | ground   |                         | ground of IFA, Demodulator, OA1 and OA2                               |

| 32      | OUT_MIX  | output   | OUT_MIX 100 VEE         | mixer output, approx. 330Ω single-ended                               |

## 3 Functional Description

### 3.1 PLL Frequency Synthesizer

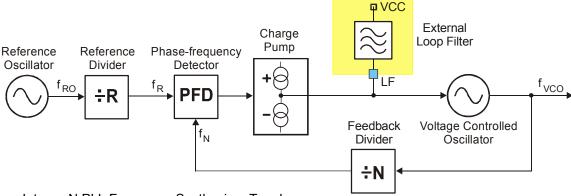

The TH7122 contains an integer-N PLL frequency synthesizer. A PLL circuit performs the frequency synthesis via a feedback mechanism. The output frequency  $f_{\text{VCO}}$  is generated as an integer multiple of the phase detector comparison frequency  $f_{\text{R}}$ . This reference frequency  $f_{\text{R}}$  is generated by dividing the output frequency  $f_{\text{RO}}$  of a crystal oscillator. The phase detector utilizes this signal as a reference to tune the VCO and in the locked state it must be equal to the desired output frequency, divided by the feedback divider ratio N.

Fig. 2: Integer-N PLL Frequency Synthesizer Topology

The output frequency of the synthesizer  $f_{VCO}$  can be selected by programming the feedback divider and the reference divider. The only constraint for the frequency output of the system is that the minimum frequency resolution, or the channel spacing, must be equal to the PFD frequency  $f_R$ , which is given by the reference frequency  $f_{RO}$  and the reference divider factor R:

$$f_{R} = \frac{f_{RO}}{R}.$$

(1)

When the PLL is unlocked (e.g. during power up or during reprogramming of a new feedback divider ratio N), the phase-frequency detector PFD and the charge pump create an error signal proportional to the phase difference of the two input signals. This error signal is low-pass filtered through the external loop filter and input to the VCO to control its frequency. A very low frequency resolution increases the settling time of the PLL and reduces the ability to cancel out VCO perturbations, because the loop filter is updated every  $1/f_R$ . After the PLL has locked, the VCO frequency is given by the following equation:

$$f_{\text{VCO}} = N \cdot \frac{f_{\text{RO}}}{R} = N \cdot f_{\text{R}} \,. \tag{2}$$

There are four registers available to set the VCO frequencies in receive (registers RR and NR) and in transmit mode (registers RT and NT). These registers can be programmed using the Serial Control Interface in Programmable User Mode (PUM). In case of Stand-alone User Mode (SUM), the registers are set fixed values (refer to para. 4.1.1).

The VCO frequency is equal to the carrier frequency in transmit mode. While in receive mode the VCO frequency is offset by the intermediate frequency IF. This is because of the super-heterodyne nature of the receive part.

39010 07122 Page 10 of 44 Data Sheet Rev. 010 Feb/09

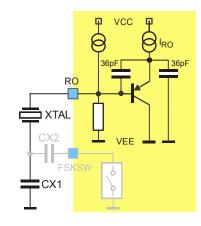

#### 3.1.1 Reference Oscillator (XOSC)

The reference oscillator is based on a Colpitts topology with two integrated functional capacitors as shown in figure 3. The circuitry is optimized for a load capacitance range of 10 pF to 15 pF. The equivalent input capacitance CRO offered by the oscillator input pin RO is about 18pF.

To ensure a fast and reliable start-up and a very stable frequency over the specified supply voltage and temperature range, the oscillator bias circuitry provides an amplitude regulation. The amplitude on pin RO is monitored in order to regulate the current of the oscillator core I<sub>RO</sub>. There are two limits ROMAX and ROMIN between the regulation is maintained. These values can be changed via serial control interface in Programmable User Mode (PUM). In Stand-alone User Mode (SUM), ROMAX and ROMIN are set to default values (refer to para. 5.1.3). ROMAX defines the start-up current of the oscillator. The ROMIN value sets the desired steady-state current. If ROMIN is sufficient to achieve an amplitude of about 400 mV on pin RO, the current I<sub>RO</sub> will be set to ROMIN. Otherwise the current will be permanently regulated between ROMIN and ROMAX. If ROMIN and ROMAX are equal, no regulation takes place. For most of the applications ROMIN and ROMAX should not be changed from default.

Fig. 3: Reference oscillator circuit

#### 3.1.2 Reference Divider

The reference divider provides the input signal of the phase detector by dividing the signal of the reference oscillator. The range of the reference divider is

$$4 \le R \le 1023$$

. (3)

#### 3.1.3 Feedback Divider

The feedback divider of the PLL is based on a pulse-swallow topology. It contains a 4-bit swallow A-counter, a 13-bit program B-counter and a prescaler. The divider ratio of the prescaler is controlled by the program counter and the swallow counter. During one cycle, the prescaler divides by 17 until the swallow A-counter reaches its terminal count. Afterwards the prescaler divides by 16 until the program counter reaches its terminal count. Therefore the overall feedback divider ratio can be expressed as:

$$N = 17 \cdot A + 16 \cdot (B - A). \tag{4}$$

The A-counter configuration represents the lower bits in the feedback divider register ( $N_{0-3} = A_{0-3}$ ) and the upper bits the B-counter configuration ( $N_{4-16} = B_{0-12}$ ) respectively. According to that, the following counter ranges are implemented:

$$0 \le A \le 15$$

;  $4 \le B \le 8191$  whereas  $B > A$  (5)

and therefore the range of the overall feedback divider ratio results in:

$$64 \le N \le 131071 . (6)$$

The user does not need to care about the A- and B-counter settings. It is only necessary to know the overall feedback divider ratio N to program the register settings.

## 3.1.4 Frequency Resolution and Operating Frequency

It is obvious from (2) that, at a given frequency resolution  $f_R$ , the maximum operating frequency of the VCO is limited by the maximum N-counter setting. The table below provides some illustrative numbers. Please also refer to section 4.4.1 for the pre-configured settings in Stand-alone User Mode (SUM).

39010 07122 Page 11 of 44 Data Sheet Rev. 010 Feb/09

| Crystal frequency f <sub>RO</sub> | Frequency resolution f <sub>R</sub> | R<br>counter | N<br>counter | Operating frequency f <sub>vco</sub> |

|-----------------------------------|-------------------------------------|--------------|--------------|--------------------------------------|

| 3.0000MHz                         | 2.93kHz                             | 1023         | 13107        | 38.437MHz                            |

| 3.0000MHz                         | 2.93kHz                             | 1023         | 131071       | 384.372MHz                           |

| 8.0000MHz                         | 12.5kHz                             | 640          | 35812        | 447.65MHz                            |

| 8.0000MHz                         | 25kHz                               | 320          | 34746        | 868.65MHz                            |

| 8.0000MHz                         | 250kHz                              | 32           | 3660         | 915.0MHz                             |

#### 3.1.5 Phase-Frequency Detector

The phase-frequency detector creates an error voltage proportional to the phase difference between the reference signal  $f_R$  and  $f_N$ . The implementation of the phase detector is a phase-frequency type. That circuitry is very useful because it decreases the acquisition time significantly. The gain of the phase detector can be expressed as:

$$K_{PD} = \frac{I_{CP}}{2\pi} , \qquad (7)$$

where  $I_{CP}$  is the charge pump current which is set via register CPCUR. In the TH7122 design the VCO frequency control characteristic is with negative polarity. This means the VCO frequency increases if the loop filter output voltage decreases and vice versa. When an external varactor diode is added to the VCO tank, the tuning characteristic can be changed between positive and negative depending on the particular varactor diode circuitry. Therefore the PDFPOL register can be used to define the phase detector polarity.

#### 3.1.6 Lock Detector

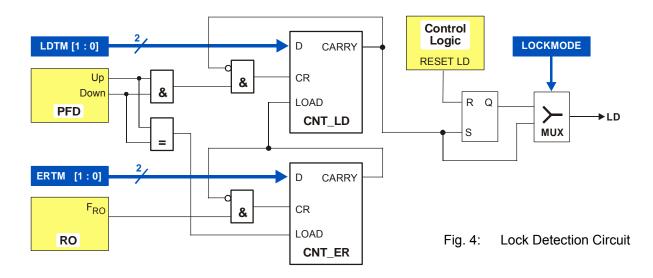

In Programmable User Mode a lock-detect signal LD is available at pin FS1/LD (pin 19). The lock detection circuitry uses Up and Down signals from the phase detector to check them for phase coherency. Figure 4 shows an overview of the lock signal generation. The locked state and the unlock condition will be decided on the register settings of LDTM and ERTM respectively. In the start-up phase of the PLL, Up and Down signals are quite unbalanced and counter CNT\_LD receives no clock signal. When the loop approaches steady state, the signals Up and Down begin to overlap and CNT\_LD counts down. Herein register LDTM sets the number of counts which are necessary to set the lock detection signal LD. If an unlock condition occurs, the counter CNT\_LD will be reloaded and therefore its CARRY falls back.

The CNT\_ER supervises the unlock condition. If Up and Down are consecutive, the counter CNT\_ER will be reloaded permanently and its CARRY will not be set, otherwise the counter level of CNT\_ER will be reduced by the reference oscillator clock ( $1/f_{RO}$ ). The register ERTM decides on the maximum number of clocks during Up and Down signals can be non-consecutive without loosing the locked state.

The transceiver offers two ways of analyzing the locked state. If the register LOCKMODE is set to '0', only one occurrence of the locked state condition is needed to remain LD = 1 during the whole active mode, otherwise the state of the PLL will be observed permanently.

#### 3.1.7 Voltage Controlled Oscillator with external Loop Filter

The transceiver provides a LC-based voltage-controlled oscillator with an external inductance element connected between VCC and pin TNK\_LO. An internal varactor diode in series with a fixed capacitor forms the variable part of the oscillator tank. The oscillation frequency is adjusted by the DC-voltage at pin LF. The tuning sensitivity of the VCO is approximately 20MHz/V for 433MHz operations and 40MHz/V at 868MHz. Since the internal varactor is connected to VCC, a lower voltage on pin LF causes the capacitance to decrease and the VCO frequency to increase. For this reason the phase detector polarity should be negative (PFDPOL = 0). If the operation frequency is below 300MHz, an external varactor diode between pin TNK\_LO and VCC\_PLL is necessary. The corresponding application schematic is shown in section 8. The VCO current VCOCUR can be adjusted via serial control interface in order to ensure stable oscillations over the whole frequency range. For lowest LO emission in receive mode, VCOCUR should be set to the lowest value.

Fig. 5: VCO schematic

#### 3.1.8 Loop Filter

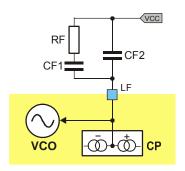

Since the loop filter has a strong impact on the function of the PLL, it must be chosen carefully. For FSK operation the bandwidth of the loop filter must be selected wide enough for a fast relock of the PLL during crystal pulling. The bandwidth must of course also be larger than the data rate. In case of ASK or OOK the bandwidth should be extended even further to allow the PLL to cancel out VCO perturbations that might be caused by the PA on/off keying. The suggested filter topology is shown in Fig. 6. The dimensions of the loop filter elements can be derived using well known formulas in application notes and other reference literature.

Fig. 6: 2<sup>nd</sup> order Loop filter

#### 3.2 Receiver Part

The RF front-end of the receiver part is a super-heterodyne configuration that converts the input radio-frequency (RF) signal into an intermediate frequency (IF) signal. The most commonly used IF is 10.7 MHz, but IFs in the range of 0.4 to 22 MHz can also be used. According to the block diagram, the front-end consists of a LNA, a Mixer and an IF limiting amplifier with received signal strength indicator (RSSI). The local oscillator (LO) signal for the mixer is generated by the PLL frequency synthesizer.

As the receiver constitutes a superhet architecture, there is no inherent suppression of the image frequency. It depends on the particular application and the system's environmental conditions whether an RF front-end filter should be added or not. If image rejection and/or good blocking immunity are relevant system parameters, a band-pass filter must be placed either in front or after the LNA. This filter can be a SAW (surface acoustic wave) or LC-based filter (e.g. helix type).

## TH7122 27 to 930MHz FSK/FM/ASK Transceiver

#### 3.2.1 LNA

The LNA is based on a cascode topology for low-noise, high gain and good reverse isolation. The open collector output has to be connected to an external resonance circuit which is tuned to the receive frequency. The gain of the LNA can be changed in order to achieve a high dynamic range. There are two possibilities for the gain setting which can be selected by the register bit LNACTRL. External control can be done via the pin GAIN\_LNA, internal control is given by the register bit LNAGAIN. In case of external gain control, a hysteresis of about 340 mV can be chosen via the register bit LNAHYST. This configuration is useful if an automatic gain control loop via the RSSI signal is established. In transmit mode the LNA-input is shorted to protect the amplifier from saturation and damaging.

#### 3.2.2 Mixer

The mixer is a double-balanced mixer which down converts the receive frequency to the IF. The default LO injection type is low side ( $f_{VCO} = f_{RX} - f_{IF}$ ). But also high side injection is possible ( $f_{VCO} = f_{RX} + f_{IF}$ ). In this case, the data signal's polarity is inverted due to the mixing process. To avoid this, the transmitted data stream can be inverted too by setting DTAPOL to '1'.

The output impedance of the mixer is about 330 $\Omega$  in order to match to an external IF filter.

### 3.2.3 IF Amplifier

After passing the channel select filter which sets the IF bandwidth the signal is limited by means of an high gain limiting amplifier. The small signal gain is about 80 dB. The RSSI signal is generated within the IF amplifier. The output of the RSSI signal is available at pin RSSI. The voltage at this pin is proportional to the input power of the receiver in dBm. Using this RSSI output signal the signal strength of different transmitters can be distinguished.

#### 3.2.4 ASK Demodulator

The receive part of the TH7122 allows for two ASK demodulation configurations:

- standard ASK demodulation or

- ASK demodulation with peak detector.

The default setting is standard ASK demodulation. In this mode SW1 and SW2 are closed and the RSSI output signal directly feeds the data slicer setup by means of OA1. The data slicer time constant equals to

$$T = 200k\Omega \cdot C3, \tag{8}$$

with C3 external to pin INT1. This time constant should be larger than the longest possible bit duration of the data stream. This is required to properly extract the ASK data's DC level. The purpose of the DC (or mean) level at the negative input of OA1 is to set an adaptive comparator threshold to perform the ASK detection.

Alternatively a peak detector can be used to define the ASK detection threshold. In this configuration the peak detector PKDET is enabled, SW1 is closed and SW2 is open, and the peak detector output is multiplexed to pin INT2/PDO. This way the peak detector can feed the data slicer, again constituted by OA1 and a few external R and C components. The peak detection mode is selectable in programmable user mode.

#### 3.2.5 FSK Demodulator

The implemented FSK demodulator is based on the phase-coincidence principle. A discriminator tank, which can either consist of a ceramic discriminator or an LC tank, is connected to pin IN\_DEM. If FSK mode is selected SW1 is open, SW2 is closed and the output of OA2 is multiplexed to pin INT2/PDO.

The demodulator output signal directly feeds the data slicer setup by means of OA1. The data slicer time constant can be calculated using (8). This time constant should be larger than the longest possible bit duration of the data stream as described in the previous paragraph.

An on-chip AFC circuit tolerates input frequency variations. The input frequency acceptance range is proportional to the FSK or FM deviation. It can be adjusted by the discriminator tank. The AFC feature is disabled by default and can be activated in programmable mode.

#### 3.3 Transmitter Part

The output of the PLL frequency synthesizer feeds a power amplifier (PA) in order to setup a complete RF transmitter. The VCO frequency is identical to the carrier frequency.

#### 3.3.1 Power Amplifier

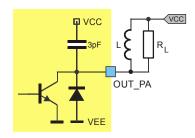

The power amplifier (PA) has been designed to deliver about 10 dBm in the specified frequency bands. Its pin OUT\_PA is an open collector output. The larger the output voltage swing can be made the better the power efficiency will be. The PA must be matched to deliver the best efficiency in terms of output power and current consumption.

The collector must be biased to the positive supply. This is done by means of an inductor parallel tuned with a capacitor. Or it is made large enough in order not to affect the output matching network. S-parameters of pin OUT\_PA are not useful because the output is very high resistive with a small portion of parallel capacitance. Since the open-collector output transistor can be considered as a current source, the only parameters needed to design the output matching network are the output capacitance, the supply voltage  $V_{\rm CC}$ , the transistor's saturation voltage and the power delivered to the load  $P_{\rm C}$ .

In order to avoid saturation of the output stage, a saturation voltage VCE $_{\text{SAT}}$  of about 0.7 V should be considered. The real part of the load impedance can then be calculated using

Fig. 7: OUT PA schematic

$$R_{L} = \frac{(V_{CC} - VCE_{SAT})^{2}}{2 \cdot P_{O}}.$$

(9)

The output capacitance is typically 3 pF.

### 3.3.2 Output Power Adjustment

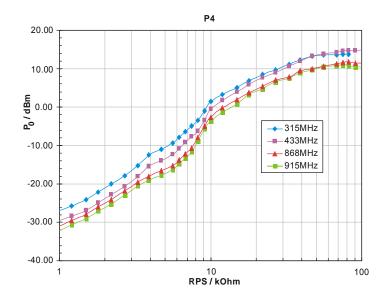

The maximum output power is adjustable via the external resistor RPS as shown in Figure 8. There are four predefined power settings in programmable user mode which can be set in the register TXPOWER. The maximum power setting P4 is the default setting.

Fig. 8: Output power vs. RPS

#### 3.3.3 Modulation Schemes

The RF carrier generated by the PLL frequency synthesizer can be ASK or FSK modulated. Depending on the selected user mode, the modulation type can be selected either by the ASK/FSK pin or via the serial control interface. Data is applied to pin IN\_DTA. The data signal can be inverted by the bit DTAPOL. The following tables for ASK and FSK modulation are valid for non-inverted data (DTAPOL = 0)

### 3.3.4 ASK Modulation

| IN_DTA | Description                                                           |  |  |  |

|--------|-----------------------------------------------------------------------|--|--|--|

| 0      | Power amplifier is turned off                                         |  |  |  |

| 1      | Power amplifier is turned on (according to the selected output power) |  |  |  |

The transceiver is ASK-modulated by turning on and off the power amplifier. Please also refer to para. 1.3 for ASK modulation limits.

#### 3.3.5 FSK Modulation

#### FSK modulation via crystal pulling

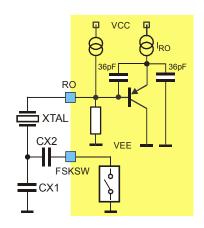

FSK modulation can be achieved by pulling the crystal oscillator frequency. A CMOS-compatible data stream applied at pin IN\_DTA digitally modulates the XOSC via an integrated NMOS switch. Two external pulling capacitors CX1 and CX2 allow the FSK deviation  $\Delta f$  and center frequency  $f_c$  to be adjusted independently. At IN\_DTA = LOW CX2 is connected in parallel to CX1 leading to the low-frequency component of the FSK spectrum ( $f_{min}$ ); while at IN\_DTA = HIGH CX2 is deactivated and the XOSC is set to its high frequency, leading to  $f_{max}$ .

| IN_DTA | Description                                       |

|--------|---------------------------------------------------|

| 0      | $f_{min} = f_c - \Delta f$ (FSK switch is closed) |

| 1      | $f_{max} = f_c + \Delta f$ (FSK switch is open)   |

Fig. 9: Crystal Pulling Circuit

An external reference signal can be directly AC-coupled to the reference oscillator input pin RO. Then the transceiver is used without a XTAL. Now the reference signal sets the carrier frequency and has to contain the FSK (or FM) modulation

#### FSK modulation via direct VCO modulation

Alternatively FSK or FM can be achieved by injecting the modulating signal into the loop filter to directly control the VCO frequency. Fig. 10 shows a circuit proposal for direct VCO modulation. This circuit is recommended for data rates in excess of about 20 kbps NRZ. An external VCO tuning varactor should be added for narrow-band applications, for example at channel spacings of 25 kHz. For details please refer to the application notes "TH7122 and TH71221 High Speed Data Communication" and "TH7122 and TH71221 Used In Narrow Band FSK Applications" as well as to the "TH7122 and TH71221 Cookbook"

Fig. 10: Circuit schematic for direct VCO modulation

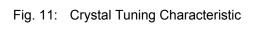

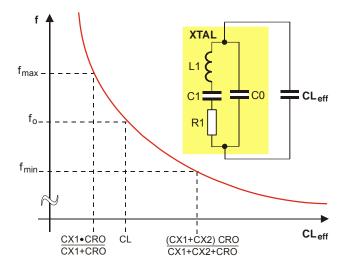

#### 3.3.6 Crystal Tuning

A crystal is tuned by the manufacturer to the requested oscillation frequency  $f_0$  for a certain load capacitance CL within the specified calibration tolerance. The only way to tune this oscillation frequency is to vary the effective load capacitance  $\text{CL}_{\text{eff}}$  seen by the crystal.

Figure 8 shows the oscillation frequency of a crystal in dependency on the effective load capacitance. This capacitance changes in accordance with the logic level of IN\_DTA around the specified load capacitance. The figure illustrates the relationship between the external pulling capacitors and the frequency deviation.

## 4 Description of User Modes

### 4.1 Stand-alone User Mode Operation

After power up the transceiver is set to stand-alone user mode. In this mode, pins FS0/SDEN and FS1/LD must be connected to  $V_{\text{EE}}$  or  $V_{\text{CC}}$  to set the desired frequency of operation. The logic level at pin FS0/SDEN must not be changed after power up in order to remain in stand-alone user mode. The default settings of the control word bits in stand-alone user mode are described in the frequency selection table. Detailed information about the default settings can be found in the tables of section 5.

### 4.1.1 Frequency Selection

| Channel frequency               | 433.92 MHz | 868.3 MHz  | 315 MHz    | 915 MHz    |

|---------------------------------|------------|------------|------------|------------|

| FS0/SDEN                        | 1          | 0          | 1          | 0          |

| FS1/LD                          | 0          | 0          | 1          | 1          |

|                                 |            |            |            |            |

| Reference oscillator frequency  |            | 7.150      | 5 MHz      |            |

| R counter ratio in RX mode (RR) | 32         | 16         | 18         | 32         |

| PFD frequency in RX mode        | 223.45 kHz | 446.91 kHz | 397.25 kHz | 223.45 kHz |

| N counter ratio in RX mode (NR) | 1894       | 1919       | 766        | 4047       |

| VCO frequency in RX mode        | 423.22 MHz | 857.60 MHz | 304.30 MHz | 904.30 MHz |

| RX frequency                    | 433.92 MHz | 868.30 MHz | 315.00 MHz | 915.00 MHz |

| R counter ratio in TX mode (RT) | 32         | 16         | 18         | 32         |

| PFD frequency in TX mode        | 223.45 kHz | 446.91 kHz | 397.25 kHz | 223.45 kHz |

| N counter ratio in TX mode (NT) | 1942       | 1943       | 793        | 4095       |

| VCO frequency in TX mode        | 433.92 MHz | 868.30 MHz | 315.00 MHz | 915.00 MHz |

| TX frequency                    | 433.92 MHz | 868.30 MHz | 315.00 MHz | 915.00 MHz |

| IF in RX mode                   | 10.7 MHz   | 10.7 MHz   | 10.7 MHz   | 10.7 MHz   |

In stand-alone user mode, the transceiver can be set to Standby, Receive, Transmit or Idle mode (only PLL synthesizer active) via control pins RE/SCLK and TE/SDTA. The modulation scheme and the LNA gain are set by pins ASK/FSK and GAIN\_LNA, respectively.

#### 4.1.2 Operation Mode

| Operation mode | Standby | Receive | Transmit | ldle |

|----------------|---------|---------|----------|------|

| RE/SCLK        | 0       | 1       | 0        | 1    |

| TE/SDTA        | 0       | 0       | 1        | 1    |

Note: Pins with internal pull-down

### 4.1.3 Modulation Type

| Modulation type | ASK | FSK |

|-----------------|-----|-----|

| ASK / FSK       | 0   | 1   |

#### 4.1.4 LNA Gain Mode

| LNA gain | high | low |

|----------|------|-----|

| GAIN_LNA | 0    | 1   |

### 4.2 Programmable User Mode Operation

The transceiver can also be used in programmable user mode. After power-up the first logic change at pin FS0/SDEN enters into this mode. Now full programmability can be achieved via the Serial Control Interface (SCI).

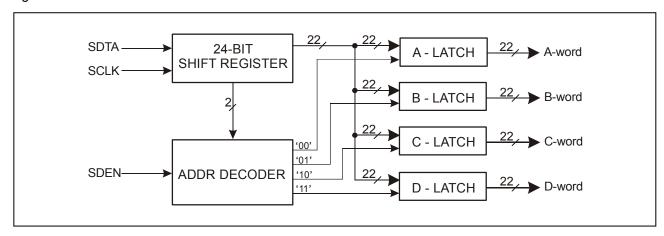

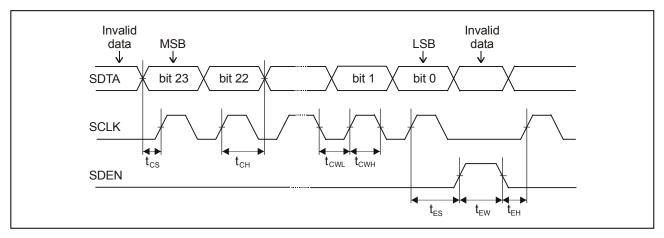

### 4.2.1 Serial Control Interface Description

A 3-wire (SCLK, SDTA, SDEN) Serial Control Interface (SCI) is used to program the transceiver in program-mable user mode. At each rising edge of the SCLK signal, the logic value on the SDTA pin is written into a 24-bit shift register. The data stored in the shift register are loaded into one of the 4 appropriate latches on the rising edge of SDEN. The control words are 24 bits lengths: 2 address bits and 22 data bits. The first two bits (bit 23 and 22) are latch address bits. As additional leading bits are ignored, only the least significant 24 bits are serial-clocked into the shift register. The first incoming bit is the most significant bit (MSB). To program the transceiver in multi-channel application, four 24-bit words may be sent: A-word, B-word, C-word and D-word. If individual bits within a word have to be changed, then it is sufficient to program only the appropriate 24-bit word. The serial data input timing and the structure of the control words are illustrated in Fig. 12 and 13.

Fig. 12: SCI Block Diagram

39010 07122 Page 19 of 44 Data Sheet Rev. 010 Feb/09

Due to the static CMOS design, the SCI consumes virtually no current and it can be programmed in active as well as in standby mode.

If the transceiver is set from standby mode to any of the active modes (idle, receive, transmit), the SCI settings remain the same as previously set in one of the active modes, unless new settings are done on the SCI while entering into an active mode.

Fig. 13: Serial Data Input Timing

## 5 Register Description

As shown in the previous section there are four control words which stipulate the operation of the whole chip. In Stand-alone User Mode SUM the intrinsic default values with respect to the applied levels at pins FS0 and FS1 lay down the configuration of the transceiver. In Programmable User Mode (PUM) the register settings can be changed via 3-wire interface SCI. The default settings which vary with the desired operating frequency depend on the voltage levels at the frequency selection pins FS0 and FS1 before entering the PUM. Table 5.1.1 shows the default register settings of different frequency selections. It should be noted that the channel frequency listed below will be achieved with a crystal frequency of 7.1505 MHz. The following table depicts an overview of the register configuration of the TH7122.

## 5.1 Register Overview

| WO | RD |         |          |        |         |          |        |                                                 |                                                 |          |         | DA     | ТА    |             |                  |        |        |       |       |       |       |      |       |         |

|----|----|---------|----------|--------|---------|----------|--------|-------------------------------------------------|-------------------------------------------------|----------|---------|--------|-------|-------------|------------------|--------|--------|-------|-------|-------|-------|------|-------|---------|

| MS | В  |         |          |        |         |          |        |                                                 |                                                 |          |         |        |       |             |                  |        |        |       |       |       |       |      | LSB   |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16     | 15                                              | 14                                              | 13       | 12      | 11     | 10    | 9           | 8                | 7      | 6      | 5     | 4     | 3     | 2     | 1    | 0     | Bit No. |

| 0  | 0  | 0       | 0        | 0      | 0       | 0        | 1      | 1                                               | 1                                               | 1        | 1       | 0      | 0     | Dep         | ends             | on F   | S0/FS  | 1 vol | ltage | level | after | powe | er up | default |

| A  | •  | EIDLE   | DATAPOL  | MODSEL | CPCUR   | LOCKMODE | PACTRL | TXPOWER                                         | [1:0]                                           | Set to 1 | LNAGAIN | OPMODE | [1:0] | RR<br>[9:0] |                  |        |        |       |       |       |       |      |       |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16     | 15                                              | 14                                              | 13       | 12      | 11     | 10    | 9           | 8                | 7      | 6      | 5     | 4     | 3     | 2     | 1    | 0     | Bit No. |

| 0  | 1  | 0       | 1        | 1      | 1       | 0        | 0      | 1                                               | 1                                               | 1        | 0       | 1      | 0     | Dep         | ends             | on F   | S0/FS  | 1 vol | ltage | level | after | powe | er up | default |

| E  | 3  | PKDET   | Set to 1 | DELPLL | LNAHYST | AFC      | 0A2    |                                                 | ROMAX<br>[2:0]<br>ROMIN<br>[2:0]<br>RT<br>[9:0] |          |         |        |       |             |                  |        |        |       |       |       |       |      |       |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16     | 15                                              | 14                                              | 13       | 12      | 11     | 10    | 9           | 8                | 7      | 6      | 5     | 4     | 3     | 2     | 1    | 0     | Bit No. |

| 1  | 0  | 0       | 0        |        |         |          |        |                                                 | Dep                                             | ends     | on F    | S0/F   | S1 vo | tage        | level            | after  | powe   | r up  |       |       |       |      |       | default |

|    |    | LNACTRL | PFDPOL   | VCOCUR | [1:0]   | BAND     |        |                                                 |                                                 |          |         |        |       |             | NR<br>[ 16 : 0 ] | •      |        |       |       |       |       |      |       |         |

| 23 | 22 | 21      | 20       | 19     | 18      | 17       | 16     | 15                                              | 14                                              | 13       | 12      | 11     | 10    | 9           | 8                | 7      | 6      | 5     | 4     | 3     | 2     | 1    | 0     | Bit No. |

| 1  | 1  | 0       | 0        | 1      | 0       | 0        |        |                                                 |                                                 | D        | epen    | ds or  | FS0   | /FS1        | volta            | ge lev | el aft | er po | wer u | ıp    |       |      |       | default |

|    | )  | MODCTRL | LDTM     | [1:0]  | ERTM    | [1:0]    |        | Depends on FS0/FS1 voltage level after power up |                                                 |          |         |        |       |             |                  |        |        |       |       |       |       |      |       |         |

## 5.1.1 Default Register Settings for FS0, FS1

| FS1 | FS0 | Channel frequency | BAND | VCOCUR<br>[1:0] | RR<br>[9:0] | NR<br>[ 16 :0 ] | RT<br>[9:0] | NT<br>[16:0] |

|-----|-----|-------------------|------|-----------------|-------------|-----------------|-------------|--------------|

| 0   | 0   | 868.30 MHz        | 1    | 11              | 16d         | 1919d           | 16d         | 1943d        |

| 0   | 1   | 433.92 MHz        | 0    | 01              | 32d         | 1894d           | 32d         | 1942d        |

| 1   | 0   | 915.00 MHz        | 1    | 11              | 32d         | 4047d           | 32d         | 4095d        |

| 1   | 1   | 315.00 MHz        | 0    | 00              | 18d         | 766d            | 18d         | 793d         |

Note: d – decimal code

A detailed description of the registers function and their configuration can be found in the following sections.

## 5.1.2 A – word

| Name     | Bits    |                | Description                                                                                           |            |  |  |  |  |

|----------|---------|----------------|-------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

|          | ro      |                | Reference divider ratio in RX operation mode                                                          |            |  |  |  |  |

| RR       | [9:0]   | 4d             | 1023d                                                                                                 |            |  |  |  |  |

|          |         |                | Operation mode                                                                                        |            |  |  |  |  |

| OPMODE   | [11:10] | 00<br>01<br>10 |                                                                                                       | #default   |  |  |  |  |

|          |         | 11             | Idle mode                                                                                             |            |  |  |  |  |

|          |         |                | LNA gain                                                                                              |            |  |  |  |  |

| LNAGAIN  | [12]    | 0              | low LNA gain                                                                                          |            |  |  |  |  |

|          |         | 1              |                                                                                                       | #default   |  |  |  |  |

|          | [40]    |                | This selection is valid if bit LNACTR (bit 21 in C-word) is set to internal LNA gain                  | control.   |  |  |  |  |

| not used | [13]    |                | set to '1' for correct function                                                                       |            |  |  |  |  |

|          |         |                | Output power steps                                                                                    |            |  |  |  |  |

| TXPOWER  | [15:14] | 00<br>01       | P1<br>P2                                                                                              |            |  |  |  |  |

|          |         | 10             | P3                                                                                                    |            |  |  |  |  |

|          |         | 11             | P4                                                                                                    | #default   |  |  |  |  |

|          |         |                | Set the PA-on condition                                                                               |            |  |  |  |  |

| PACTRL   | [16]    | 0              | PA is switched on if the PLL locks                                                                    |            |  |  |  |  |

|          |         | 1              | ,                                                                                                     | #default   |  |  |  |  |

|          |         | 0              | Set the PLL locked state observation mode before lock only                                            | #default   |  |  |  |  |

| LOCKMODE | [17]    | U              | Locked state condition will be ascertained only one time afterwards the LD signal remains high state. |            |  |  |  |  |

|          |         | 1              | before and after lock                                                                                 |            |  |  |  |  |

|          |         |                | locked state will be observed permanently                                                             |            |  |  |  |  |

|          |         |                | Charge Pump output current                                                                            |            |  |  |  |  |

| CPCUR    | [18]    | 0              |                                                                                                       | #default   |  |  |  |  |

|          |         | 1              | 1300 μΑ                                                                                               |            |  |  |  |  |

|          |         |                | Modulation mode                                                                                       | 41-6-11    |  |  |  |  |

| MODSEL   | [19]    | 0              | ASK<br>FSK                                                                                            | #default   |  |  |  |  |

|          |         | •              | This selection is valid if bit MODCTRL (bit 21 in D-word) is set to internal control.                 | modulation |  |  |  |  |

|          |         |                | Input data polarity                                                                                   |            |  |  |  |  |

|          |         | 0              | , , , , , , , , , , , , , , , , , , , ,                                                               | #default   |  |  |  |  |

| DTAPOL   | [20]    |                | '0' for space at ASK or f <sub>min</sub> at FSK, '1' for mark at ASK or f <sub>max</sub> at FSK       |            |  |  |  |  |

|          |         | 1              | inverse                                                                                               |            |  |  |  |  |

|          |         |                | '1' for space at ASK or $f_{\text{min}}$ at FSK, '0' for mark at ASK or $f_{\text{max}}$ at FSK       |            |  |  |  |  |

|          |         |                | Active blocks in IDLE mode                                                                            |            |  |  |  |  |

| IDLESEL  | [21]    | 0<br>1         | only RO active whole PLL active                                                                       | #default   |  |  |  |  |

## TH7122 27 to 930MHz FSK/FM/ASK Transceiver

### 5.1.3 B – word

| Name        | Bits    |                                                      |                                                                           |                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |  |  |  |  |

|-------------|---------|------------------------------------------------------|---------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| рт          | [0.0]   |                                                      |                                                                           | Referenc         | e divider ratio in TX operation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |  |  |  |  |

| RT          | [9:0]   | 4d                                                   | 1023d                                                                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                        |  |  |  |  |

|             |         |                                                      | Set the                                                                   | e desired st     | eady state current of the reference oscill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | lator                                                                                                                                  |  |  |  |  |

| ROMIN       | [12:10] | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 0 μA<br>75 μA<br>150 μA<br>225 μA<br>300 μA<br>375 μA<br>450 μA<br>525 μA | #default         | The control circuitry regulates the current of the between the values ROMAX and ROMIN. As the signal the amplitude on pin RO is used. If the sufficient to achieve an amplitude of about 400 no current of the reference oscillator core will be Otherwise the current will be permanently re ROMAX and ROMIN. If ROMIN and ROMA regulation of the oscillator current occurs. Plead block description of the reference oscillator in particular current occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e regulation input<br>ROMIN value is<br>nV on pin RO the<br>e set to ROMIN.<br>egulated between<br>X are equal no<br>ase also note the |  |  |  |  |

|             |         |                                                      |                                                                           | Set the star     | rt-up current of the reference oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                        |  |  |  |  |

| ROMAX       | [15:13] | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 0 μA<br>75 μA<br>150 μA<br>225 μA<br>300 μA<br>375 μA<br>450 μA<br>525 μA | #default         | Set the start-up current of the reference oscilla also note the description of the ROMIN regist description of the reference oscillator which can be seen to be seen | er and the block                                                                                                                       |  |  |  |  |