fido1100® Data Sheet

**32-Bit Real-Time Communications Controller**

Copyright © 2013 by Innovasic, Inc.

Published by Innovasic, Inc. 5635 Jefferson St. NE, Suite A, Albuquerque, New Mexico 87109 USA

fido®, fido1100®, and SPIDER™ are trademarks of Innovasic, Inc.  $I^2C^{\mathsf{TM}}$  Bus is a trademark of Philips Electronics N.V. Motorola® is a registered trademark of Motorola, Inc.

# **TABLE OF CONTENTS**

| List | of Fig | gures                                                 | 5  |  |  |  |

|------|--------|-------------------------------------------------------|----|--|--|--|

| List | of Tal | bles                                                  | 6  |  |  |  |

| 1.   | Ove    | rview                                                 | 7  |  |  |  |

| 2.   | Feat   | tures                                                 | 9  |  |  |  |

|      | 2.1    | Core CPU                                              | 10 |  |  |  |

|      | 2.2    | JTAG                                                  | 10 |  |  |  |

|      | 2.3    | Internal Memory and Memory Management                 | 11 |  |  |  |

|      | 2.4    | External Bus Interface                                | 12 |  |  |  |

|      | 2.5    | PMU/UIC/CPU DMA                                       | 12 |  |  |  |

|      | 2.6    | Internal Peripherals                                  | 13 |  |  |  |

|      |        | 2.6.1 Timer Counter Units (TCU)                       | 13 |  |  |  |

|      |        | 2.6.2 Analog-to-Digital Converter (ADC)               | 14 |  |  |  |

|      |        | 2.6.3 Timers                                          | 14 |  |  |  |

|      | 2.7    | Power Control                                         | 14 |  |  |  |

| 3.   | Libr   | raries and Support Tools                              | 15 |  |  |  |

| 4.   | Pack   | Packaging, Pin Descriptions, and Physical Dimensions. |    |  |  |  |

|      | 4.1    | PQFP Package                                          | 17 |  |  |  |

|      |        | 4.1.1 PQFP Pinout                                     |    |  |  |  |

|      |        | 4.1.2 PQFP Physical Dimensions                        | 24 |  |  |  |

|      | 4.2    | BGA 15- by 15-mm Package                              | 25 |  |  |  |

|      |        | 4.2.1 BGA 15- by 15-mm Pinout                         |    |  |  |  |

|      |        | 4.2.2 BGA 15- by 15-mm Physical Package Dimensions    | 33 |  |  |  |

|      |        | 4.2.3 BGA 15- by 15-mm Signal Routing                 |    |  |  |  |

|      | 4.3    | Power and Ground Signals                              |    |  |  |  |

| 5.   | Elec   | etrical Characteristics                               |    |  |  |  |

| 6.   | The    | rmal Characteristics                                  | 41 |  |  |  |

| 7.   | Rese   | et                                                    | 42 |  |  |  |

|      | 7.1    | Overview                                              | 42 |  |  |  |

|      | 7.2    | Signal Considerations and Reset Timing                | 42 |  |  |  |

|      | 7.3    | Clock Signals                                         |    |  |  |  |

|      | 7.4    | Typical Clock Source Implementations                  | 44 |  |  |  |

|      |        | 7.4.1 Normal or Driven Clock Source                   | 44 |  |  |  |

|      |        | 7.4.2 Using an External Crystal                       | 44 |  |  |  |

|      | 7.5    | 7.5 Off-Chip Component Value                          |    |  |  |  |

| 8.   | Sign   | nals                                                  | 47 |  |  |  |

|      | 8.1    | External Bus Operation                                | 47 |  |  |  |

|      |        | 8.1.1 Overview                                        | 47 |  |  |  |

|      |        |                                                       |    |  |  |  |

|     | 8.2          | Gener                  | al Setup and Hold Timing                                          | 47 |  |  |

|-----|--------------|------------------------|-------------------------------------------------------------------|----|--|--|

|     | 8.3          |                        |                                                                   |    |  |  |

| 9.  | Setu         | Setup and Hold Timing. |                                                                   |    |  |  |

|     | •            | 9.1.1                  | External Bus Timing for a 32-Bit Transfer (without RDY_N)         |    |  |  |

|     |              | 9.1.2                  | External Bus Timing for a 32-Bit Transfer (with RDY_N)            |    |  |  |

|     |              | 9.1.3                  | External Bus Timing for 8-Bit/16-Bit Transfer (without RDY_N)     |    |  |  |

|     |              | 9.1.4                  | External Bus Timing for 8-Bit/16-Bit Transfer (with RDY_N)        | 55 |  |  |

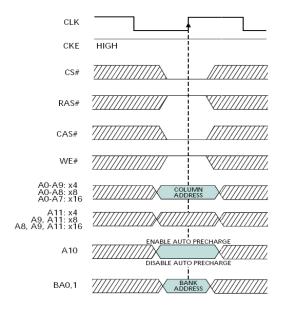

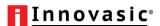

|     | 9.2          | SDRA                   | AM Timing                                                         |    |  |  |

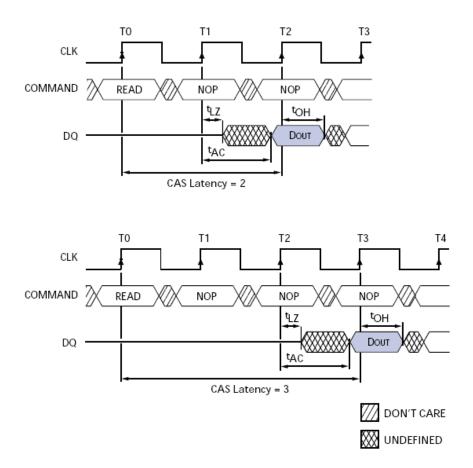

|     |              | 9.2.1                  | SDRAM CAS Timing                                                  |    |  |  |

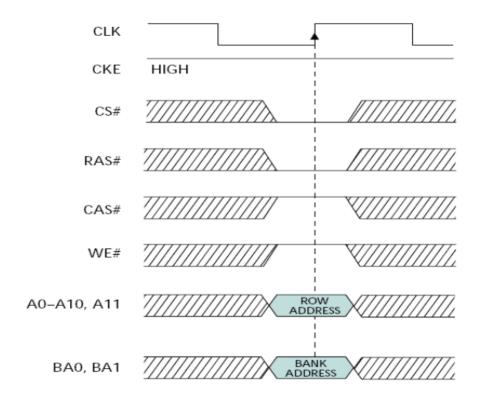

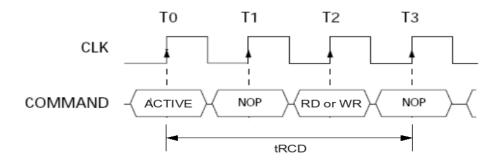

|     |              | 9.2.2                  | SDRAM Row Activation Timing                                       |    |  |  |

|     |              | 9.2.3                  | SDRAM Read Operation Timing                                       |    |  |  |

|     |              | 9.2.4                  | SDRAM Read Burst Timing                                           |    |  |  |

|     |              | 9.2.5                  | SDRAM Write Operation, Write Burst, Write-to-Write, and Write-to- |    |  |  |

|     |              |                        | Precharge Timing.                                                 | 60 |  |  |

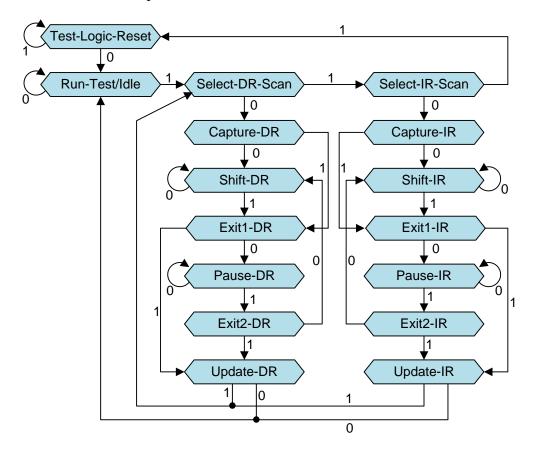

| 10. | JTA          | G                      |                                                                   | 64 |  |  |

|     | 10.1         | JTAG                   | Scan Chain Debug Functionality                                    | 65 |  |  |

| 11. |              |                        | formation                                                         |    |  |  |

| 12. | Errata       |                        |                                                                   |    |  |  |

|     | 12.1 Summary |                        |                                                                   |    |  |  |

|     | 12.2 Detail  |                        |                                                                   |    |  |  |

| 13. |              |                        |                                                                   |    |  |  |

| 1/  |              |                        | nal Information                                                   | 74 |  |  |

# **LIST OF FIGURES**

| Figure 1. Block Diagram for the fido1100                                  | 8  |

|---------------------------------------------------------------------------|----|

| Figure 2. PQFP Package Diagram                                            | 17 |

| Figure 3. PQFP Physical Package Dimensions                                | 24 |

| Figure 4. BGA 15- by 15-mm Package Diagram                                | 26 |

| Figure 5. BGA 15- by 15-mm Physical Package Dimensions                    | 33 |

| Figure 6. BGA 15- by 15-mm Signal Routing                                 | 35 |

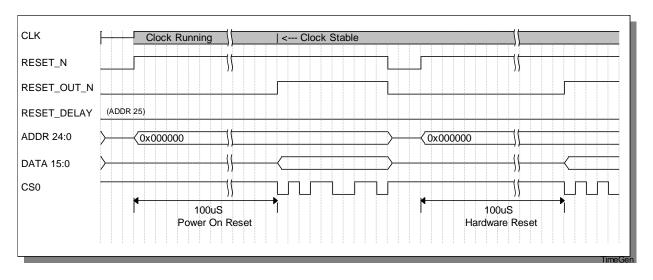

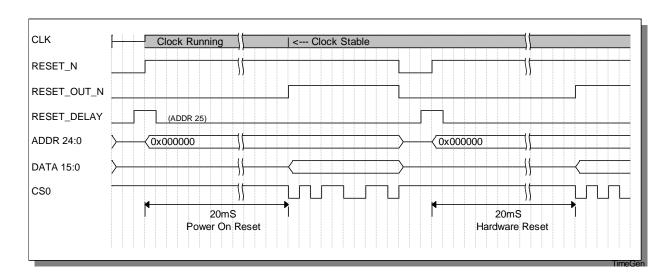

| Figure 7. Reset Timing                                                    | 43 |

| Figure 8. Extended Reset Timing                                           | 43 |

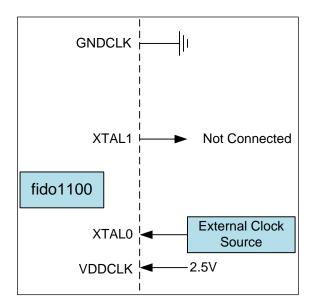

| Figure 9. Driven Clock Source                                             |    |

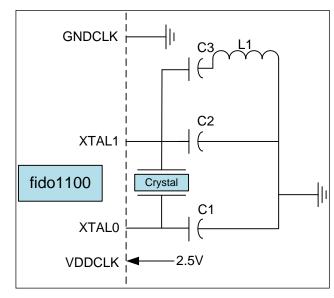

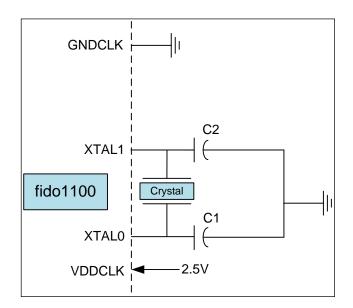

| Figure 10. Crystal Oscillator Third Overtone Off-Chip Components          | 45 |

| Figure 11. Crystal Oscillator Fundamental Overtone Off-Chip Components    |    |

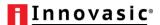

| Figure 12. Propagation Delay                                              |    |

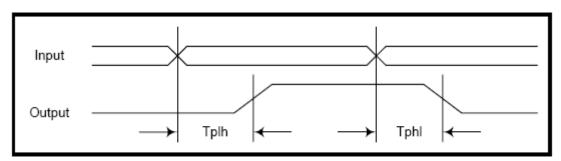

| Figure 13. Setup Time                                                     | 49 |

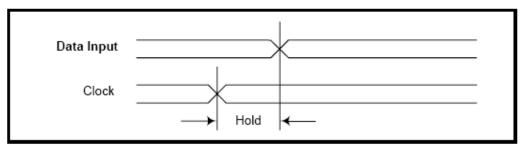

| Figure 14. Hold Time                                                      | 50 |

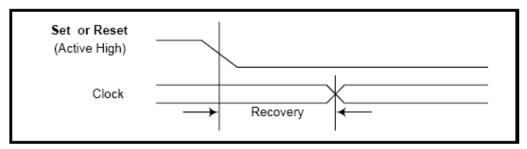

| Figure 15. Recovery Time                                                  | 50 |

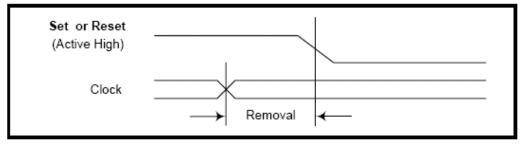

| Figure 16. Removal Time                                                   | 50 |

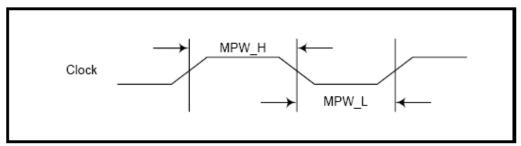

| Figure 17. Minimum Pulse Width                                            | 51 |

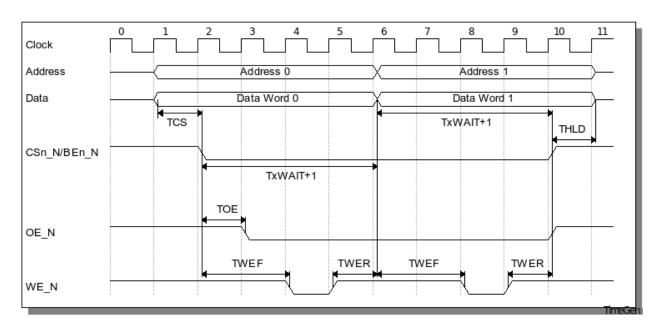

| Figure 18. External Bus Timing for a Single, 32-Bit Cycle (without RDY_N) | 52 |

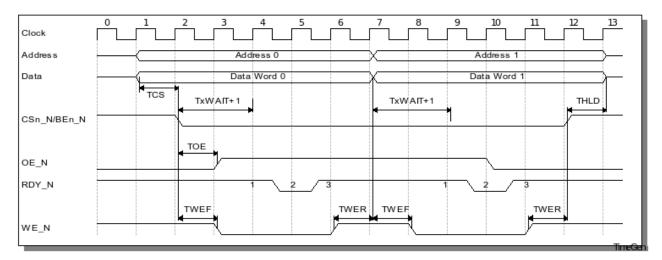

| Figure 19. External Bus Timing for a 32-Bit Transfer (with RDY_N)         | 53 |

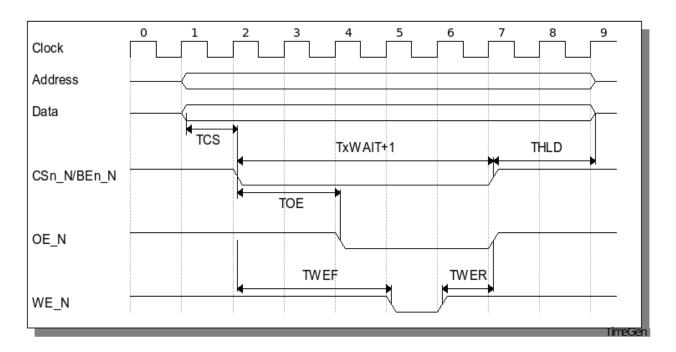

| Figure 20. External Bus Timing for 8-Bit/16-Bit Transfer (without RDY_N)  | 54 |

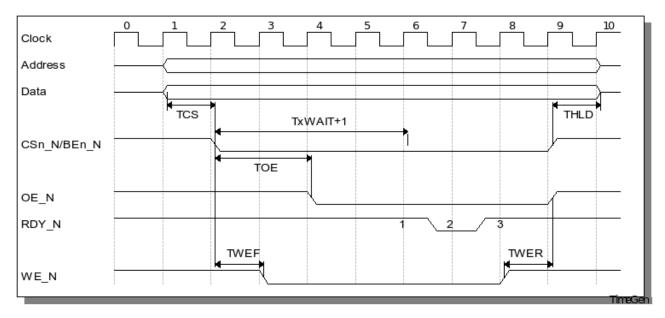

| Figure 21. External Bus Timing for 8-Bit/16-Bit Transfer (with RDY_N)     | 55 |

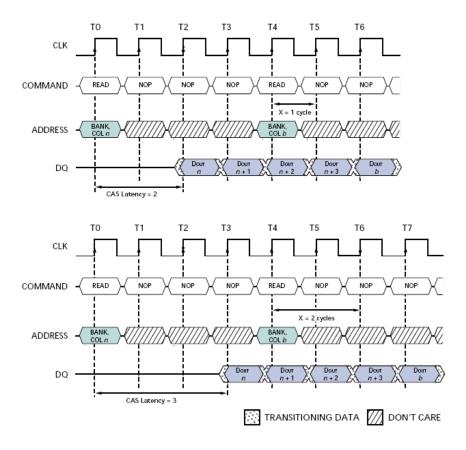

| Figure 22. SDRAM CAS Timing                                               | 57 |

| Figure 23. Specific Row Activation Timing                                 | 58 |

| Figure 24. Meeting tRCD (min) When $2 < tRCD \text{ (min)/tCK} \le 3$     | 58 |

| Figure 25. SDRAM Read Operation Timing                                    | 59 |

| Figure 26. SDRAM Read Burst Timing                                        | 60 |

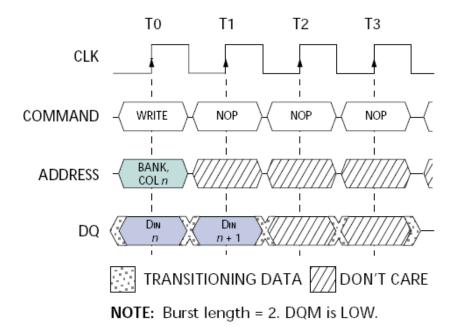

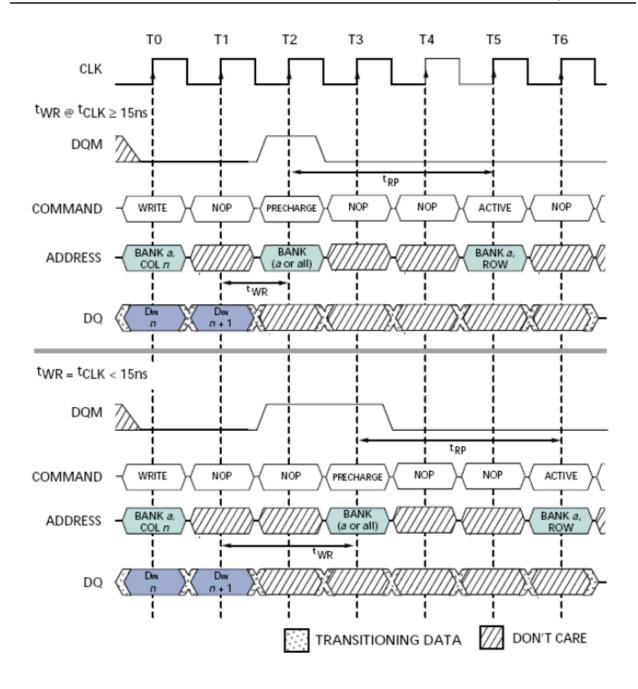

| Figure 27. SDRAM Write Operation Timing                                   | 61 |

| Figure 28. SDRAM Write Burst Timing                                       | 62 |

| Figure 29. SDRAM Write-to-Write Timing                                    | 62 |

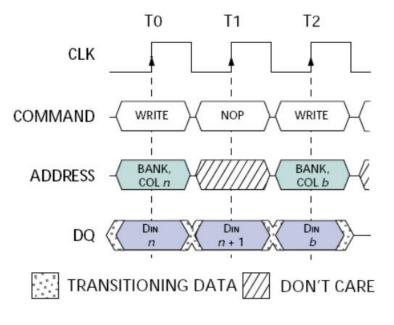

| Figure 30. SDRAM Write-to-Precharge Timing                                | 63 |

| Figure 31. JTAG State Machine                                             | 64 |

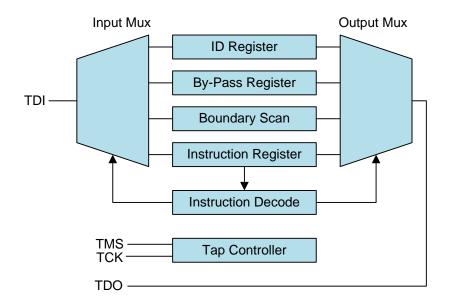

| Figure 32. JTAG Port Register Interface                                   | 65 |

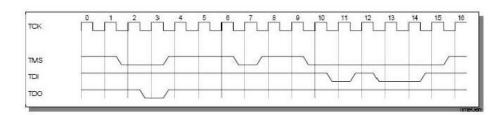

| Figure 33. Timing of JTAG Signals                                         | 65 |

|                                                                           |    |

# **LIST OF TABLES**

| Table 1. Key Features                                         |    |

|---------------------------------------------------------------|----|

| Table 2. Test Pin Descriptions                                | 11 |

| Table 3. PQFP Pin Listing                                     | 18 |

| Table 4. BGA 15- by 15-mm Package Pin Listing                 | 27 |

| Table 5. Analog Power and Ground Signals                      | 36 |

| Table 6. Crystal Oscillator Power and Ground Signals          | 36 |

| Table 7. 2.5 VDC Digital Core Power Signals                   | 36 |

| Table 8. 3.3 VDC Digital IO Power Signals                     | 37 |

| Table 9. Digital Ground Signals                               | 37 |

| Table 10. Absolute Maximum Ratings                            | 38 |

| Table 11. ESD and Latch-Up Characteristics                    | 38 |

| Table 12. Recommended Operating Conditions                    | 38 |

| Table 13. DC Characteristics                                  | 39 |

| Table 14. Input Impedance                                     | 39 |

| Table 15. AC Characteristics of Crystal Oscillator            | 39 |

| Table 16. Analog-to-Digital Converter Characteristics         | 40 |

| Table 17. Power Consumption                                   | 40 |

| Table 18. Thermal Resistance Characteristics                  | 41 |

| Table 19. Hardware Signals Involved When Asserting Reset      | 42 |

| Table 20. Suggested Off-Chip Component Values                 | 46 |

| Table 21. Debug Scan Chain Commands Supported by the JTAG TAP | 66 |

| Table 22. Part Numbers by Package Types                       |    |

| Table 23. Summary of Errata                                   | 68 |

| Table 24. Revision History                                    | 72 |

|                                                               |    |

#### 1. Overview

Innovasic Semiconductor's fido1100 is the first product in the fido™ family of real-time communication controllers. The fido communication controller architecture is uniquely optimized for solving memory bottlenecks, and is designed from the ground up for deterministic processing. Critical timing parameters, such as context switching and interrupt latency, are precisely predictable for real-time tasks. The fido1100 also incorporates the Universal I/O Controller (UIC™) that is configurable to support various communication protocols across multiple platforms. This flexibility relieves the designer of the task of searching product matrices to find the set of peripherals that most closely match the system interface needs. The Software Profiling and Integrated Debug EnviRonment (SPIDER™) has extensive real-time code debug capabilities without the burden of code instrumentation (see Table 1).

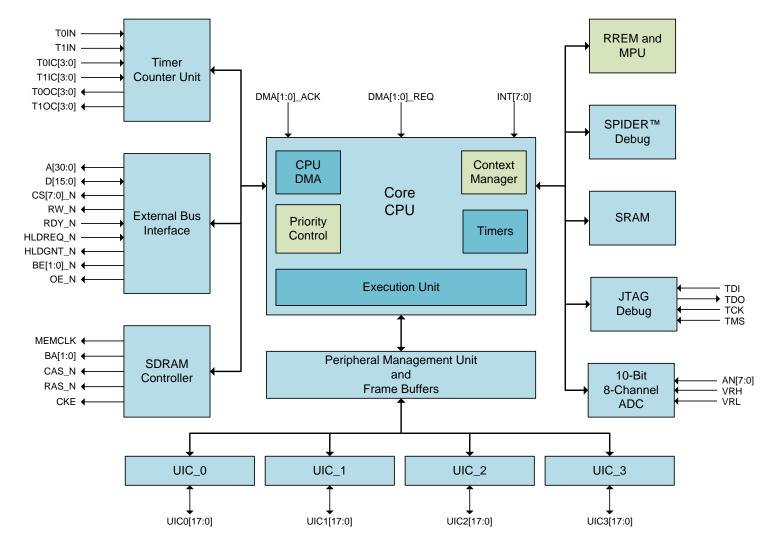

Figure 1 illustrates the top-level blocks of the fido1100 architecture.

Table 1. Key Features

| Features                | Benefits                                                                                                                                                                                                                       |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable UIC        | <ul> <li>Provides the ability to customize peripherals to match user application.</li> <li>Single chip can solve multiple end-product demands.</li> <li>Reduces costs through optimized inventory management.</li> </ul>       |

| Five Hardware Contexts  | <ul> <li>Runs tight-control loops in separate contexts while RTOS manages high level tasks in another context.</li> <li>Provides context isolation with robust time-and-space partitioning.</li> </ul>                         |

| Low-Jitter Execution    | <ul> <li>Performs tasks at much lower clock rates (66MHz versus<br/>&gt;200MHz), reducing power budget and simplifying board design.</li> </ul>                                                                                |

| SPIDER                  | <ul> <li>Reduces system integration and debug time through in-system, "what-if" testing without code changes.</li> <li>Reduces firmware development time thus cutting costs.</li> <li>Up to 1Mbyte of trace buffer.</li> </ul> |

| Long-Life-Cycle Support | <ul> <li>Fulfills Innovasic's corporate policy of supporting products for the<br/>customer's entire life-cycle, eliminating product obsolescence<br/>concerns.</li> </ul>                                                      |

Figure 1. Block Diagram for the fido1100

### 2. Features

The fido1100 communication controller's features include:

- 32-bit Core CPU

- CISC architecture optimized for real time

- CPU32+ (Motorola® 68000) instruction-set compatible

- Five hardware contexts, each with its own register set and interrupt vector table

- An 8- or 16-bit external bus interface with programmable chip selects

- 24 Kbytes of high-speed internal user SRAM

- 32 Kbytes of high-speed internal user-mappable Relocatable Rapid Execution Memory (RREM)

- A Memory Protection Unit (MPU)

- An SDRAM controller

- Flat, contiguous memory space

- Non-aligned memory access support

- Dedicated Peripheral Management Unit (PMU)

- Four Universal I/O Controllers (UICs) capable of supporting the following protocols:

- GPIO

- 10/100 Ethernet with flexible MAC Address Filtering schemes

- EIA-232

- CAN

- SPI

- $I^2C^{TM}$  Bus

- SMBus

- HDLC

- Two channels of full-featured direct memory access (DMA) with deterministic arbitration

- Two Timer/Counter Units (TCU)

- A Watchdog timer, system timer, and context timers

- JTAG emulation and debug interface

- Available in 208-pin PQFP and BGA 15- by 15-mm packages

- 3.3V operation with 5V-tolerant I/O

- Industrial temperature grade

- Software development supported by libraries and tools including UIC firmware for various interface protocols and formats, as well as a customized GNU tool set.

#### 2.1 Core CPU

The fido1100 core is based on the CPU32 architecture, and is compatible with the CPU32 instruction set. The fido1100 incorporates five independent hardware contexts. While all contexts share the same Execution Unit, each of the five hardware contexts in the fido1100 has its own register set, execution priority and exception vector table. From an application's view, this unique feature of the fido1100 allows it to operate as five independent machines in one:

- 32-bit address and data paths on-chip

- 66-MHz operation

- Instruction execution from external memory or fast internal memory.

- Each hardware context has its own copy of:

- Eight 32-bit User Data Registers (D0-D7)

- Seven 32-bit Address Registers (A0-A6)

- Two 32-bit Stack Pointers (A7 and A7')

- One 32-bit Program Counter

- One 16-bit Status Register (SR)

- One 32-bit Vector Base Register (VBR)

#### 2.2 JTAG

The fido1100 is fully compliant with the IEEE 1149.1 Test Access Port and Boundary-Scan architecture (see Table 2). The fido1100 architecture is equipped with the TAP (Test Access Port) interface, TAP controller, instruction register, instruction decoder, boundary-scan register, and by-pass register.

#### **Table 2. Test Pin Descriptions**

| Pin | Direction | Description                                                                                                                                                                                                                  |  |  |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TDO | In        | Test Data Output—The tri-state test data output changing on the falling edge of the                                                                                                                                          |  |  |

|     |           | TCK input. This is actively driven only in the shift-DR and shift-IR controller states.                                                                                                                                      |  |  |

| TDI | In        | Test Data Input—The test data input sampled on the rising edge of the TCK input.                                                                                                                                             |  |  |

| TMS | In        | Test Mode Select Input—The test mode select input used to sequence the TAP controller state machine. If TMS is a 1 for 5 clock cycles, it sends the TAP controller into reset. If TMS is 0, the TAP controller goes to IDLE. |  |  |

| TCK | ln        | Test Clock Input—All JTAG commands and serial data are synchronized by this signal.                                                                                                                                          |  |  |

The JTAG Interface is used for controlling the SPIDER Debug Features of the fido1100.

- Breakpoints—Eight hardware context-aware breakpoints that can be chained to set up if/then triggering conditions.

- Hardware breakpoints are enabled in software or over JTAG

- Watchpoints—Eight hardware watchpoints.

- Trace—Follow program execution with trace buffers.

- Single address, single buffer, and circular buffer trace modes

- Trace buffer can be written anywhere in the address space or to a peripheral

- Debug Control—Hardware single-step and context status control.

- Access to all memory and registers that are accessible to software

- Byte, word, and long-word access in full-address mode or offset mode

- Invalid address access (keystroke errors) over JTAG will not kill the session

- Direct programming of FLASH on the evaluation board without target software support

- Built-in hardware support to halt contexts and execute single instructions without software

- JTAG access to registers, stack space, etc., even if the processor is halted

- Statistical Profiling—SPIDER provides statistical software profiling to identify critical pieces of code.

#### 2.3 Internal Memory and Memory Management

- User SRAM—Internal 24-Kbyte memory that can be used by applications for general purpose data needs or as trace buffers.

- Relocatable Rapid Execution Memory (RREM)—Internal 32-Kbyte memory that can be used as an instruction source for code that requires maximum execution speed.

• Memory Protection Unit (MPU)—Access-control method for 16 user-configurable blocks of internal or external memory on a context basis. A block of memory may be inaccessible, read only or read/write accessible to a selectable set of contexts. The MPU provides the space partitioning needed in deterministic, real-time systems.

#### 2.4 External Bus Interface

The interface to all external memory. It handles memory interface timing and arbitration of external bus requests. The external bus interfaces provide all address, data, and control line to implement either an 8- or 16-bit microcontroller system bus.

- Address/data bus

- 31-bit address bus to access up to 2 Gbytes of memory space

- 8- or 16-bit data bus

- Zero-overhead Endian conversion

- Chip Selects—Eight programmable chip selects with programmable size, data width, and timing.

- SDRAM Controller—Supports 8- or 16-bit data interfaces to SDRAM and provides the necessary control signals to interface to external SDRAM. The interface to the external SDRAM uses the 16-bit-wide data bus and 13 bits of the address bus of the External Bus Interface. The dedicated clock signal for this interface (MEMCLK) operates at the same frequency as the internal master clock.

- Operates at a maximum clock rate of 66 MHz

- Executes read, write, pre-charge, auto refresh, power down, and initialize SDRAM modes

- Fixed, 4-word bursts to/from SDRAM interface

- Periodically issues auto refresh command to prevent SDRAM data loss

- External Bus Arbitration—The fido1100 provides signals to allow it to operate in a multibus master environment.

#### 2.5 PMU/UIC/CPU DMA

The PMU, UIC, and CPU DMA work together as a fast data transport scheme that requires minimal Core CPU overhead or intervention.

- Peripheral Management Unit (PMU)—A set of user-configurable buffers for data transmission and reception via the UICs.

- Universal Input/Output Controller (UIC)—Programmable protocol engine.

The UIC is a very flexible hardware solution designed to support numerous interface requirements. When working in concert with the on-board Peripheral Management Unit (PMU) and on-board data buffers, the operation of the interfaces requires little core processor intervention. This allows the processor to use its bus bandwidth for more important functions than managing data traffic. The UIC design can support complex protocols such as Ethernet or GPIO functions.

- Four software-configurable UICs

- Each supports 10/100 Ethernet, CAN, UART, SPI, I<sup>2</sup>C, HDLC, or GPIO functionality

- Software libraries are provided for various interface protocols and formats

- User-programmable integrated 256-location MAC address filter

- Dedicated PMU offloads main CPU bus traffic

- Large 1K  $\times$  32 transmit buffer and 2K  $\times$  32 receive buffers

- At a minimum, each UIC can support 1 Ethernet port (MII), 2 UARTs, or 18 GPIO

- CPU DMA—Two independent channels of DMA for data transfer

## 2.6 Internal Peripherals

The fido 1100 incorporates the following set of internal peripherals:

#### 2.6.1 Timer Counter Units (TCU)

- Two Timer Counter Units (TCU)—The fido1100 is equipped with two Timer Counter Units.

- Four channels per timer; any channel can be either input capture or output compare.

- Input captures can be either rising or falling edge.

- External signal clocking can be rising edge, falling edge, or both edges of input signal.

- Output compare can be assert high, assert low, or toggle mode.

- Underflow, overflow, input-capture, or output-compare conditions can trigger an interrupt.

- Timers can be programmed for auto-stop or auto-reload.

- Timer can generate an internal interrupt to wake up the processor from sleep mode.

- Timer periods in excess of 50 seconds are achievable.

## 2.6.2 Analog-to-Digital Converter (ADC)

- 8-channel, 10-bit ADC

- Maximum throughput rate of 200 Kbps

- High- and low-reference voltage pins ensure accuracy and temperature compensation

- Very low 5-mW power consumption and includes a built-in power-down mode

- Single- or multiple-channel conversion scan modes

- Interrupt generated at the end of conversion is assigned a priority and a context

- Interrupts from the analog-to-digital converter can be disabled

#### **2.6.3 Timers**

- System Timer.

- Provides five periodic System Timer interrupts.

- o 16-bit counter with 16-bit prescale allows a range of System Timer interrupts from 80 nS to 50 seconds with a 66-MHz system clock.

- These interrupts can be assigned to the fast-context switching hardware providing a zero overhead system executive or the System Timer interrupts can simply produce a traditional vectored interrupt request to provide a system with basic timing needs.

- Watchdog Timer

- 16-bit counter with an 11-bit prescaler

- Context Timers

- Each hardware context has a set of timing registers that can track, specify, and limit execution time.

#### 2.7 Power Control

All internal peripherals can be put into a low-power consumption mode.

# 3. Libraries and Support Tools

- Full library support

- UIC libraries

- Embedded communication stacks

- TCP/IP

- GPIO sample programs

- Customized GNU tool set

- Eclipse IDE

- Sourcery G++ from Code Sourcery

# 4. Packaging, Pin Descriptions, and Physical Dimensions

Information on the packages and pin descriptions for the fido1100 communication controller PQFP and BGA 15- by 15-mm package is provided individually. Refer to sections, figures, and tables for information on the device of interest.

#### 4.1 PQFP Package

#### 4.1.1 PQFP Pinout

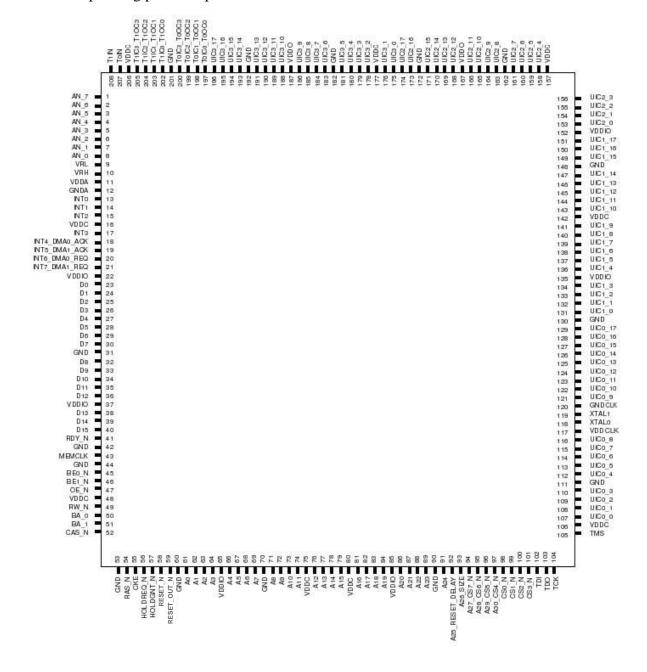

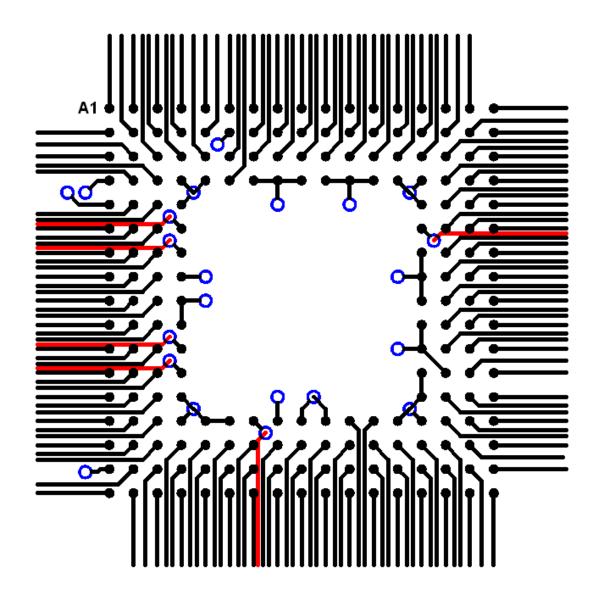

The pinout for the fido1100 communication controller PQFP package is as shown in Figure 2. The corresponding pinout is provided in Table 3.

Figure 2. PQFP Package Diagram

# Table 3. PQFP Pin Listing

| Pin | Signal Name       | Туре          | Description                                         |

|-----|-------------------|---------------|-----------------------------------------------------|

| 1   | AN_7              | Input         | Analog-to-digital converter input channel 7         |

| 2   | AN_6              | Input         | Analog-to-digital converter input channel 6         |

| 3   | AN_5              | Input         | Analog-to-digital converter input channel 5         |

| 4   | AN_4              | Input         | Analog-to-digital converter input channel 4         |

| 5   | AN_3              | Input         | Analog-to-digital converter input channel 3         |

| 6   | AN_2              | Input         | Analog-to-digital converter input channel 2         |

| 7   | AN_1              | Input         | Analog-to-digital converter input channel 1         |

| 8   | AN_0              | Input         | Analog-to-digital converter input channel 0         |

| 9   | VRL               | Input         | Analog-to-digital converter low-input reference     |

| 10  | VRH               | Input         | Analog-to-digital converter high-input reference    |

| 11  | VDDA              | Power         | Analog supply voltage (+3.3VDC)                     |

| 12  | GNDA              | Ground        | Analog ground                                       |

| 13  | INT0              | Input         | Interrupt_0                                         |

| 14  | INT1              | Input         | Interrupt_1                                         |

| 15  | INT2              | Input         | Interrupt_2                                         |

| 16  | VDDC              | Power         | Digital core supply voltage (+2.5VDC)               |

| 17  | INT3              | Input         | Interrupt_3                                         |

| 18  | INT4_DMA0_<br>ACK | Bidirectional | Muxed pin, Interrupt_4 or DMA channel 0 acknowledge |

| 19  | INT5_DMA1_<br>ACK | Bidirectional | Muxed pin, Interrupt_5 or DMA channel 1 acknowledge |

| 20  | INT6_DMA0_<br>REQ | Input         | Muxed pin, Interrupt_6 or DMA channel 0 request     |

| 21  | INT7_DMA1_<br>REQ | Input         | Muxed pin, Interrupt_7 or DMA channel 1 request     |

| 22  | VDDIO             | Power         | Digital I/O supply voltage (+3.3VDC)                |

| 23  | D0                | Bidirectional | External Bus Interface data Bit [0]                 |

| 24  | D1                | Bidirectional | External Bus Interface data Bit [1]                 |

| 25  | D2                | Bidirectional | External Bus Interface data Bit [2]                 |

| 26  | D3                | Bidirectional | External Bus Interface data Bit [3]                 |

| 27  | D4                | Bidirectional | External Bus Interface data Bit [4]                 |

| 28  | D5                | Bidirectional | External Bus Interface data Bit [5]                 |

| 29  | D6                | Bidirectional | External Bus Interface data Bit [6]                 |

| 30  | D7                | Bidirectional | External Bus Interface data Bit [7]                 |

| 31  | GND               | Ground        | Digital ground                                      |

| 32  | D8                | Bidirectional | External Bus Interface data Bit [8]                 |

| 33  | D9                | Bidirectional | External Bus Interface data Bit [9]                 |

| 34  | D10               | Bidirectional | External Bus Interface data Bit [10]                |

| 35  | D11               | Bidirectional | External Bus Interface data Bit [11]                |

Table 3. PQFP Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                                        |

|-----|-------------|---------------|----------------------------------------------------|

| 36  | D12         | Bidirectional | External Bus Interface data Bit [12]               |

| 37  | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)               |

| 38  | D13         | Bidirectional | External Bus Interface data Bit [13]               |

| 39  | D14         | Bidirectional | External Bus Interface data Bit [14]               |

| 40  | D15         | Bidirectional | External Bus Interface data Bit [15]               |

| 41  | RDY_N       | Input         | External Bus Interface External Ready Indication   |

| 42  | GND         | Ground        | Digital ground                                     |

| 43  | MEMCLK      | Output        | Memory clock used by external memory               |

| 44  | GND         | Ground        | Digital ground                                     |

| 45  | BE0_N       | Output        | Byte enable 0, active low                          |

| 46  | BE1_N       | Output        | Byte enable 1, active low                          |

| 47  | OE_N        | Output        | Output enable, active low                          |

| 48  | VDDC        | Power         | Digital core supply voltage (+2.5VDC)              |

| 49  | RW_N        | Output        | Read or write control (active low write)           |

| 50  | BA_0        | Output        | Bank Enable 0                                      |

| 51  | BA_1        | Output        | Bank Enable 1                                      |

| 52  | CAS_N       | Output        | Column activate signal, active low                 |

| 53  | GND         | Ground        | Digital Ground                                     |

| 54  | RAS_N       | Output        | Row activate signal, active low                    |

| 55  | CKE         | Output        | Clock enable to be used in conjunction with MEMCLK |

| 56  | HOLDREQ_N   | Input         | External Bus hold request, active low              |

| 57  | HOLDGNT_N   | Output        | External Bus grant request, active low             |

| 58  | RESET_N     | Input         | Reset input                                        |

| 59  | RESET_OUT_N | Output        | Reset output                                       |

| 60  | GND         | Ground        | Digital ground                                     |

| 61  | A0          | Output        | External Bus Interface address Bit [0]             |

| 62  | A1          | Output        | External Bus Interface address Bit [1]             |

| 63  | A2          | Output        | External Bus Interface address Bit [2]             |

| 64  | A3          | Output        | External Bus Interface address Bit [3]             |

| 65  | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)               |

| 66  | A4          | Output        | External Bus Interface address Bit [4]             |

| 67  | A5          | Output        | External Bus Interface address Bit [5]             |

| 68  | A6          | Output        | External Bus Interface address Bit [6]             |

| 69  | A7          | Output        | External Bus Interface address Bit [7]             |

| 70  | GND         | Ground        | Digital ground                                     |

| 71  | A8          | Output        | External Bus Interface address Bit [8]             |

| 72  | A9          | Output        | External Bus Interface address Bit [9]             |

| 73  | A10         | Output        | External Bus Interface address Bit [10]            |

| 74  | A11         | Output        | External Bus Interface address Bit [11]            |

Table 3. PQFP Pin Listing (Continued)

| Pin | Signal Name | Type                | Description                                                                                       |

|-----|-------------|---------------------|---------------------------------------------------------------------------------------------------|

| 75  | VDDC        | Power               | Digital core supply voltage (+2.5VDC)                                                             |

| 76  | A12         | Output              | External Bus Interface address Bit [12]                                                           |

| 77  | A13         | Output              | External Bus Interface address Bit [13]                                                           |

| 78  | A14         | Output              | External Bus Interface address Bit [14]                                                           |

| 79  | A15         | Output              | External Bus Interface address Bit [15]                                                           |

| 80  | VDDC        | Power               | Digital core supply voltage (+2.5VDC)                                                             |

| 81  | A16         | Output              | External Bus Interface address Bit [16]                                                           |

| 82  | A17         | Output              | External Bus Interface address Bit [17]                                                           |

| 83  | A18         | Output              | External Bus Interface address Bit [18]                                                           |

| 84  | A19         | Output              | External Bus Interface address Bit [19]                                                           |

| 85  | VDDIO       | Power               | Digital I/O supply voltage (+3.3VDC)                                                              |

| 86  | A20         | Output              | External Bus Interface address Bit [20]                                                           |

| 87  | A21         | Output              | External Bus Interface address Bit [21]                                                           |

| 88  | A22         | Output              | External Bus Interface address Bit [22]                                                           |

| 89  | A23         | Output              | External Bus Interface address Bit [23]                                                           |

| 90  | GND         | Ground              | Digital ground                                                                                    |

| 91  | A24         | Output              | External Bus Interface address Bit [24]                                                           |

| 92  | A25_RESET_  | Internal            | Muxed pin, External Bus Interface address Bit [25] or POR                                         |

|     | DELAY       | Pull-up             | counter bypass                                                                                    |

| 93  | A26_SIZE    | Internal<br>Pull-up | Muxed pin, External Bus Interface address Bit [26] or data bus size select (0 = 8-Bit, 1= 16=Bit) |

| 94  | A27_CS7_N   | Output              | Muxed pin, External Bus Interface address Bit [27] or Chip select 7 (chip select active low)      |

| 95  | A28_CS6_N   | Output              | Muxed pin, External Bus Interface address Bit [28] or Chip select 6 (chip select active low)      |

| 96  | A29_CS5_N   | Output              | Muxed pin, External Bus Interface address Bit [29] or Chip select 5 (chip select active low)      |

| 97  | A30_CS4_N   | Output              | Muxed pin, External Bus Interface address Bit [30] or Chip select 4 (chip select active low)      |

| 98  | CS0_N       | Output              | Chip select 0 (chip select active low)                                                            |

| 99  | CS1_N       | Output              | Chip select 1 (chip select active low)                                                            |

| 100 | CS2_N       | Output              | Chip select 2 (chip select active low)                                                            |

| 101 | CS3_N       | Output              | Chip select 3 (chip select active low)                                                            |

| 102 | TDI         | Input               | JTAG data input                                                                                   |

| 103 | TDO         | Output              | JTAG data output                                                                                  |

| 104 | TCK         | Input               | JTAG clock input                                                                                  |

| 105 | TMS         | Input               | JTAG control signal                                                                               |

| 106 | VDDC        | Power               | Digital core supply voltage (+2.5VDC)                                                             |

| 107 | UIC0_0      | Bidirectional       | Universal I/O Controller 0, pin 0                                                                 |

| 108 | UIC0_1      | Bidirectional       | Universal I/O Controller 0, pin 1                                                                 |

Table 3. PQFP Pin Listing (Continued)

| Pin | Signal Name | Type          | Description                                       |

|-----|-------------|---------------|---------------------------------------------------|

| 109 | UIC0_2      | Bidirectional | Universal I/O Controller 0, pin 2                 |

| 110 | UIC0_3      | Bidirectional | Universal I/O Controller 0, pin 3                 |

| 111 | GND         | Ground        | Digital ground                                    |

| 112 | UIC0_4      | Bidirectional | Universal I/O Controller 0, pin 4                 |

| 113 | UIC0_5      | Bidirectional | Universal I/O Controller 0, pin 5                 |

| 114 | UIC0_6      | Bidirectional | Universal I/O Controller 0, pin 6                 |

| 115 | UIC0_7      | Bidirectional | Universal I/O Controller 0, pin 7                 |

| 116 | UIC0_8      | Bidirectional | Universal I/O Controller 0, pin 8                 |

| 117 | VDDCLK      | Power supply  | Power Supply for the Crystal Oscillator (+2.5VDC) |

| 118 | XTAL0       | Clock         | Crystal input pin 0 (Osc. In)                     |

| 119 | XTAL1       | Clock         | Crystal input/output pin 1 (Osc. Out)             |

| 120 | GNDCLK      | Ground        | Digital ground                                    |

| 121 | UIC0_9      | Bidirectional | Universal I/O Controller 0, pin 9                 |

| 122 | UIC0_10     | Bidirectional | Universal I/O Controller 0, pin 10                |

| 123 | UIC0_11     | Bidirectional | Universal I/O Controller 0, pin 11                |

| 124 | UIC0_12     | Bidirectional | Universal I/O Controller 0, pin 12                |

| 125 | UIC0_13     | Bidirectional | Universal I/O Controller 0, pin 13                |

| 126 | UIC0_14     | Bidirectional | Universal I/O Controller 0, pin 14                |

| 127 | UIC0_15     | Bidirectional | Universal I/O Controller 0, pin 15                |

| 128 | UIC0_16     | Bidirectional | Universal I/O Controller 0, pin 16                |

| 129 | UIC0_17     | Bidirectional | Universal I/O Controller 0, pin 17                |

| 130 | GND         | Ground        | Digital ground                                    |

| 131 | UIC1_0      | Bidirectional | Universal I/O Controller 1, pin 0                 |

| 132 | UIC1_1      | Bidirectional | Universal I/O Controller 1, pin 1                 |

| 133 | UIC1_2      | Bidirectional | Universal I/O Controller 1, pin 2                 |

| 134 | UIC1_3      | Bidirectional | Universal I/O Controller 1, pin 3                 |

| 135 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)              |

| 136 | UIC1_4      | Bidirectional | Universal I/O Controller 1, pin 4                 |

| 137 | UIC1_5      | Bidirectional | Universal I/O Controller 1, pin 5                 |

| 138 | UIC1_6      | Bidirectional | Universal I/O Controller 1, pin 6                 |

| 139 | UIC1_7      | Bidirectional | Universal I/O Controller 1, pin 7                 |

| 140 | UIC1_8      | Bidirectional | Universal I/O Controller 1, pin 8                 |

| 141 | UIC1_9      | Bidirectional | Universal I/O Controller 1, pin 9                 |

| 142 | VDDC        | Power         | Digital core supply voltage (+2.5VDC)             |

| 143 | UIC1_10     | Bidirectional | Universal I/O Controller 1, pin 10                |

| 144 | UIC1_11     | Bidirectional | Universal I/O Controller 1, pin 11                |

| 145 | UIC1_12     | Bidirectional | Universal I/O Controller 1, pin 12                |

| 146 | UIC1_13     | Bidirectional | Universal I/O Controller 1, pin 13                |

| 147 | UIC1_14     | Bidirectional | Universal I/O Controller 1, pin 14                |

Table 3. PQFP Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                           |

|-----|-------------|---------------|---------------------------------------|

| 148 | GND         | Ground        | Digital ground                        |

| 149 | UIC1_15     | Bidirectional | Universal I/O Controller 1, pin 15    |

| 150 | UIC1_16     | Bidirectional | Universal I/O Controller 1, pin 16    |

| 151 | UIC1_17     | Bidirectional | Universal I/O Controller 1, pin 17    |

| 152 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)  |

| 153 | UIC2_0      | Bidirectional | Universal I/O Controller 2, pin 0     |

| 154 | UIC2_1      | Bidirectional | Universal I/O Controller 2, pin 1     |

| 155 | UIC2_2      | Bidirectional | Universal I/O Controller 2, pin 2     |

| 156 | UIC2_3      | Bidirectional | Universal I/O Controller 2, pin 3     |

| 157 | VDDC        | Power         | Digital core supply voltage (+2.5VDC) |

| 158 | UIC2_4      | Bidirectional | Universal I/O Controller 2, pin 4     |

| 159 | UIC2_5      | Bidirectional | Universal I/O Controller 2, pin 5     |

| 160 | UIC2_6      | Bidirectional | Universal I/O Controller 2, pin 6     |

| 161 | UIC2_7      | Bidirectional | Universal I/O Controller 2, pin 7     |

| 162 | GND         | Ground        | Digital ground                        |

| 163 | UIC2_8      | Bidirectional | Universal I/O Controller 2, pin 8     |

| 164 | UIC2_9      | Bidirectional | Universal I/O Controller 2, pin 9     |

| 165 | UIC2_10     | Bidirectional | Universal I/O Controller 2, pin 10    |

| 166 | UIC2_11     | Bidirectional | Universal I/O Controller 2, pin 11    |

| 167 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)  |

| 168 | UIC2_12     | Bidirectional | Universal I/O Controller 2, pin 12    |

| 169 | UIC2_13     | Bidirectional | Universal I/O Controller 2, pin 13    |

| 170 | UIC2_14     | Bidirectional | Universal I/O Controller 2, pin 14    |

| 171 | UIC2_15     | Bidirectional | Universal I/O Controller 2, pin 15    |

| 172 | GND         | Ground        | Digital ground                        |

| 173 | UIC2_16     | Bidirectional | Universal I/O Controller 2, pin 16    |

| 174 | UIC2_17     | Bidirectional | Universal I/O Controller 2, pin 17    |

| 175 | UIC3_0      | Bidirectional | Universal I/O Controller 3 pin 0      |

| 176 | UIC3_1      | Bidirectional | Universal I/O Controller 3 pin 1      |

| 177 | VDDC        | Power         | Digital core supply voltage (+2.5VDC) |

| 178 | UIC3_2      | Bidirectional | Universal I/O Controller 3 pin 2      |

| 179 | UIC3_3      | Bidirectional | Universal I/O Controller 3 pin 3      |

| 180 | UIC3_4      | Bidirectional | Universal I/O Controller 3 pin 4      |

| 181 | UIC3_5      | Bidirectional | Universal I/O Controller 3 pin 5      |

| 182 | GND         | Ground        | Digital ground                        |

| 183 | UIC3_6      | Bidirectional | Universal I/O Controller 3 pin 6      |

| 184 | UIC3_7      | Bidirectional | Universal I/O Controller 3 pin 7      |

| 185 | UIC3_8      | Bidirectional | Universal I/O Controller 3 pin 8      |

| 186 | UIC3_9      | Bidirectional | Universal I/O Controller 3 pin 9      |

Table 3. PQFP Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                                                         |

|-----|-------------|---------------|---------------------------------------------------------------------|

| 187 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)                                |

| 188 | UIC3_10     | Bidirectional | Universal I/O Controller 3 pin 10                                   |

| 189 | UIC3_11     | Bidirectional | Universal I/O Controller 3 pin 11                                   |

| 190 | UIC3_12     | Bidirectional | Universal I/O Controller 3 pin 12                                   |

| 191 | UIC3_13     | Bidirectional | Universal I/O Controller 3 pin 13                                   |

| 192 | GND         | Ground        | Digital Ground                                                      |

| 193 | UIC3_14     | Bidirectional | Universal I/O Controller 3 pin 14                                   |

| 194 | UIC3_15     | Bidirectional | Universal I/O Controller 3 pin 15                                   |

| 195 | UIC3_16     | Bidirectional | Universal I/O Controller 3 pin 16                                   |

| 196 | UIC3_17     | Bidirectional | Universal I/O Controller 3 pin 17                                   |

| 197 | T0IC0_T0OC0 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 0 or output compare 0 |

| 198 | T0lC1_T0OC1 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 1 or output compare 1 |

| 199 | T0lC2_T0OC2 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 2 or output compare 2 |

| 200 | T0lC3_T0OC3 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 3 or output compare 3 |

| 201 | GND         | Ground        | Digital ground                                                      |

| 202 | T1IC0_T1OC0 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 0 or output compare 0 |

| 203 | T1IC1_T1OC1 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 1 or output compare 1 |

| 204 | T1IC2_T1OC2 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 2 or output compare 2 |

| 205 | T1IC3_T1OC3 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 3 or output compare 3 |

| 206 | VDDC        | Power         | Digital core supply voltage (+2.5VDC)                               |

| 207 | TOIN        | Input         | Timer Counter Unit 0 external clock source                          |

| 208 | T1IN        | Input         | Timer Counter Unit 1 external clock source                          |

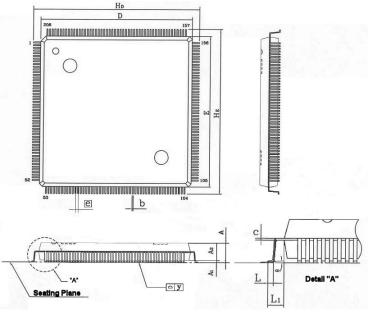

### 4.1.2 PQFP Physical Dimensions

The physical dimensions for the 208-pin PQFP package are as shown in Figure 3.

Legend:

|                | Dim   | ension ii | n mm  | Dimension in Inches |         |       |

|----------------|-------|-----------|-------|---------------------|---------|-------|

| Symbol         | Min   | Nom       | Max   | Min                 | Nom     | Max   |

| Α              | -     | ı         | 4.07  | -                   | I       | 0.160 |

| A1             | 0.25  | ı         | ı     | 0.010               | I       | _     |

| A2             | 3.15  | 3.23      | 3.30  | 0.124               | 0.127   | 0.130 |

| b              | 0.18  | _         | 0.28  | 0.007               | _       | 0.011 |

| С              | 0.13  | _         | 0.23  | 0.005               | _       | 0.009 |

| D              | 27.90 | 28.00     | 28.10 | 1.098               | 1.102   | 1.106 |

| Е              | 27.90 | 28.00     | 28.10 | 1.098               | 1.102   | 1.106 |

| е              |       | 0.50 BS   | SC    |                     | 0.020 B | SC    |

| H <sub>D</sub> | 30.35 | 30.60     | 30.85 | 1.195               | 1.205   | 1.215 |

| H <sub>E</sub> | 30.35 | 30.60     | 30.85 | 1.195               | 1.205   | 1.215 |

| L              | 0.35  | 0.50      | 0.65  | 0.014               | 0.020   | 0.026 |

| L1             |       | 1.30 RE   | F     | ·                   | 0.051 R | EF    |

| у              | _     |           | 0.19  | _                   |         | 0.004 |

| Θ              | 0°    |           | 7°    | 0°                  |         | 7°    |

#### Notes:

- 1. Dimension D & E do not include interlead flash.

- 2. Dimension B does not include damper protrusion/intrusion.

- 3. Controlling dimension: mm

- 4. General appearance spec. should be based on visual inspection spec.

Figure 3. PQFP Physical Package Dimensions

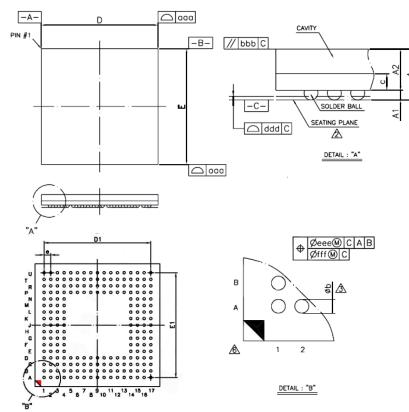

# 4.2 BGA 15- by 15-mm Package

## 4.2.1 BGA 15- by 15-mm Pinout

The pinout for the fido1100™ communication controller BGA 15- by 15-mm package is as shown in Figure 4. The corresponding pinout is provided in Table 4.

|   | 1                     | 2                     | 3                     | 4               | 5               | 6       | 7       | 8       | 9      | 10     | 11      | 12        | 13                  | 14        | 15      | 16      | 17      | _ |

|---|-----------------------|-----------------------|-----------------------|-----------------|-----------------|---------|---------|---------|--------|--------|---------|-----------|---------------------|-----------|---------|---------|---------|---|

| Α | T1IC1_<br>T1OC1       | T0IC2_<br>T0OC2       | T0IC0_<br>T0OC0       | UIC3_15         | UIC3_13         | UIC3_12 | UIC3_9  | UIC3_7  | UIC3_4 | UIC3_1 | UIC3_0  | UIC2_15   | UIC2_13             | UIC2_10   | UIC2_7  | UIC2_6  | UIC1_17 | А |

| В | AN_2                  |                       | T1IC0_<br>T1OC0       | T0IC1_<br>T0OC1 | UIC3_16         | GND     | UIC3_11 | UIC3_8  | UIC3_5 | UIC3_2 | UIC2_17 | UIC2_14   | UIC2_11             | UIC2_8    | UIC2_5  | UIC2_0  | UIC1_14 | В |

| С | AN_0                  | AN_5                  | TOIN                  | T1IC3_<br>T1OC3 | T0IC3_<br>T0OC3 | UIC3_17 | UIC3_14 | UIC3_10 | UIC3_6 | UIC3_3 | UIC2_16 | UIC2_12   | UIC2_9              | UIC2_4    | UIC2_1  | UIC1_16 | UIC1_12 | С |

| D | VDDA                  | AN_1                  | AN_6                  | GND             | GND             | T1IN    | VDDC    | VDDC    | VDDC   | VDDIO  | VDDIO   | VDDIO     | GND                 | GND       | UIC2_2  | UIC1_13 | UIC1_9  | D |

| E | GNDA                  | VRH                   | AN_3                  | GND             |                 |         |         |         |        |        |         |           |                     | GND       | UIC1_15 | UIC1_10 | UIC1_6  | E |

| F | INT2                  | INT0                  | VRL                   | AN_7            |                 |         |         |         |        |        |         |           |                     | UIC2_3    | UIC1_11 | UIC1_8  | UIC1_5  | F |

| G | INT4_<br>DMA0_<br>ACK | INT3                  | INT1                  | AN_4            |                 |         |         |         |        |        |         |           |                     | VDDIO     | UIC1_7  | UIC1_4  | UIC1_2  | G |

| Н | INT7_<br>DMA1_<br>REQ | INT6_<br>DMA0_<br>REQ | INT5_<br>DMA1_<br>ACK | VDDC            |                 |         |         |         |        |        |         |           |                     | VDDIO     | UIC1_3  | UIC1_1  | UIC1_0  | Н |

| J | D0                    | D1                    | D2                    | VDDIO           |                 |         |         |         |        |        |         |           |                     | VDDIO     | UIC0_17 | UIC0_16 | UIC0_15 | J |

| K | D3                    | D4                    | D6                    | VDDIO           |                 |         |         |         |        |        |         |           |                     | VDDC      | UIC0_14 | UIC0_13 | UIC0_12 | K |

| L | D5                    | D7                    | D11                   | OE_N            |                 |         |         |         |        |        |         |           |                     | VDDC      | UIC0_10 | UIC0_9  | UIC0_11 | L |

| М | D8                    | D10                   | D15                   | CAS_N           |                 |         |         |         |        |        |         |           |                     | GNDCLK    | VDDCLK  | UIC0_8  | XTAL1   | М |

| N | D9                    | D13                   | BE1_N                 | GND             |                 |         |         |         |        |        |         |           |                     | GND       | UIC0_5  | UIC0_7  | XTAL0   | N |

| Р | D12                   | RDY_N                 | BA_1                  | GND             | GND             | GND     | RESET_N | VDDIO   | VDDC   | VDDC   | A21     | A26_SIZE  | GND                 | GND       | UIC0_0  | UIC0_4  | UIC0_6  | Р |

| R | D14                   | BE0_N                 | BA_0                  | RAS_N           | HOLDGNT_N       | А3      | A6      | A10     | A15    | A18    | A22     | A27_CS7_N | A29_CS5_N           | CS3_N     | CS2_N   | UIC0_2  | UIC0_3  | R |

| Т | GND                   | RW_N                  | CKE                   | RESET_<br>OUT_N | A2              | A5      | A8      | A11     | A14    | A17    | A20     | A24       | A28_CS6_N           | CS0_N     | CS1_N   | TCK     | UIC0_1  | Т |

| U | MEMCLK                | HOLDREQ_N             | A0                    | A1              | A4              | A7      | A9      | A12     | A13    | A16    | A19     | A23       | A25_RESET_<br>DELAY | A30_CS4_N | TDI     | TDO     | TMS     | U |

|   | 1                     | 2                     | 3                     | 4               | 5               | 6       | 7       | 8       | 9      | 10     | 11      | 12        | 13                  | 14        | 15      | 16      | 17      | - |

Figure 4. BGA 15- by 15-mm Package Diagram

Table 4. BGA 15- by 15-mm Package Pin Listing

| Pin | Signal Name       | Type          | Description                                         |

|-----|-------------------|---------------|-----------------------------------------------------|

| F4  | AN 7              | Input         | Analog-to-digital converter input channel 7         |

| D3  | AN 6              | Input         | Analog-to-digital converter input channel 6         |

| C2  | AN_5              | Input         | Analog-to-digital converter input channel 5         |

| G4  | AN_4              | Input         | Analog-to-digital converter input channel 4         |

| E3  | AN_3              | Input         | Analog-to-digital converter input channel 3         |

| B1  | AN_2              | Input         | Analog-to-digital converter input channel 2         |

| D2  | AN_1              | Input         | Analog-to-digital converter input channel 1         |

| C1  | AN_0              | Input         | Analog-to-digital converter input channel 0         |

| F3  | VRL               | Input         | Analog-to-digital converter low-input reference     |

| E2  | VRH               | Input         | Analog-to-digital converter high-input reference    |

| D1  | VDDA              | Power         | Analog supply voltage (+3.3VDC)                     |

| E1  | GNDA              | Ground        | Analog ground                                       |

| F2  | INT0              | Input         | Interrupt_0                                         |

| G3  | INT1              | Input         | Interrupt_1                                         |

| F1  | INT2              | Input         | Interrupt_2                                         |

| D7  | VDDC              | Power         | Digital core supply voltage (+2.5VDC)               |

| G2  | INT3              | Input         | Interrupt_3                                         |

| G1  | INT4_DMA0_<br>ACK | Bidirectional | Muxed pin, Interrupt_4 or DMA channel 0 acknowledge |

| H3  | INT5_DMA1_<br>ACK | Bidirectional | Muxed pin, Interrupt_5 or DMA channel 1 acknowledge |

| H2  | INT6_DMA0_<br>REQ | Input         | Muxed pin, Interrupt_6 or DMA channel 0 request     |

| H1  | INT7_DMA1_<br>REQ | Input         | Muxed pin, Interrupt_7 or DMA channel 1 request     |

| D10 | VDDIO             | Power         | Digital I/O supply voltage (+3.3VDC)                |

| J1  | D0                | Bidirectional | External Bus Interface data Bit [0]                 |

| J2  | D1                | Bidirectional | External Bus Interface data Bit [1]                 |

| J3  | D2                | Bidirectional | External Bus Interface data Bit [2]                 |

| K1  | D3                | Bidirectional | External Bus Interface data Bit [3]                 |

| K2  | D4                | Bidirectional | External Bus Interface data Bit [4]                 |

| L1  | D5                | Bidirectional | External Bus Interface data Bit [5]                 |

| K3  | D6                | Bidirectional | External Bus Interface data Bit [6]                 |

| L2  | D7                | Bidirectional | External Bus Interface data Bit [7]                 |

| D4  | GND               | Ground        | Digital ground                                      |

| M1  | D8                | Bidirectional | External Bus Interface data Bit [8]                 |

| N1  | D9                | Bidirectional | External Bus Interface data Bit [9]                 |

| M2  | D10               | Bidirectional | External Bus Interface data Bit [10]                |

| L3  | D11               | Bidirectional | External Bus Interface data Bit [11]                |

Table 4. BGA 15- by 15-mm Package Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                                        |

|-----|-------------|---------------|----------------------------------------------------|

| P1  | D12         | Bidirectional | External Bus Interface data Bit [12]               |

| D11 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)               |

| N2  | D13         | Bidirectional | External Bus Interface data Bit [13]               |

| R1  | D14         | Bidirectional | External Bus Interface data Bit [14]               |

| M3  | D15         | Bidirectional | External Bus Interface data Bit [15]               |

| P2  | RDY_N       | Input         | External Bus Interface External Ready Indication   |

| T1  | GND         | Ground        | Digital ground                                     |

| U1  | MEMCLK      | Output        | Memory clock used by external memory               |

| D5  | GND         | Ground        | Digital ground                                     |

| R2  | BE0_N       | Output        | Byte enable 0, active low                          |

| N3  | BE1_N       | Output        | Byte enable 1, active low                          |

| L4  | OE_N        | Output        | Output enable, active low                          |

| D8  | VDDC        | Power         | Digital core supply voltage (+2.5VDC)              |

| T2  | RW_N        | Output        | Read or write control (active low write)           |

| R3  | BA_0        | Output        | Bank Enable 0                                      |

| P3  | BA_1        | Output        | Bank Enable 1                                      |

| M4  | CAS_N       | Output        | Column activate signal, active low                 |

| P6  | GND         | Ground        | Digital Ground                                     |

| R4  | RAS_N       | Output        | Row activate signal, active low                    |

| Т3  | CKE         | Output        | Clock enable to be used in conjunction with MEMCLK |

| U2  | HOLDREQ_N   | Input         | External Bus hold request, active low              |

| R5  | HOLDGNT_N   | Output        | External Bus grant request, active low             |

| P7  | RESET_N     | Input         | Reset input                                        |

| T4  | RESET_OUT_N | Output        | Reset output                                       |

| D13 | GND         | Ground        | Digital ground                                     |

| U3  | A0          | Output        | External Bus Interface address Bit [0]             |

| U4  | A1          | Output        | External Bus Interface address Bit [1]             |

| T5  | A2          | Output        | External Bus Interface address Bit [2]             |

| R6  | A3          | Output        | External Bus Interface address Bit [3]             |

| D12 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)               |

| U5  | A4          | Output        | External Bus Interface address Bit [4]             |

| T6  | A5          | Output        | External Bus Interface address Bit [5]             |

| R7  | A6          | Output        | External Bus Interface address Bit [6]             |

| U6  | A7          | Output        | External Bus Interface address Bit [7]             |

| D14 | GND         | Ground        | Digital ground                                     |

| T7  | A8          | Output        | External Bus Interface address Bit [8]             |

| U7  | A9          | Output        | External Bus Interface address Bit [9]             |

| R8  | A10         | Output        | External Bus Interface address Bit [10]            |

Table 4. BGA 15- by 15-mm Package Pin Listing (Continued)

| Pin  | Signal Name | Туре     | Description                                                                                   |

|------|-------------|----------|-----------------------------------------------------------------------------------------------|

| T8   | A11         | Output   | External Bus Interface address Bit [11]                                                       |

| D9   | VDDC        | Power    | Digital core supply voltage (+2.5VDC)                                                         |

| U8   | A12         | Output   | External Bus Interface address Bit [12]                                                       |

| U9   | A13         | Output   | External Bus Interface address Bit [13]                                                       |

| T9   | A14         | Output   | External Bus Interface address Bit [14]                                                       |

| R9   | A15         | Output   | External Bus Interface address Bit [15]                                                       |

| H4   | VDDC        | Power    | Digital core supply voltage (+2.5VDC)                                                         |

| U10  | A16         | Output   | External Bus Interface address Bit [16]                                                       |

| T10  | A17         | Output   | External Bus Interface address Bit [17]                                                       |

| R10  | A18         | Output   | External Bus Interface address Bit [18]                                                       |

| U11  | A19         | Output   | External Bus Interface address Bit [19]                                                       |

| G14  | VDDIO       | Power    | Digital I/O supply voltage (+3.3VDC)                                                          |

| T11  | A20         | Output   | External Bus Interface address Bit [20]                                                       |

| P11  | A21         | Output   | External Bus Interface address Bit [21]                                                       |

| R11  | A22         | Output   | External Bus Interface address Bit [22]                                                       |

| U12  | A23         | Output   | External Bus Interface address Bit [23]                                                       |

| E4   | GND         | Ground   | Digital ground                                                                                |

| T12  | A24         | Output   | External Bus Interface address Bit [24]                                                       |

| U13  | A_25_RESET_ | Internal | Muxed pin, External Bus Interface address Bit [25] or POR                                     |

|      | DELAY       | Pull-up  | counter bypass                                                                                |

| P12  | A_26_SIZE   | Internal | Muxed pin, External Bus Interface address Bit [26] or data bus                                |

| D.10 | 407 007 N   | Pull-up  | size select (0 = 8-Bit, 1= 16=Bit)                                                            |

| R12  | A27_CS7_N   | Output   | Muxed pin, External Bus Interface address Bit [27] or Chip                                    |

| T13  | A28_CS6_N   | Output   | select 7 (chip select active low)  Muxed pin, External Bus Interface address Bit [28] or Chip |

| 113  | A20_C30_N   | Output   | select 6 (chip select active low)                                                             |

| R13  | A29_CS5_N   | Output   | Muxed pin, External Bus Interface address Bit [29] or Chip                                    |

|      | /           | o anp ar | select 5 (chip select active low)                                                             |

| U14  | A30_CS4_N   | Output   | Muxed pin, External Bus Interface address Bit [30] or Chip                                    |

|      |             | -        | select 4 (chip select active low)                                                             |

| T14  | CS0_N       | Output   | Chip select 0 (chip select active low)                                                        |

| T15  | CS1_N       | Output   | Chip select 1 (chip select active low)                                                        |

| R15  | CS2_N       | Output   | Chip select 2 (chip select active low)                                                        |

| R14  | CS3_N       | Output   | Chip select 3 (chip select active low)                                                        |

| U15  | TDI         | Input    | JTAG data input                                                                               |

| U16  | TDO         | Output   | JTAG data output                                                                              |

| T16  | TCK         | Input    | JTAG clock input                                                                              |

| U17  | TMS         | Input    | JTAG control signal                                                                           |

| K14  | VDDC        | Power    | Digital core supply voltage (+2.5VDC)                                                         |

Table 4. BGA 15- by 15-mm Package Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                                       |

|-----|-------------|---------------|---------------------------------------------------|

| P15 | UIC0_0      | Bidirectional | Universal I/O Controller 0, pin 0                 |

| T17 | UIC0_1      | Bidirectional | Universal I/O Controller 0, pin 1                 |

| R16 | UIC0_2      | Bidirectional | Universal I/O Controller 0, pin 2                 |

| R17 | UIC0_3      | Bidirectional | Universal I/O Controller 0, pin 3                 |

| E14 | GND         | Ground        | Digital ground                                    |

| P16 | UIC0_4      | Bidirectional | Universal I/O Controller 0, pin 4                 |

| N15 | UIC0_5      | Bidirectional | Universal I/O Controller 0, pin 5                 |

| P17 | UIC0_6      | Bidirectional | Universal I/O Controller 0, pin 6                 |

| N16 | UIC0_7      | Bidirectional | Universal I/O Controller 0, pin 7                 |

| M16 | UIC0_8      | Bidirectional | Universal I/O Controller 0, pin 8                 |

| M15 | VDDCLK      | Power supply  | Power Supply for the Crystal Oscillator (+2.5VDC) |

| N17 | XTAL0       | Clock         | Crystal input pin 0 (Osc. In)                     |

| M17 | XTAL1       | Clock         | Crystal input/output pin 1 (Osc. Out)             |

| M14 | GNDCLK      | Ground        | Digital ground                                    |

| L16 | UIC0_9      | Bidirectional | Universal I/O Controller 0, pin 9                 |

| L15 | UIC0_10     | Bidirectional | Universal I/O Controller 0, pin 10                |

| L17 | UIC0_11     | Bidirectional | Universal I/O Controller 0, pin 11                |

| K17 | UIC0_12     | Bidirectional | Universal I/O Controller 0, pin 12                |

| K16 | UIC0_13     | Bidirectional | Universal I/O Controller 0, pin 13                |

| K15 | UIC0_14     | Bidirectional | Universal I/O Controller 0, pin 14                |

| J17 | UIC0_15     | Bidirectional | Universal I/O Controller 0, pin 15                |

| J16 | UIC0_16     | Bidirectional | Universal I/O Controller 0, pin 16                |

| J15 | UIC0_17     | Bidirectional | Universal I/O Controller 0, pin 17                |

| N4  | GND         | Ground        | Digital ground                                    |

| H17 | UIC1_0      | Bidirectional | Universal I/O Controller 1, pin 0                 |

| H16 | UIC1_1      | Bidirectional | Universal I/O Controller 1, pin 1                 |

| G17 | UIC1_2      | Bidirectional | Universal I/O Controller 1, pin 2                 |

| H15 | UIC1_3      | Bidirectional | Universal I/O Controller 1, pin 3                 |

| J4  | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)              |

| G16 | UIC1_4      | Bidirectional | Universal I/O Controller 1, pin 4                 |

| F17 | UIC1_5      | Bidirectional | Universal I/O Controller 1, pin 5                 |

| E17 | UIC1_6      | Bidirectional | Universal I/O Controller 1, pin 6                 |

| G15 | UIC1_7      | Bidirectional | Universal I/O Controller 1, pin 7                 |

| F16 | UIC1_8      | Bidirectional | Universal I/O Controller 1, pin 8                 |

| D17 | UIC1_9      | Bidirectional | Universal I/O Controller 1, pin 9                 |

| L14 | VDDC        | Power         | Digital core supply voltage (+2.5VDC)             |

| E16 | UIC1_10     | Bidirectional | Universal I/O Controller 1, pin 10                |

| F15 | UIC1_11     | Bidirectional | Universal I/O Controller 1, pin 11                |

Table 4. BGA 15- by 15-mm Package Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                           |

|-----|-------------|---------------|---------------------------------------|

| C17 | UIC1_12     | Bidirectional | Universal I/O Controller 1, pin 12    |

| D16 | UIC1_13     | Bidirectional | Universal I/O Controller 1, pin 13    |

| B17 | UIC1_14     | Bidirectional | Universal I/O Controller 1, pin 14    |

| N14 | GND         | Ground        | Digital ground                        |

| E15 | UIC1_15     | Bidirectional | Universal I/O Controller 1, pin 15    |

| C16 | UIC1_16     | Bidirectional | Universal I/O Controller 1, pin 16    |

| A17 | UIC1_17     | Bidirectional | Universal I/O Controller 1, pin 17    |

| J14 | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)  |

| B16 | UIC2_0      | Bidirectional | Universal I/O Controller 2, pin 0     |

| C15 | UIC2_1      | Bidirectional | Universal I/O Controller 2, pin 1     |

| D15 | UIC2_2      | Bidirectional | Universal I/O Controller 2, pin 2     |

| F14 | UIC2_3      | Bidirectional | Universal I/O Controller 2, pin 3     |

| P9  | VDDC        | Power         | Digital core supply voltage (+2.5VDC) |

| C14 | UIC2_4      | Bidirectional | Universal I/O Controller 2, pin 4     |

| B15 | UIC2_5      | Bidirectional | Universal I/O Controller 2, pin 5     |

| A16 | UIC2_6      | Bidirectional | Universal I/O Controller 2, pin 6     |

| A15 | UIC2_7      | Bidirectional | Universal I/O Controller 2, pin 7     |

| P4  | GND         | Ground        | Digital ground                        |

| B14 | UIC2_8      | Bidirectional | Universal I/O Controller 2, pin 8     |

| C13 | UIC2_9      | Bidirectional | Universal I/O Controller 2, pin 9     |

| A14 | UIC2_10     | Bidirectional | Universal I/O Controller 2, pin 10    |

| B13 | UIC2_11     | Bidirectional | Universal I/O Controller 2, pin 11    |

| K4  | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)  |

| C12 | UIC2_12     | Bidirectional | Universal I/O Controller 2, pin 12    |

| A13 | UIC2_13     | Bidirectional | Universal I/O Controller 2, pin 13    |

| B12 | UIC2_14     | Bidirectional | Universal I/O Controller 2, pin 14    |

| A12 | UIC2_15     | Bidirectional | Universal I/O Controller 2, pin 15    |

| P5  | GND         | Ground        | Digital ground                        |

| C11 | UIC2_16     | Bidirectional | Universal I/O Controller 2, pin 16    |

| B11 | UIC2_17     | Bidirectional | Universal I/O Controller 2, pin 17    |

| A11 | UIC3_0      | Bidirectional | Universal I/O Controller 3 pin 0      |

| A10 | UIC3_1      | Bidirectional | Universal I/O Controller 3 pin 1      |

| P10 | VDDC        | Power         | Digital core supply voltage (+2.5VDC) |

| B10 | UIC3_2      | Bidirectional | Universal I/O Controller 3 pin 2      |

| C10 | UIC3_3      | Bidirectional | Universal I/O Controller 3 pin 3      |

| A9  | UIC3_4      | Bidirectional | Universal I/O Controller 3 pin 4      |

| B9  | UIC3_5      | Bidirectional | Universal I/O Controller 3 pin 5      |

Table 4. BGA 15- by 15-mm Package Pin Listing (Continued)

| Pin | Signal Name | Туре          | Description                                                         |

|-----|-------------|---------------|---------------------------------------------------------------------|

| C9  | UIC3_6      | Bidirectional | Universal I/O Controller 3 pin 6                                    |

| A8  | UIC3_7      | Bidirectional | Universal I/O Controller 3 pin 7                                    |

| B8  | UIC3_8      | Bidirectional | Universal I/O Controller 3 pin 8                                    |