# Image Compression Coprocessor (ICC)

The KS0143 (ICC: Image Compression Coprocessor) integrated circuit is a very high performance programmable processor optimized for the execution of DCT-based image compression algorithms such as MPEG-1, JPEG, and H.261. In combination with commonly available RISC or DSP processors, the KS0143 and its companion chip, the KS0144 (MEC: Motion Estimation Coprocessor), form a complete, highly programmable computing solution for compressing and decompressing both still and motion video images.

#### RELATED PRODUCTS

- · KS0144 Motion Estimation Coprocessor (MEC)

- VFEB® Hardware Evaluation Kit

- Aspen / Keystone Reference Board

- · ICCST® Software Tool Kit

#### **APPLICATIONS**

- Video Conferencing and Telephony

- Video Editing

- Video CD-ROM Mastering

- · Image Storage and Retrieval

- · Multimedia-based Systems

#### **FEATURES**

- Compliant with MPEG-1 (ISO/ IEC International Standard 11172-2), JPEG (ISO/ IEC International Standard 10918-1), and ITU-T Recommendation H 261

- Graph-based dataflow programming using high-level instructions downloadable to on-chip RAM.

- Multiple internal processing units optimized for very high performance execution of widely used image compression operations.

- Memory-mapped host processor interface including 16-bit data bus, 11-bit address bus, and support for high performance burst transfers.

- High speed 32-bit video data bus for accessing multiple video frame memories required during the execution of compression algorithms.

- Auxiliary interface bus permitting the connection of user-definable external processing chips to the KS0143.

- · 50 MHz clock, 6W maximum power dissipation.

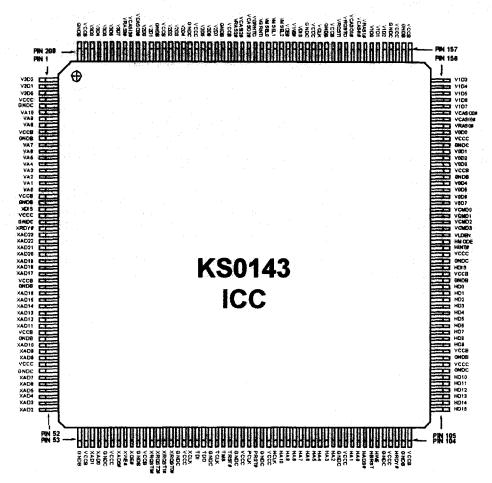

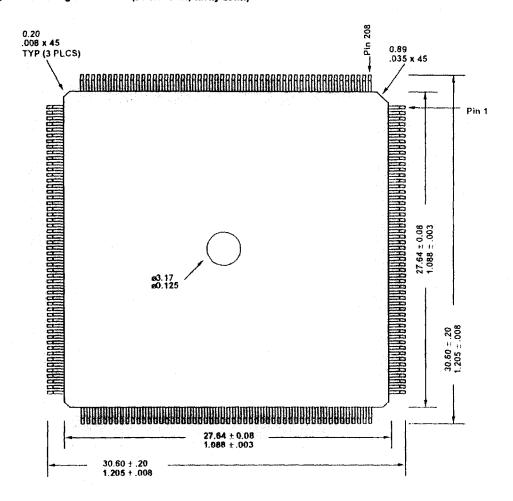

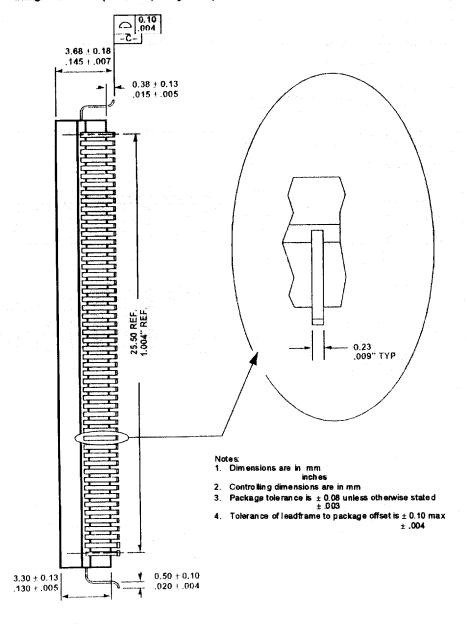

- 208-pin Metal Quad Flat Pack (MQUAD™), cavity down package.

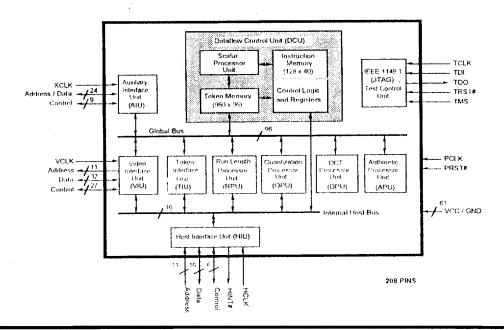

#### **FUNCTIONAL BLOCK DIAGRAM**

# INTRODUCTION TO THE KS0143 / KS0144 CHIP SET

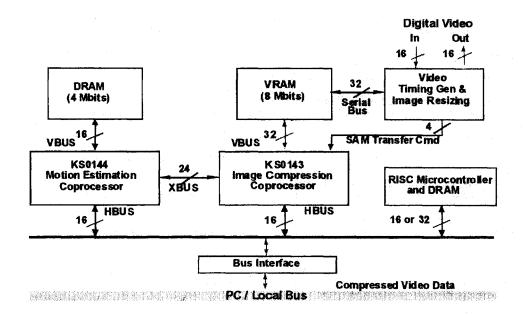

The KS0143 Image Compression Coprocessor (ICC), together with its companion chip, the KS0144 Motion Estimation Coprocessor (MEC), form the heart of a programmable video codec for implementing the JPEG, MPEG-1, and H.261 conpression standards. The codec architecture shown in Figure 1.1 may be easily programmed to implement any of the following applications at 30 frames per second:

- · H.261 codec processing CIF (352h x 288v) images

- MPEG-1 SIF (352h x 240v) encoder with up to two B frames per Prame and half-pel motion estimation

- · MPEG-1 SIF decoder

- JPEG CCIR-601 encoder or decoder

The KS0143 implements all portions of these standards other than motion estimation, variable length coding (VLC), and bit stream syntax handling. The KS0144 executes user-defined motion estimation search algorithms and is only required in systems implementing MPEG-1 or H.261 motion-predictive encoders.

VLC and bit stream syntax handling are typically performed using an off-the-shelf RISC microcontroller which also controls both the KS0143 and KS0144 via their host processor interfaces. The KS0143 / KS0144 chip set does not perform color space conversion or image resizing

#### **VIDEOFLOW ® Architecture**

The KS0143 / KS0144 chip set is based on a very high performance parallel processing architecture. Its parallel processing KS0144hanism has been implemented using a unique vector dataflow architecture which delivers exceptionally high performance and decouples the user from the complexities of a parallel processor. This vector dataflow (VIDEOFLOW) architecture combines dataflow control with vector instruction execution, allowing a user to control a very complex parallel processor via simple program flowgraphs. In addition, the VIDEOFLOW architecture is highly scalable and modular, allowing Array Microsystems to readily produce architecturally compatible derivative products.

Figure 1.1 - Typical Application

Programmable video codec for JPEG, MPEG-1, and H.261-based multimedia applications

Copyright 1995 Samsung Electronics co., LTD. All rights reserved.

Samsung Electronics Co., LTD.

Sa #14, Nongseo-Ri, Kihung-Eup, Youngin-Kun,

Kyungki-D, Korea 449-900

Suwon P.O. Box #105

Tel: +82 (331) 280-9454, 280-9484

FAX: =84 (331) 280-9459

Email: sspds @ jupiter. info. samsung. co.kr

#### **Product Ordering Information:**

| Revision Number | Release Date |

|-----------------|--------------|

| SMP9601DS V1.0  | 7/93         |

| SMP9601DS V1.1  | 7/93         |

| SMP9601DS V1.2  | 1/95         |

| KS0143DS V1.3   | 4/96         |

**REVISION HISTORY**

| Part Number | Speed  | Processing | Temperature<br>Range ( case ) | Voltage Range | Pin Count | Package Type        |

|-------------|--------|------------|-------------------------------|---------------|-----------|---------------------|

| KS0143-50   | 50 MHz | Commercial | 0 × to 100 × C                | 4.75 to 5.25V | 208       | MQUAD <sup>1M</sup> |

| KS0143-40   | 40 MHz | Commercial | 0 × to 100 × C                | 4.75 to 5.25V | 208       | MQUAD <sup>TM</sup> |

# Trademark acknowledgments:

KS0143/KS0144 is a trademark of Samsung Electronics Co.,LTD VIDEO FLOW is a trademark of Array Microsystems Inc. Intel and 1960 are trademarks of intel Corporation 29KTM is trademark of Advanced Micro Devices, Inc.

# **WARNING - LIFE SUPPORT APPLICATIONS POLCY**

Samsung Electronics products should notbge used within Life Support Systems without specific written consent of Samsung

Electronics Co., LTD. A Life Support System is a product or system intended to support or sustain life which, if it fails,

be reasonably expected to result in significant personal injury or death.

#### NOTICE - DOCUMENTATION SUPPORT POLICY

The information in this publication is subject to change without notice. Samsung assumes no responsibility for any errors

or omissions, and disclaims responsibility for any consequences rsulting from the use of the information included herein.

Additionally, Samsung assumes no responsibility for the functioning of undescribed features or parameters.

#### NOTICE - APPLICATIONS SUPPORT POLOCY

Samsung Electronics Co., LTD. assumes no liability for applications assistance or customer product design.

#### **NOTICE - PRODUCT AVAILABILITY**

Samsung Electronics Co., LTD. reserves the right to make changes to product specifications or to discontinue products without notice.

#### **NOTICE - STATED OR IMPLIED WARRANTY**

This publication neither states nor implies any warranty of any kind, including byt not limited toimplied warranties of merchantability or fitness for a particular application.

## **NOTICE - COPY PERMISSION**

Permission is hereby expressly granted to copy this publication for informatinal purposes only. Copying this material for any other use is strictly prohibited.

#### KS0143 / KS0144 Chip Set Performance

The parallel processing architectures embodied in the KS0143 / KS0144 chip set permit it to deliver exceptional performance for the JPEG, MPEG-1, and H.261 standards. Table 1.1 shows representative real-time (i.e. 30 frames per second) applications of the standards using the 40 and 50 MHz versions of the chip set. The KS0144 is not required for H.261 decoder, MPEG-1 decoder. or JPEG applications.

A unique feature of the chip set, owing to the programming style and very high performance of the KS0143, is its ability to simultaneously process multiple image channels. For example, for multipoint video conferencing, a single KS0143/KS0144 chip set may be used to implement an H.261 video codec capable of simultaneously encoding a single image sequence (e.g. the one being transmitted) and decoding multiple received bit streams. Also, for MPEG-1 multimedia applications running in a windowed environment, a single KS0143 can decode two different SIF image bit streams in real time.

As shown in Table 1.1, another unique feature of the chip set is its ability to decode MPEG-1 images as they are encoded. This Oreal-time previewO feature is the result of the high performance and programmability of the chip set. Real-time previewing allows the user of MPEG-1 multimedia applications to create bit streams and visually monitor encoding results without the need for additional hardware for MPEG-1 decoding.

Furthermore, the ability of the KS0143 chip to real-time JPEG encode or decode the large image sizes shown in Table 1.1 is extremely useful in video editing applications. These applications typically operate with very high resolution images and compress them prior to storing them on disk.

#### High Speed, Compatible Bus Interfaces

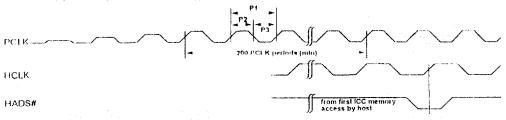

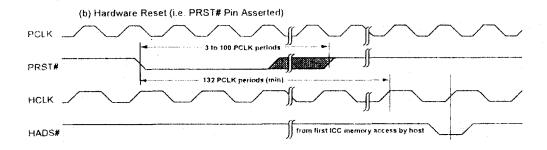

As shown in Figure 1.1, the KS0143 and KS0144 have three bus interfaces called HBUS, XBUS, and VBUS which are compatible between the two chips. Each bus interface operates synchronously with its own dedicated clock (HCLK, XCLK, and VCLK). A separate clock (PCLK) is used for internal data processing and has a maximum frequency of 40 or 50 MHz depending upon the speed grade.

The HBUS is a 16-bit, 33 MHz synchronous host processor interface optimized for connection to the buses of RISC microcontrollers from families such as the Intel<sup>®</sup> 1960\* and Advanced Micro Devices 29K\*. The KS0143 and KS0144 operate exclusively as slaves on the HBUS. The host processor (RISC microcontroller) accesses registers and memories within these chips via memory-mapped accesses.

Both the KS0143 and KS0144 contain on-chip program memories which are typically loaded by the RISC microcontroller over the HBUS. The KS0143 instruction RAM is 128 words by 40 bits and the KS0144 instruction RAM is 768 words by 32 bits.

The highest bandwidth utilization of the HBUS occurs during the transfer of zero-run length coded symbols between the KS0143 and host processor during real-time compression and decompression operations. The HBUS also provides a level-sensitive interrupt from the KS0143 or KS0144 to the host processor.

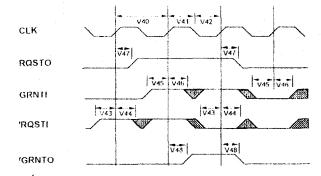

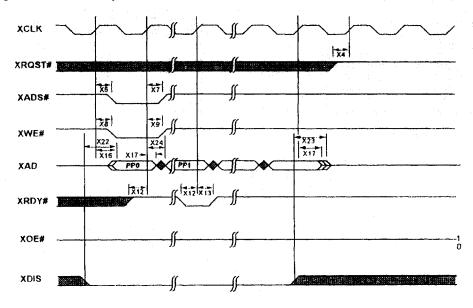

The XBUS is a 24-bit, 40 MHz synchronous auxiliary processor bus used primarily for vector data transfers between the KS0143 and KS0144. The user may also define KS0143 "external" instructions to direct transfers over the XBUS which may be connected to processors other than the KS0144.

Table 1.1-KS0143 / KS0144 Performance Benchmarks at 30 Frams Per Second

|                              | KS0143CQ-50<br>KS0144CQ-50                                                               | KS0143CQ-40<br>KS0144CQ-40                                                                 |

|------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| H.261<br>Codec               | CIF (352h × 288y) encode + 1CIF decode, or<br>QCIF (176h × 144V) encode + 5 QCIF decodes | QCIF encode + 1 CIF decode @ 15 fps, or QCIF encode + 6 QCIF decodes @ 30 fps              |

| MPEG-1<br>Encoder            | SIF ( 352h × 240V ) IBP encode with real-time preview                                    | SIF (352h × 240V) IBP encode, or<br>SIF (320h × 240V) IBP encode with real-time<br>preview |

| MPEG-1<br>Decoder            | 2 SIF (352h × 240V) IBP decodes at 30fps, or 1 SIF IBP decode @ 60fps                    | 2 SIF (352 $\times$ 240V) IBP decodes @ 30 fps, or 1 SIF IBP decode @ 60 fps               |

| JPEG<br>Encode or<br>Decoder | 720h × 480V, 4:2:2 YCrCb                                                                 | 720h × 480V, 4:2:2 YCrCb                                                                   |

The KS0143 is always the master of the XBUS, and up to four slave processors may be connected to it. In particular, up to four KS0144 chips may be connected to a single KS0143 for the purpose of allowing more searches in a given search area or allowing a search area to be expended beyond the capacity of a single KS0144. During motion estimation operations, the XBUS is used by the KS0143 to send 16x16 blocks of luminance pels to the KS0144 for prediction. The KS0144 in turn, uses the XBUS to return motion vectors and their corresponding 16x16 pel blocks found during motion estimation searches.

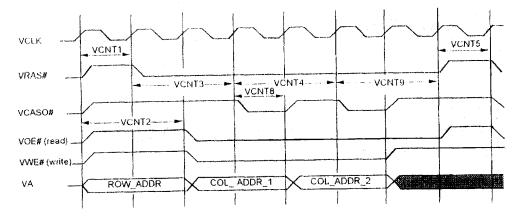

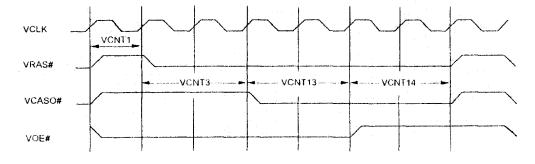

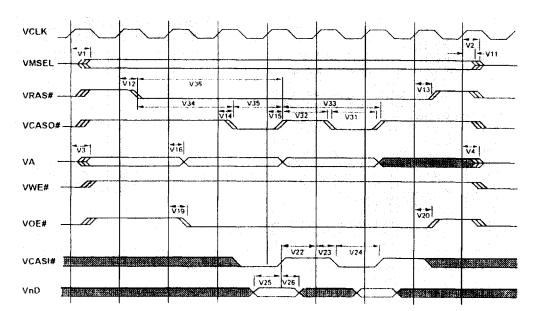

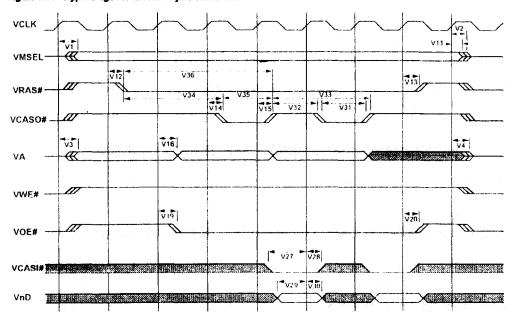

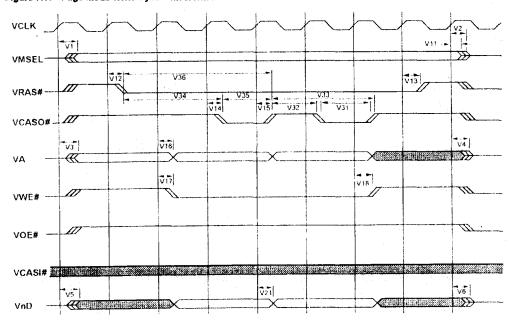

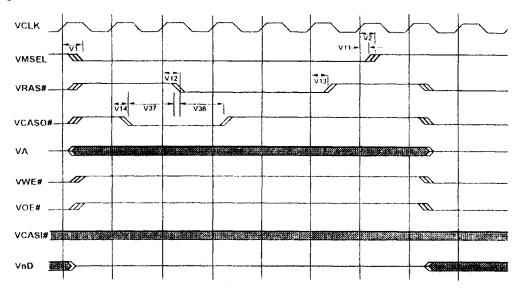

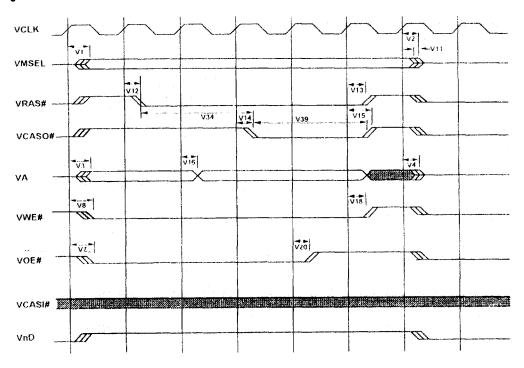

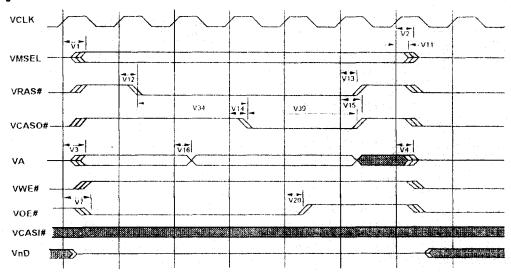

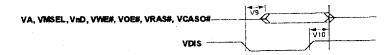

The VBUS is a multi-master, 32-bit memory bus designed to be directly connected to the data, address, and control pins of DRAMs and VRAMs. The timing characteristics of signals on the VBUS are determined by user-programmable registers within the KS0143 and KS0144. VBUS data transfers may be dynamically resized to 16 or 32-bits.

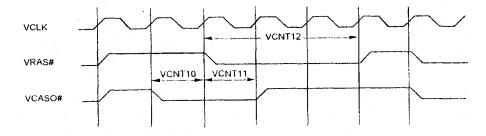

The VBUS data interface is divided into byte-wide lanes, each lane transferring one 8-bit pel. In 16-bit mode, the VBUS transfers two pels at a time and in 32-bit mode transfers four pels at a time. All transfers are performed as fast page mode accesses at a maximum rate of one column-access every 50 nsec, allowing a 16 x 16 pel block to be read or written in about 4.5 msec. The VBUS has an 11-bit address bus and three bits for memory selection which can access up to eight different images up to 4096 by 4096 pels each. A programmable CAS-before-RAS refresh controller is also included in the VBUS interface logic of both the KS0143 and KS01444.

The VBUS on both the KS0143 and KS0144 may be awarded to other bus masters via serial daisy chained bus arbitration. For example, an external bus master may be used to transfer images into or out of DRAMs connected to the KS0143. If an application permits, the KS0143 and KS0144 VBUS interfaces may be connected together in order to share the same memories. In this case, either the KS0143 or KS0144 is programmed to be at the head of the arbitration daisy chain, and one chip requests the VBUS from the other.

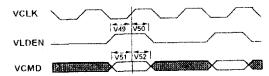

A unique feature of the KS0143 VBUS interface logic allows the KS0143 to transfer data between the serial and dynamic memory portions of VRAMs. This allows the serial port on VRAMs rather than the random access port on DRAMs to be used for image input/output, making the interface with external logic simpler and faster. Internal VRAM data transfers may be requested by either a video timing generator which asserts the KS0143 Övideo transfer commandó pins (VCMD[3:0]) or the host processor through a memory mapped register.

Input, output, and scratch images are stored in DRAMor VRAM-based memories connected to the VBUS on

the KS0143 and KS0144. The 4 Mbit memory shown in

Figure 1.1 stores the reference images used during

H.261 and MPEG-1 motion estimation searches and

may be implemented using a single 256K by 16-bit

DRAM. The 8 Mbit memory stores input and output

images as well as H.261 and MPEG-1 decoder

reference images. It may be implemented using two

256K by 16-bit or four 256K by 8-bit VRAMs depending

on how image input/output is performed. It is also

possible to use DRAMs in place of the VRAMs.

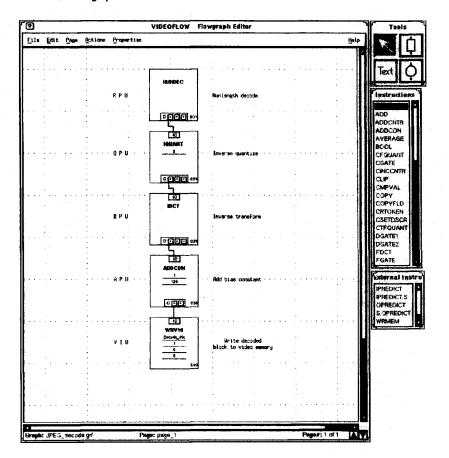

# **VIDEOFLOW Support Tools**

Array Microsystems, Inc. supplies a Hardware Evaluation Kit and Software Tool Kit to help customers design their KS0143/KS0144-based systems.

VFEB Hardware Evaluation Kit provides a hardware vehicle for designers and application developers wishing to explore the real-time performance and multi-standard versatility of the KS0143 and KS0144 chips. It consists of a PC plug-in board for the ISA or VI. bus, embedded software, a graphical user interface (GUI) that is compatible with the Windows<sup>TM</sup> operating system, and User Guide.

The KS0143/KS0144-based PC plug-in board and GUI allow the user to perform real-time (30 fps) demonstrations of the MPEG-1, JPEG, and H.261 standards for both video encoding and decoding. For encoding, users can connect their own analog video to the board and store compressed video to disk in real-time. Decoding demonstrations can read compressed video from either disk or CD-ROM and display the results on a video monitor.

The ICCST Software Tool Kit provides a UNIX workstation-based software development environment for designers wishing to architect, program, simulate, and verify video compression solutions based on the KS0143 and KS0144 chips. The tool kit contains:

- Programming tools consisting of a graphical flowgraph editor, assembler and linker for the KS0143, and a C-compiler and assembler for the KS0144

- Simulation tools consisting of an KS0143/KS0144 system simulator, configuration tools, program debugging aids, and various graphical displays for monitoring program performance

- Image analysis tools supporting the display of image sequences at or near real-time on a workstation monitor with optional graphical overlays of color-coded compression algorithm decisions and motion vectors produced by the simulator

- Comprehensive user and reference guide

- Demonstration package containing programs and simulation examples for the MPEG-1, JPEG, and H.261 video compression standards

#### Section 2 - KS0143 FUNCTIONAL

DESCRIPTION

The functional description of the KS0143 that follows refers to the block diagram that appears on the front page. Architecturally, the KS0143 is a programmable parallel processor consisting of a central controller and seven processor/bus interface units interconnected by a 96-bit global bus. The controller, called the Dataflow Control Unit (DCU), contains a 128 word by 40-bit instruction RAM and a large token memory which is used to hold instruction execution results.

Each of the processor and bus interface units (generically called functional units), is optimized to execute a subset of the KS0143 instruction set. The DCU schedules instructions for execution at run-time on the appropriate functional units, sends instructions and operands to these units over the global bus, and receives instruction results for storage in the token memory. Allocation and deallocation of token memory storage is handled by the DCU as a background task and is not explicitly controlled by the programmer.

The DCU and all functional units are clocked by PCLK which has a maximum frequency of 50 MHz. The collective KS0143 functional units have a peak throughput of over 1 billion operations per second. The global bus is capable of transferring eight 12-bit words per PCLK cycle, yielding a maximum burst throughput of 400 Mwords (or 600 Mbytes) per second.

#### **Dataflow Computing Model**

The KS0143 uses the DCU to implement a dataflow computing model. Dataflow computers such as the KS0143, share the primary characteristic that they are data-driven rather than control-driven like common microprocessors. Dataflow computers do not use a program counter to determine instruction execution order. Dataflow computers execute or "fire" an instruction when the operands, the resources, and a place to put the results are available. In a dataflow computer which contains multiple processor units (like the KS0143), many instructions may meet these criteria at the same time and can be executed in parallel.

Programs for dataflow computers are represented using directed graphs consisting of instruction nodes interconnected by arcs representing the flow of data between instructions. The data objects which travel on these flowgraph arcs are called "tokens".

The KS0143 is a static dataflow computer which allows only a single token to exist on an arc at any one time. This means that an instruction cannot execute again until its result from a previous execution has been consumed by all of its destination instructions.

The flowgraph-based programming used in the KS0143 makes it very easy for the user to specify the parallel execution of instructions. No complicated compiler technology is required as with VLIW (very long instruction word) and SIMD (single instruction - multiple data) architectures. The KS0143 programmer simply specifies how data flows between instructions by interconnecting them using the graphical flowgraph editor/assembler supplied with the VIDEOFLOW Software Tools. The DCU does the rest by scheduling instruction executions at runtime.

The KS0143 further simplifies programming by using highlevel instructions to perform arithmetic operations such as DCT and quantization on multiple data blocks. This allows programs to be very compact and therefore easy to write and understand.

#### **DCU Operation**

The DCU continually scans the KS0143 instruction RAM for instructions which are ready for execution. It checks the ready status of each instruction by consulting bookkeeping memories which tell it when the instruction operands (if any) are present in the DCU token memory and the result token (if any) from a previous execution of the instruction has been consumed by all of its destinations. The DCU also checks whether the functional unit required to execute the instruction is idle. Once an instruction is ready, the DCU dispatches both it and its operands to the appropriate functional unit over the global bus or, in some cases, executes the instruction itself.

If an operand is not needed by any other instruction after it is transmitted, the storage it occupies in the token memory is deallocated so that it may be reused by result tokens. After a functional unit finishes executing an instruction, it requests service from the DCU. The DCU subsequently allocates space in the token memory for the functional unit result token (if any) and directs the functional unit to send the result to the token memory over the global bus.

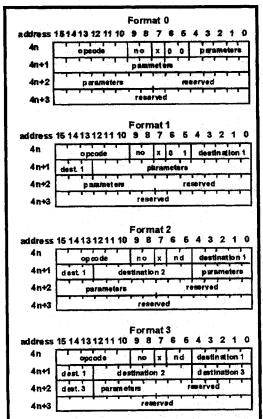

#### Instruction Formats and Field Definitions

| Field       | Definitions                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------|

| opcode      | x=0 : Internal function code<br>x=1 : opcode (5:2) is external function code<br>opcode (1:0) aux. processor address |

| no          | number of operands (0,1, or 2)                                                                                      |

| X           | external instruction flag (1=external)                                                                              |

| nd          | actual number of destinations                                                                                       |

| destination | Instruction destination address<br>bits 7:1 ≖Instruction address<br>bit0=operand port (0≃OP1, 1=OP2)                |

| parameters  | parameter field<br>(defination determined by opcode)                                                                |

#### Instruction Set

The KS0143 instruction set consists of 56 internal instructions plus 64 user-definable external instructions. The internal instructions are executed by the on-chip functional units or the DCU. The external instructions are executed by up to four off-chip (i.e. auxiliary) processors such as the KS0144. Each of these instructions processes zero, one, or two operand tokens and creates zero or one result tokens.

A user's KS0143 program consists of one or more flowgraphs which are loaded into the DCU instruction RAM by the host processor as part of system initialization.

Figure 2.1 shows that KS0143 instructions appear to the host as 64-bit words, but only the most significant 40 bits of each instruction are used. Each KS0143 instruction falls into one of four formats based on its maximum number of destinations.

The nd field specifies the actual number of destinations. For internal instructions (i.e. those for which x = 0), the opcode field specifies one of the KS0143 56 internal instruction types. For external instructions, opcode is undefined except for its two least significant bits which specify the address of the audiliary processor required to execute the instruction. Parameter bits have definitions which may vary from instruction to instruction.

The KS0143 instruction set is specifically designed to handle the real-time algorithm requirements of the H.261, MPEG-1, and baseline JPEG video compression standards and is divided into the following functional categories:

- Arithmetic instructions perform operations such as addition, subtraction, forward and inverse DCT (discrete cosine ransform), and forward and inverse quantization.

- Logical instructions perform boolean operations.

- Host Interface instructions allow data in a variety of formats to be transferred between the KS0143 and the host processor via the HBUS.

- Descriptor Modification instructions allow descriptive information about a token to be altered.

- Dataflow Control instructions control the passing of tokens between instructions based on data or flag-dependent conditions

- Video Memory instructions transfer tokens of image data between the KS0143 and video memories connected to the VBUS.

- External instructions execute on auxiliary processors (e.g. the KS0144) which are connected to the XBUS.

KS0143 internal instructions are listed in Tables 3.1 through 3.6 by functional category. The tables give the following information about each instruction:

- · the instruction mnemonic.

- · numerical operation code in hex (opcode),

- · number of required operands (no),

- · instruction format (fmt),

- · the unit which executes the instruction.

- · a brief operational description, and

- · a list of the instruction parameters.

For maximum performance, each of the KS0143 functional units is optimized to execute a particular subset of instructions. Some units only communicate with the global bus. These units include the:

- DCT Processor Unit (DPU),

- · Quantization Processor Unit (QPU), and

- · Arithmetic Processor Unit (APU).

Other functional units are primarily responsible for interfacing the KS0143 to the VBUS, HBUS, and XBUS and may also perform a moderate amount of computation. These include the:

- Video Interface Unit (VIU),

- · Token Interface Unit (TIU),

- · Run ength Processor Unit (RPU), and

- Auxiliary Interface Unit (AIU).

The Host Interface Unit (HIU), shown in the Functional Block Diagram, is not connected to the global bus but translates HBUS accesses by the host processor into accesses on an internal host bus which is connected to most of the functional units.

In addition to managing instruction executions, the DCU is capable of quickly modifying token descriptor contents. Note that the DCU itself is responsible for executing all of the instructions listed in Tables 3.2, 3.4, and 3.5. These operations are performed by the DCU Scalar Processor Unit shown in the Functional Block Diagram. While the DCU is executing an instruction, it cannot communicate with any of the functional units over the global bus.

All of the instruction mnemonics and parameter names that appear in Tables 3.1 - 3.6 are compatible with the VIDEOFLOW Software Tool Kit graphical flowgraph editor/assembler. The flowgraph editor allows the programmer to select KS0143 instructions from a menu, specify parameter values, and graphically interconnect different instructions to form flowgraphs. The numerical contents of all instruction fields are then automatically generated. Figure 2.2 shows a

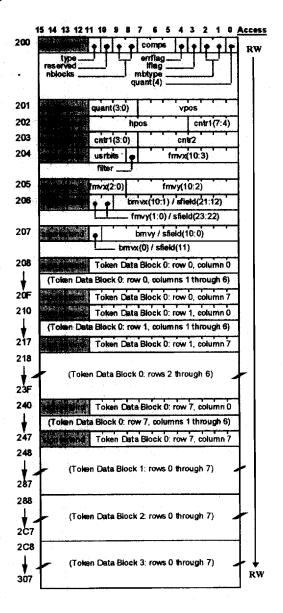

Token Types

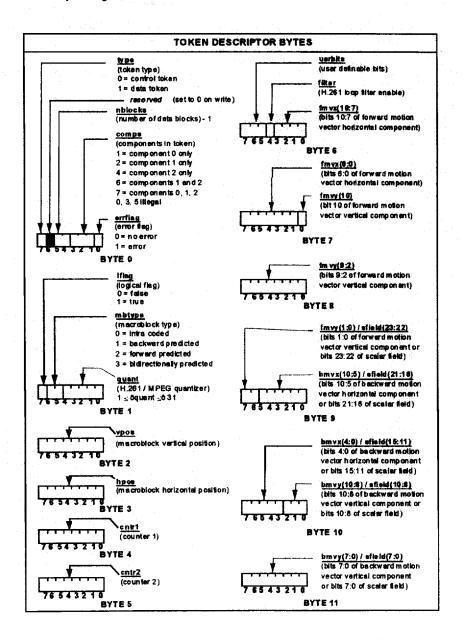

KS0143 instructions produce and consume two types of tokens: control tokens and data tokens. Both token types have a common data structure called the token descriptor. This is a single 96-bit word which for programming purposes, is organized as twelve 8-bit bytes having the fields shown in Figure 2.3. The most important field is the type field of byte 0 which identifies the token as a control or data token. Token descriptor contents are manipulated primarily using Descriptor Modification instructions (Table 3.4).

A control token consists of only a token descriptor. The data token consists of a token descriptor plus one to four data blocks. Each data block consists of 64 twelve-bit words which are generally interpreted by instructions as an 8x8, two's complement integer array. The number of data blocks making up a data token is indicated by the nblocks field within byte 0 of the token descriptor.

KS0143 instructions generally act on both token descriptors and data blocks. With data tokens, the information contained in the token descriptor relates to the token data blocks. For example, it may contain video memory coordinates, motion vectors associated with the data blocks, or other parameters to be applied to the data blocks during processing.

Both control and data tokens are stored in DCU token memory. Token data blocks are stored in the token memory in units called block allocation units (BAUs), each of which can hold up to two data blocks. A single BAU may not be split between two tokens, so each data token requires one or two full BAUs. The token memory can store a total of 52 BAUs which is sufficient for all JPEG, MPEG-1, and H.261 applications. The token memory also stores a total of 128 token descriptors (one for every instruction in the KS0143 instruction RAM). This is a sufficient capacity for all KS0143 programs, since each instruction in a flowgraph can produce only one result token.

Figure 2.2 - JPEG Decoder Flowgraph

3-10

Figure 2.3 - Token Descriptor Programmer's Model

#### Estimating KS0143 Performance

The best way to determine program performance is to simulate it using the KS0143 / KS0144800 VIDEOFLOW Software Tool Kit. The real-time statistical displays of the simulation manager show functional unit and global bus utilization during program execution. The tool kit instruction trace capability provides a detailed timing profile of each instruction execution, allowing instruction parallelism bottlenecks to be readily identified.

Execution times for each of the 56 KS0143 internal instructions are listed in Table 3.7 in PCL/ks. Two execution times are listed for each instruction (DCU Cycles and Unit Cycles). Both are functions of the number of data blocks making up instruction operand tokens. For non-DCU instructions, the clock cycles listed under DCU Cycles are used by the DCU to transfer tokens over the global bus to and from the functional units. Cycles listed under Unit Cycles are used by the functional units to both transfer and process tokens. Transfers over the global bus involving a given functional unit are not overlapped with data processing within that unit. This means Unit Cycles are the sum of DCU Cycles and token processing cycles. DCU instructions are executed entirely within the DCU, so their Unit Cycles are not applicable.

The execution time of an KS0143 program may be estimated in the manner described in the following sequence.

- Determine the computational loading of each KS0143

functional unit by adding together the Unit Cycles of all the

instructions in the program which are assigned to that unit.

The time associated with each instruction should include all

activities contributing to the execution time of that instruction,

e.g. video bus transfer time, host bus transfer time, amortized

overtiead for video memory refresh, etc.

- Estimate DCU loading by adding up the DCU Cycles across all instructions in the program.

- Pick the maximum time across all functional units and the DCU. This is an ideal estimate of program execution time.

Note:The ideal estimate does not include additional delays due to factors like DCU instruction operand polling or lack of synchronization between the firings and durations of different instructions. A more realistic estimate can be obtained by dividing the ideal time by a derating factor of 0.75. Note that derating factors are highly program dependent, and 0.75 is a pessimistic value of evaluation of a wide range of programs by Array Microsystems.

#### **Example Calculation:**

Assume a program which contains FDCT, IDCT, FQUANT and DDCONT instructions.

|               | Unit Cycles           | DCU Cycles         |

|---------------|-----------------------|--------------------|

| FDCT          | (80n+37) × (20nsec)   | (16n+4) × (20nsec) |

| IDCT          | (80n+35) × (20nsec)   | (16n+4) × (20nsec) |

| <b>FQUANT</b> | (80n+21) × (20nsec)   | (16n+4) × (20nsec) |

| <b>ADDCO</b>  | 1 (48n+15) × (20nsec) | (16n+4) × (20nsec) |

|              | DCU      | DPU       | QPU      | APU      |

|--------------|----------|-----------|----------|----------|

| FDCT         | 1.36usec | 7.14usec  |          |          |

| IDCT         | 1,36usec | 7.10usec  |          |          |

| FQUANT       | 1.36usec |           | 6.82usec |          |

| ADDCON       | 1.36usec |           |          | 4.14usec |

| Unit Loading | 5.44usec | 14.24usec | 6.82usec | 4.14usec |

Assume PCLK = 50Mhz (20 nsec), n=4 (16 × 16 pel block)

The ideal execution time is 14.24 msec. A derated estimate is 18.99 msec ( 14.24/0.75 )

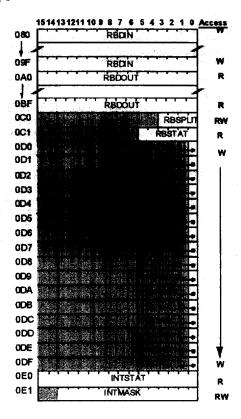

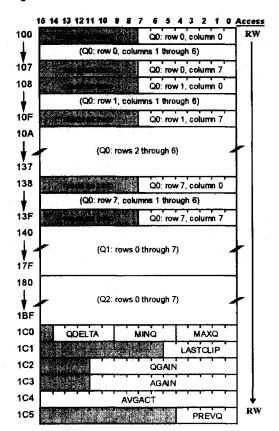

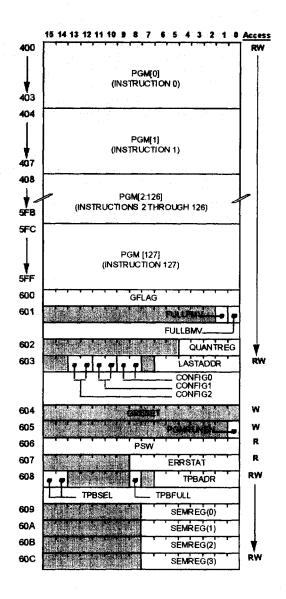

#### **Functional Unit Memory Maps**

All functional units except the DPU, APU, and AlU have registers and/or memories which the host processor may access using the HBUS. These registers and memories are described in Section 4. All register and memory names used are compatible with the KS0143 / KS0144800 VIDEOFLOW Software Tool Kit. Note that all addresses shown in the memory maps included in Section 4 are in hexadecimal and all shaded areas should be set to zero when written and are undefined when read unless otherwise noted.

#### Video Interface Unit (VIU)

The VIU (Section 4.1) supports all VBUS operations such as fast page mode read and write, memory refresh, and SAM (serial access memory) transfers. Arbitration logic within the VIU selects which internal operation has access to the VBUS at any point in time.

The VIU also supports reading blocks of image data which are offset by motion vectors stored in fmvx, fmvy, bmvx, and bmvy token descriptor fields (Figure 2.3). Motion vectors are interpreted as having full or half pel resolution depending on the state of the FULLFMV and FULLBMV registers in the DCU (Section 4.6). Full pel motion vectors follow the H.261 standard while half pel vectors follow the MPEG-1 standard.

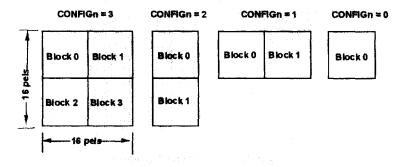

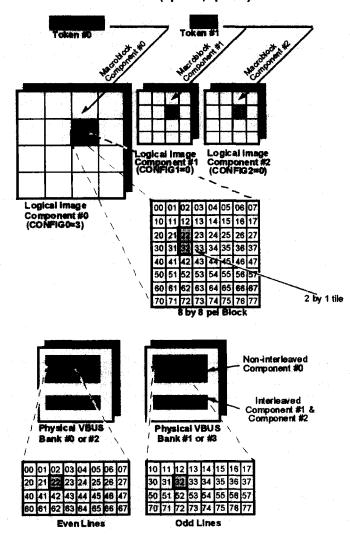

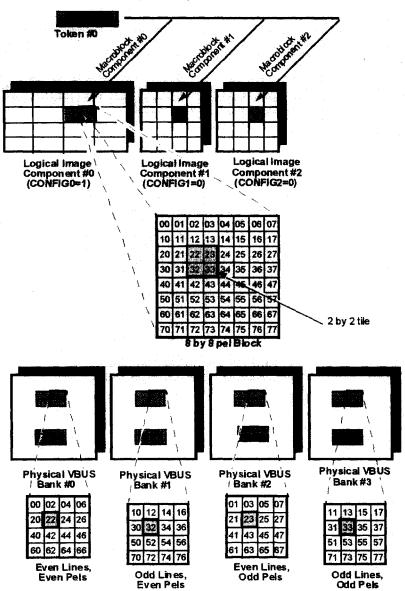

The KS0143 programming model treats a logical image as a series of logical image components (such as RGB or YUV) each up to 4096 by 4096 pels in size. Logical images are partitioned into "macroblocks" consisting of spatially-related components. Each macroblock component consists of one, two, or four 8x8 pel blocks as defined by its CONFIG register in the DCU memory map (Section 4.6).

A macroblock position is derived from the vpos (vertical position) and hpos (horizontal position) token descriptor fields of the VIU instruction operand token (Figure 2.3). These coordinates are further modified by factors such as motion displacement, interleave, and interpolation. The VIU transacts macroblocks with the DCU in the form of one or more tokens depending on the CONFIG registers. The comps field in the data token descriptor together with the values of the CONFIG registers (Section 4.6) determine the number of 8x8 pel blocks contained in the data token.

Figures 2.5 and 2.6 show how macroblocks may be assembled from tokens. The example 4:2:0 MPEG/H.261 macroblock configuration (Figure 2.5) appears to the KS0143 program as two tokens. Token 0 contains the image luminance data (Logical Image Component 0; comps = 1) configured as four 8x8 pel blocks (CONFIG0 = 3). Token 1 contains the image chrominance data (Logical Image Components 1, 2; comps = 6) configured as single 8x8 pel blocks (CONFIG1 = 0, CONFIG2 = 0). A macroblock can also fit into one token as in the case of the CCIR-601 YUV 2:1:1 image (Figure 2.6).

Figure 2.4 - Component Block Configuration

Logical image components are physically distributed across two or four 8-bit wide memory banks connected to the VBUS. The number of banks depends on whether 16- or 32-bit access mode is selected. More than one memory bank may be stored on a single memory chip; for example, a 256K by 16-bit DRAM stores two 512 by 512 eight-bit banks. The VIU transacts image data with physical memory in the form of 2x1 or 2x2 pel tiles depending on whether 16-bit or 32-bit access mode is selected.

In 16-bit access mode (Figure 2.5), pels from even numbered lines of a logical image component are stored in one memory bank and all pels from odd numbered lines are stored in the other. The two memory banks may be connected to video data buses VD0 and VD1 (Low Bus mode), or VD2 and VD3 (High Bus mode). Tiles are organized as two rows by one column pel arrays in order to minimize RAS cycle time in DRAM memory systems. The example configuration in Figure 2.5 shows that an 8x8 pel block can be fetched using only four RAS cycles.

In 32-bit access mode (Figure 2.6), even numbered pels from even lines are stored in bank 0, even numbered pels from odd lines are stored in bank 1, odd numbered pels from even numbered lines are stored in bank 2, and odd numbered pels from odd numbered lines are stored in bank 3. Each of the four memory banks is connected to a different video data bus. Using 32-bit access mode, tiles are dimensioned as 2x2 pels. Again, fewer RAS cycles are required, but if a motion vector is involved, the number of extra pels that are fetched is minimized.

Figure 2.5 - Example Macrobiack 4;2;0 Configuratin Using 16-bit Bus Mode

Macroblock at (hpos=2, vpos=1)

3-10

Figure 2.6 - Example Macroblock 2:1:1 Con figuration Using 32 bit Bus Mode

Macroblock at (hpos=2, vpos=1)

The example configuration in Figure 2.6 shows an 8x8 pel block motion offset by one row can be loaded using only five RAS cycles.

The VIU also supports features such as pel interleaving and line swapping which simplify the transfer of pels to and from external devices.

#### Run Length Processor Unit (RPU)

The RPU (Section 4.3) is responsible for converting data tokens between the internal format supported by all the functional units and the zero-run length coded format used for transferring compressed image data between the KS0143 and its host processor. The host processor then converts between the zero-run length coded format and the bit stream syntax defined by the particular compression standard being implemented.

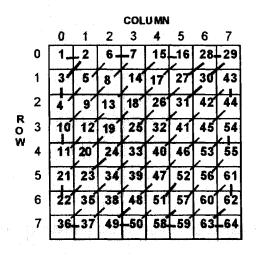

Each 8x8 data block within a data token is converted to the zero-run length coded format by first linearly ordering its words according to the zigzag scheme shown in Figure 2.7. The result is then coded as a sequence of 16-bit words containing (zero-run, level) pairs or symbols where Ozero-runO is the number of consecutive zero values preceding the value OlevelO. The zigzag ordering convention conforms to the JPEG, MPEG-1, and H.261 standards.

Figure 2.7- Data Block Zigzag Ordering

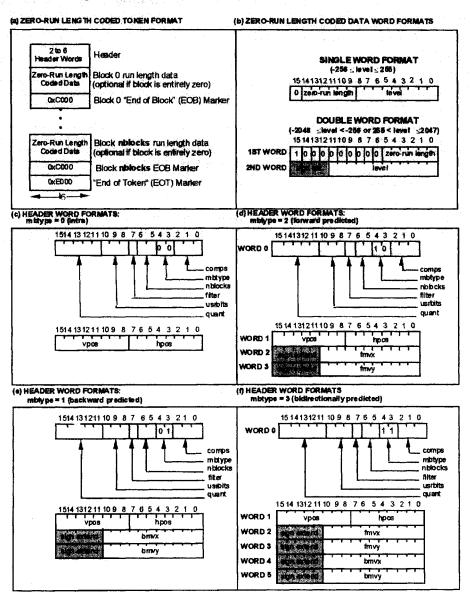

Figure 2.8 shows the various elements of the zero-run length coded format. Figure 2.8(a) shows the basic structure of a token coded in this format, it begins with two to six header words which contain a subset of the fields in the token's corresponding token descriptor. The number of header words depends on the token descriptor mixtype field which indicates which motion vectors (if arry) are associated with the token. Header word formats appear in Figures 2.8(c) through 2.8(f)

The header words are followed by nblocks+1 sequences of zero-run length coded symbols, i.e. one sequence for every data block in the token. As shown in Figure 2.8(b), each symbol consists of either one or two 16-bit words, depending on the level. Each sequence is terminated by an end-of-block marker word. The last end-of-block marker is followed by an end-of-token marker word.

The RUNENC and RUNENC.S instructions (Table 3.3) convert operand data tokens into zero-run length coded symbols and header words, while the RUNDEC instruction does the inverse. The symbols and headers reside in a 256 word by 16-bit bidirectional FIFO within the RPU. One end of the FIFO is accessed by the RPU while the other is accessed by the host processor via the HIU.

From the programmer's viewpoint, the FIFO is partitioned into two sections called INFIFO and OUTFIFO whose relative lengths may be configured by the host processor. The host always writes zero-run length coded symbols and header words to INFIFO and reads them from OUTFIFO. The access ports for both INFIFO and OUTFIFO appear in the RPU memory map as does a status register for informing the host of FIFO fullness. The RPU also contains togic for generating a level-sensitive interrupt to the host processor via the HINT# pin. The interrupt may be the result of the occurrence of one or more of 14 different interrupt conditions as defined by the INTSTAT register in the RPU memory map (Section 4.3).

#### Token Interface Unit (TIU)

The TIU (Section 4.5) contains a single 264 word by 12-bit memory called the Token Passing Buffer (TPB) which is used to pass tokens in their raw form between the KS0143 and the host processor. At any point in time the TPB may hold a single data or control token. The TIU writes the TPB with the operand token of a SNOOP instruction, and the host subsequently reads it in the format shown in the TIU memory map.

Figure 2.8 - Zero - Run Length Coded Data Formats

Figure 2.9 - ADPATQ instruction Execution

With SNEAK instructions, the host writes a token into the TPB using the format shown in Section 4.5. As a result, the TIU writes the token back to the DCU over the global bus. The host controls the TPB via the TPBSEL, TPBFULL, and TPBADR registers which reside in the DCU memory map (Section 4.6). An interrupt condition is also defined that notifies the host when the TPB is empty or full (see INTSTAT; Section 4.3).

The programmer may regard SNEAK and SNOOP instructions as software probes allowing a token to be injected or sampled at any point in the KS0143 program. For example, they may be used for program debugging, starting flowgraph execution, or signaling the host processor of various events. SNOOP and SNEAK may also interface with the entry and return points. respectively, of procedures implemented by the host processor.

#### Quantization Processor Unit (QPU)

The QPU (Section 4.4) implements the JPEG, MPEG-1, and H.261 forward and inverse quantization algorithms, it also performs variance, mean square, and adaptive quantizer computations. The JPEG, MPEG-1, and H.261 inverse quantization algorithms fully conform to all three standards. The MPEG-1 and H.261 forward quantization algorithms are derived from MPEG-1 OVideo Simulation Model 3Ó (SM3) and H.261 ÖReference Model 8Ó (RM8), respectively.

in place of the SM3 flat matrix, the QPU version of the SM3 non-intra forward quantization algorithm fully incorporates the nonintra quantization matrix of the MPEG-1 standard.

The adaptive thresholding algorithm implemented in the TFQUANT and CTFQUANT instructions is taken from Section 7.2.1 of SM3.

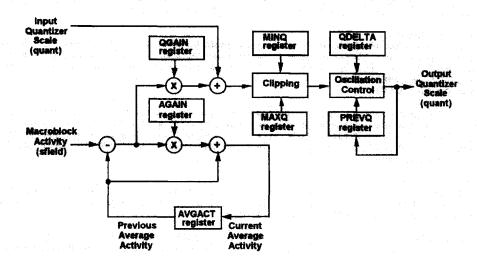

The MPEG-1 quantizer\_scale or the H.261 macroblock quantizer is stored in the token descriptor quant field. The QPU provides three stages for adaptively modifying quant during MPEG-1 and H.261 encoding via the SETQUANT, ADAPTQ, CFQUANT, and CTFQUANT instructions. During the first stage, quant is initialized by the SETQUANT instruction which copies the contents of the DCU QUANTREG register (Section 4.6) into the quant field of the SETQUANT operand token. QUANTREG is modified by the host processor as needed to achieve a targeted bit rate.

During the second stage, the ADAPTO instruction modifies quant as a linear function of changes in instantaneous image activity relative to average image activity, generally pushing quant higher for positive changes and lower for negative changes. This decreases quant in relatively flat image areas and increases it in busy areas in order to achieve good perceived quality across the entire reconstructed image without compromising compression. Prior to the execution of ADAPTQ, image activity is computed for the luminance token of a macroblock by the VAR instruction with the results stored in the sfield token descriptor

A block diagram of the ADAPTQ instruction execution appears in Figure 2.9. The various registers depicted in the block diagram are defined in the QPU register descriptions of Section 4.4.

During the third stage, the CFQUANT or CTFQUANT instruction automatically increases quant as needed to prevent excessive quantization clipping, and then performs forward quantization.

Excessive clipping causes image artifacts. These artifacts are especially visible for DCT coefficients closer to the DC coefficient. CFQUANT and CTFQUANT use the contents of the QPU LASTCLIP register to determine which coefficients to protect from excessive clipping. Details appear in the description of the LASTCLIP register in Section 4.4.

#### **DCT Processor Unit (DPU)**

The DPU performs forward and inverse discrete cosine transforms (DCTs) on 8x8 blocks of data. Forward DCTs process 9-bit twoÖs complement data into 12-bit twoÖs complement results. Inverse DCTs process 12-bit twoÖs complement data into 9-bit twoÖs complement results. The accuracy of the inverse DCT performed by the DPU fully conforms to the require ments of the JPEG, MPEG-1, and H.261 standards.

Arithmetic Processor Unit (APU)

The APU is the only functional unit capable of operating on two data token operands performing binary operations such as addition and subtraction. The most complex operation performed by the APU is the loop filter function as defined in the H.261 standard. The loop filter is conditionally invoked by the FILTER instruction (Table 3.1) depending on whether the filter token descriptor bit is set in the instruction operand token. Bidirectional predictions as defined in the MPEG-1 standard are computed using the AVERAGE instruction.

#### Host Interface Unit (HIU)

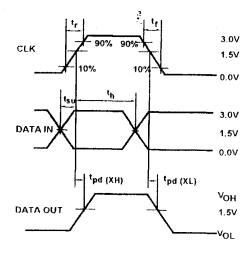

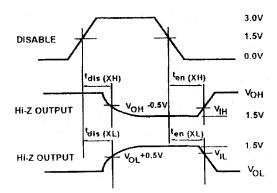

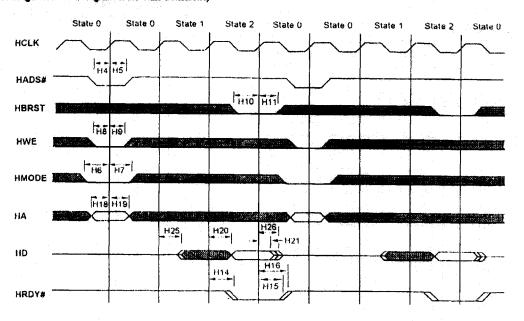

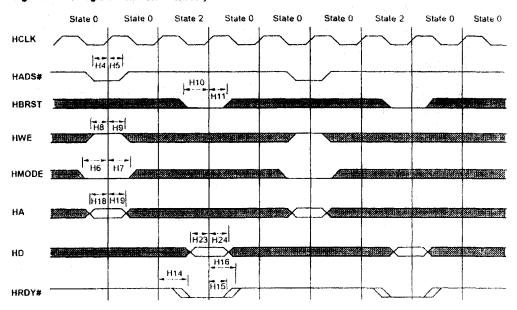

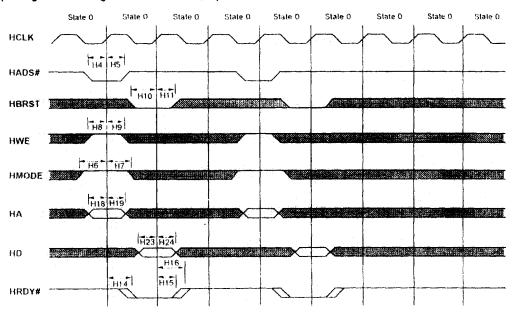

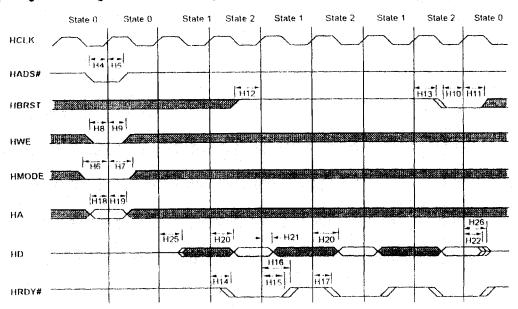

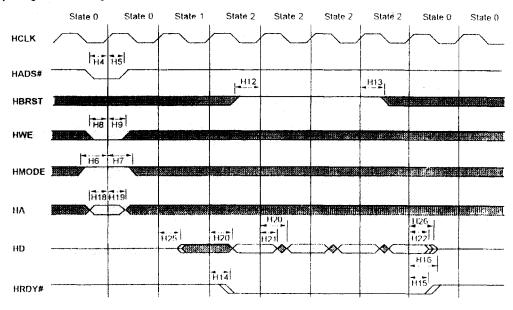

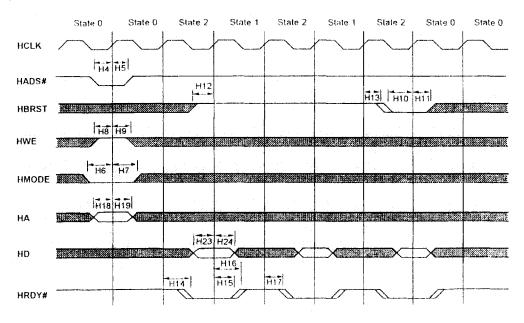

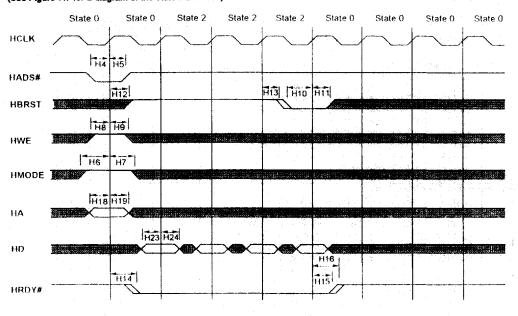

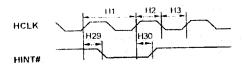

All host interface bus cycles supported by the HIU transfer 16-bit words synchronous to HCLK. Both burst and non-burst cycles are supported. Each non-burst read by the host processor requires four HCLK cycles (HMODE pin = 0). Each non-burst write requires two or three HCLK cycles (HMODE = 1 or 0, respectively).

Burst cycles transfer multiple words at the rate of one every one or two HCLK cycles (HMODE = 1 or 0, respectively). The host processor need only supply the address for the first word in a burst since the other addresses are generated internally by the HIU.

When accessing multiple words at the same address (e.g. the RPU INFIFO or OUTFIFO port), the host processor may disable internal incrementing of burst transfer addresses by writing a "1" to the BINCDIS register beforehand (Section 4.2).

All burst cycles other than burst reads with HMODE = 1 are terminated by the deassertion of the HBRST pin during the final word transfer and may be up to 2048 words long. A burst read cycle with HMODE = 1 can only be up to 257 words long and requires that its length be written beforehand into the HIU BLENGTH register.

#### Auxiliary Interface Unit (AIU)

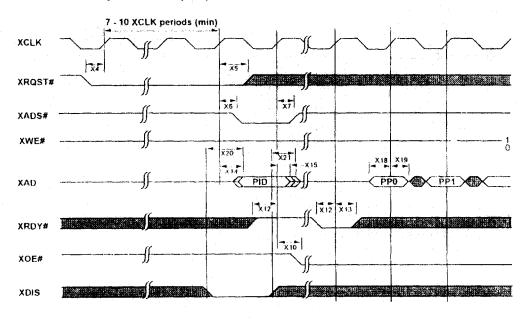

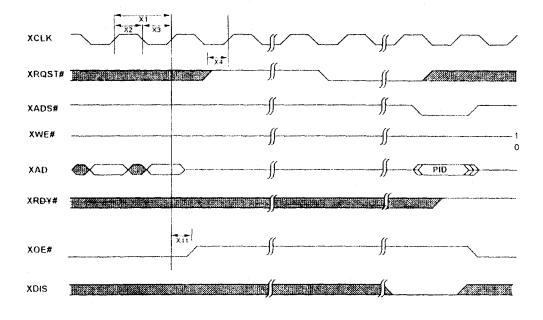

The DCU dispatches each external instruction to the AIU, which then transmits both the instruction and its operand token (if any) to the appropriate auxiliary processor unit via the XBUS. The auxiliary processor then executes the instruction and returns its result to the AIU, which then notifies the DCU. Each external instruction may process either zero or one operand token and create either zero or one result token. An auxiliary processor may execute up to four different instructions in parallel. For example, the KS0144 can simultaneously execute three external instruction classes called (PREDICT, OPREDICT, and WRMEM.

Figure 2.1 shows the least significant two bits (bits 1:0) of an external instruction opcode field selects the auxiliary processor to be used. Bits 3:2 of opcode specify the parallel execution class of the instruction. Instructions from different classes may execute in parallel, but only one instruction may execute at a time from any given class. The DCU maintains a 16-bit external instruction status table to track which classes have instructions executing on which auxiliary processors at any point in time.

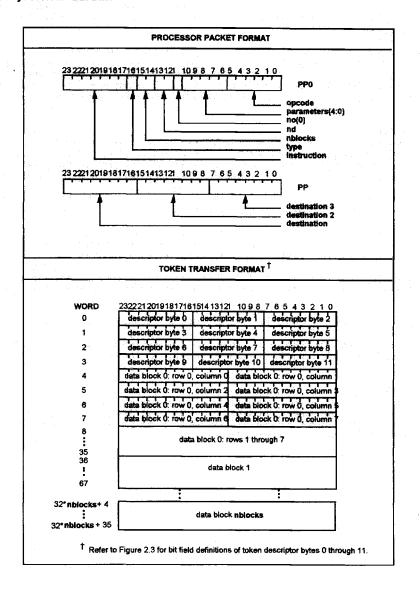

The AlU uses auxiliary processor write cycles to transmit external instructions and operands over the XBUS. These cycles are 24-bit word data transfers consisting of two processor packet words (PPO and PP1) followed by zero to 132 words of token data. The processor packet and token transfer formats appear in Figure 2.10.

One 24-bit word is transmitted every XCLK cycle. The processor packet consists of fields copied from the external instruction and nblocks and type fields copied from the operand token descriptor, if it exists.

3-11

Figure 2.10 - Auxally Processor Bus Data

The operand token is transmitted as four words containing the token descriptor followed by 32 words for each of (nblocks+1) token data blocks if the token is a data token. An auxiliary processor sends results back to the AIU by first requesting an auxiliary processor read cycle from the AIU.

The selected auxiliary processor does this by asserting its XRQST# pins (one of four) on the KS0143. The AlU acknowledges the auxiliary processor by broadcasting its address on the XBUS. The auxiliary processor then responds by sending back a processor packet corresponding to the instruction completing execution. The processor packet is followed by zero to 132 words of result token data, all of which have the formats shown in Figure 2.10. Depending on external instruction execution times, it is possible that several auxiliary processor write cycles may take place for different instructions before an auxiliary processor read cycle occurs.

#### **Dataflow Control Unit (DCU)**

The instructions executed by the DCU create tokens, modify token descriptors, copy tokens, and control program dataflow. The CRTOKEN instruction bootstraps flowgraph execution by firing only once and creating a token from a parameter list. Token descriptor modification instructions operate on either arbitrary bits within the token descriptor bytes of Figure 2.3 or on predefined fields such as hoos and vpos. Token copying instructions copy either all or part of one token to another.

Dataflow control instructions fall into two groups. Instructions in the first group, such as FGATE and DGATE1, act like spigots which turn dataflow on and off by either passing or annihilating tokens.

Instructions in the other group (semaphore instructions), do not turn dataflow on and off but rather delay turning it on until certain events occur. Semaphore instructions may be used to create dataflow multiplexers, guard the entrances to flowgraphs so as to prevent token memory overflow, and synchronize flowgraph execution with the host processor.

The semaphore instructions are INITSEM, TSTSEM, TSTDEC, and INCSEM. These instructions atomically manipulate and/or test the contents of the semaphore registers (SEMREG0, SEMREG1, SEMREG2, and SEMREG3) in the DCU memory map (Section 4.6).

The semaphore registers and like global variables, allowing dataflow in different branches of a flowgraph to be synchronized.

For example, the TSTSEM instruction holds its operand token at its input until a semaphore matches the cntr1 field in the operand token's token descriptor. Typically, the semaphore's value is changed by a INCSEM instruction elsewhere in the program.

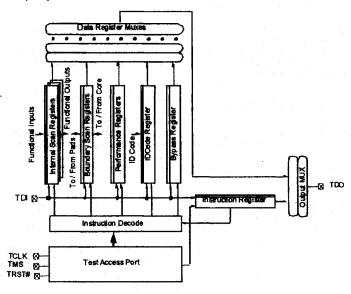

#### **Test Control Unit (TCU)**

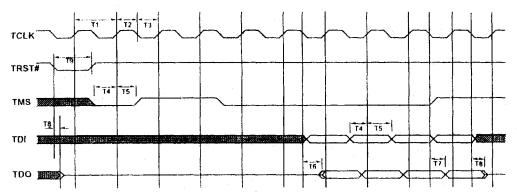

A simplified block diagram of the KS0143 Test Control Unit (TCU), associated registers, and instruction set appear in Figure 2.11. The TCU supports boundary scan in compliance with the IEEE 1149.1 (JTAG) standard and also allows external logic to read and write the KS0143's internal scan paths, please contact the Array Microsystems technical applications support group.

3-10

Figure 2.11 - Test Control Unit (TCU)

### Instruction Set

SAMPLE/PRELOADLoad/sample boundary registers through I/O pins

EXTESTStimulate/observe I/O pins through serial test port

INTESTStimulate/observe IC core through serial test port

BYPASSQuick bypass of serial data input to serial data out

IDCODER ead hardwired ID code through serial test port

PERFORMANCEEnable/observe internal performance ring counter

INSCANStimulate/observe internal data registers through serial test port (with reset)

INSAMPLEStimulate/observe internal data registers through serial test port (without reset)

#### **SECTION3 - KS0143 INSTRUCTION SET**

This section contains Tables 3.1 through 3.6 which describe the various instructions that the KS0143 executes internally. The table columns are defined as follows:

- Mnemonic is the instruction symbolic name as defined by the VIDEOFLOW Software Tools flowgraph editor.

- · opcode and no are the contents of the corresponding instruction fields as shown in Figure 2.1:

- > opcode is the instruction operation code.

- > no identifies the number of operands required by the instruction.

- fmt identifies which of the four formats the instruction is (see Figure 2.1). It also identifies the maximum number of destinations the instruction can have in an KS0143 program.

- · Unit identifies the KS0143 functional unit responsible for executing the instruction.

- Description contains the basic operation performed by the instruction including any required parameter fields. Parameter names are those defined by the VIDEOFLOW Software Tools flowgraph editor. The numbers preceding each parameter name identify the bit positions the parameter occupies within the instruction.

Table 3.7 contains the instruction timing for each of the instructions relative to PCLK cycles.

Table 3.1 - KS0143 Arkhmetic Instructions

| Mnemonic | op-code | no | fmt | Unit | Description                                                                                                                                                                                             |

|----------|---------|----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FILTER   | 01      | 1  | 3   | APU  | Conditionally performs H.261 loop filter on data token based on filter descriptor bit ( no parameters )                                                                                                 |

| ADD      | 02      | 2  | 3   | APU  | Adds two data token and optionally clips the sum to the range [0.255] (0) clip: 1=enable clipping, 0=disable clipping                                                                                   |

| AVERAGE  | 03      | 2  | 3   | APU  | Adds two data tokens, halves the sum, and merges motion vectors (no parameters)                                                                                                                         |

| SUBTRACK | 04      | 2  | 3   | APU  | Subtracts two data tokens ( no parameters )                                                                                                                                                             |

| ADDCON   | 05      | 1  | 2   | APU  | Adds const to data token and optionally clips the sum to the range [0,255]  (9) clip: 1=enable clipping, 0=disable clipping  (8:0) const: constant with a range [-256,255]                              |

| CLIP     | - 06    | 1  | 1   | APU  | Clips data token to fall within the range [minval, maxval] (15:8) minval: constant with the range [0,255] (7:0) maxval: constant with the range [0,255]                                                 |

| FDCT     | 07      | 1  | 3   | DPU  | Performs 8x8 inverse DCT on each of the data blocks within a data token (no parameters)                                                                                                                 |

| IDCT     | 08      | 1  | 3   | DPU  | Performs 8x8 inverse DCT on each of the data blocks within a data token (no parameters)                                                                                                                 |

| FQUANT   | 09      | 1  | 3   | QPU  | Forward quantizes and clips data token  (4:2) clipsel (clipping range limits ):  0 = ± 127, 1= ± 255, 2= ± 511, 3= ± 1023, 4= ± 2047  (!:0) algsel ( quantization algorithm ):  0=H.261, 1=MPEG, 2=JPEG |

| TFQUANT  | 0A      | 1  | 3   | QPU  | Adaptively thresholds, forward quantizes, and clips data token (4:2) clipsel (clipping range limits):  0= ± 127, 1= ± 255, 2= ± 511, 3= ± 1023, 4 (0) algsel (quantization algorithm):  0=H.261, 1=MPEG |

Table 3.1 - KS0143 Arithmetic Instructions ( Continued )

| Mnemonic | op-code | no | fmt | Unit | Description                                                                                                                                                                                                                                                                                        |

|----------|---------|----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IQUANT   | OB      | 1  | 3   | QPU  | Inverse quantizes data down<br>(1:0) algsel (quantization algorithm):<br>0≈H.261, 1≈MPEG, 2≈JPEG                                                                                                                                                                                                   |

| MEANSQ   | 0C      | 1  | 3   | QPU  | Computers mean square value of Component 0 within data token (no parameters )                                                                                                                                                                                                                      |

| VAR      | 000     | 1  | 3   | QPU  | Computes variance or spatial activity of Component 0 within data token  (0) varsel: 0=compute variance, 1=compute spatial activity                                                                                                                                                                 |

| ADAPTQ   | 34      | 1  | 3   | QPU  | Adapts quantizer quant field based on relative measure of spatial activity (no parameters)                                                                                                                                                                                                         |

| CTFQUANT | 38      | 1  | 3   | QPU  | Adaptively thresholds, forward quantizes and clips data token increasing quantizer as needed to prevent excessive quantization clipping (4:2) clipsel (clipping range limits):  0=± 127, 1=± 255, 2=± 511, 3=± 1023, 4=± 2047 (0) algsel (quantization algorithm):  0=±.261, 1=MPEG                |

| CFQUANT  | 39      | 1  | 3   | QPU  | Forward quantizes and clips data token, increasing quantizer as needed to prevent excessive quantization clipping (4:2) clipsel (clipping range limits):  O=clipsel (clipping range limits):  O=± 127, 1=± 255, 2=± 511, 3=± 1023, 4=± 2047  (0) algsel (quantization algorithm):  O=H.261, 1=MPEG |

Table 3.2 -KS0143 Logical instructions

| Mnemonic | op-code | no  | fmt | Unit | Description                                                                                                                                                                                                                                          |

|----------|---------|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMPVAL   | OF      | 2   | 3   | DCU  | Compares the sfield descriptor fields of two tokens (no parameters)                                                                                                                                                                                  |

| TSTVAL   | 10      | - 1 | 1   | DCU  | Compares the sfield descriptor field of a token against a constant (20:0) const : constant with a range [-2 <sup>20</sup> , 2 <sup>20</sup> -1]                                                                                                      |

| TSTDSCR  | 11      | 1   | 1   | DCU  | Logically matches a specified token descriptor bit field against constant (19:6) bytesel: descriptor byte select with a range [0,11] (15:8) mask: boolean mask applied to selected byte (7:0) boonst: boolean constant used for bit-wise comparision |

| BOOL     | 12      | 2   | 3   | DCU  | Performs a logical operation between two token descriptor iflag fields (2) compl1: 1= complement iflag of first operand token (1) compl2: 1= complement iflag of second operand token (0) op (logical operation): 0=OR, 1=AND                        |

| TSTCNTR  | 35      | 1   | 2   | DCU  | Compares a specified token descriptor counter field against a constant (9:8) cntrsel (counter field): 0= vpos, 1=hpos, 2=cntr1, 3=cntr2 (7:0) const: constant with the range [0,255]                                                                 |

Table 3.3 - Host Interface instructions

| Mnemonic | op-code | no | fmt | Unit | Description                                                                                                                                                            |

|----------|---------|----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RUNENC   | 2B      | 1  | 0   | RPU  | Reorders token data block words in zigzag fashion, encodes them as (zero - run, level ) pairs, and palces them in the RPU OUTFIFO for access by host ( np parameters ) |

| RUNENC.S | 2C      | 1  | 3   | RPU  | Same as RUNENC, except signals after writing all data to the RPU OUTFIFO (no parameters)                                                                               |

| RUNDEC   | 2D      | 0  | 3   | RPU  | Reads a series of (zero - run, level) pairs from the RPU INFIFO, decodes and inverse zigzags, and creates a data token from the result (no parameters)                 |

| SNOOP    | 2E      | 1  | 0   | TIU  | Copies token into Token Passing Buffer for access by host processor (no parameters)                                                                                    |

| SNEAK    | 30      | 0  | 3   | TIU  | Creates token from contents of Token Passing Buffer (no parameters)                                                                                                    |

Table 3.4 - KS0143 Descriptor Modification Instructions

| Mnemonic | op-code | по | fmt | Unit | Description                                                                                                                                                                                                                                                          |

|----------|---------|----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUBVAL.  | OE      | 2  | 3   | DCU  | Subtracts the sfield descriptor fields of two tokens  (0) scale: 0=subtract the sfield descriptor bits of two tokens 1=divide the first sfield by two before subtracting                                                                                             |

| СОРУ     | 13      | 1  | 3   | DCU  | Copies an entire token or only the token's descriptor (0) copysel: 0= copy entire token 1= copy token descriptor only                                                                                                                                                |

| CRTOKEN  | 15      | 0  | 3   | DCÚ  | Creates a control token based on instruction parameters (4:3) nblocks: result descriptor nblocks field (2:0) comps: result descriptor comps field                                                                                                                    |

| INCONTR  | 16      | 1  | 2   | DCU  | Unconditionally adds const to a specified token descriptor counter field (9:8) cntrsel (counter field): 0=vpos, 1=hpos, 2=cntr, 3=cntr2 (7:0) const: constant with the range [-128,255]                                                                              |

| CINCONTR | 17      | 2  | 2   | DCU  | Conditionally adds a constant to a specified token descriptor counte field  (10) Isense: Iflag descriptor bit value required to enable increment operation  (9:8) cntrsel: 0=vpos, 1=hpos, 2=cntr1, 3=cntr2  (7:0) const: constant with the range [-128,256]         |

| ADDONTR  | 18      | 2  | 3   | DCU  | Adds the specified token descriptor counter fields from two tokens (3:2) cntrsel1 (operand 1 counter field): 0=vpos, 1=hpos, 2=cntr1, 3=cntr2 (1:0) cntrsel2 (operand 2 counter field): 0=vpos, 1=hpos, 2=cntr1, 3=cntr2                                             |

| SETDSCR  | 18      | 1  | 1   | DCU  | Unconditionally sets a specified token descriptor bit field to a constant (19:16) bytesel: descriptor byte select with the range [0,11] (15:8) mask: boolean mask specifying bits in selected byte (7:0) bconst: boolean constant specifying values of selected bits |

| COPYFLD  | 37      | 2  | 2   | DCU  | Copies a specified token descriptor bit field from one token to another (12) copyall: 1=copu entire descriptor to output token (11:8) bytesel: descriptor byte select with the range [0,11] (7/:0) mask; boolean mask specifying bits in selected byte               |

Table 3.4 - KS0143 Descriptor Modification Instructions ( Contiuned )

| Mnemonic | op-code | no | fint | Unit    | Description                                                                                |

|----------|---------|----|------|---------|--------------------------------------------------------------------------------------------|

|          |         |    |      |         | Conditionally sets a specified token descriptor bit field to a constant                    |

|          |         |    | 1    | 1       | (20) isense : Ifiag descriptor bit value required to enable set                            |

| CSETDSCR | 1C      | 2  | 1 1  | DCU     | operation                                                                                  |

|          |         | ł  |      |         | (19:16) bytesel: descriptor byte select with the range [0,11]                              |

|          |         |    | ]    |         | (15:8) mask: boolean mask specifying bits in selected byte                                 |

| 254      |         | 1  |      | Same of | (7:0) boonst: boolean constant specifying values of selected bits                          |

| SETQUANT | 1D      | 1  | 3    | DCU     | Sets token descriptor quant field to the contents of the QUANTREC register (no parameters) |

Table 3.5 - KS0143 Dataflow Control Unit Instructions

| Mnemonic | op-code | no | frent | Unit | Description                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|----|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DGATE1   | 14      | 1  | 1     | DCU  | Gates token based on value of bit field in token's token descriptor  (20) Isense: 0=pass token if bit field does not equal value  1=pass token if bit field equals value  (19,16) bytesel: descriptor byte select with the range [0,11]  (15:8) mask: boolean mask specifying bits in selected byte  (7:0) bconst: boolean constant specifying values of selected bits |

| DGATE2   | 2F      | 2  | 1     | DCU  | Gates Operand 1 based on value of bit field in token descriptor of Operand 2  (20) Isense: 0=pass token if bit field does not equal value 1=pass token if bit field equals value, (19:16) bytesel: descriptor byte select with the range [0,11] (15:8) mask: boolean mask specifying bits in selected byte (7:0) const: constant with the range [0,255]                |

| CGATE    | 36      | 1  | 2     | DCU  | Gates token based on value of counter field in token's descriptor  (10) Isense: 0=pass token if bit field does not equal value  1=pass token if bit field equals value  (9:8) cntrsel (counter field):  0= vpos, 1=hpos, 2=cntr1, 3=cntr2  (7:0) const : constant with the range [0,255]                                                                               |

| MINIMAX  | 31      | 2  | 3     | DCU  | Selects token having minimum or maximum sfield descriptor field (4) maxsel: 0=select minimum, 1=select maximum                                                                                                                                                                                                                                                         |

| GATE     | 1E      | 2  | 3     | DCU  | Gates token based on the Iflag descriptor bit of another token (4) Isense : value of Iflag in Operand 2 require to pass Operand 1                                                                                                                                                                                                                                      |

| FGATE    | 1F      | 1  | 3     | DCU  | Gates token based on the state of selected bit in GFLAG register (4) Isense: 0=pass token if selected bit in GFLAG is 0 1=pass token if selected bit in GFLAG is 1 (3:0) flagsel: GFLAG bit select with the range [0,15]                                                                                                                                               |

| INITSEM  | 22      | 1  | 2     | DCU  | Sets selected bits of a semaphore register to a constant (11:10) semreg : semaphore register select with the range [0,3] (9:8) semnib ( semaphore nibble select ):  O=low nibble, 1=high nibble, 2=entire register (7:0) const : constant                                                                                                                              |

| TSTSEM   | 20      | 1  | 2     | DCU  | Suspends dataflow until selected cntr1 bit field in token descriptor matches bit field in selected sempaphore register (11:10) semreg : semaphore register select with the range [0,3] (8) semnib ( semaphore nibble select ):  0=low nibble, 1=high nibble (3:0) mask : boolean mask specifying bits in cntr1 and selected nibble                                     |

Table 3.5 - KS0143 Dataflow Control Unit Instructions ( Continued )

| Mnemonic | op-code | no | fmt | Unit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSTDEC   | ЗА      | 1  | 2   | DCU  | Suspends data flow until selected semaphore register is greater than or eual to a constant, then subtracts the constant from semaphore register (11:10) semreg: semaphore register select with the range [0,3] (9:8) semnib (semaphore nibble select):  O= low nibble, 1= high nibble, 2=entire register (7:4) const1: constant with the range [0,15]; select if nblocks descriptor field in operand token is 2 or 3  (3:0) const2: constant with the range [0,15]; selected if nblocks descriptor field in operand token is 0 or 1 |

| INCSEM   | 21      | 1  | 2   | DCU  | Adds constant to selected semaphore register  (11:10) semreg; semaphore register selecft with the range [0,3]  (9:8) semnib ( semaphore nibble select ):  0= low nibble, 1= high nibble, 2= entire register  (7:4) const1: constant with the range [0,15];  selected if nblocks descriptor field in operand token is 2  or 3  (3:0) const2: constant with the range [0,15];  selected if nblocks descriptor field in operand token is 0  or 1                                                                                       |

Table 3.6 - KS0143 Video Memory Instructions

| Mnemonic | op-code | no | fmt | Unit | Description                                                                                                                                                                            |

|----------|---------|----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDV16    | 23      | 1  | 2   | VIU  | Reads data token from 16-bit wide memory (12:10) memsel: memory select 0,1,2,3=uses Low Bus: 4,5,6,7 uses High Bus (9:8) corgsel: component origin register select with the range[0,3] |

| NOVIO    | 23      | ,  |     | *10  | (7:4) horgsel: subpicture horizontal origin divided by 128 with the range [0,15]                                                                                                       |

|          |         |    |     |      | (3:0) vorgsel: subpicture vertical origin divided by 128 with the range [0,15]                                                                                                         |

|          |         |    |     |      | Reads data token from 16-bit wide memory offset by forward motion vector                                                                                                               |

|          |         |    |     |      | (12:10) memsel : memory select 0,1,2,3=uses Low Bus: 4,5,6,7 uses High Bus                                                                                                             |

| RDV16FMV | 24      | 1  | 2   | VIU  | (9:8) corgsel: component origin register select with the range [0,3] (7:4) horgsel: subpicture horizontal origin divided by 128 with the range [0,15]                                  |

|          |         |    |     |      | (3:0) vorgsel: subpicture vertical origin divided by 128 with the range [0,15]                                                                                                         |

|          |         |    |     |      | Reads data token from 16-bit wide memory offset by backward motion vector                                                                                                              |

|          |         |    |     |      | (12:10) memsel: memory select: 0,1,2,3=uses Low Bus;4,5,6,7 uses High Bus                                                                                                              |

| RDV16BMV | 25      | 1  | 2   | VIU  | (9:8) corgsel: component origin register select with the range [0,3] (7:4) horgsel: subpicture horizontal origin divided by 128 with the range [0,15]                                  |

|          |         |    |     |      | (3:0) vorgsel: subpicture vertical origin divided by 128 with the range [0,15]                                                                                                         |

Table 3.5 - KS0143 Video Memory Instructions (Continued)

| Mnemonic   | op-code | no | fmt | Unit | Description                                                                                                                                                                                                                                                                                                                                                              |

|------------|---------|----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRV16 26 1 |         | 1  | 0   | VIU  | Writes data token to 16-bit wide memory (12:10) memsel: memory select 0,1,2,3=uses Low Bus: 4,5,6,7 uses High Bus (9:8) corgsel: component origin register select with the range[0,3] (7:4) horgsel: subpicture horizontal origin divided by 128 with the range [0,15] (3:0) vorgsel: subpicture horizontal origin divided by 128 with the range [0,15]                  |

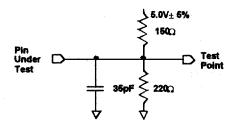

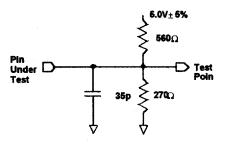

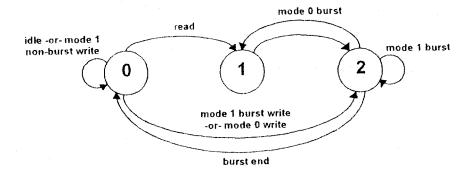

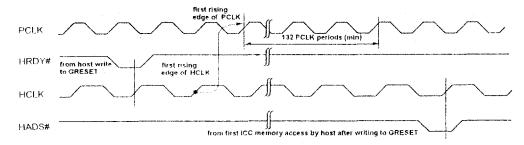

| WRV16.S    | 32      | 1  | 2   | VIU  | Writes data token to 16-bit wide memory and signals whem finished (12:10) memsel: memory origin register select with the range [0,3] (9:8) corgsel: component origin register select with the range [0,3] (7:4) horgsel: subpicture horizontal origin divided by 128 with the range [0,15] (3:0) vorgsel: subpicture vertical origin divide by 128 with the range [0,15] |