# RFX144V12-S and RFX96V12-S MONOFAX® Modems with DigiTalk™ Voice Coder/Decoder and DigiTalk™ Full-Duplex Speakerphone

### INTRODUCTION

The Rockwell RFX144V12-S and RFX96V12-S are MONOFAX® facsimile modems featuring Rockwell's DigiTalk™ speech processing technology for voice compression and full-duplex speakerphone capability. The DigiTalk™ voice coder/decoder compresses voice at 5.7 kbps with near toll quality playback, allowing up to 12 minutes of speech to be stored in 4 Mbits of memory. The DigiTalk™ speakerphone provides full-duplex hands-free voice conversation with both acoustic and line echo cancellation.

These functions are supplied in a two-device set: a modem data pump (MDP) packaged in a 100-pin PQFP and a secondary integrated analog codec (SIA) device packaged in a 28-pin PLCC. The MDP contains the primary integrated analog codec (PIA) and is pin-compatible with the RFXxxxV12 MONOFAX modem. This device set enables the OEM to cost-effectively add a digital answering machine and a full-duplex speakerphone to their fax machine design.

The modem can operate at 14400 (RFX144V12-S), 12000 (RFX144V12-S), 9600, 7200, 4800, 2400, or 300 bps, and can perform HDLC framing according to T.30 at the same rates. A programmable DTMF receiver and three programmable tone detectors are provided.

The 5.7 kbps DigiTalk™ voice coder/decoder allows the host controller to efficiently store and playback digital incoming messages (ICMs) and outgoing messages (OGMs). This low-bit-rate voice coder/decoder, employing Rockwell's proprietary speech compression algorithm provides 12 minutes per 4 Mbit of RAM. Selectable error correction coding allows storage in audio grade RAMs (ARAMs). DTMF and tone detection are available during voice coder/decoder operation to support user selectable features. The modem can be programmed to record messages from either the PIA or SIA. Echo cancellation techniques are employed during playback to allow DTMF and tone detection.

The speakerphone algorithm constantly adjusts its parameters to deliver the best performance during real-time conditions, allowing automatic fallback from full-duplex to pseudo-duplex. Therefore, the host controller can easily set up the speakerphone and change the operation such as mute, automatic gain control (AGC) enable/disable, microphone level, speaker volume, tone transmit, and handset functions.

### **FEATURES**

- · Group 3 facsimile transmission/reception

- CCITT V.17 and V.33 (RFX144V12-S)

- CCITT V.29, V.27 ter, T.30, V.21 Channel 2, T.4

- HDLC framing at all speeds

- Receive dynamic range: 0 dBm to -43 dBm

- Equalization

Automatic adaptive

Fixed and programmable digital compromise

- V.27 ter short train

- · Caller ID reception

- 5.7 kbps DigiTalk™ voice coder/decoder

- 12 minutes of voice storage per 4 Mbit memory

- Near toll quality voice recording and playback of ICMs and OGMs

- Error correction coding allows ARAM use at 5.9 kbps

- DTMF and tone detection

- Pitch synchronized fast and slow playback

- Near-end echo cancellation

- Room monitor

- DigiTalk™ full-duplex speakerphone

- Acoustic echo cancellation

30 dB speech echo return loss enhancement 65 ms echo length

Zero processing delay

- Line echo cancellation

40 dB speech echo return loss enhancement 21 ms echo length

Zero processing delay

- Programmable microphone AGC

- Programmable speaker AGC

- Microphone volume selection and muting

- Speaker volume control and muting

30 dB speaker volume control range in 2 dB steps

- Two DTMF generators and one tone detector

- Auto fallback toward pseudo-duplex operation under poor operating conditions

- Programmable handset echo simulation in handset operation

- Concurrent DTMF, FSK, and tone reception Programmable transmit level

- Programmable dual tone generation

- Programmable tone detection

(Continued)

Data Sheet (Preliminary) Order No. MD115 Rev. 1, November 8, 1994

### FEATURES (CONT'D)

- · Programmable interface memory interrupt

- Programmable ring detector

- 8-bit or 16-bit high quality audio mode transmission/ reception

- Eight general purpose input (GPI) and eight general purpose output (GPO) pins for host assignment

- DTE interface: two alternate ports

- Selectable microprocessor bus (6500 or 8085)

- CCITT V.24 (EIA/TIA-232-E compatible) interface

- TTL and CMOS compatible

- +5V operation

- Power consumption (see Table 10):

- Normal: 620 mW (typical)

- Sleep: 10.8 mW (typical)

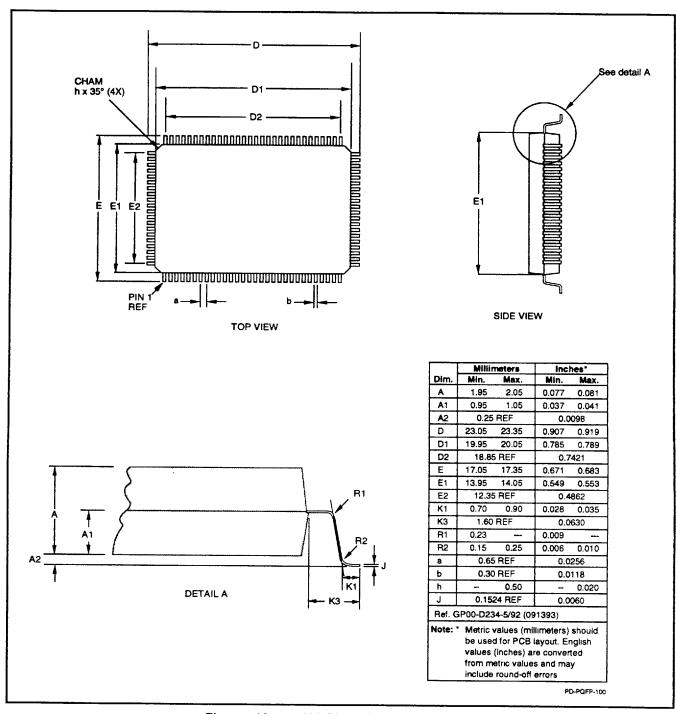

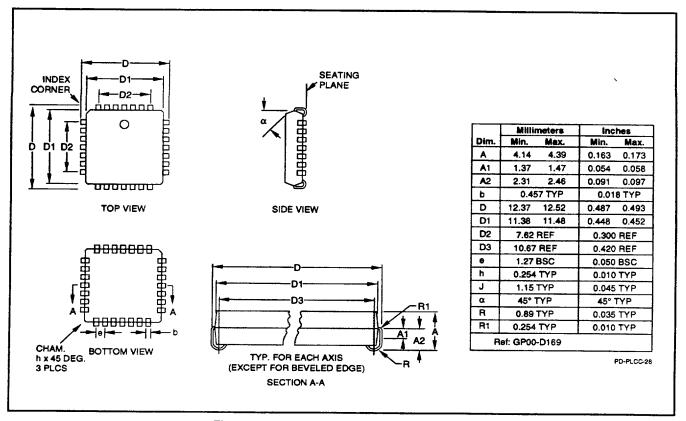

- Packaging

- MDP: 100-pin PQFP (plastic quad flat pack)

- SIA: 28-pin PLCC (plastic leaded chip carrier)

- Software compatible with other MONOFAX modems

MONOFAX is a registered trademark of Rockwell International. DigiTalk is a trademark of Rockwell International.

### TECHNICAL SPECIFICATIONS

### Configurations, Signaling Rates and Data Rates

The selectable modern configurations, along with the corresponding signaling (baud) rates and data rates, are listed in Table 1.

#### Tone Generation

The modern can generate voice-band single or dual tones from 0 Hz to 4800 Hz with a resolution of 0.15 Hz and an accuracy of 0.01%. Tones over 3400 Hz are attenuated. Dual tone generation allows the modem to operate as a programmable DTMF dialer.

### **Data Encoding**

The data encoding conforms to CCITT recommendations V.17 (RFX144V12-S), V.33 (RFX144V12-S), V.29, V.27 ter, V.21 Channel 2, and V.23 receive.

### **Automatic Adaptive Equalizer**

An adaptive equalizer in V.17 (RFX144V12-S), V.33 (RFX144V12-S), V.29 and V.27 ter modes compensates for transmission line amplitude and group delay distortion.

### Fixed Digital Cable Compromise Equalizer

Compromise equalization can improve performance when operating over low quality lines. The modem has a selectable fixed digital compromise cable equalizer in the high speed receive and transmit data paths.

Table 1 Configurations, Signaling Rates, and Data Rates

|                              | Table 1. Comigurations, Signating Rates, and Data Rates |                                     |                           |                        |                 |                         |  |  |  |  |

|------------------------------|---------------------------------------------------------|-------------------------------------|---------------------------|------------------------|-----------------|-------------------------|--|--|--|--|

| Configuration                | Modulation                                              | Carrier<br>Frequency<br>(Hz) ±0.01% | Data Rate<br>(bps) ±0.01% | Baud<br>(Symbols/Sec.) | Bits<br>/Symbol | Constellation<br>Points |  |  |  |  |

| V.17/V.33 14400 <sup>2</sup> | ТСМ                                                     | 1700 or 1800                        | 14400                     | 2400                   | 6               | 128                     |  |  |  |  |

| V.17/V.33 12000 <sup>2</sup> | там                                                     | 1700 or 1800                        | 12000                     | 2400                   | 5               | 64                      |  |  |  |  |

| V.17 9600 <sup>2</sup>       | том                                                     | 1700 or 1800                        | 9600                      | 2400                   | 4               | 32                      |  |  |  |  |

| V.17 7200 <sup>2</sup>       | ТСМ                                                     | 1700 or 1800                        | 7200                      | 2400                   | 3               | 16                      |  |  |  |  |

| V.29 9600                    | QAM                                                     | 1700                                | 9600                      | 2400                   | 4               | 16                      |  |  |  |  |

| V.29 7200                    | QAM                                                     | 1700                                | 7200                      | 2400                   | 3               | 8                       |  |  |  |  |

| V.29 4800                    | QAM                                                     | 1700                                | 4800                      | 2400                   | 2               | 4                       |  |  |  |  |

| V.27 ter 4800                | DPSK                                                    | 1800                                | 4800                      | 1600                   | 3               | 8                       |  |  |  |  |

| V.27 ter 2400                | DPSK                                                    | 1800                                | 2400                      | 1200                   | 2               | 4                       |  |  |  |  |

| V.21 Channel 2 300           | FSK                                                     | 1650, 1850                          | 300                       | 300                    | 1               | -                       |  |  |  |  |

| V.23 receive HDX             | FSK                                                     | 1300, 2100                          | 1200                      | 1200                   | 1               | _                       |  |  |  |  |

| V.23 receive HDX             | FSK                                                     | 1300, 2100                          | 1200                      | 1200                   | 1               | <del>-</del>            |  |  |  |  |

2

#### Notes:

Modulation legend:

QAM: Quadrature Amplitude Modulation

DPSK: FSK:

Differential Phase Shift Keying

TCM:

Frequency Shift Keying Trellis-Coded Modulation

RFX144V12-S only.

### Transmitted Data Spectrum

The transmitted data spectrum is shaped in the baseband by an excess bandwidth finite impulse response filter (FIR) with the following characteristics:

When operating at 2400 baud, the transmitted spectrum is shaped by a square root of 20% raised cosine filter.

When operating at 1600 baud, the transmitted spectrum is shaped by a square root of 50% raised cosine filter.

When operating at 1200 baud, the transmitted spectrum is shaped by a square root of 90% raised cosine filter.

The out-of-band transmitter energy levels in the 4 kHz - 50 kHz frequency range are below --55.0 dBm.

#### Turn-on Sequence

Transmitter tum-on sequence times are shown in Table 2.

#### Turn-off Sequence

Transmitter turn-off sequence times are shown in Table 3.

### Transmit Level

The transmitter output (TXA) level is programmable in the DSP RAM from 0 dBm to -15.0 dBm. The modem adjusts the output level by digitally scaling the output to the transmitter's digital-to-analog converter.

Table 2. Turn-On Sequence Times

|                               | -RTS On to -CTS On                    |                                   |  |  |

|-------------------------------|---------------------------------------|-----------------------------------|--|--|

| Configuration                 | Echo<br>Protector<br>Tone<br>Disabled | Echo<br>Protector<br>Tone Enabled |  |  |

| V.17/V.33                     | 1395 ms                               | 1602 ms                           |  |  |

| V.17 Short Train              | 144 ms                                | 351 ms                            |  |  |

| V.29 Long Train               | 255 ms                                | 443 ms                            |  |  |

| V.27 ter 4800 bps Long Train  | 710 ms                                | 917 ms                            |  |  |

| V.27 ter 4800 bps Short Train | 52 ms                                 | 259 ms                            |  |  |

| V.27 ter 2400 bps Long Train  | 945 ms                                | 1152 ms                           |  |  |

| V.27 ter 2400 bps Short Train | 69 ms                                 | 276 ms                            |  |  |

| V.21 Channel 2 300 bps        | ≤ 14 ms                               | ≤ 14 ms                           |  |  |

Table 3. Turn-Off Sequence Times

| Configuration                 | Data<br>and<br>Scram-<br>bied<br>Ones | No<br>Trans-<br>mitted<br>Energy | Total   |

|-------------------------------|---------------------------------------|----------------------------------|---------|

| V.17/V.33                     | 13.3 ms                               | 20 ms                            | 33.3 ms |

| V.17 Short Train              | 13.3 ms                               | 20 ms                            | 33.3 ms |

| V.29 Long Train               | 5 ms                                  | 20 ms                            | 25 ms   |

| V.27 ter 4800 bps Long Train  | 7 ms                                  | 20 ms                            | 27 ms   |

| V.27 ter 4800 bps Short Train | 7 ms                                  | 20 ms                            | 27 ms   |

| V.27 ter 2400 bps Long Train  | 10 ms                                 | 20 ms                            | 30 ms   |

| V.27 ter 2400 bps Short Train | 10 ms                                 | 20 ms                            | 30 ms   |

| V.21 Channel 2 300 bps        | 7 ms                                  | 0 ms                             | 7 ms    |

#### Notes:

- In parallel data mode, the turn-off sequence may be extended by 8 bit times.

- In HDLC mode, the turn-off sequence may be extended by more than 8 bit times.

MD115

### Scrambler/Descrambler

The modem incorporates a self-synchronizing scrambler/descrambler in accordance with V.17 (RFX144V12-S), V.33 (RFX144V12-S), V.29, or V.27 ter recommendations, depending on the selected configuration.

### Receive Dynamic Range

The receiver satisfies PSTN performance requirements for received line signal levels from 0 dBm to -43 dBm measured at the Receiver Analog Input (RXA) input. An external input buffer and filter must be supplied between RXA and RXIN.

The default values of the programmable Received Line Signal Detector (~RLSD) turn-on and turn-off threshold levels are -43 dBm and -48 dBm, respectively. The -RLSD threshold levels can be programmed over the following range:

Turn on: -10 dBm to -47 dBm Turn off: -10 dBm to -52 dBm

### Receiver Timing

The timing recovery circuit can track a ±0.01% frequency error in the associated transmit timing source.

#### Carrier Recovery

The carrier recovery circuit can track a  $\pm 7$  Hz frequency offset in the received carrier.

#### Clamping

Received Data (RXD) is clamped to a constant mark whenever ~RLSD is off.

#### **Tone Detectors**

The tone detector signal path is separate from the main received signal path thus enabling tone detection to be independent of the receiver status. The tone detectors operate in all modes, except speakerphone where only tone detector one is operational. The filter coefficients of each filter are host programmable in RAM.

#### Voice Mode

The voice mode enables the host to efficiently record and playback voice messages. In this mode, the modem can compress a voice message to 5.7 kbps (5.9 kbps with error correction coding), and decompress a voice message at various pitch synchronized playback speeds. A room monitor feature is also supported.

### **Audio Mode**

3

The audio mode enables the host to transmit and receive 8-bit or 16-bit audio signals. In this mode, the host can access the analog-to-digital (A/D) converter (ADC) and the digital-to-analog (D/A) converter (DAC). Incoming analog audio signals can then be converted to digital format and digital signals can be converted to analog audio output.

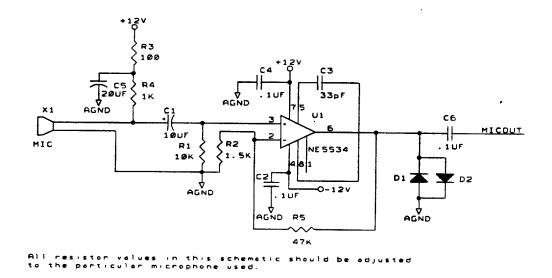

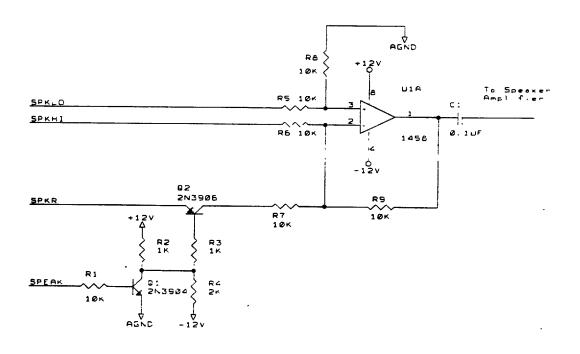

#### Speakerphone Mode

The speakerphone mode provides hands-free full-duplex telephone operation under host control. The host can separately control volume, muting, AGC, and tone generation in microphone and speaker channels. The speakerphone automatically recalculates loop control parameters to maintain duplexity and stability.

### HARDWARE INTERFACE SIGNALS

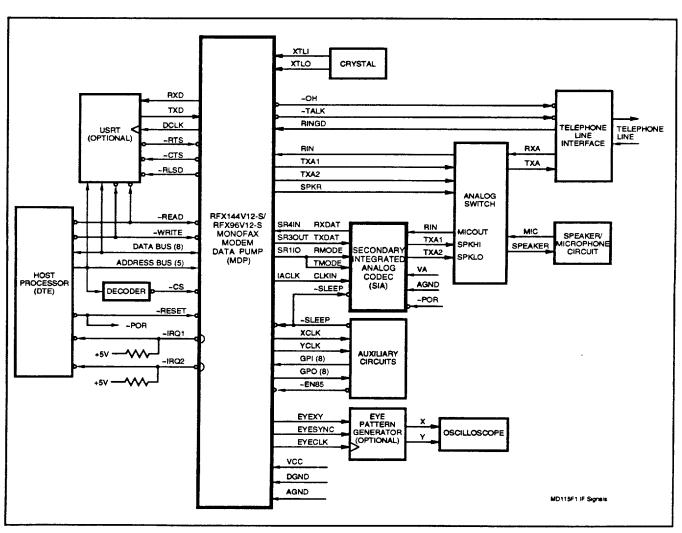

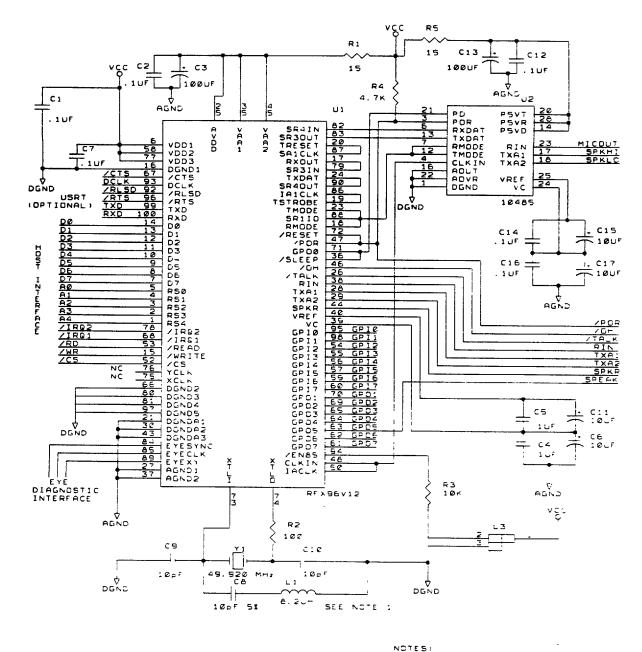

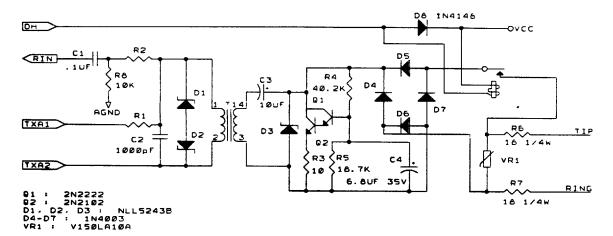

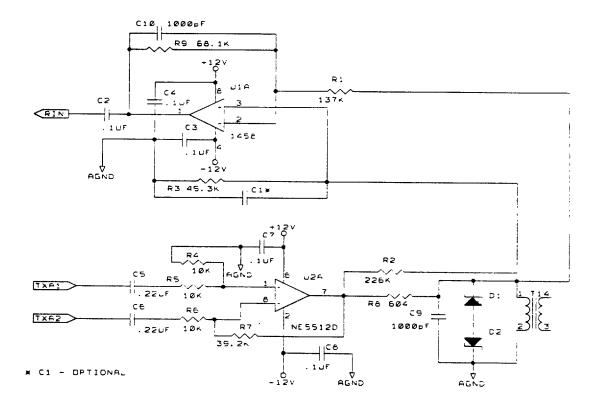

The hardware interface signals are shown in Figure 1.

In Figure 1, any point that is active when exhibiting the relatively more negative voltage of a two-voltage system (e.g., 0 VDC for TTL or -12 VDC for EIA/TIA-232-E) is called active low and is represented by a small circle at the signal point. Active low signals are indicated by a tilde (~), e.g., ~RESET. Edge-triggered clocks are indicated by a small triangle (e.g., TDCLK). Open-collector (open-source or open-drain) outputs are denoted by a small half circle (e.g., signal ~IRQ1).

A clock intended to activate logic on its rising edge (low-to-high transition) is called active low, while a clock intended to activate logic on its falling edge (high-to-low transition) is called active high. When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

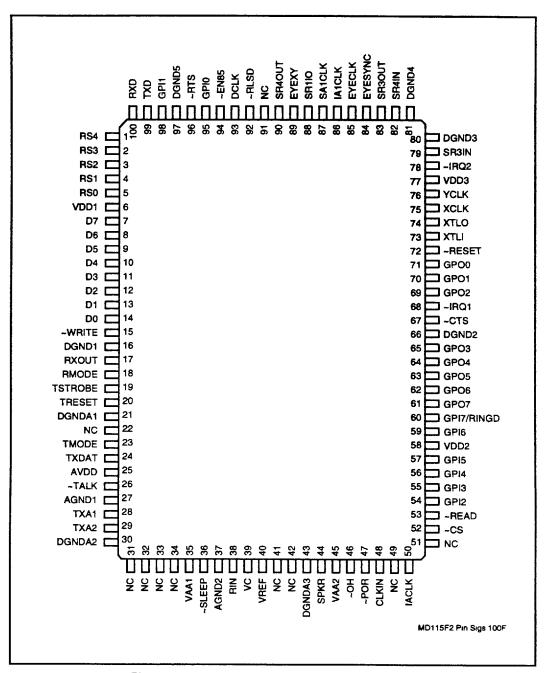

The MDP pin assignments are shown in Figure 2 and hardware interface signals are listed by pin number in Table 4.

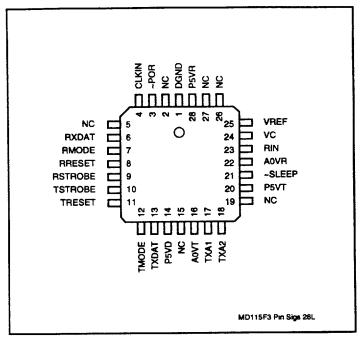

The SIA pin assignments are shown in Figure 3 and hardware interface signals are listed by pin number in Table 5.

The MDP hardware interface signals are defined in Table 6.

The SIA hardware interface signals are defined in Table 7.

Digital signal interface characteristics are defined in Table 8.

Analog signal interface characteristics are defined in Table 9.

Power consumption is listed in Table 10.

Absolute maximum ratings are specified in Table 11.

Figure 1. Modem Functional Interconnect Diagram

Figure 2. MDP Pin Signals - 100-Pin PQFP

Table 4. MDP Pin Signals - 100-Pin PQFP

| Pin | Signal Label | 1/0        | Interface                            | Pin | Signal Label | 1/0   | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------------|------------|--------------------------------------|-----|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |              | Туре       |                                      | 1   |              | Type  | interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1   | RS4          | IA         | Host Parallel Interface              | 51  | NC           | - 775 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | RS3          | М          | Host Parallel Interface              | 52  | -cs          | I A   | Host Parallel Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3   | RS2          | И          | Host Parallel Interface              | 53  | -READ        | Ä     | Host Parallel Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4   | RS1          | А          | Host Parallel Interface              | 54  | GPI2         | Ä     | General Purpose Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | RS0          | и          | Host Parallel Interface              | 55  | GPI3         | Ä     | General Purpose Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | VDD1         | PWR        | vcc                                  | 56  | GPI4         | Ä     | General Purpose Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7   | D7           | IA/OB      | Host Parallel Interface              | 57  | GPI5         | IA    | General Purpose Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8   | D6           | IA/OB      | Host Parallel Interface              | 58  | VDD2         | PWR   | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9   | D5           | WOB        | Host Parallel Interface              | 59  | GPI6         | А     | General Purpose Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10  | D4           | IA/OB      | Host Parallel Interface              | 60  | GPI7/RINGD   | A     | General Purpose Input/Line Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11  | D3           | IA/OB      | Host Parallel Interface              | 61  | GPO7         | ОВ    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12  | D2           | IA/OB      | Host Parallel Interface              | 62  | GPO6         | ОВ    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13  | D1           | IA/OB      | Host Parallel Interface              | 63  | GPO5         | OB    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14  | D0           | IA/OB      | Host Parallel Interface              | 64  | GPO4         | OB    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | -WRITE       | IA         | Host Parallel Interface              | 65  | GPO3         | OB    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16  | DGND1        | GND        | DGND                                 | 66  | DGND2        | GND   | DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17  | RXOUT        | M!         | MDP: SR3IN (79)                      | 67  | -CTS         | OA    | DTE Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 18  | RMODE        | MI         | MDP: TMODE (23) & SR1IO (88);        | 68  | ~IRQ1        | oc oc | Host Parallel Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |              |            | SIA: RMODE (7)                       |     |              |       | The state of the s |

| 19  | TSTROBE      | MI         | MDP: IA1CLK (86)                     | 69  | GPO2         | ОВ    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20  | TRESET       | M!         | MDP: SA1CLK (87)                     | 70  | GPO1         | ОВ    | General Purpose Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21  | DGNDA1       | GND        | AGND                                 | 71  | GPO0         | ОВ    | MDP: ~SLEEP (36)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22  | NC           |            |                                      | 72  | ~RESET       | OA    | Reset Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 23  | TMODE        | MI         | MDP: RMODE (18)                      | 73  | XTLI         | ı     | Crystal/Clock Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24  | TXDAT        | MI         | MDP: SR4OUT (90)                     | 74  | XTLO         | 0     | Crystal/Clock Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25  | AVDD         | PWR        | VCC through power decoupling filter  | 75  | XCLK         | 00    | Diagnostic Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |