# FGA Series ASPECT™ ECL Gate Arrays

# **General Description**

The FGA Series is a new generation of ECL gate arrays based on National's ASPECT process. These advanced ECL gate arrays, ranging from 200 to over 30,000 equivalent gates, offer typical internal propagation delays of 150 ps and consume thirty percent less power than conventional ECL arrays. (Refer to Table I.)

With system clock frequencies up to 1.2 GHz, the speed domain of Gallium Arsenide, FGA Series gate arrays are especially well-suited for such high-performance applications as mainframe and supermini computers, fiber-optic communications, and many military and aerospace systems. With only internal cells and I/O cells, FGA Series arrays are easy to use. Designers can implement logic using two-level or three-level series gating circuit structures within an array, with no complex signal mixing rules required. An extensive macro library, common to all FGA Series arrays, contains more than eighty SSI/MSI logic functions and 36 supporting I/O macros. In addition, internal macros may be grouped to form re-usable "soft macros" with even greater functional complexity.

All FGA Series gate arrays feature CAD-programmable speed/power options that allow the designer to maximize performance by individually assigning the switching speed and output drive currents for each internal macro. The speed/power feature provides maximum ECL speed where needed, yet allows overall chip power to remain at air-coolable levels. On-chip termination to -2V for the internal output emitter followers further reduces power consumption.

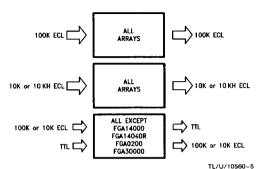

All FGA Series products interface with ECL 100K, ECL 10K and ECL 10KH components, and, except for the FGA200, FGA14000, FGA14040R, and FGA30000, are fully FAST\*/TTL compatible. The TTL interface eliminates requirements for separate off-chip signal converters in mixed logic level systems, thereby resulting in reduced board space and cost, as well as avoiding the performance and reliability penalties associated with off-chip signal converters.

In addition to providing superior speed/power performance with high density, the ASPECT process is scalable to submicron dimensions. FGA Series arrays are designed to accommodate multiple ASPECT process generations to allow designs implemented today to migrate to tomorrow's arrays based on future ASPECT processes.

#### **Features**

- New generation ECL gate arrays with complexity to 30,000 equivalent logic gates

- Manufactured with 1.5-micron ASPECT process

- CAD-programmable speed/power options

- 150 ps typical internal delay

- Flexible array architecture with only two cell types: Internal cells and I/O cells

- F100K, 10K or 10KH ECL-compatible I/Os

- Mixable ECL/TTL I/Os

- Allows large number of simultaneously switching outputs

FIGURE 1. FGA Series Gate Array

TL/U/10560-1

Note 1: FGA150, 600, 1300, 4000 and 15000 offer mixable ECL/TTL I/Os.

FAST® is a registered trademark of National Semiconductor Corporation. ASPECT™ is a trademark of National Semiconductor Corporation.

© 1989 National Semiconductor Corporation

TL/U/10560

RRD-B20M129/Printed in U. S. A

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature (TSTG) -65°C to +150°C Maximum Junction Temp. (T<sub>1</sub>) + 150°C

Case Temp. under Bias (Tc) -55°C to + 125°C

Vec Pin Potential to

V<sub>CC</sub> Pins (V<sub>MAX</sub>) -7.0V to +0.5VInput Voltage (DC) (Vi)  $V_{EE}$  to  $(V_{CC} + 0.5V)$ Output Current (DC Output HIGH) (Io) -50 mA

Operating Range ECL (VFF) -5.7V to -4.2V Operating Range TTL (VTTL) 4.5V to 5.5V

Note: Stresses greater than those listed in "Absolute Maximum Ratinas" may cause permanent damage to the device. This is a stress rating only: operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC Specifications

All FGA Series gate arrays operate from a standard ECL power supply and an additional -2V supply (VTT) which terminates internal cell emitter followers to reduce power consumption. With F100K inputs and outputs, the FGA series is designed to operate from a standard 100K power supply, although a standard 10K power supply may be used instead. When used for mixed ECL/TTL operations, an additional power supply is required. The following table provides the power requirements for each allowable interface configuration

## **Power Supply Requirements**

| 1/0        | V <sub>CC</sub> (V) | V <sub>TT</sub> (V)(Note 2) | V <sub>EE</sub> (V) | V <sub>TTL</sub> (V) | Arrays              |

|------------|---------------------|-----------------------------|---------------------|----------------------|---------------------|

| F100K      | GND                 | −1.9 to −2.1                | −4.2 to −5.7        | _                    | All                 |

| F10K       | GND                 | −1.9 to −2.1                | -4.7 to -5.7        | _                    | All                 |

| F100K/TTL  | GND                 | −1.9 to −2.1                | -4.2 to -5.7        | 4.5 to 5.5           | Except FGA200,      |

| F10K/TTL   | GND                 | -1.9 to -2.1                | −4.7 to −5.7        | 4.5 to 5.5           | FGA14000, FGA14040R |

| Pseudo TTL | V <sub>TTL</sub>    | (V <sub>TTL</sub> −2) ±0.1  | GND                 | 4.75 to 5.25         | and FGA 30000       |

#### F100K ECL DC Characteristics

$V_{EE} = -4.5V$ ,  $V_{TT} = -2V$ ,  $V_{CC} = V_{CCA} = GND$ ,  $T_{J} = -10^{\circ}C$  to  $+125^{\circ}C$  (Note 3)

| Symbol                   | Parameter           | Con                                     | Min                      | Тур    | Max    | Units  |    |

|--------------------------|---------------------|-----------------------------------------|--------------------------|--------|--------|--------|----|

| V <sub>OH</sub>          | Output HIGH Voltage | V <sub>IN</sub> = V <sub>IH (max)</sub> | Loaded with 50Ω to ~2.0V | - 1035 | -955   | -870   | mV |

| V <sub>OL</sub>          | Output LOW Voltage  | or V <sub>IL (min)</sub>                | 2.0V                     | -1830  | - 1705 | - 1605 | m∨ |

| V <sub>IH</sub> (Note 5) | Input HIGH Voltage  | Guaranteed HIGH Signal for All Inputs   |                          | -1125  |        | -880   | m∨ |

| V <sub>IL</sub> (Note 5) | Input LOW Voltage   | Guaranteed LOW Signal for All Inputs    |                          | -1810  |        | - 1605 | mV |

Note 1: Unless otherwise specified contractually.

Note 2: For internal cell output emitter follower termination to save power.

Note 3: Fouilibrium temperature

Note 4: Conditions for testing are chosen to guarantee operation under worst case conditions.

Note 5: Forcing one input at a time. Apply VIH (max) or VIL (min) to all other inputs.

# F10K ECL DC Characteristics $v_{EE} = -5.2 \text{V}, V_{TT} = -2 \text{V}, V_{CC} = V_{CCA} = \text{GND}$

| Parameter                     | Conditions                            |              | Junction Temperature |        |        |       |  |

|-------------------------------|---------------------------------------|--------------|----------------------|--------|--------|-------|--|

|                               |                                       | 0°C          | 25°C                 | 65°C   | 125°C  | Units |  |

| V <sub>OH</sub> Max           |                                       | -897         | -862                 | -810   | -732   | m∨    |  |

| V <sub>OH</sub> Min           | V <sub>IH</sub> = V <sub>IH</sub> Max | -1112        | 1077                 | - 1025 | -947   | mV    |  |

| V <sub>OL</sub> Max           | V <sub>IL</sub> ≕ V <sub>IL</sub> Min | <b> 1656</b> | - 1644               | - 1620 | 1584   | mV    |  |

| V <sub>OL</sub> Min           |                                       | -1920        | - 1920               | -1920  | -1920  | mV    |  |

| V <sub>IH</sub> Max (Note 1)  |                                       | -888         | -858                 | -810   | -738   | mV    |  |

| V <sub>IL</sub> Min (Note 1)  |                                       | - 1920       | -1920                | -1920  | - 1920 | mV    |  |

| V <sub>IHA</sub> Min (Note 1) |                                       | - 1209       | -1172                | -1125  | - 1045 | mV    |  |

| V <sub>ILA</sub> Max (Note 1) |                                       | 1604         | - 1567               | - 1520 | - 1440 | mV    |  |

# TTL DC Characteristics over Operating Temperature Range $v_{CC}=5V~\pm5\%,\,T_{J}=-10^{\circ}C~to~+125^{\circ}C$

| Symbol           | Parameter                                 | Conditio                                    | Conditions                     |      | Тур  | Max  | Units |

|------------------|-------------------------------------------|---------------------------------------------|--------------------------------|------|------|------|-------|

| V <sub>OH</sub>  | Output HIGH Voltage                       | $I_{OH} = -400 \mu A$                       | V <sub>CC</sub> = 4.75V        | 2.7  | 3.0  | _    | v     |

| V <sub>OL</sub>  | Output LOW Voltage                        | I <sub>OH</sub> = 8.0 mA/20 mA              | $V_{CC} = 4.75V$               | _    | 0.25 | 0.5  | V     |

| V <sub>IH</sub>  | Input HIGH Voltage                        |                                             |                                | 2.0  |      |      | ٧     |

| V <sub>IL</sub>  | Input LOW Voltage                         |                                             |                                |      | _    | 0.80 | V     |

| I <sub>IH</sub>  | Input HIGH Current (Note 2)               | $V_{CC} = 5.25V, V_{IN} = 2.4V$             |                                | _    | _    | 40   | μА    |

| I <sub>IL</sub>  | Input LOW Current (Note 2)                | $V_{CC} = 5.25V, V_{IN} = 0.4$              | 4V                             | _    |      | -400 | μА    |

| l <sub>OZH</sub> | Output OFF Current HIGH                   | V <sub>CC</sub> = 5.25V, V <sub>OUT</sub> = | 2.4V                           | _    | _    | 40   | μΑ    |

| lozL             | Output OFF Current LOW                    | V <sub>CC</sub> = 5.25V, V <sub>OUT</sub> = | 0.4V                           | _    |      | -40  | μΑ    |

| los              | Output Off Short Circuit Current (Note 3) | 8/20 mA Driver                              | $V_{CC} = 5.25V$ $V_{OUT} = 0$ | - 15 | _    | -130 | mA    |

Note 1: Forcing one input at a time. Apply VIH (max) or VIL (min) to all other inputs.

Note 2: Current per input.

Note 3: Not more than one output should be shorted at a time. Output should not be shorted for more than one second.

# **FGA Series ECL Gate Array Family**

TABLE I. The FGA Gate Array Series

| Description                 | FGA0150                              | FGA0200                              | FGA0600         | FGA1300                     | FGA4000                      | FGA14000 | FGA14040R          | FGA15000 | FGA30000        |

|-----------------------------|--------------------------------------|--------------------------------------|-----------------|-----------------------------|------------------------------|----------|--------------------|----------|-----------------|

| Equivalent<br>Gates         | 269                                  | 269                                  | 792             | 1642                        | 4704                         | 16709    | 7853 + 4.6K<br>RAM | 16644    | 28486           |

| Internal<br>Cells (MAU)     | 75                                   | 75                                   | 240             | 528                         | 1600                         | 5904     | 2624 Plus<br>RAM   | 5920     | 10266           |

| Internal Gate<br>Delay      | 150PS                                | 150PS                                | 150PS           | 150PS                       | 150PS                        | 150PS    | 150PS              | 150PS    | 150PS           |

| Speed/Power<br>Options      | Yes                                  | Yes                                  | Yes             | Yes                         | Yes                          | Yes      | Yes                | Yes      | Yes             |

| 100K/10K/10KH<br>Compatible | Yes                                  | Yes                                  | Yes             | Yes                         | Yes                          | Yes      | Yes                | Yes      | Yes             |

| ECL/TTL<br>Mixed I/O        | 22                                   | 0                                    | 36              | 72                          | 128                          | 0        | 0                  | 220      | 0               |

| ECL Only I/O                | 0                                    | 22                                   | 12              | 0                           | 0                            | 256      | 256                | 0        | 256             |

| Power/Ground                | 6                                    | 6                                    | 12              | 40                          | 48                           | 56       | 56                 | 72       | -<br>5 <b>6</b> |

| Typical<br>Power (W)        | 0.5-1.0                              | 0.5-1.0                              | 0.5-1.5         | 1-3                         | 3-6                          | 10-20    | 10-20              | 10-20    | 15-30           |

| Standard<br>Packages        | 16, 24<br>Metal Flat<br>28 PLCC/LDCC | 16, 24<br>Metal Flat<br>28 PLCC/LDCC | 44LDCC<br>75PGA | 109PGA<br>116LDCC<br>75PGA* | 173PGA<br>172LDCC<br>99PGA** | 323PGA   | 323PGA             | 303PGA   | 323PGA          |

| Available                   | Now                                  | Now                                  | Now             | Now                         | Now                          | Now      | Now                | Now      | 1Q90            |

<sup>\*</sup>Maximum of 48 I/O

#### **ASPECT Process**

FGA Series arrays use a National proprietary process called ASPECT which uses conservative 1.5-micron design rules to achieve VLSI density and 150 ps typical internal gate delays at thirty percent of conventional ECL power consumption levels.

ASPECT is the first bipolar process to use polysilicon for emitter and base structures. Polysilicide serves as a source of impurities for both the emitter and the base. This permits the fabrication of extremely shallow (500Å below the surface) emitters and narrow base regions. The combination of shallow emitters and base leads to transistors with a very high switching speed. ASPECT also uses polysilicon resistors.

Such resistors exhibit low junction capacitance, making them ideal passive elements for high-speed logic circuits.

An important feature is the self-aligning process used in ASPECT gate arrays. This insensitivity to misalignment makes ASPECT a high-yield process and enables the move to smaller geometries with less difficulty than conventional bipolar processes.

# **Array Organization**

Electrical components (transistors, resistors, diodes and capacitors) are organized into repeating structures called cells, Macros, which are the basic building blocks of gate array logic design, are built by interconnecting the components in one or more cells.

<sup>\*\*</sup>Maximum of 64 I/O

# Array Organization (Continued)

The FGA Series employs only two cell types: internal cells and I/O cells. The internal cells are the workhorses of the array, where most of the circuit logic is implemented. All signals going to or coming from the outside world must exit or enter the array through an I/O cell. Since all signal level conversions are performed in the I/O cells, no signal mixing

takes place within the array, thus simplifying the design effort. Cell types and their functions are described in greater detail in the following paragraphs. The bonding pads are located around the periphery of the array. In addition to performing I/O functions, some of the

pads are reserved for power and ground busses. Biasing occurs in dedicated routing channels and is optimally performed automatically by placement and routing CAD soft-All FGA Series arrays employ three-layer metalization for signals and bussing. The first metal layer connects components within macros and makes horizontal connections between macros. Layer two is primarily for vertical connec-

tions between macros, while layer three contains most of the power bussing. Future versions of the ASPECT process may include four metal lavers. In that case, first-layer metal would not be needed to connect macros, thus eliminating

Internal Cell and Logic Complexity The basic internal cell in an FGA Series array is called a

routing channels and increasing gate counts for a given die

"minimum addressable unit", or MAU. It is the smallest portion of the chip that a CAD system can access for placing or The number of elements in this minimum cell is actually

smaller than on any competing array. In fact, this small, compact cell structure, said to have a fine granularity, increases efficiency. In general, the larger the cell, the greater the likelihood that some cell resources go unused, thereby decreasing efficiency.

Single-level, two-level, and three-level series gated ECL structures are used in FGA Series arrays to implement various logic functions. Series gating allows complex logic functions to be implemented with fewer gates while maintaining optimum performance. Additional logic complexity at no cost in cell utilization may be gained in internal cells by connecting the outputs together (emitter dotting) to form wired-OR functions Speed/power options can be used to assign the current

settings in each internal cell macro. This feature allows the designer to maximize speed when needed, yet minimize the power consumption. The termination of internal output emitter followers to a -2V internal bus further reduces power Typically, internal cell utilization of eighty-five percent is considered optimum. Designs can be completed with up to

one-hundred percent utilization; however placement and routing at this level sometimes requires special interactive lavout.

The FGA Macro Library contains a number of physical macros with MSI-level complexity. The final portion of this data sheet includes a representative sample of macros included in the FGA Series Macro Library. Full documentation for all macros, including specifications, can be found in the FGA Series Macro Library Reference Manual

# I/O and Interface Capabilities I/O cells in the FGA Series are capable of performing input,

tions. The array's I/O organization is flexible, with each signal pad supported by a dedicated I/O cell. An incoming signal can enter the internal array through any I/O cell and, after completing the logic implementation, can then exit the array through any I/O cell without restriction. The flexible functionality of individual I/O cells can be espe-

output, transceiver logic and ECL/TTL conversion func-

cially useful in system applications requiring latched inputs and outputs. The ability of an FGA Series I/O cell to be

# I/O and Interface Capabilities

(Continued)

configured as a latch saves having to use an internal cell for this function. In addition, although most ECL devices drive  $50\Omega$  loads. I/Os can be paired to drive  $25\Omega$  loads.

Each I/O cell offers a choice of signal termination options. For relatively short signal paths, designers may build series-terminated outputs, simplifying designs in systems where placing termination resistors on the board is not practical. To minimize noise, internal pull-down resistors are provided to keep unused inputs from floating.

Either F100K, 10K, or 10KH interface capability is available on all FGA Series arrays. All input thresholds and logic levels must uniformly belong to the same ECL family. Likewise, the output interface must be the same as that used for input. With the exception of the FGA0200, FGA14000, FGA14000, FGA14000, each I/O can also be a mixable ECL/TTL I/O. This means that every I/O can be independently configured as either ECL or TTL. The TTL I/O is capable of producing totem-pole, open-collector, or three-state output levels. Figure 2 illustrates the acceptable interface options for FGA Series arrays.

FIGURE 2. Interface Capabilities

#### Embedded RAM

The embedded RAM block is a self-timing memory device with the capabilities of supporting various memory configurations, different bit select patterns, output power options, and different clock systems. The embedded RAM block contains 576 bits, and is organized as 64 words by 9 bits. There are 8 RAM blocks in the FGA14040R with the total of 4608 bits. Each embedded RAM block has its own built-in decoder and control circuit, thus improving system performance and reliability while saving board space. The embedded RAM has three modes of operation, Normal mode. Scan mode and Test mode. At high power operation, the typical access time is 3.75 ns and the worst case access time is 5 ns. Two output drive options, 0.6 mA and 1.2 mA, are available to support the driving capabilities of the embedded RAM. Note that the memory is called self-timed memory device because it generates and shapes its own write strobe internally. This pulse is generated off of the rising edge of the clock which is applied to the embedded RAM.

### **Speed/Power Options**

Speed/power options are a feature of all FGA Series gate arrays. This feature allows the designer to maximize speed where needed, yet minimize overall chip power consumption.

Two sets of macros are available for each logic function in the FGA arrays, the standard macros and the double macros (see Table IV). The double macros use two times as much current as standard macros, and are designed for use in the critical circuitry. These two macro types can be used interchangeably within the same chip.

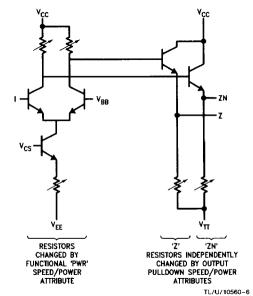

Essentially, speed/power options are used to assign one or two current values (high = 0.3 mA, low = 0.15 mA) to the current source which controls switching speed; and one of two current values (high = 0.6 mA, low = 0.3 mA) to the true and complement outputs for output drive currents. The latter setting permits zero power consumption for unused outputs. Figure 3 illustrates circuit options for each of the three settings.

FIGURE 3. Speed/Power Options

The speed/power options are assigned during schematic capture. Default values for each setting may be specified during schematic capture as well. Designers may use the speed/power options to fine tune the design after placement and routing simply by returning to schematic capture and reassigning values without having to repeat placement and routing.

The examples in Table III illustrate how speed/power options can affect propagation delay vs. power consumption at the macro level. Additional speed/power tradeoffs are listed in "Macro Performance Examples" later in this data sheet.

# Speed/Power Options (Continued)

TABLE III. Macro Speed/Power Tradeoffs

| Mac             | ro   | Speed (ps) | Power (mW) |

|-----------------|------|------------|------------|

| 2-Input<br>NOR  | High | 235        | 2.5        |

| ORN02 Low       |      | 410        | 1.2        |

| D Flip-<br>Flop | High | 415        | 7.5        |

| DFI01           | Low  | 680        | 5.6        |

TABLE IV. Current Setting of Speed/Power Options

| Current        | Standard   | Macro (S) | Double M   | acros (D) |

|----------------|------------|-----------|------------|-----------|

| μ <b>Α</b>     | High Speed | Low Power | High Speed | Low Power |

| Source Current | 300        | 150       | 600        | 300       |

| OEF Current    | 600        | 300       | 600        | 300       |

# **AC Specifications**

FGA Series macro propagation delays are specified as MIN, TYP, and MAX values, with variations due to process, power supply and temperature, as shown in the "AC Performance

Variations" table.

# **Macro Performance Examples**

The following pages contain performance specifications for some important internal cell macros. Complete information, including design rules and application notes, can be found in the FGA Series Design Manual and FGA Series Macro Library.

#### **AC Performance Variations**

| Variation   | Derating from Ty                | Derating from Typical (%) (Note 2) |  |  |  |  |

|-------------|---------------------------------|------------------------------------|--|--|--|--|

| Туре        | Type Minimum (Note 1) Maximum ( |                                    |  |  |  |  |

| Temperature | -10                             | 15                                 |  |  |  |  |

| Voltage     | ~0                              | ~0                                 |  |  |  |  |

| Process     | -20                             | 20                                 |  |  |  |  |

| Total       | -30%                            | 35%                                |  |  |  |  |

Note 1: Minimum: T<sub>J</sub> = 0°C, V<sub>EE</sub> = -4.8V, Best Case Process

Note 2: Typical:  $T_J = 25^{\circ}C$ ,  $V_{EE} = -4.5V$ , Normal Process

Note 3: Maximum: T<sub>J</sub> = 125°C, V<sub>EE</sub> = -4.2V, Worst Case Process

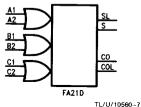

# FA21D One Bit Full Adder with Gates Inputs

, ,

#### Propagation Delay (units in ps)

| From   | То     | ,   | High Pow | er  | ı   | Low Pow | er  |

|--------|--------|-----|----------|-----|-----|---------|-----|

| Inputs | Output | Min | Тур      | Max | Min | Тур     | Max |

| A1, A2 | s 🖍    | 330 | 410      | 550 | 420 | 530     | 710 |

| A1, A2 | s 🔨    | 380 | 470      | 640 | 420 | 530     | 710 |

| B1, B2 | s _/   | 380 | 470      | 640 | 470 | 580     | 790 |

| B1, B2 | s ~    | 450 | 560      | 760 | 490 | 620     | 830 |

| C1, C2 | s _    | 200 | 250      | 340 | 200 | 250     | 340 |

| C1, C2 | s 🔪    | 240 | 300      | 400 | 280 | 350     | 480 |

| A1, A2 | C0 _   | 190 | 230      | 310 | 190 | 240     | 330 |

| A1, A2 | C0 ~_  | 190 | 240      | 330 | 290 | 360     | 490 |

| B1, B2 | C0 _   | 240 | 300      | 400 | 260 | 330     | 450 |

| B1, B2 | C0 ~_  | 260 | 330      | 450 | 380 | 470     | 640 |

| C1, C2 | C0 _   | 240 | 300      | 400 | 260 | 330     | 450 |

| C1, C2 | C0 ~   | 260 | 330      | 450 | 380 | 470     | 640 |

# Macro Performance Examples (Continued)

#### Current in Base Macro

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| IEE (mA)  |      | -    |      |

| HIGH      | 1.36 | 1.80 | 2.26 |

| LOW       | 0.92 | 1.20 | 1.52 |

| ITT (mA)  |      |      |      |

| HIGH      | 0.21 | 0.30 | 0.39 |

| LOW       | 0.21 | 0.30 | 0.39 |

#### **Current in Macro Outputs**

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| ITT (mA)  |      |      |      |

| HIGH      | 0.42 | 0.60 | 0.78 |

| LOW       | 0.21 | 0.30 | 0.39 |

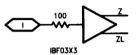

#### IBF03X2(3) Input Buffer

TL/U/10560-8

#### Propagation Delay (units in ps)

| From<br>Input | To<br>Outputs | Min | Тур | Max |

|---------------|---------------|-----|-----|-----|

| 1             | Z, ZL 🗸       | 220 | 280 | 380 |

| 1             | Z, ZL \       | 220 | 280 | 380 |

#### Current in Base Macro

| Min      | Тур  | Max  |

|----------|------|------|

| IEE (mA) |      |      |

| 0.60     | 0.80 | 1.0  |

| ITT (mA) |      |      |

| 0.84     | 1.20 | 1.56 |

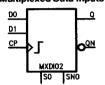

#### MXDI02—D Flip Flop with Multiplexed Data Inputs

TL/U/10560-9

#### Propagation Delay (units in ps)

| From  | То     | ŀ   | ligh Pow | er  | ı   | ow Pow | er  |

|-------|--------|-----|----------|-----|-----|--------|-----|

| input | Output | Min | Тур      | Max | Min | Тур    | Max |

| СР    | a _    | 340 | 420      | 570 | 530 | 660    | 890 |

| CP    | Q ~    | 300 | 380      | 510 | 530 | 660    | 890 |

| CP    | QN _   | 340 | 430      | 580 | 540 | 670    | 910 |

| CP    | QN 🔨   | 310 | 390      | 530 | 540 | 680    | 920 |

#### Current in Base Macro

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| IEE (mA)  |      |      |      |

| HIGH      | 0.92 | 1.20 | 1.52 |

| LOW       | 0.68 | 0.90 | 1.14 |

| ITT (mA)  |      |      |      |

| HIGH      | 0.84 | 1.20 | 1.56 |

| LOW       | 0.84 | 1.20 | 1.56 |

#### **Current in Macro Outputs**

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| ITT (mA)  |      |      |      |

| HIGH      | 0.42 | 0.60 | 0.78 |

| LOW       | 0.21 | 0.30 | 0.39 |

# **Macro Performance Examples (Continued)**

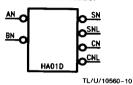

#### HA01D—Half Adder

#### Propagation Delay (units in ps)

|        |        | riopaya | uon bea | ı <b>y</b> (units in | ps)       |     |     |

|--------|--------|---------|---------|----------------------|-----------|-----|-----|

| From   |        |         | g       |                      | Low Power |     |     |

| Inputs | Output | Min     | Тур     | Max                  | Min       | Тур | Max |

| AN     | SN 🖍   | 160     | 200     | 270                  | 160       | 200 | 270 |

| AN     | SN ╲   | 170     | 210     | 280                  | 200       | 250 | 340 |

| AN     | CN 🗸   | 150     | 190     | 250                  | 140       | 180 | 240 |

| AN     | CN 🔨   | 150     | 190     | 250                  | 190       | 230 | 310 |

| BN     | SN 🗸   | 200     | 250     | 340                  | 190       | 240 | 330 |

| BN     | SN 🔍   | 230     | 290     | 390                  | 270       | 340 | 460 |

| BN     | CN _   | 200     | 250     | 340                  | 200       | 250 | 340 |

| BN     | CN 🔨   | 220     | 280     | 370                  | 270       | 340 | 460 |

#### **Current in Base Macro**

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| IEE (mA)  |      |      |      |

| HIGH      | 0.68 | 0.90 | 1.13 |

| LOW       | 0.46 | 0.60 | 0.76 |

#### **Current in Macro Outputs**

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| ITT (mA)  |      |      |      |

| HIGH      | 0.42 | 0.60 | 0.78 |

| LOW       | 0.21 | 0.30 | 0.39 |

#### 0R05D-5 Input OR Gate

## Propagation Delay (units in ps)

| From  | То      | High Power |     | 1   | ow Pow | er  |     |

|-------|---------|------------|-----|-----|--------|-----|-----|

| Input | Outputs | Min        | Тур | Max | Min    | Тур | Max |

| Α     | Z, ZL 🖍 | 160        | 200 | 270 | 180    | 230 | 310 |

| Α     | Z, ZL 🔪 | 160        | 200 | 270 | 200    | 250 | 340 |

#### Current in Base Macro

### IEE (mA)

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| HIGH      | 0.45 | 0.60 | 0.75 |

| LOW       | 0.23 | 0.30 | 0.38 |

# Current in Macro Outputs

ITT (mA) for each macro output used:

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| HIGH      | 0.42 | 0.60 | 0.78 |

| LOW       | 0.21 | 0.30 | 0.39 |

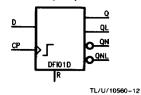

#### DFI01D-D Flip Flop with Reset

#### Propagation Delay (units in ps)

|         |        | opuga |          | y (unito in | P3) |        |     |

|---------|--------|-------|----------|-------------|-----|--------|-----|

| From    | То     | ŀ     | ligh Pow | er          | ı   | ow Pow | er  |

| Inputs  | Output | Min   | Тур      | Max         | Min | Тур    | Max |

| CP      | Q ~    | 340   | 420      | 570         | 500 | 620    | 840 |

| CP      | Q ~    | 350   | 430      | 580         | 380 | 480    | 650 |

| CP      | QN 🗸   | 310   | 390      | 530         | 400 | 500    | 680 |

| CP      | QN 🔨   | 340   | 430      | 580         | 400 | 490    | 670 |

| CP LOW  |        |       |          |             |     |        |     |

| R       | a ~    | 300   | 380      | 510         | 550 | 680    | 920 |

| R       | QN 🗸   | 350   | 430      | 590         | 490 | 610    | 820 |

| CP HIGH |        |       |          |             | •   |        |     |

| R       | a      | 370   | 460      | 620         | 560 | 710    | 950 |

| R       | QN 🗸   | 370   | 460      | 630         | 520 | 650    | 880 |

# Macro Performance Examples (Continued) Current in Base Macro

| Power ATT | Min  | Тур  | Max  |  |  |  |  |

|-----------|------|------|------|--|--|--|--|

| IEE (mA)  |      |      |      |  |  |  |  |

| HIGH      | 1.13 | 1.50 | 1.88 |  |  |  |  |

| LOW       | 0.69 | 0.90 | 1.14 |  |  |  |  |

| ITT (mA)  |      |      |      |  |  |  |  |

| HIGH      | 0.84 | 1.20 | 1.56 |  |  |  |  |

| LOW       | 0.84 | 1.20 | 1.56 |  |  |  |  |

#### **Current in Macro Outputs**

| Power ATT    | Min  | Тур  | Max  |

|--------------|------|------|------|

| ITT (mA)     |      |      |      |

| HIGH         | 0.42 | 0.60 | 0.78 |

| LOW (Note 1) | 0.21 | 0.30 | 0.39 |

Note 1: Output Q is hard wired to 0.6 mA current source and cannot be assigned power attributes.

#### MXI22D-2:1 Multiplexer

#### Dramantian Dalay (units in as)

| Fropagation belay (units in ps) |        |     |            |     |           |     |     |

|---------------------------------|--------|-----|------------|-----|-----------|-----|-----|

| From                            | То     | ı   | High Power |     | Low Power |     | er  |

| Input                           | Output | Min | Тур        | Max | Min       | Тур | Max |

| l                               | z _    | 170 | 210        | 280 | 190       | 230 | 310 |

| ı                               | z ~_   | 170 | 210        | 280 | 230       | 290 | 390 |

| 1                               | ZN 🗸   | 160 | 200        | 270 | 160       | 200 | 270 |

| j                               | ZN 🔪   | 170 | 210        | 280 | 200       | 250 | 340 |

| s                               | z _/   | 240 | 300        | 400 | 320       | 400 | 540 |

| S                               | z ~_   | 240 | 300        | 400 | 320       | 400 | 540 |

| S                               | ZN 🗸   | 230 | 290        | 390 | 260       | 330 | 450 |

| S                               | ZN 🔪   | 230 | 290        | 390 | 260       | 330 | 450 |

#### Current in Base Macro

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| IEE (mA)  |      |      | ·    |

| HIGH      | 0.68 | 0.90 | 1.13 |

| LOW       | 0.46 | 0.60 | 0.76 |

#### **Current in Macro Outputs**

| Power ATT | Min  | Тур  | Max  |

|-----------|------|------|------|

| ITT (mA)  |      |      |      |

| HIGH      | 0.42 | 0.60 | 0.78 |

| LOW       | 0.21 | 0.30 | 0.39 |

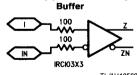

## IRCI03X2 (3)—Differential Input

TL/U/10560-14

#### Propagation Delay (units in ps)

| From<br>Inputs | To<br>Output | Min | Тур | Max |

|----------------|--------------|-----|-----|-----|

| I, IN          | z _          | 120 | 150 | 210 |

| i, IN          | z 🔨          | 120 | 150 | 210 |

| I, IN          | ZN 🗸         | 120 | 150 | 210 |

| I, IN          | ZN 🔍         | 120 | 150 | 210 |

#### **Current in Base Macro**

| Min      | Тур      | Max  |  |  |  |  |

|----------|----------|------|--|--|--|--|

| IEE (mA) | IEE (mA) |      |  |  |  |  |

| 0.60     | 0.80     | 1.0  |  |  |  |  |

| iTT (mA) | ITT (mA) |      |  |  |  |  |

| 0.84     | 1.20     | 1.56 |  |  |  |  |

#### I0RI02X2-2 Input OR/NOR Gate

TL/U/10560-15

#### Propagation Delay (units in ps)

| From<br>Input | To<br>Outputs | Min | Тур | Max |  |

|---------------|---------------|-----|-----|-----|--|

| Α             | z 🦯           | 190 | 240 | 320 |  |

| A             | z 🔨 .         | 180 | 230 | 310 |  |

| A             | ZN _          | 160 | 200 | 270 |  |

| A             | ZN 🔍          | 200 | 250 | 340 |  |

#### **Current in Base Macro**

| Min     | Тур      | Max |  |  |  |  |

|---------|----------|-----|--|--|--|--|

| IEE (mA | IEE (mA) |     |  |  |  |  |

| 0.60    | 0.80     | 1.0 |  |  |  |  |

#### **Current in Macro Outputs**

| Min      | Тур  | Max  |  |  |  |  |

|----------|------|------|--|--|--|--|

| ITT (mA) |      |      |  |  |  |  |

| 0.84     | 1.20 | 1.56 |  |  |  |  |

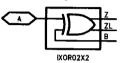

# Macro Performance Examples (Continued)

TL/U/10560-16

#### IXOR02X2—2 Input XOR Gate

#### Propagation Delay (units in ne)

| r ropagation belay (units in ps) |               |     |     |     |  |

|----------------------------------|---------------|-----|-----|-----|--|

| From<br>Input                    | To<br>Outputs | Min | Тур | Max |  |

| Α                                | Z, ZL 🖍       | 210 | 270 | 370 |  |

| Α                                | Z, ZL 🔨       | 190 | 240 | 320 |  |

| Α                                | Z, ZL 🗸       | 330 | 410 | 550 |  |

| Α                                | Z, ZL 🔨       | 300 | 380 | 510 |  |

#### Current in Base Macro

| Min      | Тур  | Мах |  |  |

|----------|------|-----|--|--|

| IEE (mA) |      |     |  |  |

| 1.20     | 1.60 | 2.0 |  |  |

| Current in Macro Outputs |          |      |  |  |  |  |

|--------------------------|----------|------|--|--|--|--|

| Min Typ Max              |          |      |  |  |  |  |

| ITT (mA                  | ITT (mA) |      |  |  |  |  |

| 0.84                     | 1.20     | 1.56 |  |  |  |  |

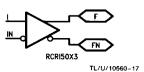

## RCRI5OX3—Differential Output Buffer

# Propagation Delay (units in ps)

| From<br>Inputs | To<br>Outputs | Min | Тур        | Max        |

|----------------|---------------|-----|------------|------------|

|                |               |     | 470<br>370 | 640<br>500 |

#### **Current in Base Macro**

| Min      | Тур  | Max  |

|----------|------|------|

| IEE (mA) | 1    |      |

| 4.35     | 5.80 | 7.25 |

# ORI250X2

TL/U/10560-18

# Propagation Delay (units in ps)

| From<br>Input | To<br>Output | Min | Тур | Max |

|---------------|--------------|-----|-----|-----|

| Α             | FZ _         | 290 | 360 | 490 |

| Α             | FZ 🔨         | 290 | 360 | 490 |

| Α             | FZN _        | 280 | 350 | 470 |

| Α             | FZN 🔍        | 290 | 360 | 490 |

#### Current in Base Macro

| Min     | Тур  | Max  |

|---------|------|------|

| IEE (mA | )    |      |

| 4.95    | 6.60 | 8.25 |

# **Current in Macro Outputs**

| Min      | Тур  | Max  |

|----------|------|------|

| IVCCA (I | mA)  |      |

| 23.8     | 28.0 | 32.2 |

# **Macro Cells Library**

# Internal Macros

| Name         | Function                            | Cells |

|--------------|-------------------------------------|-------|

| UFFERS, INVE | RTERS                               | ·     |

| BF01         | Buffer                              | 1     |

| BFI01        | Buffer/Inverter                     | 2     |

| RCR01D       | Differential Receiver/Buffer        | 1     |

| RCR11D       | Differential Receiver/Buffer        | 1     |

| RCRI01       | Differential Receiver/Buffer        | 2     |

| RCRN01       | Inverting Differential Receiver     | 1     |

| ATES         |                                     |       |

| ANI02        | 2-Input AND/NAND                    | 2     |

| OAI23D       | 3-3 OR/AND—Invert                   | 2     |

| OAI23S       | 3-3 OR/AND—Invert, 1.2 mA loef      | 4     |

| OAI24        | 4-4 OR/AND—Invert                   | 2     |

| OAI32DT      | 2-2-2 OR/AND—Invert                 | 3     |

| OAI44D       | 4-3-3-3 OR/AND—Invert               | 4     |

| OAI44S       | 4-3-3-3 OR/AND—Invert               | 4     |

| OAI46        | 5-4-5-6 OR/AND—Invert               | 5     |

| OAI55DT      | 5-4-3-2-1 OR/AND—Invert             | 5     |

| OAI66DT      | 6-6-4-4-2-2 OR/AND—Invert           | 7     |

| OR02         | 2-Input OR                          | 2     |

| OR02D        | 2-Input OR                          | 1     |

| OR05         | 5-Input OR                          | 1     |

| OR05D        | 5-Input OR                          | 1     |

| ORI02        | 2-Input OR/NOR                      | 2     |

| ORI02D       | 2-Input OR/NOR                      | 2     |

| ORI02S       | 2-Input OR/NOR                      | 4     |

| ORI05        | 5-Input OR/NOR                      | 2     |

| ORI05D       | 5-Input OR/NOR                      | 2     |

| ORI05S       | 5-Input OR/NOR, 1.2 mA loef         | 4     |

| ORI08        | 8-Input OR/NOR                      | 2     |

| ORI08D       | 8-Input OR/NOR                      | 2     |

| ORI012D      | 12-Input OR/NOR                     | 3     |

| ORN02        | 2-Input NOR                         | 2     |

| ORN02D       | 2-Input NOR                         | 1     |

| ORN05        | 5-Input NOR                         | 1     |

| ORN05D       | 5-Input NOR                         | 1     |

| 20R02D       | Dual 2-Input OR, 0.6 mA loef        | 2     |

| 4OR02S       | Quad 2-Input OR, 1.2 mA loef        | 4     |

| XOR04        | 4-Input XOR                         | 4     |

| XOR09        | 9-Input XOR                         | 8     |

| XORI03DT     | 3-Input XOR/XNOR                    | 3     |

| XORI03ST     | 3-Input XOR/XNOR, 1.2 mA loef       | 4     |

| XORI22D      | Gated 2-Input XOR/XNOR              | 2     |

| XORI22S      | Gated 2-Input XOR/XNOR, 1.2 mA loef | 4     |

| XORI23       | Gated 2-Input XOR/XNOR              | 2     |

| XORN04D      | 4-Input XNOR                        | 3     |

| XORN04S      | 4-Input XNOR, 1.2 mA loef           | 5     |

| XORN06DT     | 6-Input XNOR                        | 5     |

# Macro Cells Library (Continued)

# Internal Macros (Continued)

| Name          | Function Function                                         | Cells |

|---------------|-----------------------------------------------------------|-------|

| DECODERS, M   | JLTIPLEXERS                                               |       |

| DCE02DT       | 2:4 Decoder with Enable                                   |       |

| DCE22         | 2:4 Decoder with Enable                                   | 4     |

| MX22          | 2:1 MUX                                                   | 4     |

| MX34          | 4:1 MUX, 3 Select Inputs                                  | 1     |

| MXI02         | 2:1 MUX, Low Enable, OR Gated Select, Comp. Outputs       | 3     |

| MXI02DT       | 2:1 MUX, Low Enable, Complement Outputs                   | 3     |

| MXI02ST       | 2:1 MUX, Low Enable, 1.2 mA loef                          | 2     |

| MXI04         | 4:1 MUX, Low Enable, Complement Outputs                   | 4     |

| MXI04DT       | 4:1 MUX, Complement Outputs                               | 4     |

| MXI08ST       | 8:1 MUX, High Enable, Comp. Outputs 1.2 mA loef           | 3     |

| MXI22         | 2:1 MUX, Low Enable, OR Gated Select, Comp. Outputs       | 9     |

| MXI22D        | 2:1 MUX 2:1 MUX 2:1 MUX                                   | 2     |

| MXI24DT       | 4:1 MUX, Low Enable, Complementary Outputs                | 2     |

| 2MX04DT       | Dual 4:1 Multiplexer                                      | 4     |

| 2SELI04D      | Dual 4:1 Multiplexer                                      | 6     |

| 4MXI22D       |                                                           | 5     |

| 4MXI22S       | Quad 2:1 Multiplexer                                      | 8     |

|               | Quad 2:1 Multiplexer, 1.2 mA loef                         | 5     |

| LATCHES, MUX  |                                                           |       |

| LAI01         | D Latch with Reset and 2-Input OR Enable                  | 2     |

| FLIP-FLOPS    |                                                           |       |

| 2DFN04        | Dual D Flip-Flop with a Common Clock                      | 4     |

| DFI01         | M/S D Flip-Flop with Asynchronous Reset                   | 4     |

| DFI01D        | M/S D Flip-Flop with Asynchronous Reset                   | 4     |

| DFI02         | M/S D Flip-Flop with Set, Reset, Gated Data & Clock       | 4     |

| DFI02D        | M/S D Flip-Flop with Set, Reset, Gated Data & Clock       | 4     |

| DFI02DT       | M/S D Flip-Flop with Active Low Enable                    | 4     |

| DFI04         | M/S D Flip-Flop, Positive Edge Triggered                  | 3     |

| DFI21         | M/S D Flip-Flop with Asynchronous Reset                   | 3     |

| DFI22         | M/S D Flip-Flop with Scan Input                           | 4     |

| DFS02DT       | M/S D Flip-Flop with Scan Input                           | 5     |

| DFS02ST       | M/S D Flip-Flop with Scan Input, 1.2 mA loef              | 7     |

| DFS21DT       | M/S D Flip-Flop with Scan Input, Data Enable              |       |

| DFS21ST       | M/S D Flip-Flop with Scan Input, Data Enable, 1.2 mA foef | 5     |

| JKI02         | M/S JN-K Flip-Flop                                        | 7     |

| MXDI02        | M/S D Flip-Flop with Multiplexed Data Input               | 4 4   |

| OMPARATORS    |                                                           |       |

| None Availabl | e at This Time                                            |       |

| IISCELLANEOU  | S                                                         |       |

| AD01          | 1-Bit Carry Look Ahead Adder                              |       |

| FA21D         | 1-Bit Full Adder w/Gated Inputs                           | 3     |

| FA21S         | 1-Bit Full Adder w/Gated Inputs, 1.2 mA loef              | 4     |

| HA01D         | 1-Bit Half Adder                                          | 8     |

| HLI01         | High-Low Level Generator with Temperature Diode           | 2     |

| IEMORY        | mg., Low cover deficition with Femperature blode          | 1     |

|               | Charad Inguit Duffer 0.0 All 1                            |       |

| IDC02X2       | Shared Input Buffer, 0.6 mA loef                          | 1     |

| IDC12X2       | Shared Input Buffer, 0.6 mA loef                          | 1     |

| MTX50X2       | Shared Output Buffer, $50\Omega$                          | 1     |

| RS69D         | 64 X 9 RAM                                                |       |

|               |                                                           |       |

|               |                                                           |       |

# Macro Cells Library (Continued)

# Input Macros

| Name          | Function                                              | Cells |

|---------------|-------------------------------------------------------|-------|

| UFFERS, INVER | TERS                                                  |       |

| IBF02X2 (3)   | High Fan-Out Buffer, 10 mA loef (Note 1)              | 1     |

| IBF03X2 (3)   | Input Buffer, 0.6 mA loef                             | 1     |

| IBFI03X2 (3)  | Input Buffer, Complementary Outputs, 0.6 mA loef      | 1     |

| IBFN03X2      | Input Buffer, Inverting 0.6 mA loef                   | 1     |

| OFFERENTIAL R | ECEIVERS                                              |       |

| ICKD0X2       | Differential Input Clock Driver, 18 mA loef (Note 1)  | 2     |

| ICKD0X3       | Differential Input Clock Driver, 18 mA loef (Note 1)  | 2     |

| ICKD1X2       | Differential Input Clock Driver, 18 mA loef (Note 2)  | 2     |

| IRCI02X2 (3)  | Differential Input Buffer, Comp. Outputs, 10 mA loef  | 2     |

| IRCI03X2 (3)  | Differential Input Buffer, Comp. Outputs, 0.6 mA loef | 2     |

| GATES         |                                                       |       |

| IOR02X2       | 2-Input OR, 0.6 mA loef                               | 2     |

| IORI02X2      | 2-Input OR/NOR, 0.6 mA loef                           | 2     |

| IORN02X2      | 2-Input NOR, 0.6 mA loef                              | 2     |

| IXOR02X2      | 2-Input XOR, 0.6 mA loef                              | 1     |

| IXORN2X2      | 2-Input XNOR, 0.6 mA loef                             | 1     |

| MISCELLANEOU: | S                                                     |       |

| IN00X2 (3)    | Input Pad (Zero Resistance)                           | 1     |

Note 2: ICKD12X2 uses two external cells for electrical connection and covers 44 internal cells for clock dis

# **Output Macros**

| Name           | Function                                | Cells |

|----------------|-----------------------------------------|-------|

| BUFFERS, INVER | TERS                                    |       |

| BF50X2 (3)     | Output Buffer, 50Ω, F100K               | 1     |

| BFI50X3        | Complementary Output Buffer, 50Ω, F100K | 2     |

| BFN50X2        | Output Inverter, 50Ω, F100K             | 1     |

| RCRI50X3       | Differential Output Buffer, 50Ω, F100K  | 2     |

| GATES          |                                         |       |

| OR220X2        | 2-Input OR, 25Ω, F100K                  | 1     |

| ORI220X2       | 2-Input OR/NOR, 25Ω, F100K              | 2     |

| OR250X2        | 2-Input OR, 50Ω, F100K                  | 1     |

| ORN250X2       | 2-Input NOR, 50Ω, F100K                 | 1     |

| ORI250X2       | 2-Input OR/NOR, 50Ω, F100K (FGA 14K)    | 2     |

| ORI250X3       | 2-Input OR/NOR, 50Ω, F100K (FGA 4K)     | 2     |

| OR450X2        | 4-Input OR, 50Ω, F100K                  | 1     |

| ORN450X2       | 4-Input NOR, 50Ω, F100K                 | 1     |

| OR1450X2       | 4-Input OR/NOR, 50Ω, F100K              | 2     |

| BUS DRIVERS    |                                         |       |

| BD20X2         | 2-Input OR, 25 $\Omega$ , F100K         | 1     |

| BDN20X2 (3)    | 2-Input NOR, 25Ω, F100K                 | 1     |

| TR20X3               | Function Function                                          | Cel   |

|----------------------|------------------------------------------------------------|-------|

|                      | 2-Input OR ECL Transceiver, 25Ω                            | 1     |

| TRN20X3              | 2-Input NOR ECL Transceiver, 25Ω                           | 1     |

| TRN50X2 (3)          | 2-Input NOR ECL Transceiver, 50Ω                           | 1     |

| Miscellar            | neous                                                      |       |

| Name                 | Function                                                   | Cell  |

| OUT00X2 (3)          | Output Pad (Zero Resistance)                               | 1     |

| TTL Macı             | ros                                                        |       |

| Name                 | Function                                                   | Cells |

| TED11X3              | TTI locat Duffee                                           |       |

| TES11X3              | TTL Input Buffer TTL Input Buffer (+5V Only)               | 1 1   |

| OUTPUT BUFFER        | S                                                          |       |

| TOBD01X3             | 8 mA TTL Output Buffer                                     | 1     |

| TOBD11X3<br>TOBS11X3 | 20 mA TTL Output Buffer 20 mA TTL Output Buffer (+5V Only) | 1     |

| TRANSCEIVERS         | 20 THA TTE Output Buller (+5V Only)                        | 1     |

| TTRD11X3             | 20 mA TTL Transceiver                                      | 1     |

| TTRS01X3             | 8 mA TTL Transceiver (+5V Only)                            | '1    |

|                      |                                                            |       |

|                      |                                                            |       |

Macro Cells Library (Continued)

# **ASIC Design Centers**

#### Santa Clara

2900 Semiconductor Dr. P.O. Boy 8090 Santa Clara, CA 95052-8090 Tel: 408-721-4140

# Los Angeles

15641 Red Hill Ave Suite 120 Tustin, CA 92680 Tel: 714-259-1540

## **Boston**

111 S. Bedford Street Suite 200 Burlington, MA 01803 Tel: 617-273-7430

#### Minnesota

1801 Fast 79th Street Bloomington, MN 55420 Tel: 612-854-8200

# Canada

5925 Airport Road Suite 112 Mississauga, ON L4V1W1 Tel: (416) 678-2597

## Japan

National Semiconductor Janan 1 td. Sansei-doh Shiniuku Bldg. 5f 4-15. Nishishiniuku, Shiniuku-ku Tokyo 160

Tel: 3-299-7020

# Hona Kona

4th Floor, Austin Tower 22-26 Austin Avenue Tsimshatsui, Kowloon, Hong Kong Tel: 852-3-733-1946

#### Taiwan

9th Floor, No. 18 Sec. 1. Chang An East Road Taipei, Taiwan Tel: (02)-562-2881

# South Korea

13th Floor, Dai Han Life Insurance Building 60 Yoido-Dong, Youngdeungpo-Ku Seoul Korea 150-763 Tel: 82-2-784-8051

#### Australia

Suite 4 Level 15 3 Thomas Holt Dr. North Rvde, N.S.W. 2113 Sydney, Australia Tel: 61-2-887-4355

### United Kinadom

National Semiconductor (UK) Ltd. The Maples Kembrey Park Wilshire, SN 26 UT Swindon United Kingdom Tel: 0793-614141

Lit #103755

# France

National Semiconductor La Bousidiere - Bat Champagne RN 186 92357 Le Plessis Robinson Cedex France Tel: 033-140-948-888

# Italy

National Semiconductor SPA Strada 7-Palazzo R/3 20089 Rozzano-Milanfiori Italy Tel: 02-8242046

#### West Germany

National Semiconductor GmbH Industriestr 10 8080 Fuerstenfeldbruck West Germany Tel: 08141-103-0

## Sweden

National Semiconductor AB Stensatravagen 13 12702 Skarholmen Sweden Tel: 08-970190

#### Israel

National Semiconductor Ltd. Masketstreet P.O. Box 3007 Herzlia B. 46104 lerapi Tel: 02525-22255

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can

be reasonably expected to result in a significant injury

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

to the user.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: (408) 721-5000 TWX: (910) 339-9240 National Semiconductor GmbH Industriestrasse 10 D-8080 Furstenfeldbruck West Germany Tel: (0-81-41) 103-0 Fax: (08141) 103554

NS Japan Ltd. Sanseido Bldg. 5F 4-15 Nishi Shinjuku Shinjuku-Ku, Tokyo 160, Japan Tel: 3-299-7001 FAX: 3-299-7000

National Semiconductor Hong Kong Ltd. Suite 513, 5th Floor Chinachem Golden Plaza, 77 Mody Road, Tsimshatsui East, Kowloon, Hong Kong Tell: 3-7231290 Telex: 52996 NSSEA HX Fax: 3-3112536

National Semicondutores Do Brasil Ltda. Av. Brig. Faria Lima, 1383 6.0 Andor-Conj. 62 01451 Sao Paulo, SP. Brasil

Melbourne, 3004 Tel: (55/11) 212-5066 Fax: (55/11) 211-1181 NSBR BR

National Semiconductor (Australia) PTY, Ltd. 1st Floor, 441 St. Kilda Rd Tel: (03) 267-5000 Fax: 61-3-2677458

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without not