## HD Radio<sup>™</sup> baseband receiver

Preliminary data

#### **Features**

#### General

- HD Radio signal decoding for AM and FM digital audio

- Tensilica<sup>TM</sup> signal/audio processing core architecture running up to 166 MHz

- Hardware support for conditional access (one-time programmable 640-bit memory)

- 2 internal PLLs: processor cores and peripheral bus

- 1 Internal clock oscillator and external clock input

- 250 mW with core voltage of 1.2 V and IO voltage of 3.3 V

- Temperature range: -40 to +85 °C

#### **Memories**

- Internal boot ROM

- SDRAM controller addressing up to 512 Mbit of SDRAM in x16 configuration

- Serial Flash memory interface for application code loading

#### **Turner interface**

- Support of RF-IF peripheral processor (RIPP) and other front ends such as STA3004 and STA7506

- Input from RF front-end via programmable serial interface supporting 650 kS/s, 675 kS/s, 744.1875 kS/s, 882 kS/s, 912 kS/s sample rates

- Secondary RF front-end interface for dual tuner applications

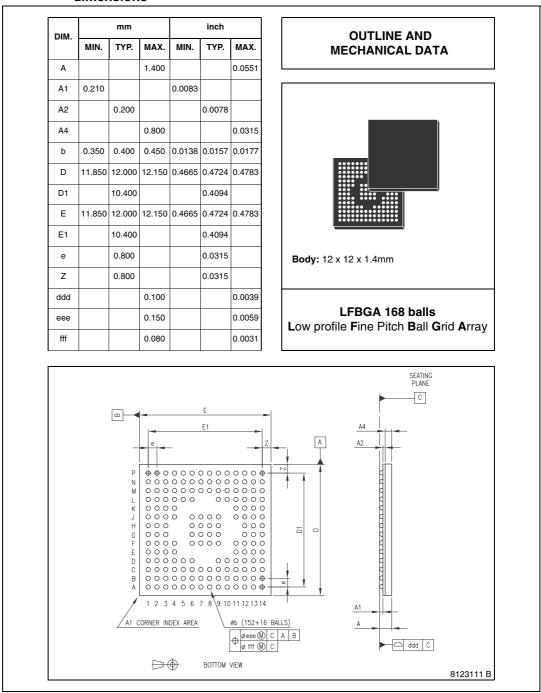

# LGFP144 (20x20x1.4 mm) LFBGA 168 balls (12x12x1.4 mm)

#### Other interfaces

- One stereo audio sample rate converter (44.1 kS/s, 45.6 kS/s, 48 kS/s)

- One input and three stereo channels audio output (by IIS serial audio interface)

- 2 IIC and 3 SPI serial interfaces

- 1 UART interface

- 1 GPIO interface (8 lines)

- SD/MMC interface via SPI

- JTAG interface

#### Supported HD Radio system capabilities

- Multicasting

- Program service data

- Real-time traffic

- Audio time shifting

- iTunes Tagging<sup>™</sup>

- Surround sound

#### **Applications**

- Car radio

- Personal navigation device (PND)

- Portable battery operated systems

#### Table 1. Device summary

| Order code | Package <sup>(1)</sup>         | Packing |

|------------|--------------------------------|---------|

| STA680     | LFBGA 168 balls (12x12x1.4 mm) | Tray    |

| STA680Q    | LQFP144 (20x20mm)              | Tray    |

1. ECOPACK® compliant.

Contents STA680

# **Contents**

| 1    | Description              |                   |                                |            |  |  |  |  |  |  |  |

|------|--------------------------|-------------------|--------------------------------|------------|--|--|--|--|--|--|--|

| 2    | HD Radio™ system         |                   |                                |            |  |  |  |  |  |  |  |

| 3    | Receiver system overview |                   |                                |            |  |  |  |  |  |  |  |

|      | 3.1                      | HD Ra             | dio processing                 | 9          |  |  |  |  |  |  |  |

|      | 3.2                      | Dual st           | ream HD Radio processing       | 9          |  |  |  |  |  |  |  |

|      | 3.3                      | Additio           | nal processing                 | 10         |  |  |  |  |  |  |  |

|      |                          | 3.3.1             | AM/FM processing               |            |  |  |  |  |  |  |  |

|      |                          | 3.3.2             | Audio codec                    | 10         |  |  |  |  |  |  |  |

|      |                          | 3.3.3             | Other                          | 11         |  |  |  |  |  |  |  |

|      | 3.4                      | Overvi            | ew of main functional blocks   | 11         |  |  |  |  |  |  |  |

|      |                          | 3.4.1             | Adjacent channel filter        |            |  |  |  |  |  |  |  |

|      |                          | 3.4.2             | HiFi2 core                     |            |  |  |  |  |  |  |  |

|      |                          | 3.4.3             | Vectra core                    |            |  |  |  |  |  |  |  |

|      |                          | 3.4.4             | DMA                            | 11         |  |  |  |  |  |  |  |

|      |                          | 3.4.5             | Hardware accelerator (VITERBI) |            |  |  |  |  |  |  |  |

| 4    | I/O d                    | descripti         | on                             | 12         |  |  |  |  |  |  |  |

|      | 4.1                      | LQFP (            | description                    | 12         |  |  |  |  |  |  |  |

|      | 4.2                      | LFBGA description |                                |            |  |  |  |  |  |  |  |

|      | 4.3                      | Pin list          |                                |            |  |  |  |  |  |  |  |

|      | 4.4                      | I/Os su           | pply groups                    | 22         |  |  |  |  |  |  |  |

| 5    | Ope                      | ration ar         | nd general remarks             | 23         |  |  |  |  |  |  |  |

|      | 5.1                      |                   | chemes                         |            |  |  |  |  |  |  |  |

|      | 5.2                      | Power             | on                             | 25         |  |  |  |  |  |  |  |

|      |                          | 5.2.1             | Power supply ramp up phase     |            |  |  |  |  |  |  |  |

|      |                          | 5.2.2             | Oscillator setting time        |            |  |  |  |  |  |  |  |

|      |                          | 5.2.3             | Boot sequence                  | 26         |  |  |  |  |  |  |  |

|      |                          | 5.2.4             | Normal operation mode          | 27         |  |  |  |  |  |  |  |

| 6    | Digi                     | tal I/O ar        | nd memory interfaces           | 28         |  |  |  |  |  |  |  |

|      | 6.1                      | Interfac          | es: LQFP vs. LFBGA             | 28         |  |  |  |  |  |  |  |

| 2/47 |                          |                   | Doc ID 14860 Rev 3             | <b>577</b> |  |  |  |  |  |  |  |

STA680 Contents

|   | 6.2  | Tuner i   | interface                                     | 29 |

|---|------|-----------|-----------------------------------------------|----|

|   | 6.3  | Audio     | interface (AIF)                               | 31 |

|   |      | 6.3.1     | Output serial audio interface (SAI)           | 31 |

|   |      | 6.3.2     | Input serial audio interface                  | 32 |

|   |      | 6.3.3     | S/PDIF interface                              | 32 |

|   |      | 6.3.4     | Audio sample rate converter (ASRC)            | 33 |

|   | 6.4  | Serial    | peripheral interfaces (SPI)                   | 33 |

|   |      | 6.4.1     | Host micro serial peripheral interface (SPI1) | 34 |

|   |      | 6.4.2     | Flash serial peripheral interface (SPI2)      | 35 |

|   |      | 6.4.3     | SD/MMC serial peripheral interface (SPI3)     | 35 |

|   |      | 6.4.4     | I <sup>2</sup> C interfaces                   | 35 |

|   |      | 6.4.5     | Host micro I <sup>2</sup> C interface (I2C1)  | 37 |

|   |      | 6.4.6     | Auxiliary I <sup>2</sup> C interface (I2C2)   | 37 |

|   | 6.5  | SDRA      | M interface                                   | 38 |

| 7 | Elec | trical sp | pecifications                                 | 40 |

|   | 7.1  | Absolu    | ute maximum ratings                           | 40 |

|   | 7.2  |           | ial data                                      |    |

|   | 7.3  | Operat    | ting conditions                               | 41 |

| 8 | Pack | age inf   | ormation                                      | 44 |

| 9 | Revi | sion his  | storv                                         | 46 |

List of tables STA680

# List of tables

| Table 1.  | Device summary                                         | 1    |

|-----------|--------------------------------------------------------|------|

| Table 2.  | Pins description                                       | . 14 |

| Table 3.  | Reference clock configuration                          | . 23 |

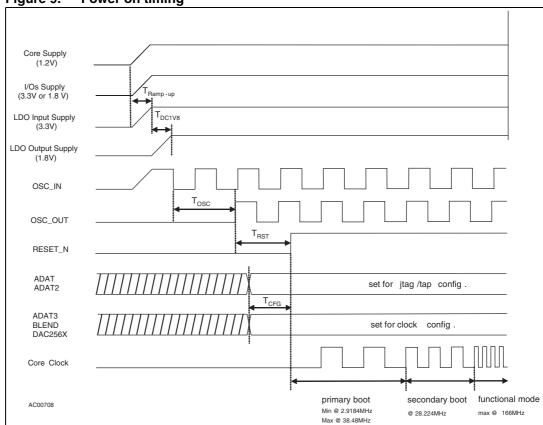

| Table 4.  | Power on timing parameters                             | . 25 |

| Table 5.  | Interface list                                         | . 28 |

| Table 6.  | Baseband interfaces pin list                           | . 29 |

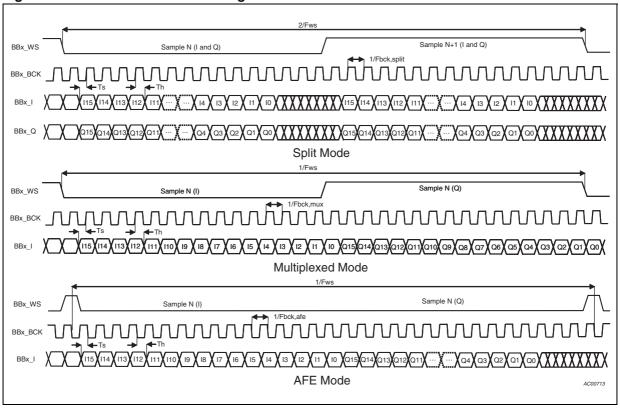

| Table 7.  | BBI timing values                                      | . 30 |

| Table 8.  | AIF pin list                                           | . 31 |

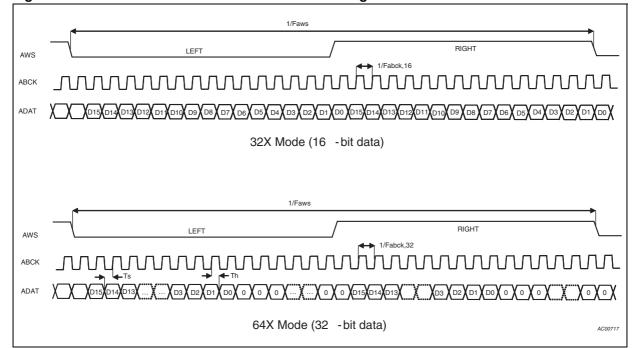

| Table 9.  | Serial audio interface timing values                   | . 32 |

| Table 10. | SPI interface timing values                            | . 34 |

| Table 11. | Host Micro SPI pin list                                | . 34 |

| Table 12. | Flash SPI pin list                                     | . 35 |

| Table 13. | SD/MMC SPI pin list                                    |      |

| Table 14. | Host and auxiliary I <sup>2</sup> C interface pin list | . 36 |

| Table 15. | I <sup>2</sup> C interface timing values               | . 36 |

| Table 16. | I2C1 interface device address                          | . 37 |

| Table 17. | I2C2 interface device address                          | . 37 |

| Table 18. | SDRAM Interface pin description                        | . 38 |

| Table 19. | SDRAM interface timing values                          | . 39 |

| Table 20. | Absolute maximum ratings                               | . 40 |

| Table 21. | Thermal data                                           | . 40 |

| Table 22. | DC electrical characteristics                          | . 41 |

| Table 23  | Document revision history                              | 46   |

STA680 List of figures

# **List of figures**

| Figure 1.  | Functional data flow diagram                                          | 6    |

|------------|-----------------------------------------------------------------------|------|

| Figure 2.  | HD Radio™ system logo                                                 | 7    |

| Figure 3.  | STA680 block diagram (detailed)                                       | 8    |

| Figure 4.  | Single channel application                                            | 9    |

| Figure 5.  | Dual channel application                                              | . 10 |

| Figure 6.  | LQFP pinout (top view)                                                | 12   |

| Figure 7.  | LFBGA ballout (top view)                                              | . 13 |

| Figure 8.  | Clock generation unit                                                 |      |

| Figure 9.  | Power on timing                                                       | . 25 |

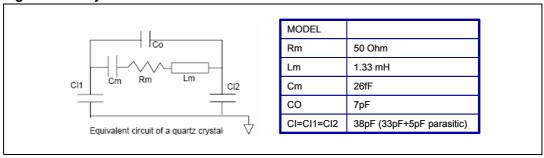

| Figure 10. | Crystal characteristics                                               | 26   |

| Figure 11. | BBI waveforms and timings                                             | 30   |

| Figure 12. | Serial audio interface waveforms and timings                          | . 32 |

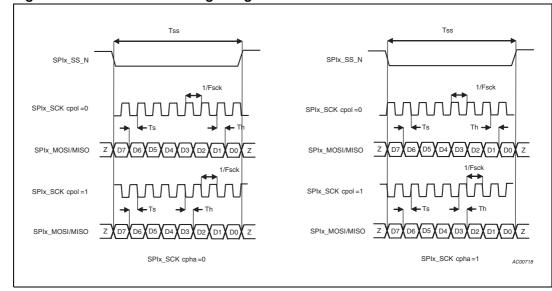

| Figure 13. | SPI interface timings diagrams and waveforms                          | . 34 |

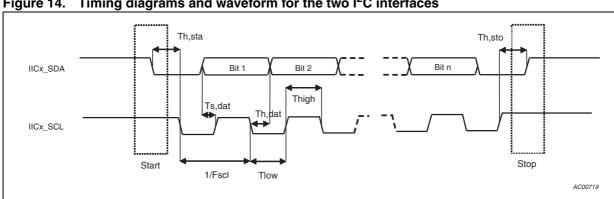

| Figure 14. | Timing diagrams and waveform for the two I <sup>2</sup> C interfaces  | 36   |

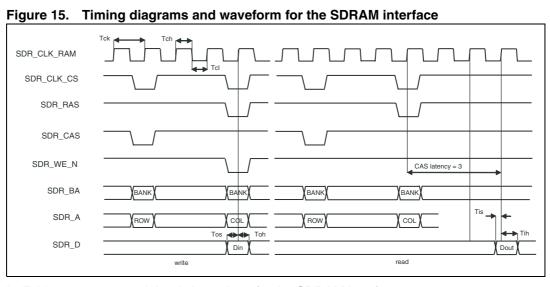

| Figure 15. | Timing diagrams and waveform for the SDRAM interface                  | 38   |

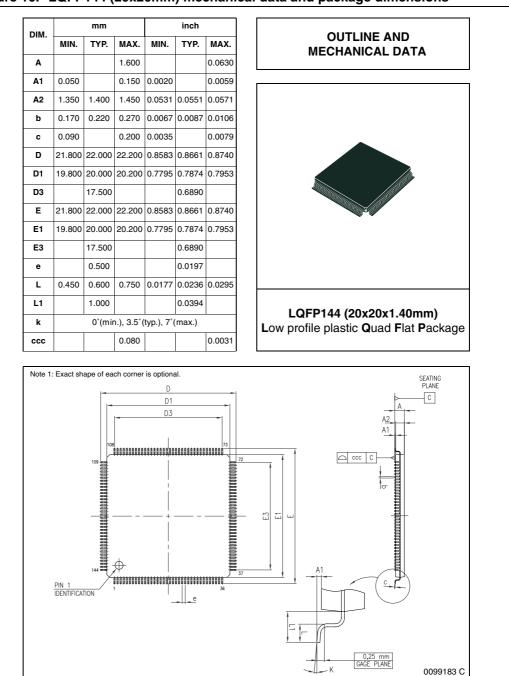

| Figure 16. | LQFP144 (20x20mm) mechanical data and package dimensions              | . 44 |

| Figure 17. | LFBGA 168 balls (12x12x1.4 mm) mechanical data and package dimensions | . 45 |

Description STA680

# 1 Description

The STA680 from STMicroelectronics is a system on a chip designed for demodulating and decoding of HD Radio<sup>(a)</sup> signals. The STA680 is compliant with the iBiquity specification and extends the possibility to implement new and optional features and to manage additional services.

The device combines it all into a single IC consisting of several hardware blocks and a programmable core to guarantee the proper level of flexibility, low current consumption and an optimized die size.

The STA680 implements the entire signal processing chain of an HD Radio receiver.

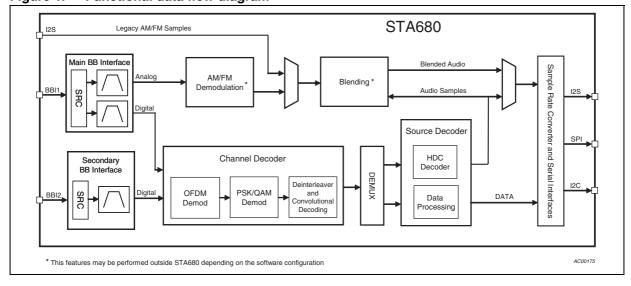

- The digital channel demodulation and decoding, including OFDM demodulation and error correction.

- Source decoding, consisting of audio and data decoding of the digital channel.

- The analog demodulator extracting the audio signal from the legacy analog AM/FM signal (can be implemented as an optional feature)

- The blending of the analog and digital audio signals

*Figure 1* presents a functional diagram describing the data flow inside STA680 for HD Radio demodulating and decoding.

The architecture consists of an effective and balanced hardware/software implementation, to pursue the best combination in terms of current consumption, system flexibility and device cost.

Functional blocks which are standard, and computation intensive, are implemented using custom logic. Software implementation is more efficient for functional blocks where flexibility is needed. Such flexibility enables the STA680 to be ready for future evolution, and allows the implementation of specific and optional features.

Figure 1. Functional data flow diagram

6/47

Doc ID 14860 Rev 3

a. HD Radio™ technology manufactured under license from iBiquity Digital Corp. U.S. and Foreign Patents.

HD Radio™ and the HD Radio logo are proprietary trademarks of iBiquity Digital Corp.

STA680 HD Radio™ system

# 2 HD Radio™ system

The HD Radio™ system, compliant with National Radio System Committee NSRC-5 standard, was developed by iBiquity Digital Corporation.

This system is designed to permit a smooth evolution from current (legacy) analog AM/FM radio to a fully digital in-band on-channel (IBOC) system. The HD Radio system delivers digital audio and data services to mobile, portable, and fixed receivers from terrestrial trasmitters in the existing medium frequency (MF) and very high frequency (VHF) radio bands. Broadcaster may continue to transmit analog AM and FM simultaneusly with the new, higher quality and more robust digital signal, allowing themselves and their listener to convert from legacy analog to digital radio while maintaining their current frequencies allocations.

The HD Radio system is identified by the logo reported hereafter:

Figure 2. HD Radio™ system logo

# 3 Receiver system overview

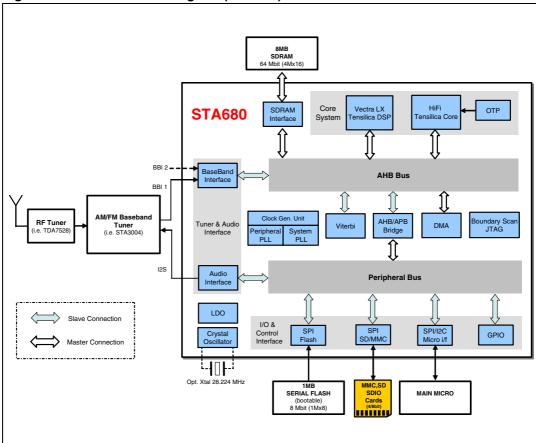

Figure 3 shows the partitioning of the HD Radio receiver system, composed by an AM/FM RF front-end, IF channel signal processor and the HD Radio decoder (STA680).

Figure 3. STA680 block diagram (detailed)

The analog IF signal from the tuner front-end is digitized by a high-resolution sigma-delta A/D converter. A digital down-converter block, embedded into the IF channel signal processor, transforms the IF into a complex baseband signal. Its Bandwidth and sample rate have been adapted by filtering and decimation to match the specification of the HD Radio system. The complex baseband signal feed the HD Radio decoder (STA680) where the HD Radio stream is demodulated and decoded. The STA680 receives a digital baseband signal from the IF channel signal processor and returns the recovered audio and data services.

STA680 can be configured to work with digital IF baseband inputs based on standard frontends. Front-ends must conform to HD Radio standards for filter bandwidth and linearity.

The STA680 requires external serial Flash memory to boot but can also be configured to boot from a host controller on IIC or SPI interfaces. The FLASH memory Is issued for program code and configuration data storage. STA680 needs SDRAM for bulk data storage required during the IBOC signal processing.

8/47 Doc ID 14860 Rev 3

## 3.1 HD Radio processing

The STA680 HD Radio decoder does the processing of the IBOC signal. It receives a complex digital signal from an AM/FM IF channel signal processor. The native sample rate is 744.1875 kS/s for FM and 46.51171875 kS/s for AM. However, other input sample rates are acceptable because of the sample rate converter in the baseband Interface (BBI). These include: 650 kS/s, 675 kS/s, 882 kS/s and 912 kS/s. If a baseband signal is provided that is not at the native sample frequency of 744.1875 kHz it must be sample rate converted to this rate. Sample rate conversion hardware is provided on-chip to support this. This feature allows the STA680 to operate with various AM/FM front-ends.

The STA680is then responsible for detection, acquisition, and demodulation of the IBOC signal. Such function is primarily implemented by the Vectra DSP core. The demodulated signal is then passes to the Hi-Fi processor, for decoding, audio blending and handling of data services. A digital 44.1 kHz decompressed audio is output via the Digital Audio Interface.

The STA680 uses sophisticated algorithms to recover IBOC data even in the presence of signal impairments including fading and a variety of other interferences.

To process the HD Radio stream STA680 requires a 4M x16 external SDRAM (with up to 32M x16 supported) for data storage.

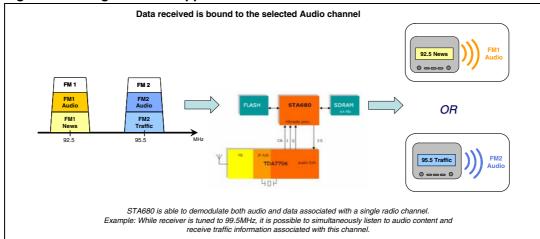

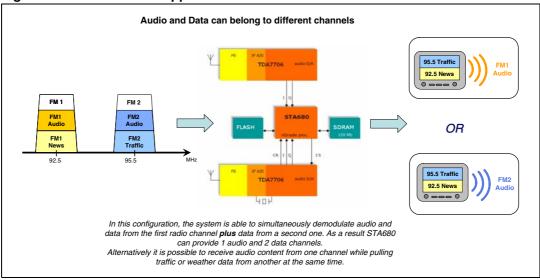

### 3.2 Dual stream HD Radio processing

STA680 is capable to simultaneously demodulate two different HD Radio streams. This unique feature enables the device to decode an HD Radio audio stream, in parallel with any data service broadcasted by a different radio channel. The implementation of the dual stream HD Radio processing requires that two AM/FM RF tuners are connected to the STA680.

In a single channel implementation a single RF tuner is used. In such configuration STA680 is able to demodulate at the same time both the audio and the data associated with the radio channel (i.e. 92.5 MHz or 102.5 MHz). This means that if the user sets the tuner 102.5 MHz, he or she can listed to FM2 audio and receive traffic information broadcasted on that channel. At the same time if the user tunes to another frequency (FM1), current traffic information will be lost.

Figure 4. Single channel application

577

In a dual channels implementation STA680 can simultaneously demodulate audio and data associated to different radio channels. This means that in the example above it would be still possible to receive traffic information broadcasted on FM2 (102.5 MHz) while listening FM1 audio program broadcasted on 92.5 MHz

## 3.3 Additional processing

The HD Radio stream demodulation and decoding take up only part of the computation power and memories resources available on STA680. This makes it possible to use the spare resources to implement additional features.

Depending on memory and computation power required by the additional features, it is possible to run them in parallel with the HD Radio stream decoding or in alternative, having all the hardware resources available for the additional features.

#### 3.3.1 AM/FM processing

It is possible to implement legacy AM/FM processing in parallel with the HD Radio stream demodulation and decoding. Such solution is particularly suitable and appealing when the STA680 processor works jointly with an AM/FM RF front-end not incorporating the AM/FM demodulation.

#### 3.3.2 Audio codec

STA680 can be used as a media processor to decode MP3/WMA audio stream. Thanks to the availability of the MMC and SD interface it is possible to reproduce an MP3 stream stored into any MMC or SD cards

10/47 Doc ID 14860 Rev 3

#### 3.3.3 Other

The spare computation power and memories are suitable to implement other specific algorithms or custom software application. For example sophisticated sound and audio processing could be implemented on the HD Radio decompressed audio. Audio output can be provided either in IIS master clock mode or in slave mode with the on-chip audio sample rate converter. Up to six audio channels may be provided in a standard configuration.

Another possibility is to implement on the STA680 the handling of data services.

#### 3.4 Overview of main functional blocks

#### 3.4.1 Adjacent channel filter

This module performs time domain filtering specifically for IBOC system. It receives a complex baseband IBOC signal input from SRC module and pre-conditions the signal for subsequent modem processing. The module is a front-end device.

#### 3.4.2 HiFi2 core

The HiFi2 is a signal processing engine specifically designed to provide high quality 24-bit audio processing. The HiFi2 is also useful for advanced data applications such as storage and playback of received audio and conditional access processing. The HiFi2 leverages the Tensilica Xtensa LX engine with additional useful hardware capabilities such as:

- Specialized instructions for 24-bit Audio MAC & stream coding

- Dual MAC (each supports 24 x 24 and 32 x 16 bit format)

- Huffman Encode / Decode and truncate functions

- Two way SIMD arithmetic and Boolean operations

#### 3.4.3 Vectra core

The Vectra LX is a powerful, configurable 32-bit RISC engine optimized for DSP with VLIW capabilities. The Vectra LX on board the STA680 includes eight MAC units, sixteen 160-bit vector operation registers, and a number of SIMD arithmetic instructions. Custom instructions in the Vectra are targeted for DSP applications such as filters and FFTs. The Vectra processor has been further configured with specific instructions for efficient performance on the HD Radio application.

#### 3.4.4 DMA

A ten-channel DMA controller is attached to the AHB bus to allow the Vectra and HiFi2 processor cores to move large blocks of data efficiently. Certain channels are dedicated for use with certain hardware blocks because of hardware handshaking signals.

#### 3.4.5 Hardware accelerator (VITERBI)

A complex convolutional Viterbi module is designed to fully comply with the HD Radio system. The module supports both K constant of 7 and 9, for IBOC digital FM and AM bands respectively.

I/O description **STA680**

#### I/O description 4

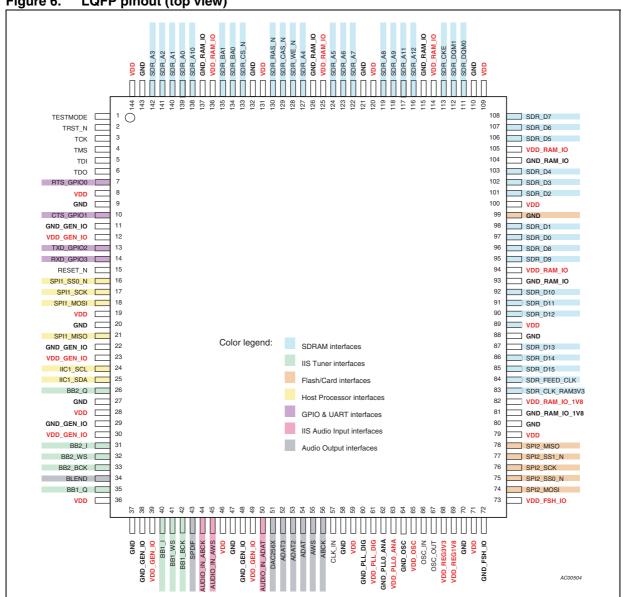

The STA680 has two package options to suit different application needs. The first option is a 20x20mm LQFP package with 144 pins while the second one is a 12x12mm LFBGA with 169 balls and 0.8mm pitch.

#### 4.1 LQFP description

Figure 6 presents the pinout of the STA680 for the LQFP package option. Different colors have been used for I/O signals from different interfaces according to Table 2 reported in Section 4.3.

STA680 I/O description

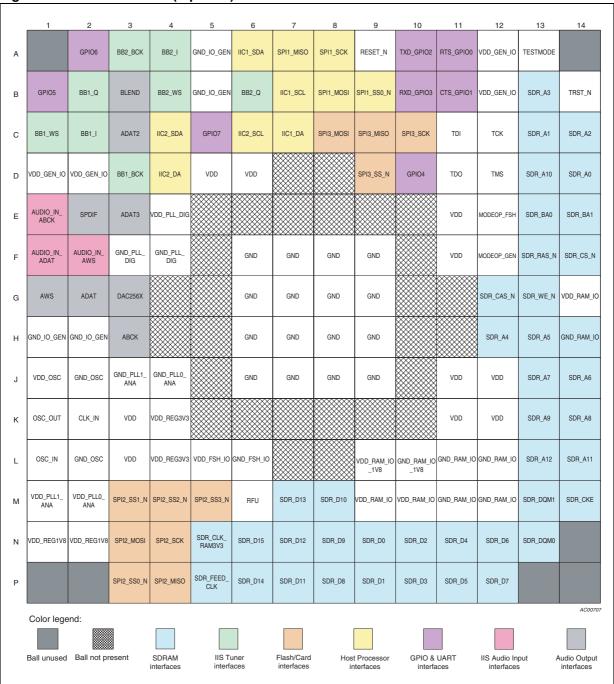

# 4.2 LFBGA description

Figure 7 presents the ballout of the STA680 for the LFBGA package option. Different colors have been used for I/O signals from different interfaces according to *Table 2* reported in Section 4.3.

Figure 7. LFBGA ballout (top view)

I/O description STA680

# 4.3 Pin list

The *Table 2* briefly describes the main function and characteristics of the STA680 I/O signals in normal operation mode.

Table 2. Pins description

| Pin #         | Ball#                          | Signal name | Туре       | Pull-up              | Electrical        | Supply               | Description                     |  |  |  |  |  |

|---------------|--------------------------------|-------------|------------|----------------------|-------------------|----------------------|---------------------------------|--|--|--|--|--|

| Test          |                                | <u> </u>    | <i>,</i> . | /down <sup>(1)</sup> |                   | group                | ·                               |  |  |  |  |  |

| 1             | A13                            | TESTMODE    | ı          | Pull-down            | 1.8 V or<br>3.3 V | Generic<br>IO supply | Factory test mode enable        |  |  |  |  |  |

| Standa        | Standard 1149.1 JTAG interface |             |            |                      |                   |                      |                                 |  |  |  |  |  |

| 2             | B14                            | TRST_N      | ı          | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | JTAG active-low test reset      |  |  |  |  |  |

| 3             | C12                            | TCK         | I          | Pull-down            | 1.8 V or<br>3.3 V | Generic<br>IO supply | JTAG test clock                 |  |  |  |  |  |

| 4             | D12                            | TMS         | I          | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | JTAG test mode state            |  |  |  |  |  |

| 5             | C11                            | TDI         | ı          | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | JTAG test data in               |  |  |  |  |  |

| 6             | D11                            | TDO         | 0          | -                    | 1.8 V or<br>3.3 V | Generic<br>IO supply | JTAG test data out              |  |  |  |  |  |

| GPIO &        | UART i                         | nterfaces   |            |                      |                   |                      |                                 |  |  |  |  |  |

| 7             | A11                            | RTS_GPIO0   | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | UART ready to send / GPIO bit 0 |  |  |  |  |  |

| 10            | B11                            | CTS_GPIO1   | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | UART clear to send / GPIO bit 1 |  |  |  |  |  |

| 13            | A10                            | TXD_GPIO2   | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | UART transmit data / GPIO bit 2 |  |  |  |  |  |

| 14            | B10                            | RXD_GPIO3   | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | UART receive data / GPIO bit 3  |  |  |  |  |  |

| Not<br>bonded | D10                            | GPIO4       | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | GPIO bit 4                      |  |  |  |  |  |

| Not<br>bonded | B1                             | GPIO5       | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | GPIO bit 5                      |  |  |  |  |  |

| Not<br>bonded | A2                             | GPIO6       | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | GPIO bit 6                      |  |  |  |  |  |

| Not<br>bonded | C5                             | GPIO7       | I/O        | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | GPIO bit 7                      |  |  |  |  |  |

| Reset         |                                |             |            |                      |                   |                      |                                 |  |  |  |  |  |

| 15            | <b>A</b> 9                     | RESET_N     | I          | Pull-up              | 1.8 V or<br>3.3 V | Generic<br>IO supply | Device active-low reset         |  |  |  |  |  |

STA680 I/O description

Table 2. Pins description (continued)

| Pin #         | Ball#      | Signal name | Туре | Pull-up<br>/down <sup>(1)</sup> | Electrical        | Supply<br>group      | Description                                     |

|---------------|------------|-------------|------|---------------------------------|-------------------|----------------------|-------------------------------------------------|

| Host pr       | ocessoi    | rinterfaces |      |                                 |                   |                      |                                                 |

| 16            | В9         | SPI1_SS0_N  | 1    | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 1 active-low slave select         |

| 17            | A8         | SPI1_SCK    | ı    | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 1 serial clock                    |

| 18            | B8         | SPI1_MOSI   | 1    | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 1 serial data master out/slave in |

| 21            | A7         | SPI1_MISO   | 0    | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 1 serial data master in/slave out |

| 24            | В7         | IIC1_SCL    | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | IIC interface 1 serial clock line               |

| 25            | A6         | IIC1_SDA    | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | IIC interface 1 serial data line                |

| Not<br>bonded | C7         | IIC1_DA     | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | IIC interface 1 data acknowledged               |

| Not<br>bonded | C6         | IIC2_SCL    | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | IIC interface 2 serial clock line               |

| Not<br>bonded | C4         | IIC2_SDA    | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | IIC interface 2 serial data line                |

| Not<br>bonded | D4         | IIC2_DA     | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | IIC interface 2 data acknowledged               |

| IIS tune      | er interfa | ices        |      |                                 |                   |                      |                                                 |

| 40            | C2         | BB1_I       | 1    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Primary baseband interface serial I data        |

| 35            | B2         | BB1_Q       | ı    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Primary baseband interface serial Q data        |

| 41            | C1         | BB1_WS      | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Primary baseband interface word strobe          |

| 42            | D3         | BB1_BCK     | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Primary baseband interface bit clock            |

| 31            | A4         | BB2_I       | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Secondary baseband interface serial I data      |

| 26            | В6         | BB2_Q       | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Secondary baseband interface serial Q data      |

| 32            | B4         | BB2_WS      | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Secondary baseband interface word strobe        |

| 33            | А3         | BB2_BCK     | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Secondary baseband interface bit clock          |

I/O description STA680

Table 2. Pins description (continued)

| Pin #    | Ball#                     | Signal name   | Туре | Pull-up<br>/down <sup>(1)</sup> | Electrical        | Supply<br>group      | Description                                     |  |  |  |  |  |

|----------|---------------------------|---------------|------|---------------------------------|-------------------|----------------------|-------------------------------------------------|--|--|--|--|--|

| IIS audi | IIS audio input interface |               |      |                                 |                   |                      |                                                 |  |  |  |  |  |

| 45       | F2                        | AUDIO_IN_AWS  | ı    | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio input word strobe                 |  |  |  |  |  |

| 44       | E1                        | AUDIO_IN_ABCK | I    | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio input bit clock                   |  |  |  |  |  |

| 50       | F1                        | AUDIO_IN_ADAT | I    | Pull-down                       | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio input serial data                 |  |  |  |  |  |

| Audio d  | output ir                 | nterfaces     |      |                                 |                   |                      |                                                 |  |  |  |  |  |

| 55       | G1                        | AWS           | I/O  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output word strobe                |  |  |  |  |  |

| 56       | НЗ                        | ABCK          | 1/0  | Pull-up                         | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output clock                      |  |  |  |  |  |

| 54       | G2                        | ADAT          | 0    | 1                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output serial data                |  |  |  |  |  |

| 53       | СЗ                        | ADAT2         | 0    | -                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output serial data channel 2      |  |  |  |  |  |

| 52       | E3                        | ADAT3         | 0    | -                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output serial data channel 3      |  |  |  |  |  |

| 43       | E2                        | SPDIF         | 0    | -                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output in SPDIF format            |  |  |  |  |  |

| 34       | ВЗ                        | BLEND         | 0    | 1                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output blend output               |  |  |  |  |  |

| 51       | G3                        | DAC256X       | 0    | -                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Digital audio output oversampling clock         |  |  |  |  |  |

| Clock    | & oscilla                 | ator          |      |                                 |                   |                      |                                                 |  |  |  |  |  |

| 57       | K2                        | CLK_IN        | I    | -                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | Reference digital clock                         |  |  |  |  |  |

| 66       | L1                        | OSC_IN        | ana  | -                               | 1.8 V             | Osc<br>supply        | 28,224MHz crystal in or digital clock input     |  |  |  |  |  |

| 67       | L2                        | OSC_OUT       | ana  | -                               | 1.8 V             | Osc<br>supply        | Crystal output                                  |  |  |  |  |  |

| SPI Fla  | sh inter                  | face          |      |                                 |                   |                      |                                                 |  |  |  |  |  |

| 78       | P4                        | SPI2_MISO     | I    | Pull-up                         | 1.8 V or<br>3.3 V | Flash IO<br>supply   | SPI interface 2 serial data master in/slave out |  |  |  |  |  |

| 74       | N3                        | SPI2_MOSI     | 0    | Pull-up                         | 1.8 V or<br>3.3 V | Flash IO<br>supply   | SPI interface 2 serial data master out/slave in |  |  |  |  |  |

| 75       | P3                        | SPI2_SS0_N    | 0    | Pull-up                         | 1.8 V or<br>3.3 V | Flash IO<br>supply   | SPI interface 2 active-low slave select 0       |  |  |  |  |  |

STA680 I/O description

Table 2. Pins description (continued)

| Table 2.      |           | is description (c  | •    | , , , , , , , , , , , , , , , , , , , |                   |                      | T                                               |

|---------------|-----------|--------------------|------|---------------------------------------|-------------------|----------------------|-------------------------------------------------|

| Pin #         | Ball#     | Signal name        | Туре | Pull-up<br>/down <sup>(1)</sup>       | Electrical        | Supply<br>group      | Description                                     |

| 77            | МЗ        | SPI2_SS1_N         | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Flash IO supply      | SPI interface 2 active-low slave select 1       |

| Not<br>bonded | M4        | SPI2_SS2_N         | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Flash IO<br>supply   | SPI interface 2 active-low slave select 2       |

| Not<br>bonded | M5        | SPI2_SS3_N         | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Flash IO<br>supply   | SPI interface 2 active-low slave select 3       |

| 76            | N4        | SPI2_SCK           | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Flash IO supply      | SPI interface 2 serial clock                    |

| SPI SD/       | MMC in    | terface            |      |                                       |                   |                      |                                                 |

| Not<br>bonded | C9        | SPI3_MISO          | I    | Pull-up                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 3 serial data master in/slave out |

| Not<br>bonded | C8        | SPI3_MOSI          | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 3 serial data master out/slave in |

| Not<br>bonded | D9        | SPI3_SS_N          | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 3 active-low slave select         |

| Not<br>bonded | C10       | SPI3_SCK           | 0    | Pull-up                               | 1.8 V or<br>3.3 V | Generic<br>IO supply | SPI interface 3 serial clock                    |

| SDRAM         | l interfa | ce                 |      |                                       |                   |                      |                                                 |

| 84            | P5        | SDR_FEED_CLK       | I    | -                                     | 3.3 V             | SDRAM<br>IO supply   | Feedback clock from SDRAM interface             |

| 83            | N5        | SDR_CLK_RAM<br>3V3 | 0    | -                                     | 3.3 V             | SDRAM<br>IO supply   | Clock to SDRAM for 3.3 V interface              |

| 97            | N9        | SDR_D0             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 0                  |

| 98            | P9        | SDR_D1             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 1                  |

| 101           | N10       | SDR_D2             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 2                  |

| 102           | P10       | SDR_D3             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 3                  |

| 103           | N11       | SDR_D4             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 4                  |

| 106           | P11       | SDR_D5             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 5                  |

| 107           | N12       | SDR_D6             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 6                  |

| 108           | P12       | SDR_D7             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 7                  |

| 96            | P8        | SDR_D8             | I/O  | -                                     | 3.3 V             | SDRAM<br>IO supply   | SDRAM bidirectional data bit 8                  |

I/O description STA680

Table 2. Pins description (continued)

| Pin #  | Ball# | Signal name | Туре | Pull-up              | Electrical | Supply             | Description                      |

|--------|-------|-------------|------|----------------------|------------|--------------------|----------------------------------|

| FIII # | Dall# | Signal name | туре | /down <sup>(1)</sup> | Electrical | group              | Description                      |

| 95     | P9    | SDR_D9      | I/O  | -                    | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 9   |

| 92     | M8    | SDR_D10     | I/O  | -                    | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 10  |

| 91     | P7    | SDR_D11     | I/O  | -                    | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 11  |

| 90     | N7    | SDR_D12     | I/O  | -                    | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 12  |

| 87     | M7    | SDR_D13     | I/O  | -                    | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 13  |

| 86     | P6    | SDR_D14     | I/O  |                      | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 14  |

| 85     | N6    | SDR_D15     | I/O  | ı                    | 3.3 V      | SDRAM<br>IO supply | SDRAM bidirectional data bit 15  |

| 111    | N13   | SDR_DQM0    | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Low-byte data input/output mask  |

| 112    | M13   | SDR_DQM1    | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | High-byte data input/output mask |

| 128    | G13   | SDR_WE_N    | 0    | ı                    | 3.3 V      | SDRAM<br>IO supply | Active-low write enable          |

| 129    | G12   | SDR_CAS_N   | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Active-low column address strobe |

| 130    | F13   | SDR_RAS_N   | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Active-low row address strobe    |

| 113    | M14   | SDR_CKE     | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Clock enable                     |

| 133    | F14   | SDR_CS_N    | 0    | 1                    | 3.3 V      | SDRAM<br>IO supply | Active-low chip select           |

| 134    | E13   | SDR_BA0     | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Bank select address 0            |

| 135    | E14   | SDR_BA1     | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Bank select address 1            |

| 139    | D14   | SDR_A0      | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Address bit 0 to SDRAM           |

| 140    | C13   | SDR_A1      | 0    | 1                    | 3.3 V      | SDRAM<br>IO supply | Address bit 1 to SDRAM           |

| 141    | C14   | SDR_A2      | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Address bit 2 to SDRAM           |

| 142    | B13   | SDR_A3      | 0    | -                    | 3.3 V      | SDRAM<br>IO supply | Address bit 3 to SDRAM           |

STA680 I/O description

Table 2. Pins description (continued)

| Pin #                                                                                 | Ball#                                                             | Signal name | Туре | Pull-up<br>/down <sup>(1)</sup> | Electrical | Supply<br>group    | Description                                                                                                                                                  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------|------|---------------------------------|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 127                                                                                   | H12                                                               | SDR_A4      | 0    | -                               | 3.3 V      | SDRAM<br>IO supply | Address bit 4 to SDRAM                                                                                                                                       |

| 124                                                                                   | H13                                                               | SDR_A5      | 0    | -                               | 3.3 V      | SDRAM<br>IO supply | Address bit 5 to SDRAM                                                                                                                                       |

| 123                                                                                   | J14                                                               | SDR_A6      | 0    | ı                               | 3.3 V      | SDRAM<br>IO supply | Address bit 6 to SDRAM                                                                                                                                       |

| 122                                                                                   | J13                                                               | SDR_A7      | 0    | -                               | 3.3 V      | SDRAM<br>IO supply | Address bit 7 to SDRAM                                                                                                                                       |

| 119                                                                                   | K14                                                               | SDR_A8      | 0    | -                               | 3.3 V      | SDRAM<br>IO supply | Address bit 8 to SDRAM                                                                                                                                       |

| 118                                                                                   | K13                                                               | SDR_A9      | 0    | ı                               | 3.3 V      | SDRAM<br>IO supply | Address bit 10 to SDRAM                                                                                                                                      |

| 138                                                                                   | D13                                                               | SDR_A10     | 0    | ı                               | 3.3 V      | SDRAM<br>IO supply | Address bit 10 to SDRAM                                                                                                                                      |

| 117                                                                                   | L14                                                               | SDR_A11     | 0    | -                               | 3.3 V      | SDRAM<br>IO supply | Address bit 11 to SDRAM                                                                                                                                      |

| 116                                                                                   | L13                                                               | SDR_A12     | 0    | -                               | 3.3 V      | SDRAM<br>IO supply | Address bit 12 to SDRAM                                                                                                                                      |

| Supplie                                                                               | es                                                                |             |      |                                 |            |                    |                                                                                                                                                              |

| Not<br>bonded                                                                         | F12                                                               | MODEOP_GEN  | I    | Pull-up                         | 3.3 V      | SDRAM<br>IO supply | Define the opereting voltage of<br>the "Generic I/O" supply group. If<br>tied low the I/Os work at 1.8V<br>else they work at 3.3V. Default<br>value is 3.3V. |

| Not<br>bonded                                                                         | E12                                                               | MODEOP_FSH  | -    | Pull-up                         | 3.3 V      | SDRAM<br>IO supply | Define the opereting voltage of<br>the "Flash I/O" supply group. If<br>tied low the I/Os work at 1.8V<br>else they work at 3.3V. Default<br>value is 3.3V.   |

| 8, 19,<br>28, 36,<br>46, 59,<br>71, 79,<br>89,<br>100,<br>109,<br>120,<br>131,<br>144 | D5,<br>D6,<br>E11,<br>F11,<br>J11,<br>J12,<br>K3,<br>K11,<br>K12, | VDD         | n/a  | -                               | 1.2 V      | Core<br>supply     | Power supply for core logic                                                                                                                                  |

I/O description STA680

Table 2. Pins description (continued)

| Pin #                                                                             | Ball#                                                                                                 | Signal name  | Туре | Pull-up<br>/down <sup>(1)</sup> | Electrical        | Supply<br>group         | Description                              |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------|------|---------------------------------|-------------------|-------------------------|------------------------------------------|

| 9, 20,<br>27, 37,<br>47, 58,<br>70, 80,<br>88, 99,<br>110,<br>121,<br>132,<br>143 | F6,<br>F7,<br>F8,<br>F9,<br>G6,<br>G7,<br>G8,<br>G9,<br>H6,<br>H7,<br>H8,<br>H9,<br>J6, J7,<br>J8, J9 | GND          | n/a  | -                               | ,                 | Core<br>supply          | Ground for core logic                    |

| 11, 22,<br>29, 38,<br>48                                                          | A5,<br>B5,<br>H1,<br>H2                                                                               | GND_GEN_IO   | n/a  | -                               | -                 | Generic<br>IO supply    | Generic I/Os ground                      |

| 12, 23,<br>30, 39,<br>49                                                          | A12,<br>B12,<br>D1,<br>D2                                                                             | VDD_GEN_IO   | n/a  | -                               | 1.8 V or<br>3.3 V | Generic<br>IO supply    | Generic I/Os power supply                |

| 72                                                                                | L6                                                                                                    | GND_FSH_IO   | n/a  | -                               | -                 | Flash IO supply         | Ground for Flash Interface I/Os          |

| 73                                                                                | L5                                                                                                    | VDD_FSH_IO   | n/a  | -                               | 1.8 V or<br>3.3 V | Flash IO supply         | Power supply for Flash Inteface I/Os     |

| 93,<br>104,<br>115,<br>126,<br>137                                                | H14,<br>L11,<br>L12,<br>M11,<br>M12                                                                   | GND_RAM_IO   | n/a  | -                               | -                 | SDRAM<br>IO supply      | Ground for SDRAM Interface I/Os          |

| 94,<br>105,<br>114,<br>125,<br>136                                                | G14,<br>M9,<br>M10                                                                                    | VDD_RAM_IO   | n/a  | -                               | 3.3 V             | SDRAM<br>IO supply      | Power supply for SDRAM<br>Interface I/Os |

| 60                                                                                | F3, F4                                                                                                | GND_PLL_DIG  | n/a  | -                               | -                 | PLL digital supply      | Ground for PLL digital part              |

| 61                                                                                | E4                                                                                                    | VDD_PLL_DIG  | n/a  | -                               | 1.2 V             | PLL digital supply      | Power supply for PLL digital part        |

| 62                                                                                | J4                                                                                                    | GND_PLL0_ANA | n/a  | -                               | -                 | PLL<br>analog<br>supply | Ground for PLL0 analog part (2)          |

| 62                                                                                | J3                                                                                                    | GND_PLL1_ANA | n/a  | -                               | -                 | PLL<br>analog<br>supply | Ground for PLL1 analog part (2)          |

STA680 I/O description

Table 2. Pins description (continued)

| Pin #         | Ball#     | Signal name        | Туре | Pull-up<br>/down <sup>(1)</sup> | Electrical | Supply<br>group         | Description                                      |

|---------------|-----------|--------------------|------|---------------------------------|------------|-------------------------|--------------------------------------------------|

| 63            | M2        | VDD_PLL0_ANA       | n/a  | -                               | 1.8 V      | PLL<br>analog<br>supply | Power supply for PLL0 analog part <sup>(3)</sup> |

| 63            | M1        | VDD_PLL1_ANA       | n/a  | -                               | 1.8 V      | PLL<br>analog<br>supply | Power supply for PLL1 analog part <sup>(3)</sup> |

| 64            | J2, L2    | GND_OSC            | n/a  | -                               | -          | Osc<br>supply           | Ground for oscillator core                       |

| 65            | J1        | VDD_OSC            | n/a  | -                               | 1.8 V      | Osc<br>supply           | Power supply for oscillator core                 |

| 68            | K4, L4    | VDD_REG3V3         | n/a  | -                               | 3.3 V      | LDO<br>supply           | Voltage regulator input power supply @ 3.3 Volt  |

| 69            | N1,<br>N2 | VDD_REG1V8         | n/a  | -                               | 1.8 V      | LDO<br>supply           | Voltage regulator output power supply@1.8 Volt   |

| 82            | L9        | VDD_RAM_IO<br>_1V8 | n/a  | -                               | 1.8 V      | n/a                     | Reserved - connect to 1.8 V supplyt              |

| 81            | L10       | GND_RAM_IO<br>_1V8 | n/a  | -                               | -          | n/a                     | Reserved - Connect to ground                     |

| Others        | Others    |                    |      |                                 |            |                         |                                                  |

| Not<br>bonded | M6        | RFU                | n/a  | -                               | n/a        | n/a                     | Reserved for future use - do not connect         |

Each input pin has a pull-up/down resistor to its default value. Unless otherwise specified, unused pins can be left unconnected after verifying that the impedance value of the pull-up/down resistor (see *Table 22*) is sufficient to guarantee noise immunity in user application environment.

<sup>2.</sup> In the LQFP package GND\_PLL0\_ANA and GND\_PLL1\_ANA are bonded together.

<sup>3.</sup> In the LQFP package VDD\_PLL0\_ANA and VDD\_PLL1\_ANA are bonded together.

I/O description STA680

## 4.4 I/Os supply groups

The STA680 I/O signals are arranged into three different supply groups: Generic IO supply, Flash IO supply and SDRAM IO supply group (see *Table 2*).

In the LQFP package option all three groups must be supplied with 3.3 V.

In the LFBGA package the three supply groups can independently operate at 3.3 V or 1.8 V.

- The SDRAM\_IO supply group must always be supplied at 3.3 V.

- The MODEOP\_GEN pin selects the operating voltage of the Generic\_IO supply group. If it is shorted to ground then all the I/O signals belonging to the Generic\_IO supply group will work at 1.8 V; if the MODEOP\_GEN pin is left floating or it is tied high (3.3 V) all the group I/Os will operate at 3.3 V.

- The MODEOP\_FSH pin selects the operating voltage of the Flash\_IO supply group. If it is shorted to ground then all the I/O signals belonging to the Flash\_IO supply group will work at 1.8 V; if the MODEOP\_FSH pin is left floating or it is tied high (3.3 V) the Flash Interface I/Os will operate at 3.3 V.

# 5 Operation and general remarks

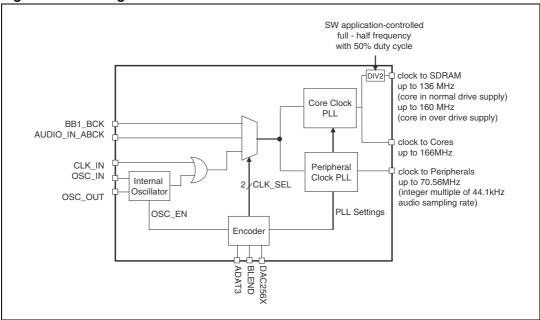

#### 5.1 Clock schemes

The STA680 needs an external clock source to feed the internal Phase Locked Loops (PLLs) to generate all the frequency needed by its cores and peripherals. This reference clock may be supplied in several ways thus offering flexibility in the development of the final application:

- The reference clock may be supplied through the use of an external crystal or as a digital signal coming from an external IC.

- The reference clock may have different frequencies and can be fed to the STA680 through different input pins.

The selection of the clock input mode is performed during the power-on phase of the device by latching the value of the pins ADAT3, BLEND and DAC256X on the rising edge of the RESET\_N signal (see *Chapter 5.2*); this value shall be selected according to *Table 3*.

Table 3. Reference clock configuration

| [ADAT3, BLEND,<br>DAC256X] | Clock type | Input pin            | Clock frequency<br>(MHz) |

|----------------------------|------------|----------------------|--------------------------|

| [0,0,0] <sup>(1)</sup>     | Crystal    | OSC_IN               | 28.224                   |

| [0,0,1]                    | Digital    | OSC_IN or CLK_IN (2) | 23.3472                  |

| [0,1,0]                    | Digital    | OSC_IN or CLK_IN (2) | 36.48                    |

| [0,1,1]                    | Digital    | OSC_IN or CLK_IN (2) | 2.9184                   |

| [1,0,0]                    | Digital    | BB1_BCK              | 10.4                     |

| [1,0,1]                    | Digital    | BB1_BCK              | 10.8                     |

| [1,1,0]                    | Digital    | BB1_BCK              | 14.112                   |

| [1,1,1]                    | Digital    | AUDIO_IN_ABCK        | 2.9184                   |

<sup>1.</sup> Default setting.

<sup>2.</sup> When using OSC\_IN pin to input the reference clock the CLK\_IN pin must be connected to ground and vice versa.

*Figure 8* shows a simplified version of the internal clock generation unit.

Figure 8. Clock generation unit

Some remarks on the choice of the clock input pin must be done:

- OSC IN is always a 1.8 V input pin.

- CLK\_IN, BB1\_BCK and AUDIO\_IN\_ABCK are 3.3 V pins when the LQFP package is selected while they can be configured as a 3.3 V or 1.8 V pins if the LFBGA is chosen (see Chapter 4.4)

- When the clock is fed through CLK\_IN pin, the OSC\_IN pin must be connected to ground. Similarly if the clock is fed using CLK\_IN pin then the OSC\_IN pin must be connected to ground.

- The BB1\_BCK pin is the bit clock of the digital interface to the baseband Tuner, so to fed the reference clock through this pin the selected clock frequency must be chosen accordingly to the Primary baseband Interface settings (see *Chapter 6.2*):

- 10.4 MHz = 16 \* 2 \* 650 kHz  $\rightarrow$  BBI set to 650 Ksample/s

- 10.8 MHz = 16 \* 2 \* 675 kHz  $\rightarrow$  BBI set to 675 Ksample/s

- 14.112 MHz = 16 \* 2 \* 882 kHz → BBI set to 882 Ksample/s

- The AUDIO\_IN\_ABCK is the bit clock of the digital audio input interface to the Tuner.

When this pin is selected as clock source the STA680 Input Serial Audio Interface (see Chapter 6.3.2) must be set according to following specification:

- Slave mode

- Input sample rate = 45.6 kHz

- Word length = 32 bit

With this settings the reference clock frequency is 2.9184 MHz = 32 \* 2 \* 45.6 kHz.

#### 5.2 Power on

This chapter describes the power-on procedure for the cold start (cold start means that the device is completely disconnected from the power supply before being turned on). *Figure 9* and *Table 4* show the timing for the power up sequence of the cold start.

Table 4. Power on timing parameters

| Symbol                          | Parameter                         | Min                      | Max                         | Unit |

|---------------------------------|-----------------------------------|--------------------------|-----------------------------|------|

| T <sub>ramp-up</sub>            | External supply ramp-up time      | Same ramp<br>3.3 V and 1 | -up time for<br>.2 V supply | -    |

| T <sub>DC1V8</sub>              | DC1V8 regulator start-up time     | -                        | 1                           | ms   |

| T <sub>OSC</sub> <sup>(1)</sup> | Oscillator start-up time          | -                        | 400                         | μs   |

| T <sub>RST</sub>                | Reset release time                | 10                       | -                           | μs   |

| T <sub>CFG</sub>                | Setup of clock/jtag configuration | 0.1                      | -                           | μs   |

Oscillator start-up time depends on the crystal connected to the internal oscillator. The given value is estimated for a crystal with these characteristics:

Figure 10. Crystal characteristics

#### 5.2.1 Power supply ramp up phase

All power supplies must be ramped-up to their specified levels within the time  $T_{Ramp-up}$ , set by the external power supply circuit on the board. The ramp up phase of each power domain should start at the same time.

The RESET\_N pin must be kept low since the beginning. For normal applications, the TESTMODE pin (Factory test mode enable, see *Table 2*) must be connected to ground.

#### 5.2.2 Oscillator setting time

Once the power supply has reached the operating level, the internal voltage regulator gets functional after  $T_{DC1V8} = 1$  s (see *Table 4*) and starts supplying the 1.8 V voltage to internal IPs such as PLLs and Crystal Oscillator.

The PLL is powered up but not yet functioning since the internal logic keeps it in bypass mode until a stable clock is available and STA680 has entered the secondary boot phase.

As shown in *Figure 9*, if an external crystal is connected to the internal oscillator this will output a correct waveform after  $T_{OSC} = 400 \, \mu s$  (see *Table 4*).

At this time, if no crystal is used, a digital clock must be supplied according to the instructions detailed in *Section 5.1*.

Either if an external crystal is used or the reference clock is provided through a digital source, the RESET\_N pin must be kept low for an additional  $T_{RST} = 1.1 \mu s$ .

As described in Section 5.1 the internal clock configuration is defined latching on the rising edge of the RESET\_N signal the value of the pins ADAT3, BLEND and DAC256X; the value of this three signals must be stable at least  $T_{CFG} = 0.1 \,\mu s$  before the leading edge of the RESET N signal.

#### 5.2.3 Boot sequence

Once the RESET\_N signal has been released and the power up sequence correctly performed, the STA680 enters the boot procedure, which consists of two phases consisting of device setup and application authentication and download.

During the first phase the STA680 executes the on-chip primary boot code contained in the 32 kilobyte Boot ROM. The primary boot synchronizes the internal cores, initializes the SPI and IIC interfaces and automatically selects the secondary boot code source by searching a pre-defined pattern into UART1, Flash, SPI1, IIC1 and IIC2.

26/47 Doc ID 14860 Rev 3

Once the device on which the secondary boot resides has been found, following tasks are performed: the code is authenticated, the SDRAM is initialized and the secondary boot code is downloaded into it.

The downloading speed depends on the device reference clock frequency even if this parameter does not have a big impact on the overall boot time since the dimension of this part of the code is small.

During the second phase of the boot procedure to achieve acceptable boot time the STA680 performs PLLs setup and takes the internal clock frequency to 28.224 MHz (see *Figure 9*) then downloads and validates the application code from the external Flash memory. This last task ends the boot procedure.

#### 5.2.4 Normal operation mode

After the execution of the boot code, the device enters the normal operation mode by jumping to the main program loop.

# 6 Digital I/O and memory interfaces

## 6.1 Interfaces: LQFP vs. LFBGA

The STA680 interface set depends on the package option selected, the LFBGA giving the maximum flexibility where the LQFP package has a slightly smaller set of interfaces, due to its smaller pin count.

The differences between the two package options are detailed in *Table 5*.

Table 5. Interface list

| Interface name                                      | Direction | LQFP | LFBGA |

|-----------------------------------------------------|-----------|------|-------|

| Baseband interface 1                                | I         | ✓    | 1     |

| Baseband interface 2 (data only)                    | I         | ✓    | 1     |

| I <sup>2</sup> S audio input                        | I         | ✓    | 1     |

| I <sup>2</sup> S audio output (six channels)        | 0         | ✓    | 1     |

| I <sup>2</sup> C primary interface (Micro)          | I/O       | ✓    | 1     |

| I <sup>2</sup> C secondary Interface                | I/O       | Х    | 1     |

| SPI micro interface                                 | I/O       | ✓    | 1     |

| SPI Flash interface (double chip select)            | I/O       | ✓    | 1     |

| SPI Flash interface extension (up to 4 chip select) | I/O       | Х    | 1     |

| SPI SD/MMC                                          | I/O       | Х    | 1     |

| SDRAM interface                                     | I/O       | ✓    | 1     |

| S/PDIF interface                                    | 0         | ✓    | 1     |

| UART interface                                      | I/O       | ✓    | 1     |

| 4 GPIO lines                                        | I/O       | Х    | 1     |

| JTAG test interface (boundary scan only)            | I/O       | ✓    | 1     |

#### 6.2 Tuner interface

The STA680 provides two digital baseband interfaces, named BBI1 and BBI2, through which the demodulated IBOC signals can enter the HD Radio decoder. The baseband Tuner accepts the analog signal from the RF Tuner, samples it, performs down conversion and filtering, and sends the zero-IF signal across a baseband interface (BBI) to the STA680.

Using two interfaces the STA680 is able to decode two channels at the same time, allowing the implementation of features such as the background scanning of HD Radio channels in search of traffic or weather information.

The BBI consists of four-wires, 16 bit wide I and Q data and two clocks. MSB is always transmitted first. All signals are assumed to be zero-if.

The native rate for FM is 744.1875 kS/s and for AM it is 46.51171875 kS/s. Sample rates of 650 kS/s, 675 kS/s, 882 kS/s and 912 kS/s are acceptable via the use of a sample rate converter.

BBI2 is similar to BBI1 except BBI2 doesn't have center filter so it is intended to be used for digital modulated signal only. For pin description refers to the *Table 5*.

Table 6. Baseband interfaces pin list

| Pin name | Designation                                | Туре | Drive |

|----------|--------------------------------------------|------|-------|

| BB1_WS   | Secondary base band interface word strobe  | I    | -     |

| BB1_BCK  | Primary baseband interface bit clock       | I    | -     |

| BB1_I    | Primary baseband interface serial I data   | I    | -     |

| BB1_Q    | Primary baseband interface serial Q data   | I    | -     |

| BB2_WS   | Secondary baseband interface word strobe   | I    | -     |

| BB2_BCK  | Secondary baseband interface bit clock     | I    | -     |

| BB2_I    | Secondary baseband interface serial I data | I    | -     |

| BB2_Q    | Secondary baseband interface serial Q data | I    | -     |

The data stream of the baseband interface varies depending on the mode selected.

Split mode splits I and Q data onto the BB1\_I and BB1\_Q pins, respectively. The rising and falling edges of BB1\_WS mark the beginning of each I and Q pair.

Multiplexed mode places the I and Q data onto the BB1\_I data pin. The falling edge of BB1\_WS marks the start of the I data and the rising edge marks the start of Q data.

AFE mode uses a single clock pulse on BB1\_WS to indicate the start of I data followed by Q data using the BB1\_I pin only.

Figure 11 show signals waveform for the three modes.

Figure 11. BBI waveforms and timings

In Table 7 are reported the timing values for the BB interface.

Table 7. BBI timing values

| Symbol Parameter |                               | Condition | Working rate |     |         |     | Unit     |      |

|------------------|-------------------------------|-----------|--------------|-----|---------|-----|----------|------|

| Symbol           | Parameter                     | Condition | Min.         |     |         |     | Max.     | Oill |

| Fws              | Word strobe                   | -         | 650          | 675 | 744.188 | 882 | 912      | kHz  |

| Fbck,split       | Bit clock in split mode       | -         | 16 x Fws     | -   | -       | -   | 66       | MHz  |

| Fbck,mux         | Bit clock in multiplexed mode | -         | 32 x Fws     | -   | -       | -   | 32 x Fws | MHz  |

| Fbck,afe         | Bit clock in AFE mode         | -         | 32 x Fws     | -   | -       | -   | 66       | MHz  |

| Th               | Data hold time                | -         | 4            | -   | -       | -   | -        | ns   |

| Ts               | Data setup time               | -         | 8            | -   | -       | -   | -        | ns   |

## 6.3 Audio interface (AIF)

The AIF (Audio Interface) is used for the communication with external digital signal sources and receivers. The main AIF features are:

- 1 Input SAI interface.

- 3 Output SAI interface.

- 1 S/PDIF transmitter.

- Audio Sample Rate Converter (ASRC).

- I/O sample rates: 44.1 kHz, 45.6 kHz, 48 kHz.

The AIF includes 1 Input SAI interface, 3 Output SAI interface and 1 S/PDIF (industry standard) transmitter. The receivers and transmitters can be used either in master-mode, running with the STA680 internal audio frequency of 44.1 kHz or in slave mode running with a frequency determined by the external device. In slave mode, in order to adapt the external data rate to the internal audio data rate, it is possible to use an internal Audio Sample Rate Converter (ASRC, see *Chapter 6.3.4*).

Table 8. AIF pin list

| Pin name      | Designation                                        | Туре | Drive |

|---------------|----------------------------------------------------|------|-------|

| AUDIO_IN_AWS  | Digital audio input word strobe                    | I/O  | -     |

| AUDIO_IN_ABCK | Digital audio input bit clock                      | I/O  | -     |

| AUDIO_IN_ADAT | Digital audio input serial data                    | I    | -     |

| AWS           | Digital audio output word strobe                   | I/O  | 4mA   |

| ABCK          | Digital audio output clock                         | I/O  | 4mA   |

| ADAT          | Digital audio output serial data                   | 0    | 4mA   |

| ADAT2         | Digital audio output serial data channel 2         | 0    | 4mA   |

| ADAT3         | Digital audio output serial data channel 3         | 0    | 4mA   |

| DAC256X       | Digital audio output oversampling clock (256 x Fs) | 0    | 4mA   |

| SPDIF         | Digital audio output in SPDIF format               | 0    | 4mA   |

| BLEND         | Digital audio output blend output                  | 0    | 4mA   |

#### 6.3.1 Output serial audio interface (SAI)

The output serial audio interface is used to send decoded audio samples from the HD Radio Decoder to an external IC for audio processing, or directly to a digital power amplifier.

The output SAI is an I2S interface which provides audio samples in stereo at a 44,1 kS/s sample rate. Other sample rates may be provided by means of the internal ASRC (see *Chapter 6.3.4*).

The output SAI interface shares the word strobe and the bit clock signal with three data output signals in order to support up to a total of 3 stereo channels of audio output. For interfacing the STA680 to an external DAC an oversampling clock whose frequency is 256 times the sampling frequency is provided. For pin description refers to *Table 8*.

The output SAI supports a 32x or 64x bit clock. The 32x clock mode shifts out serial data with no padding. The 64x clock mode shifts out the 16-bit audio data first followed by 16 bits of zero padding. *Figure 12* shows timing diagrams for the supported modes.

Figure 12. Serial audio interface waveforms and timings

In *Table 9* are reported the timing values for the output SAI interface.

Table 9. Serial audio interface timing values

| Symbol   | Parameter                 | Condition | Working rate |             | Unit      |     |

|----------|---------------------------|-----------|--------------|-------------|-----------|-----|

| Faws     | Word strobe               | -         | 44.1 ±10 Hz  | 45.6 ±15 Hz | 48 ±15 Hz | kHz |

| Fabck,16 | Bit clock for 16-bit data | -         | 32 x Faws    |             | MHz       |     |

| Fabck,32 | Bit clock for 32-bit data | -         | 64 x Faws    |             | MHz       |     |

| Th       | Data hold time            | -         | 5            |             | ns        |     |

| Ts       | Data setup time           | -         | 20           |             | ns        |     |

#### 6.3.2 Input serial audio interface

The input serial audio interface is used to receive the legacy AM/FM demodulated samples from an external AM/FM Tuner for blending purpose.

The input SAI is an I2S interface which accepts 16 bit audio samples in stereo at a 44,100 S/s sample rate. Other sample rates may be supported by means of the internal ASRC. For pin description refers to *Table 8*.

The input SAI supports a 32x or 64x bit clock. The 32x clock mode shifts out serial data with no padding. The 64x clock mode shifts out the 16-bit audio data first followed by 16 bits of zero padding. *Figure 12* shows timing diagrams for the supported modes.

#### 6.3.3 S/PDIF interface

The S/PDIF Interface is an output only. It is compliant to the standard IEC 958 type II. For pin description refers to *Table 8*.

32/47 Doc ID 14860 Rev 3

#### 6.3.4 Audio sample rate converter (ASRC)

The STA680 supports various external host audio interfaces. The audio sample rate converter is designed to interface the audio output to systems with local master audio clock sources.

Output sample rates of 44,100 ( $\pm$  10 Hz), 45,600 ( $\pm$  15 Hz) and 48,000 ( $\pm$  15 Hz) are acceptable. Total harmonic distortion plus noise (THD+N) at 1 kHz is greater than 85 dB down (0.0056%).

One stereo channel (i.e. single ADAT line) either from the input SAI or from the output SAI can be used with the audio sample rate converter.

In applications where the STA680 supplies the master clock to the audio D/A converter, the ASRC will be bypassed.

## 6.4 Serial peripheral interfaces (SPI)

The STA680 provides three serial peripheral interfaces, each one intended for a different and specific purpose:

- SPI1 The first SPI is intended for communicating with the Host Microcontroller.

Alternatively to this purpose can be also the Host Micro I<sup>2</sup>C Interface (see Chapter 6.4.1)

- SPI2 The second SPI has been taught to interface the STA680 with the external an external flash typically used to store the application code.

- SPI3 The third SPI allow the HD Radio decoder to control an external SD/MMC card.