# RAIO RA8808

# 128x64 Driver for Dot Matrix LCD

**Specification**

Version 1.0

March 26, 2009

RAiO Technology Inc.

©Copyright RAiO Technology Inc. 2009

#### 1. General Description

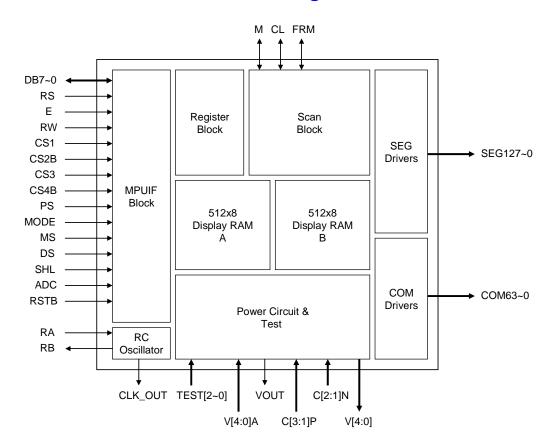

The RA8808 is a LCD driver LSI with 128(Segment)  $\times$  64(Common) driver output for dot matrix liquid crystal graphic display systems. This device consists of the display RAM,128-bit segment drivers, 64-bit common drivers and decoder logic. It has the internal display RAM for storing the display data transferred from an 8-bit 8080/6800 micro controller or 3-wire-SPI/IIC controller and generates the dot matrix liquid crystal driving signals corresponding to stored data.

#### 2. Features

- Dot matrix LCD segment driver with 128 channel output, and common driver with 64 channel output.

- Internal timing generator circuit for dynamic display.

- Selection of master/slave mode for combine two RA8808 controller to support 256x64 dot Matrix.

- ◆ Applicable LCD common duty: 1/48, 1/64.

- ◆ Support 6800/8080 8-bit parallel MPU interface.

- Support 3-wires SPI and IIC serial MPU interface.

- ◆ Two 512 bytes (4096-bits) Display RAM

- ♦ LCD driving voltage: 8V ~17V

- Built-in 2X~4X Voltage Booster and Voltage Follower

- ◆ Power supply voltage: +2.7V ~ 5.5V

- ♦ High voltage CMOS process

- ◆ Bare gold bump chip available

#### 3. Block Diagram

# 4. Pad Diagram

# 5. Pin Description

#### 5-1 MPU Interface

| Pin Name | I/O | Description                                                                                                                                                                                                                                                     |                                                                                                                                              |  |  |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | I/O | In Parallel Mode: Data Bus These are data bus for data transfer between MPU(6800/8080) and RA8808. In Serial Mode:                                                                                                                                              |                                                                                                                                              |  |  |

|          |     | Pin                                                                                                                                                                                                                                                             | Description                                                                                                                                  |  |  |

|          |     | DB7<br>DB6                                                                                                                                                                                                                                                      | These pins are not used and must be connected to low.                                                                                        |  |  |

|          |     | DB5                                                                                                                                                                                                                                                             | In IIC Interface : These pins are used as the IIC device address input.                                                                      |  |  |

|          |     | DB4                                                                                                                                                                                                                                                             | (SA[2:0]) In SPI Interface :                                                                                                                 |  |  |

| DB0~DB7  |     | DB3                                                                                                                                                                                                                                                             | These pins are not used and must be connected to high or low.                                                                                |  |  |

|          |     | DB2                                                                                                                                                                                                                                                             | In IIC Interface: This pin is not used and must be connected to low. In SPI Interface: This pin is used as Chip selection, active low. (ZCS) |  |  |

|          |     | DB1                                                                                                                                                                                                                                                             | In IIC Interface: This pin is used as Bi-direction serial Data.(SDA) In SPI Interface: This pin is used as Bi-direction serial Data.(SDA)    |  |  |

|          |     | DB0                                                                                                                                                                                                                                                             | In IIC Interface: This pin is used as serial clock.(SCL) In SPI Interface: This pin is used as serial clock.(SCK)                            |  |  |

| E        | I   | In Parallel Mode: Enable or Read Control When use 6800 series interface, this pin is used as Enable, active high. When use 8080 series interface, this pin is used as data read, active low. In Serial Mode: This pin is not used and must be connected to low. |                                                                                                                                              |  |  |

| RW          | 1 | In Parallel Mode: Read-Write Control or Write Control When use 6800 series interface, this pin is used as data read/write control. Active high for read and active low for write. When use 8080 series interface, this pin is used as data write, active low. In Serial Mode: This pin is not used and must be connected to low. |            |                        |     |  |

|-------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|-----|--|

| RS          | I | In Parallel Mode:  Data or Instruction  RS = H → DB0~DB7: Display RAM data  RS = L → DB0~DB7: Instruction data  In Serial Mode:  This pin is not used and must be connected to low.                                                                                                                                              |            |                        |     |  |

| CS1<br>CS2B | 1 | In Parallel Mode: Chip selection for left side (Note 1) In order to interface left side data for input or output, the terminals have to be CS1 = H, CS2B = L. In Serial Mode: These pins are not used and must be connected to high or low.                                                                                      |            |                        |     |  |

| CS3<br>CS4B | I | In Parallel Mode: Chip selection for right side (Note 1) In order to interface right side data for input or output, the terminals have to be CS3 = H, CS4B = L. In Serial Mode: These pins are not used and must be connected to to high or low.                                                                                 |            |                        |     |  |

| RSTB        | I | Reset Signal When RSTB = L, _ON/OFF register becomes set by 0. (display off) _Display start line register becomes set by 0.(Z-address 0 set, display from line 0) After releasing reset, this condition can be changed only by instruction.                                                                                      |            |                        |     |  |

|             | I | Parallel/Serial MPU Interface Selection                                                                                                                                                                                                                                                                                          |            |                        |     |  |

| PS          |   | PS                                                                                                                                                                                                                                                                                                                               | Paralle    |                        |     |  |

|             |   | H<br>L                                                                                                                                                                                                                                                                                                                           | Para<br>Se |                        |     |  |

|             |   | MPU Interface Selection(Combine with PS)                                                                                                                                                                                                                                                                                         |            |                        |     |  |

|             | I | PS                                                                                                                                                                                                                                                                                                                               | MODE       | MPU Interf             | ace |  |

| MODE        |   | Н                                                                                                                                                                                                                                                                                                                                | H          | 6800 seri              |     |  |

|             |   | H<br>L                                                                                                                                                                                                                                                                                                                           | L<br>H     | 8080 seri<br>3-wire SI |     |  |

|             |   |                                                                                                                                                                                                                                                                                                                                  | '          | J-WILE OF              |     |  |

#### **5-2 LCD Panel Interface**

| Pin Name        | I/O | Description                                                                                                                                                                                          |                                                      |         |                                  |  |

|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------|----------------------------------|--|

| SEG0~<br>SEG127 | 0   | LCD Segment Driver Output Display RAM data 1 : On, Display RAM data 0 : Off Relation of display RAM & M :                                                                                            |                                                      |         |                                  |  |

|                 |     | M<br>L<br>L<br>H                                                                                                                                                                                     | Data L H L H                                         | \       | /t Level<br>/2<br>/0<br>/3<br>ND |  |

|                 |     |                                                                                                                                                                                                      | al Output for LCD Dri<br>mon signal & M:             | ving    |                                  |  |

| COM0~           |     | M                                                                                                                                                                                                    | Common Signal                                        | Ou      | tput Level                       |  |

| COM63           | 0   | L                                                                                                                                                                                                    | L                                                    |         | V1                               |  |

|                 |     | L                                                                                                                                                                                                    | H                                                    |         | GND                              |  |

|                 |     | Н                                                                                                                                                                                                    | L L                                                  |         | V4                               |  |

|                 |     | H                                                                                                                                                                                                    | Н                                                    |         | V0                               |  |

| М               | I/O | Alternating Signal Input for LCD Driving. The input/output selection is determined by MS.                                                                                                            |                                                      |         |                                  |  |

| CL              | I/O | Display Synchronous Signal Display data is latched at rising time of the CL signal and increments the Z- address counter at CL falling time. The input/output selection is determined by MS.         |                                                      |         |                                  |  |

| FRM             | I/O | Synchronous Control Signal  Presets the 6-bit Z counter and synchronizes the common signal with the frame signal when the frame signal becomes high. The input/output selection is determined by MS. |                                                      |         |                                  |  |

|                 |     | Master/Slave Mode Selection                                                                                                                                                                          |                                                      |         |                                  |  |

| MS              | I   |                                                                                                                                                                                                      | Master/Slave Mod  Master Slave  mode, M, CL, FRM are | e outpu |                                  |  |

|                 |     | When in Slave mode, M, CL, FRM are input pins.                                                                                                                                                       |                                                      |         |                                  |  |

#### 5-3 Clock

| Pin Name | I/O | Description                                                                                                                                                                                                             |  |  |  |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RA       | I   | In internal clock mode, this pin connects to external resistor for RC circuit.  In external clock mode, this pin is an input of external clock.  Internal Clock Mode  RA8808  RA8808  RA RB  RA RB  External Clock Open |  |  |  |

| RB       | 0   | In internal clock mode, this pin connects to external resistor for RC circuit. In external clock mode, this pin must keep floating.                                                                                     |  |  |  |

| CLK_OUT  | 0   | Internal system clock output for cascade application or others for user.                                                                                                                                                |  |  |  |

## 5-4 Power

| Pin Name    | I/O | Description                                                                                  |

|-------------|-----|----------------------------------------------------------------------------------------------|

| VOUT        | 0   | Regulator Voltage Output                                                                     |

| VDD<br>VDDP | Р   | Digital Power                                                                                |

| GND<br>GNDP | Р   | Digital Ground                                                                               |

| AVDD        | Р   | Analog Power                                                                                 |

| AGND        | Р   | Analog Ground                                                                                |

| C1N<br>C1P  | I   | Capacitor Input These are used to connect a capacitor for internal Booster.                  |

| C2N<br>C2P  | I   | Capacitor Input These are used to connect a capacitor for internal Booster.                  |

| СЗР         | I   | Capacitor Input These are used to connect a capacitor for internal Booster.                  |

| V0A~V4A     | I   | Voltage Input                                                                                |

| V0~V4       | 0   | Voltage Source of LCD Driver  The relationship of the power is V0 > V1 > V2 > V3 > V4 > GND. |

## **5-5 MISC**

| Pin Name                | I/O | Description                                                                                                                 |  |  |  |

|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                         |     | Selection of Segment Data Direction                                                                                         |  |  |  |

| ADC                     | 1   | ADC         Common Data Shift Direction           H         SEG0 → SEG1 → SEG127           L         SEG127 → SEG126 → SEG0 |  |  |  |

|                         |     | Selection of Common Data Shift Direction                                                                                    |  |  |  |

| SHL                     | ı   | SHL       Common Data Shift Direction         H       COM0 → COM1 → COM63         L       COM63 → COM62 → COM0              |  |  |  |

|                         |     | Selection of Display Duty                                                                                                   |  |  |  |

| DS                      | I   | DS         Duty           H         1/64           L         1/48                                                           |  |  |  |

| TEST0<br>TEST1<br>TEST2 | I   | These pins must contact to GND in normal mode.                                                                              |  |  |  |

www.raio.com.tw

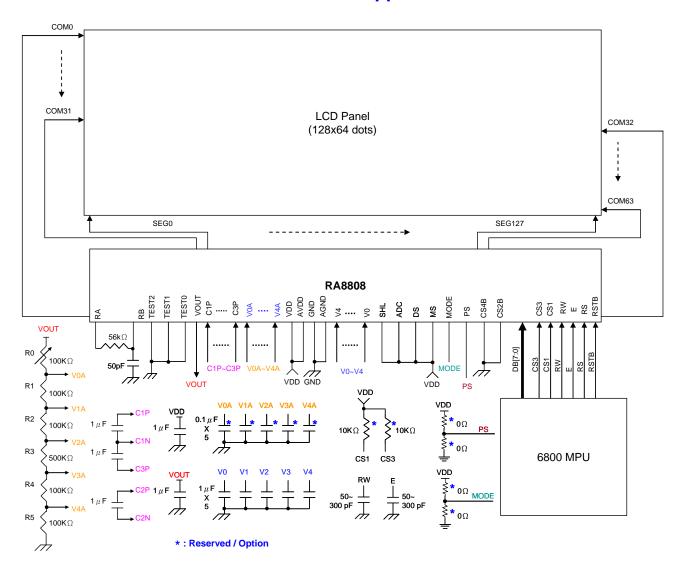

# 6. LCD Panel Interface Application Circuit