# FAH4840 Haptic Driver for Linear Resonant Actuators (LRAs)

## Features

- Direct Drive of LRA (Linear Resonant Actuator)

- External PWM Input (10 kHz to 250 kHz) with Divider

- Internal Motor Enable / Disable Input

- Auto Resonant Tracking

- LDO Provides Stable Haptic Effect with Battery Depletion

- Low Shutdown Current: < 5 nA</p>

- Fast Wake-Up Time

- Nearly Rail-to-Rail Output Swing

- Thermal Shutdown, Over-Current Shutdown

- Register-Based Control by I<sup>2</sup>C

- Immersion TouchSense® 3000 Certified

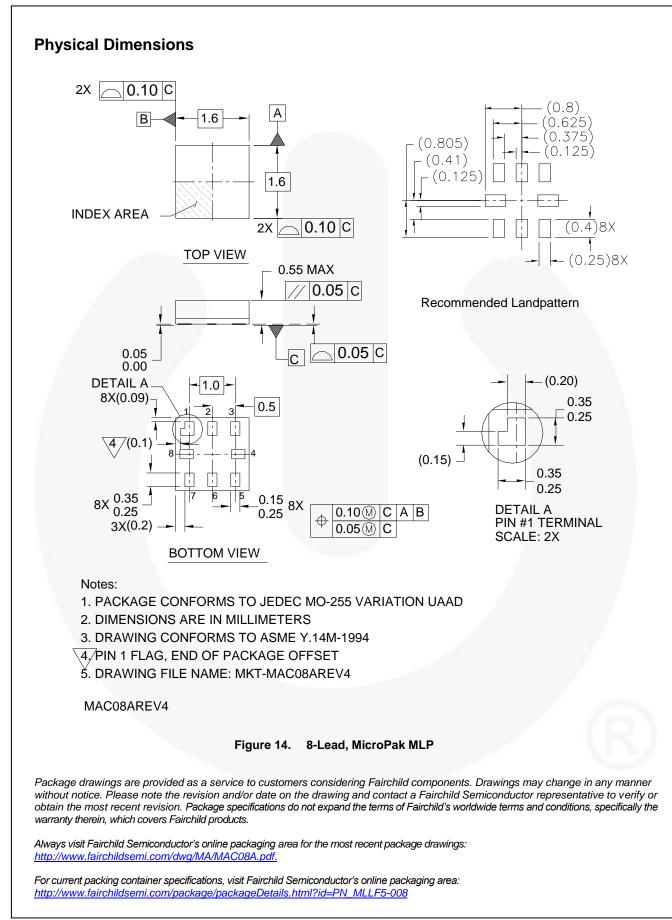

- Package: 8- Lead MicroPak™ MLP

All trademarks are the property of their respective owners.

# Description

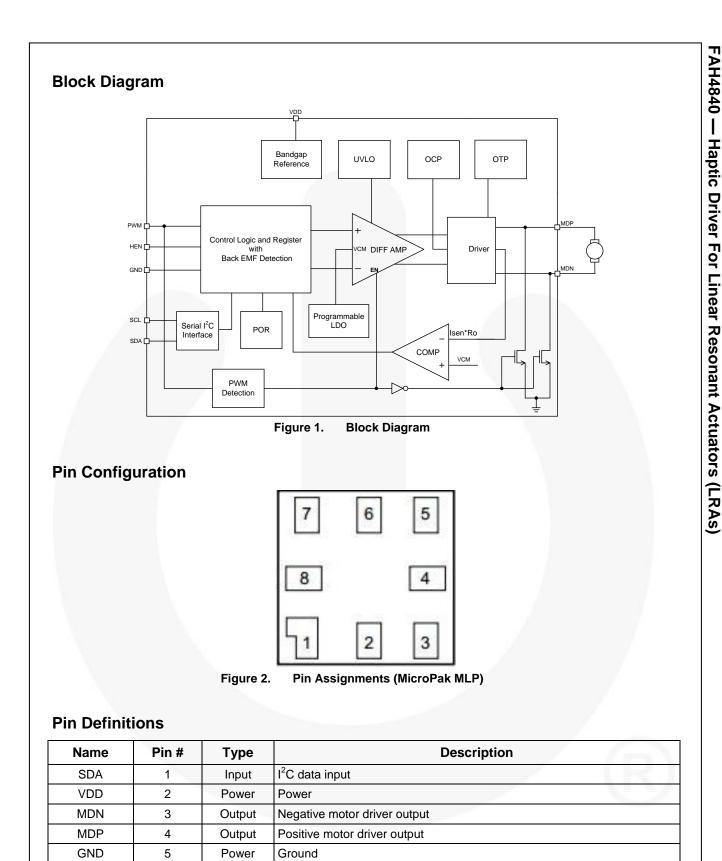

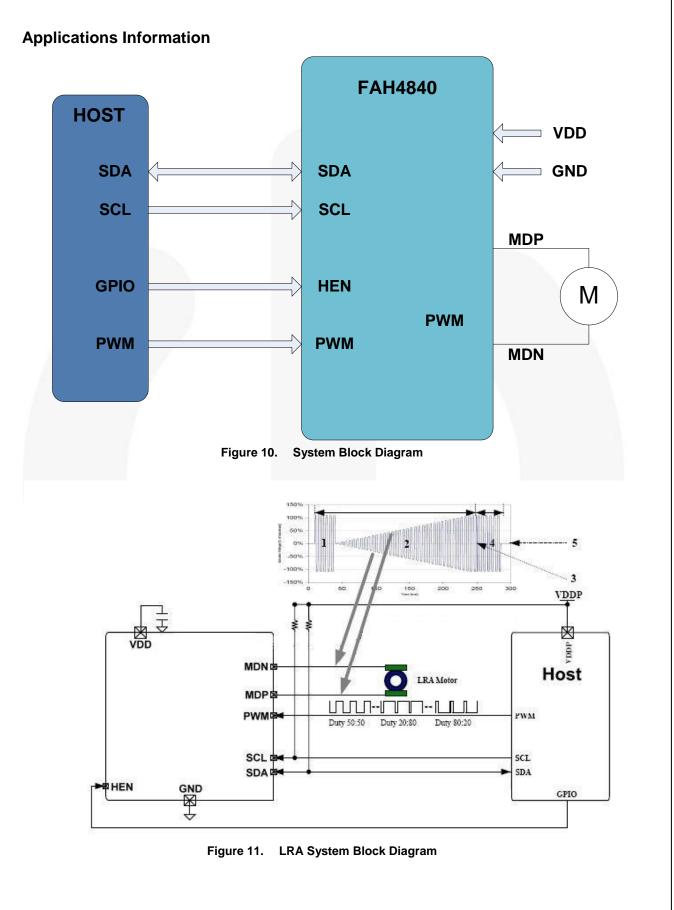

The FAH4840 is a high-performance amplifier for mobile phones and other hand-held devices. The haptic driver takes a single-ended PWM input signal to control a Linear Resonant Actuator (LRA). The device utilizes an external 10 kHz to 250 kHz PWM signal capable of meeting the wide range of resonant frequencies needed for an LRA haptics applications. The FAH4840 register map is accessible through an I<sup>2</sup>C serial communication port.

# **Applications**

- Mobile Phones

- Handheld Devices

- Any Key pad interface

# **Ordering Information**

| Part Number | Top Mark | Operating Temperature Range | Package       | Packing Method | Quantity |

|-------------|----------|-----------------------------|---------------|----------------|----------|

| FAH4840L8X  | YB       | -40°C to +85°C              | MicroPak™ MLP | Reel           | 5000     |

6

7

8

PWM

SCL

HEN

Haptic motor enable/disable (HIGH: enable, LOW: disable)

**PWM** input

I<sup>2</sup>C clock input

Input

Input

Input

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol          | Parameter                                          | Min. | Max.                 | Unit |

|-----------------|----------------------------------------------------|------|----------------------|------|

| V <sub>DD</sub> | DC Supply Voltage                                  | -0.3 | 6.0                  | V    |

| V <sub>IO</sub> | Analog and Digital I/O (All Input and Output Pins) | -0.3 | V <sub>CC</sub> +0.3 | V    |

# **Reliability Information**

| Symbol           | Parameter                 | Min. | Тур. | Max. | Unit |

|------------------|---------------------------|------|------|------|------|

| TJ               | Junction Temperature      |      |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range | -65  |      | +150 | °C   |

# **Electrostatic Discharge Information**

| Symbol   | Parameter                                     | Max. | Unit |

|----------|-----------------------------------------------|------|------|

| ESD      | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 | 4    | kV   |

| E9D      | Charged Device Model, JESD22-C101             | 1    | ĸv   |

| Latch-Up | Test Condition for Latch-Up Current           | ±150 | mA   |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            | Parameter                   | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------|------|------|------|------|

| T <sub>A</sub>    | Operating Temperature Range | -40  |      | +85  | °C   |

| V <sub>DD</sub>   | Supply Voltage Range        | 2.5  | 3.3  | 4.3  | V    |

| Z <sub>LOAD</sub> | Load impedance              | 15   | 25   | 50   | Ω    |

# **Dissipation Ratings**

This thermal data is measured with a high-K board (four-layer board, according to the JESD51-7 JEDEC standard.)

| Package             | θ <sub>JA</sub> | Unit |

|---------------------|-----------------|------|

| 8-Lead MicroPak MLP | 280             | °C/W |

# FAH4840 — Haptic Driver For Linear Resonant Actuators (LRAs)

# **DC Electrical Characteristics**

$T_A = 25^{\circ}C$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $V_{REG}=2.0 \text{ V}$ , unless otherwise noted.

| Symbol              | Parameter                   | Conditions                                                                                                                                                                                                                         | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| <b>f</b> IPWM       | PWM Input Frequency         | Square Wave Input                                                                                                                                                                                                                  | 10   |      | 250  | kHz  |

| $IIH_PWM$           | Input Current               | PWM = 1.8 V                                                                                                                                                                                                                        |      | 1    | 3    | μA   |

| IIH <sub>HEN</sub>  | Input Current               | HEN = 1.8 V                                                                                                                                                                                                                        |      | 1    | 3    | μA   |

| IIL <sub>PWM</sub>  | Input Current               | PWM = 0 V                                                                                                                                                                                                                          |      | 1    | 3    | μΑ   |

| IIL <sub>HEN</sub>  | Input Current               | HEN = 0 V                                                                                                                                                                                                                          |      | 1    | 3    | μΑ   |

| VIH                 | Input Logic HIGH (HEN, PWM) |                                                                                                                                                                                                                                    | 1.15 |      |      | V    |

| VIL                 | Input Logic LOW (HEN, PWM)  |                                                                                                                                                                                                                                    |      |      | 0.5  | V    |

| CIN                 | Input Capacitance           | PWM Capacitance to GND or 1.8 V                                                                                                                                                                                                    |      | 6    | 10   | pF   |

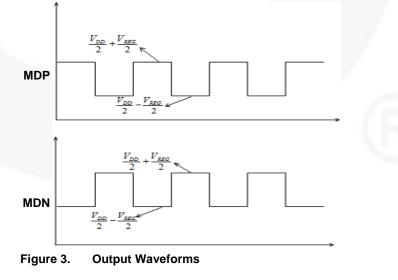

| V <sub>OL</sub>     | Output Voltage              | $      V_{\text{DD}} = 3.3 \text{ V},  \text{R}_{\text{L}} = 15 \Omega,  \text{V}_{\text{OL}} = \text{V}_{\text{OL}(\text{measure})^{-}} \\ (\text{V}_{\text{CM}} \text{-} \text{V}_{\text{REG}}/2),  \text{See Waveforms Below} $ |      | 0.02 |      | mV   |

| V <sub>OH</sub>     | Output Voltage              | $      V_{DD} = 3.3 \text{ V},  \text{R}_{L} = 15 \Omega,  \text{V}_{OH} = \text{V}_{OH(measure)} - (\text{V}_{CM} - \text{V}_{REG}/2),  \text{See Waveforms Below} $                                                              |      | 1.95 |      | V    |

| I <sub>OUT</sub>    | Output Drive Current        | $V_{DD}$ =3.3 V, $V_{REG}$ =3.0 V, $R_L$ = 15 $\Omega$                                                                                                                                                                             |      | 200  |      | mA   |

| I <sub>OUTSCP</sub> | Short-Circuit Protection    | V <sub>DD</sub> =3.3 V, V <sub>REG</sub> =3.0 V, MDP and<br>MDN Shorted Together and Each<br>Shorted to Ground                                                                                                                     |      | 350  | 400  | mA   |

| I <sub>DD1</sub>    | Supply Current              | $\label{eq:pwm} \begin{array}{l} PWM = 22.4 \ kHz \ 50\% \ Duty, \ HEN = \\ HIGH, \ R_{L} = \ No \ Load \end{array}$                                                                                                               |      | 2    | 5    | mA   |

| I <sub>DD2</sub>    | Supply Current              | PWM=22.4 kHz 90/10% Duty, HEN = HIGH, $R_L$ = 25 $\Omega$                                                                                                                                                                          |      | 77   |      | mA   |

| I <sub>DD3</sub>    | Supply Current              | PWM,HEN = 0 V, $R_L$ = 25 $\Omega$                                                                                                                                                                                                 |      | 15   |      | μA   |

| I <sub>DD4</sub>    | Supply Current              | PWM, HEN=0 V, V <sub>DD</sub> =2.5 V, Address<br>0 Bit 7 Set to Zero                                                                                                                                                               |      | 2.0  |      | nA   |

| V <sub>REG</sub>    | Output Voltage Range        | Measure V <sub>REG</sub> , V <sub>DD</sub> per Table                                                                                                                                                                               | 1.4  | 2.0  | 3.2  | V    |

| V <sub>REGA</sub>   | Output Voltage Accuracy     | Measure V <sub>REG</sub>                                                                                                                                                                                                           | -2.5 |      | 2.5  | %    |

# **AC Electrical Characteristics**

| Symbol          | Parameter               | Conditions                                                                                        | Min. | Тур. | Max.  | Unit |

|-----------------|-------------------------|---------------------------------------------------------------------------------------------------|------|------|-------|------|

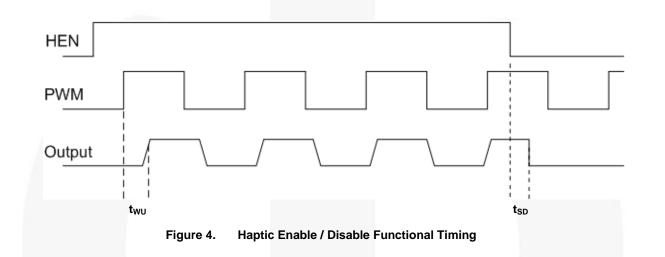

| t <sub>WU</sub> | Wake-Up Time            | PWM=80/20% Duty Cycle, HEN/PWM LOW<br>to HIGH, Measurement Point PWM = 50%,<br>Output Point = 90% |      | 1    | 150   | μs   |

| t <sub>SD</sub> | Shutdown Time           | PWM=80/20% Duty Cycle, HEN HIGH to<br>LOW, Measurement Point HEN = 50%,<br>Output Point = 90%     |      | 0.2  | 150.0 | μs   |

| Restrk          | Auto Resonance Tracking | PWM=22.4 kHz 80/20% Duty, R <sub>L</sub> = 25 Ω                                                   | -2.5 |      | 2.5   | Hz   |

# Table 1.VDD vs. VREG Supply Values

|                      |     | V <sub>DD</sub> | (V) |     |

|----------------------|-----|-----------------|-----|-----|

|                      | 2.5 | 2.7             | 3.0 | 3.3 |

|                      | 1.4 | 1.4             | 1.4 | 1.4 |

|                      | 1.6 | 1.6             | 1.6 | 1.6 |

|                      | 1.8 | 1.8             | 1.8 | 1.8 |

| V <sub>REG_OUT</sub> | 2.0 | 2.0             | 2.0 | 2.0 |

| (Programmed Voltage) | 2.2 | 2.2             | 2.2 | 2.2 |

|                      | 2.4 | 2.4             | 2.4 | 2.4 |

|                      |     | 2.6             | 2.6 | 2.6 |

|                      |     |                 | 2.8 | 2.8 |

|                      |     |                 |     | 3.0 |

|                      |     |                 |     | 3.2 |

# I<sup>2</sup>C DC Electrical Characteristics

$T_{\text{A}}$  = 25°C,  $V_{\text{DD}}$  = 3.3 V,  $V_{\text{REG}}$  =2.0 V, unless otherwise noted.

| Symbol          | Parameter                                                                    |      | Fast Mode (400 kHz) |      |  |  |

|-----------------|------------------------------------------------------------------------------|------|---------------------|------|--|--|

| Symbol          |                                                                              |      | Max.                | Unit |  |  |

| V <sub>IL</sub> | Low-Level Input Voltage                                                      | -0.3 | 0.6                 | V    |  |  |

| VIH             | High-Level Input Voltage                                                     | 1.3  |                     | V    |  |  |

| V <sub>OL</sub> | Low-Level Output Voltage at 3 mA Sink Current (Open-Drain or Open-Collector) | 0    | 0.4                 | V    |  |  |

| IIн             | High-Level Input Current of Each I/O Pin, Input Voltage=V <sub>SVDD</sub>    | -1   | 1                   | μA   |  |  |

| IIL             | Low-Level Input Current of Each I/O Pin, Input Voltage=0 V                   | -1   | 1                   | μA   |  |  |

# I<sup>2</sup>C AC Electrical Characteristics

$T_A = 25^{\circ}C$ ,  $V_{DD} = 3.3 V$ ,  $V_{REG}=2.0 V$ , unless otherwise noted.

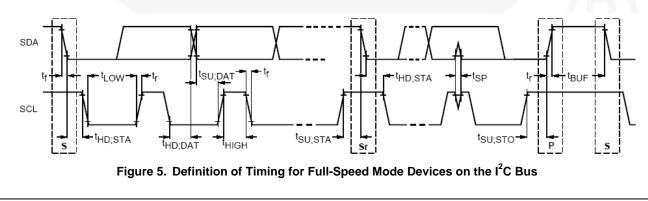

| 0                   | Deremeter                                                         | Fast     | /lode (400 | kHz) |

|---------------------|-------------------------------------------------------------------|----------|------------|------|

| Symbol              | Parameter                                                         | Min.     | Max.       | Unit |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0        | 400        | kHz  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6      |            | μs   |

| t <sub>LOW</sub>    | Low Period of SCL Clock                                           | 1.3      |            | μs   |

| t <sub>HIGH</sub>   | High Period of SCL Clock                                          | 0.6      |            | μs   |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition                          | 0.6      |            | μs   |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0        | 0.9        | μs   |

| t <sub>SU;DAT</sub> | Data Set-up Time <sup>(1)</sup>                                   | 100      |            | ns   |

| tr                  | Rise Time of SDA and SCL Signals <sup>(2)</sup>                   | 20+0.1Cb | 300        | ns   |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(2)</sup>                   | 20+0.1Cb | 300        | ns   |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                    | 0.6      |            | μs   |

| t <sub>BUF</sub>    | BUS-Free Time between STOP and START Conditions                   | 1.3      |            | μs   |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0        | 50         | ns   |

Notes:

A Fast-Mode I<sup>2</sup>C Bus® device can be used in a Standard-Mode I<sup>2</sup>C bus system, but the requirement t<sub>SU;DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the Serial Data (SDA) line t<sub>r\_max</sub> + t<sub>SU;DAT=</sub>1000 + 250=1250 ns (according to the Standard-Mode I<sup>2</sup>C Bus specification) before the SCL line is released.

C<sub>b</sub> equals the total capacitance of one bus line in pf. If mixed with High-Speed Mode devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

# **Functional Description**

# I<sup>2</sup>C Control

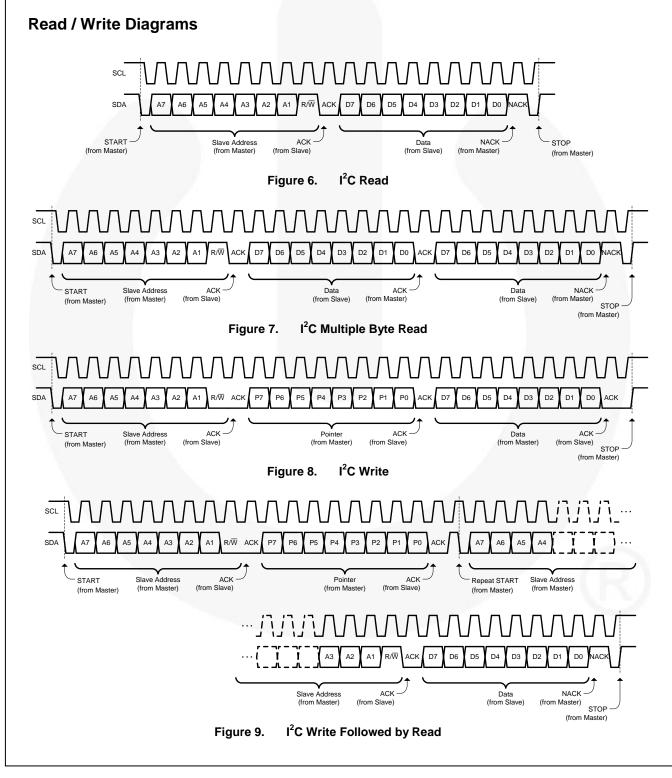

Writing to and reading from registers is accomplished via the  $I^2C$  interface. The  $I^2C$  protocol requires that one device on the bus initiates and controls all read and write operations. This device is called the "master" device. The master device generates the SCL signal, which is the clock signal for all other devices on the bus. All other devices on the bus are called "slave" devices. The FAH4840 is a slave device. Both the master and slave devices can send and receive data on the bus.

During I<sup>2</sup>C operations, one data bit is transmitted per clock cycle. All I<sup>2</sup>C operations follow a repeating nineclock-cycle pattern that consists of eight bits (one byte) of transmitted data followed by an acknowledge (ACK) or not acknowledge (NACK) from the receiving device. There are no unused clock cycles during any operation; therefore, there must be no breaks in the stream of data and ACKs/NACKs during data transfers.

For most operations,  $l^2C$  protocol requires the SDA line to remain stable (unmoving) whenever SCL is HIGH; i.e. transitions on the SDA line can only occur when SCL is LOW. The exceptions to this rule are when the master device issues a START or STOP condition. The slave device cannot issue a START or STOP condition.

**START Condition:** This condition occurs when the SDA line transitions from HIGH to LOW while SCL is HIGH. The master device uses this condition to indicate that a data transfer is about to begin.

**STOP Condition:** This condition occurs when the SDA line transitions from LOW to HIGH while SCL is HIGH. The master device uses this condition to signal the end of a data transfer.

Acknowledge and Not Acknowledge: When data is transferred to the slave device, the slave device sends acknowledge (ACK) after receiving every byte of data. The receiving device sends an ACK by pulling SDA LOW for one clock cycle.

When the master device is reading data from the slave device, the master sends an ACK after receiving every byte of data. Following the last byte, a master device sends a "not acknowledge" (NACK) instead of an ACK, followed by a STOP condition. A NACK is indicated by leaving SDA HIGH during the clock after the last byte.

## **Slave Address**

Each slave device on the bus must have a unique address so the master can identify the device sending or receiving data. The FAH4840 slave address is 0000110X binary or 06 HEX where "X" is the read/write bit. Master write operations are indicated when X=0. Master read operations are indicated when X=1.

## Writing to and Reading from the FAH4840

All read and write operations must begin with a START condition generated by the master. After the START condition, the master must immediately send a slave address (7 bits), followed by a read/write bit. If the slave address matches the address of the FAH4840, the FAH4840 sends an ACK after receiving the read/write bit by pulling the SDA line LOW for one clock cycle.

# **Setting the Pointer**

For all operations, the pointer stored in the command register must be pointing to the register that is going to be written or read. To change the pointer value in the command register, the read/write bit following the address must be 0. This indicates that the master writes new information into the command register.

After the FAH4840 sends an ACK in response to receiving the address and read/write bit, the master must transmit an appropriate 8-bit pointer value, as explained in the  $I^2C$  Registers section. The FAH4840 sends an ACK after receiving the new pointer data.

The pointer set operation is illustrated in Figure 8 and Figure 9. Any time a pointer set is performed, it must be immediately followed by a read or write operation. The command register retains the current pointer value between operations; therefore, once a register is indicated, subsequent read operations do not require a pointer set cycle. Write operations always require the pointer be reset.

# Reading

If the pointer is already pointing to the desired register, the master can read from that register by setting the read/write bit (following the slave address) to 1. After sending an ACK, the FAH4840 begins transmitting data during the following clock cycle. The master should respond with a NACK, followed by a STOP condition (see Figure 6).

The master can read multiple bytes by responding to the data with an ACK instead of a NACK and continuing to send SCL pulses, as shown in Figure 7, then the FAH4840 increments the pointer by one and sends the data from the next register. The master indicates the last data byte by responding with a NACK, followed by a STOP condition.

To read from a register other than the one currently indicated by the command register, a pointer to the desired register must be set. Immediately following the pointer set, the master must perform a repeated START condition (see Figure 9), which indicates to the FAH4840 that a new operation is about to occur. If the repeated START condition does not occur, the FAH4840 assumes that a write is taking place and the selected register is overwritten by the upcoming data on the data bus. After the START condition, the master must again send the device address and read/write bit. This time, the read/write bit must be set to 1 to indicate a read. The rest of the read cycle is the same as described in the previous paragraphs for reading from a preset pointer location.

# Writing

All writes must be preceded by a pointer set, even if the pointer is already pointing to the desired register.

Immediately following the pointer set, the master must begin transmitting the data to be written. After transmitting each byte of data, the master must release the Serial Data (SDA) line for one clock cycle to allow the FAH4840 to acknowledge receiving the byte. The write operation should be terminated by a STOP condition from the master (see Figure 8).

As with reading, the master can write multiple bytes by continuing to send data. The FAH4840 increments the pointer by one and accepts data for the next register. The master indicates the last data byte by issuing a STOP condition.

| Adrs | Register           | Туре | Reset<br>Value | Bit 7         | Bit 6          | Bit 5          | Bit 4           | Bit 3     | Bit 2            | Bit 1           | Bit 0        |

|------|--------------------|------|----------------|---------------|----------------|----------------|-----------------|-----------|------------------|-----------------|--------------|

| 00H  | CTRL1              | R/W  | 10000000       | HAPTIC_<br>EN | Reserved       | Reserved       | Rese            | rved      | EN_LPF           | SE              | VREG_<br>VCM |

| 01H  | CTRL2              | R/W  | 00110011       |               | IN_RES[2:0     | )]             | EN_PW<br>M_DET  |           | VREG_            | OUT[3:0]        |              |

| 02H  | STATUS1            | R    | Xxxx111x       | Reserved      | Reserved       | Reserved       | Reserved        | VDD_G     | VREG_<br>OUT_G   | VOT             | Reserved     |

| 03H  | CTRL_DIV1          | R/W  | 01010011       |               |                |                | PWM_[           | DIV[7:0]  |                  |                 |              |

| 04H  | CTRL_DIV2          | R/W  | 00000000       |               |                |                | PWM_D           | IV[15:8]  |                  |                 |              |

| 05H  | CTRL_CALI<br>B1    | R/W  | 00000011       | R             | ESONANCE       | E_MARGIN       | [3:0]           |           | 6_DELAY<br>[1:0] | EN_TEMP<br>_REG | CALIB_<br>EN |

| 06H  | CTRL_CALI<br>B2    | R/W  | xxxx0011       | Reserved      | Reserved       | Reserved       | Reserved        | I P       | ULSE_NUN         | M[2:0]          | SEL_<br>AVRG |

| 07H  | CTRL_THR           | R/W  | 00000100       |               |                |                | Z_X_N           | JM[7:0]   |                  |                 |              |

| 08H  | CALIB_STA<br>TUS1  | R    | X001000        | Reserved      | CALIB_<br>FAIL | LAST_<br>LEVEL | CALIB_<br>FIRST |           | CALIB_           | STATE[3:0]      |              |

| 09H  | CALIB_STA<br>TUS2  | R    | 00000000       |               |                |                | FIRST_1         | GG[7:0]   |                  |                 |              |

| 0AH  | CALIB_STA<br>TUS3  | R    | 00000000       |               |                |                | FIRST_T         | AG[15:8]  | 0                |                 |              |

| 0BH  | CALIB_STA<br>TUS4  | R    | 00000000       |               |                |                | PWM_DIVI        | SOR_A[7:0 | )]               |                 |              |

| 0CH  | CALIB_STA<br>TUS5  | R    | 00000000       |               |                | F              | WM_DIVIS        | OR_A[15:  | 8]               |                 |              |

| 0DH  | CALIB_STA<br>TUS6  | R    | 00000000       |               |                |                | PWM_DIVI        | SOR_B[7:0 | )]               |                 |              |

| 0EH  | CALIB_STA<br>TUS7  | R    | 00000000       |               |                | F              | WM_DIVIS        | OR_B[15:  | 8]               |                 |              |

| 0FH  | CALIB_STA<br>TUS8  | R    | 00000000       |               |                | y              | PWM_DIV         | ISOR[7:0] |                  |                 |              |

| 10H  | CALIB_STA<br>TUS9  | R    | 00000000       |               |                | 1              | PWM_DIV         | SOR[15:8] |                  |                 | 1            |

| 11H  | CALIB_STA<br>TUS10 | R    | 00000000       |               |                |                | CNT_            | H[7:0]    | 2                |                 |              |

| 12H  | CALIB_STA<br>TUS11 | R    | 00000000       |               |                |                | CNT_            | L[7:0]    |                  |                 |              |

| 13H  | CALIB_STA<br>TUS12 | R    | 00000000       |               |                |                | CNT_Z           | ZX[7:0]   |                  |                 |              |

| 14H  | CTRL3              | W/R  | Xxxxxxx0       | Reserved      | Reserved       | Reserved       | Reserved        | Reserved  | Reserved         | Reserved        | SW_RST       |

| Table 3<br>Address:             |                |      |                                                                                                                            |

|---------------------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------|

| Reset Va                        | alue: 1xxxx000 | C    |                                                                                                                            |

| Bit #                           | Name           | Туре | Function                                                                                                                   |

| 7                               | HAPTIC_EN      | R/W  | 1: Haptic Drive Enable Mode<br>0: Power-Down Mode                                                                          |

| 6:3                             | Reserved       |      |                                                                                                                            |

| 2                               | EN_LPF         | R/W  | 1: Enable internal 20 kHz LPF<br><b>0: Disable internal LPF</b>                                                            |

| 1                               | SE             | R/W  | 1: Single-Ended Mode<br>0: Differential Mode                                                                               |

| 0                               | VREG_VCM       | R/W  | 1: Outputs use V <sub>REG</sub> /2 as VCMO<br>0: Outputs use V <sub>DD</sub> /2 as VCMO                                    |

| Table 4<br>Address:<br>Reset Va | 0x01           | 1    |                                                                                                                            |

| Bit #                           | Name           | Туре | Function                                                                                                                   |

| 7:5                             | IN_RES[2:0]    | R/W  | Input Resistance.<br>000: 8 kΩ<br><b>001: 10 k</b> Ω<br>010: 12 kΩ<br>011: 14 kΩ<br>100: 16 kΩ<br>101: 18 kΩ<br>110: 20 kΩ |

111: 22 kΩ

0000 1.4 V 0001 1.6 V 0010 1.8 V 0011 2.0 V 0100 2.2 V

0101 2.4 V

0110 2.6 V 0111 2.8 V 1000 3.0 V 1001 3.2 V

R/W

R/W

1: Enable PWM detection circuit

0: Disable PWM detection circuit

EN\_PWM\_DET

VREG\_OUT[3:0

1

4

3:0

During LRA calibration stage 1,  $V_{REG_{OUT}}$  is always 2.0 V.

# Table 5.

STATUS1

Address: 0x02

Reset Value: xxxx111x

| Bit # | Name           | Туре | Function                                                                                                                                            |

|-------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4   | Reserved       |      |                                                                                                                                                     |

| 3     | VDD_G          | R    | 0: Input voltage is not good (less UVLO), Input voltage is less than 2.3 V (rising), 2.1 V (falling)<br><b>1: Input voltage is good (over UVLO)</b> |

| 2     | VREG_OUT_<br>G | R    | 0: Regulator output is not good (V <sub>REG_OUT</sub> is less than 70% of VREG_OUT programmed)<br><b>1: Regulator output is good</b> <sup>(3)</sup> |

| 1     | VOT            | R    | 0: Over temperature protection is tripped<br>1: Over temperature protection is not tripped                                                          |

| 0     | Reserved       |      |                                                                                                                                                     |

## Note:

3. HEN must be HIGH for VREG\_OUT to be enabled.

## Table 6. CTRL\_DIV1

Address:

0x03

Reset Value: 01010011

| Bit # | Name         | Туре | Function                                                                                                                                                                                                                                                                                                                               |

|-------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

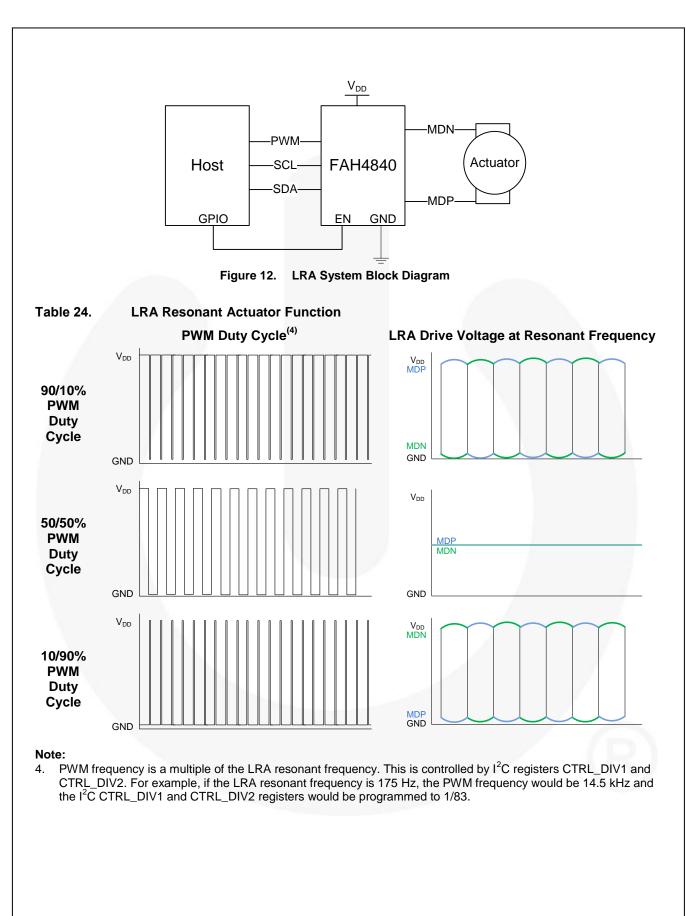

| 7:0   | PWM_DIV[7:0] | R/W  | LSB of the PWM divisor. For example, if the intended resonance frequency is<br>175 Hz and the PWM input clock frequency is 40 kHz, program the<br>PWM[15:0] register as:<br>PWM_DIV[15:0] = (1/175)/(1/40 kHz) = 228(decimal) = E4(HEX)<br>PWM_DIV[15:8] = 00<br>PWM_DIV[7:0] = E4<br>Counter range is from 01 to E4.<br>Default is 83 |

# Table 7. CTRL\_DIV2

Address:

0x04

Reset Value: 00000000

| Bit # | Name          | Туре | Function                                |

|-------|---------------|------|-----------------------------------------|

| 7:0   | PWM_DIV[15:8] | R/W  | MSB of the PWM divisor.<br>Default is 0 |

# Table 8. Address:

CTRL\_CALIB1 0x05

Reset Value:

| Bit # | Name                          | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4   | RESONANCE<br>_MARGIN<br>[3:0] | R/W  | This is the % (of programmed PWM_DIV[15:0]) margin that is acceptable.<br>The measured resonance frequency is $\pm$ compared against this margin. If within $\pm$ margins, the measured resonance frequency is accepted, else it is discarded.<br><b>0000 No limit</b><br>0001 1/256 * 100 = %0.39<br>0010 1/128 * 100 = %0.78<br>0011 1/64 * 100 = %1.56<br>0100 1/32 * 100 = %3.12<br>0101 1/16 * 100 = %6.25<br>0110 1/8 * 100 = %12.5<br>0111 1/4 * 100 = %25.0 |

| 3:2   | MEAS_DELA<br>Y[1:0]           | R/W  | Delay the zero crossing detection by a number of PWM clock cycles, which is calculated by below ratio multiple PWM_DIV. For example, if set to 00, the delay number is (PWM_DIV*1/8).<br><b>00: 1/8</b><br>01: 1/16<br>10: 1/32<br>11: 1/64                                                                                                                                                                                                                         |

| 1     | EN_TEMP_<br>REG               | R/W  | If set to 1, the detected PWM divisor value is stored in a Temp register and used at the starting of the next haptic event.<br>If set to 0, haptic cycles always use the initial set PWM_DIV.                                                                                                                                                                                                                                                                       |

| 0     | CALIB_EN                      | R/W  | If set to 1, the part performs calibration, else no calibration.                                                                                                                                                                                                                                                                                                                                                                                                    |

# Table 9.

Address:

0x06

CTRL\_CALIB2

Reset Value: xxxx0011

| Bit # | t # Name Type      |     | Function                                                                                                                                                                                                                                                                                                           |  |  |

|-------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:4   | Reserved           | 0   |                                                                                                                                                                                                                                                                                                                    |  |  |

| 3:1   | PULSE_NUM<br>[2:0] | R/W | Determines the pulse number in stage 1 when calibration at beginning.<br>The pulse number is #(PULSE_NUM+1).<br>000: pulse number 1<br><b>001: pulse number 2</b><br>010: pulse number <b>3</b><br>011: pulse number 4<br>100: pulse number 5<br>101: pulse number 6<br>110: pulse number 7<br>111: pulse number 8 |  |  |

| 0     | SEL_AVRG           | R/W | <ol> <li>select average value of two periods as final LRA period result.</li> <li>select the detected first period as final LRA period result.</li> </ol>                                                                                                                                                          |  |  |

| <b>Table ′</b><br>Address<br>Reset V | s: 0x07      |      |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit #                                | Name         | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7:0                                  | Z_X_NUM[7:0] | R/W  | Threshold for transition region around zero-crossing point. It represents the jitter width around the zero-crossing point. When accumulative comparator result for one level (HIGH or LOW) around the transition edge reaches the threshold, zero-crossing point is thought to be found.<br>The threshold is programmed referring to PWM_DIV. To be safe, set the threshold a bit larger than the real transition region. |

#### Table 11. CALIB\_STATUS1 0x08

Address:

Reset Value: x0010000

| Bit # | Name        | Туре | Function                                                                                                                                                   |

|-------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Reserved    | 8    |                                                                                                                                                            |

| 6     | CALIB_FAIL  | R    | After the measurement delay period passes, count period of 3*PWM_DIV. During this time, if the four zero-crossing points are not found, calibration fails. |

| 5     | LAST_LEVEL  | R    | Indicate the last level (HIGH or LOW) for detecting next zero-crossing point.                                                                              |

| 4     | CALIB_FIRST | R    | Indicate whether current resonant detection is the first after power on reset or not.                                                                      |

| 3:0   | CALIB_STATE | R    | Resonant detection state machine.                                                                                                                          |

#### CALIB\_STATUS2 Table 12.

Address:

0x09

Reset Value: 00000000

| Bit # | Name           | Туре | Function                                                    |

|-------|----------------|------|-------------------------------------------------------------|

| 7:0   | FIRST_TAG[7:0] | R    | LSB bits of the tag for the first found zero-crossing edge. |

#### Table 13. CALIB\_STATUS3

Address:

0x0A

0000000 Reset Value:

| Bit # | Name            | Туре | Function                                                    |

|-------|-----------------|------|-------------------------------------------------------------|

| 7:0   | FIRST_TAG[15:8] | R    | MSB bits of the tag for the first found zero-crossing edge. |

#### CALIB\_STATUS4 Table 14.

Address:

0x0B

| Reset Val | ue: 00000000       |      |                                                                                              |

|-----------|--------------------|------|----------------------------------------------------------------------------------------------|

| Bit #     | Name               | Туре | Function                                                                                     |

| 7:0       | PWM_DIVISOR_A[7:0] | R    | LSB bits of the resonant period calculated by the first zero-crossing point and third point. |

# Table 15.

CALIB\_STATUS5

Address: 0x0C

| Bit # | Name                | Туре | Function                                                                                     |

|-------|---------------------|------|----------------------------------------------------------------------------------------------|

| 7:0   | PWM_DIVISOR_A[15:8] | R    | MSB bits of the resonant period calculated by the first zero-crossing point and third point. |

#### CALIB\_STATUS6 Table 16.

Address:

0x0D

Reset Value: 00000000

| Bit # | Name               | Туре | Function                                                                                           |

|-------|--------------------|------|----------------------------------------------------------------------------------------------------|

| 7:0   | PWM_DIVISOR_B[7:0] | R    | LSB bits of the resonant period calculated by the second zero-crossing point and the fourth point. |

#### Table 17. CALIB\_STATUS7

Address:

**—**

0x0E

| Bit #    | Name         | Туре |  |

|----------|--------------|------|--|

| Reset Va | lue: 0000000 |      |  |

| Bit # | Name                | Туре | Function                                                                                           |

|-------|---------------------|------|----------------------------------------------------------------------------------------------------|

| 7:0   | PWM_DIVISOR_B[15:8] | R    | MSB bits of the resonant period calculated by the second zero-crossing point and the fourth point. |

#### Table 18. CALIB\_STATUS8 0x0F

Address:

#### Reset Value: 00000000

| Bit # | Name             | Туре | Function                                                                                                                                                               |

|-------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | PWM_DIVISOR[7:0] | R    | LSB bits of the final resonant period.<br>PWM_DIVISOR may comes from initial PWM_DIV, or<br>PWM_DIVISOR_A, or the average value of PWM_DIVISOR_A and<br>PWM_DIVISOR_B. |

#### Table 19. CALIB\_STATUS9 0x10

Address:

Reset Value: 0000000

| Bit # | Name              | Туре | Function                               |

|-------|-------------------|------|----------------------------------------|

| 7:0   | PWM_DIVISOR[15:8] | R    | MSB bits of the final resonant period. |

#### Table 20. CNT H

Address:

Reset Value: 00000000

0x11

| Bit # | Name       | Туре | Function                                        |

|-------|------------|------|-------------------------------------------------|

| 7:0   | CNT_H[7:0] | R    | High level counter during first edge detection. |

| Table | 21. |  |

|-------|-----|--|

0x12 Address:

Reset Value: 00000000

| Bit # | Name       | Туре | Function                                       |

|-------|------------|------|------------------------------------------------|

| 7:0   | CNT_L[7:0] | R    | Low level counter during first edge detection. |

# Table 22.

Address:

0x13 Reset Value: 00000000

0x14

CNT\_H

CNT\_L

| Bit # | Name        | Туре | Function                                               |

|-------|-------------|------|--------------------------------------------------------|

| 7:0   | CNT_ZX[7:0] | R    | Level counter used for zero-crossing points detection. |

#### Table 23. CTRL3

Reset Value: xxxxxx0

| Bit # | Name     | Туре | Function                                                                                                                                                                                                                                                             |

|-------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1   | Reserved |      |                                                                                                                                                                                                                                                                      |

| 0     | SW_RST   | W/R  | Software reset bit, default is zero.<br>When this bit is set 1, a negative pulse is generated and all the ongoing<br>operation is stopped and all registers reset to default values.<br>This bit is self-clearing and changes back to HIGH after the negative pulse. |

# Internal LDO

The internal LDO is designed for adjustable output voltage ( $V_{REG_OUT}$ ), controlled by a 16-step  $I^2C$  register. This provides flexibility, convenience, and configuration for low-power consumption. The LDO includes an internal circuit for short-circuit current protection.

## **Serial Interface**

The  $I^2C$  registers allow the user to program the motor type, PWM dividing ratio, power-down, and other functions. The device needs to function without any  $I^2C$  input signals connected.

## **Thermal Shutdown**

The device has thermal shutdown capability. If the junction temperature is above 150°C, the temperature control block shuts down and remains off until the temperature goes below 134°C. The register values are kept, so re-initialization is not required.

## **Over-Current Limitation**

The driver includes a current-limitation block to protect against an over-current condition. This is mainly a protection against a stuck spring condition. Over-current shutdown is at 350 mA typically.

## **Status Registers**

The status register set monitors LDO input voltage, regulator output voltage, and over-temperature status.

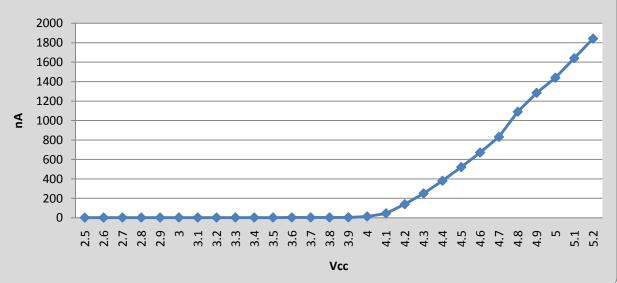

# FAH4840 shut down current, software disable ON, HEN=0. PWM=0

Figure 13. Typical Performance Characteristics

###

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

| AccuPower™               |

|--------------------------|

| AX-CAP <sup>®</sup> *    |

| BitSiC™                  |

| Build it Now™            |

| CorePLUS™                |

|                          |

| CorePOWER™               |

| CROSSVOLT™               |

| CTL™                     |

| Current Transfer Logic™  |

| DEUXPEED®                |

| Dual Cool™               |

| EcoSPARK <sup>®</sup>    |

| EfficientMax™            |

| ESBC™                    |

| <b>F</b> <sup>®</sup>    |

| +                        |

| Fairchild®               |

| Fairchild Semiconductor® |

| FACT Quiet Series™       |

| FACT®                    |

| FAST®                    |

| FastvCore™               |

| FETBench™                |

| FEIDenui                 |

**FRFET<sup>®</sup>** Global Power Resource<sup>S</sup> GreenBridge™ Green FPS™ Green FPS™ e-Series™ Gmax™ **GTO**<sup>™</sup> IntelliMAX<sup>™</sup> **ISOPLANAR™** Making Small Speakers Sound Louder and Better MegaBuck™ MICROCOUPLER™ MicroFET<sup>11</sup> MicroPak™ MicroPak2™ MillerDrive™ MotionMax™ mWSaver OptoHiT™ **OPTOLOGIC<sup>®</sup> OPTOPLANAR<sup>®</sup>**

F-PFS<sup>™</sup>

PowerTrench® PowerXS™ Programmable Active Droop™ OFET QS™ Quiet Series™ RapidConfigure™ Saving our world, 1mW/W/kW at a time™ SignalWise<sup>T</sup> SmartMax™ SMART START Solutions for Your Success™ SPM STEALTH<sup>TM</sup> SuperFET<sup>®</sup> SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SvncFET™

#### Sync-Lock™ SYSTEM GENERAL®

$\begin{array}{l} \text{TinyBoost}^{\textcircled{0}}\\ \text{TinyBuck}^{\textcircled{0}}\\ \text{TinyCalc}^{^{\text{TM}}}\\ \text{TinyLogic}^{\textcircled{0}}\\ \text{TinyCoptO}^{^{\text{TM}}}\\ \text{TinyPower}^{^{\text{TM}}}\\ \text{TinyPower}^{^{\text{TM}}}\\ \text{TinyPWM}^{^{\text{TM}}}\\ \text{TinyWire}^{^{\text{TM}}}\\ \text{TinyWire}^{^{\text{TM}}}\\ \text{TransIc}^{^{\text{TM}}}\\ \text{TriFault Detect}^{^{\text{TM}}}\\ \text{TRUECURRENT}^{\textcircled{0}_{*}}\\ \mu \underline{\text{SetDes}}^{^{\text{TM}}}\\ \end{array}$

UHC<sup>®</sup> Ultra FRFET™ UniFET™ VCX™ VisualMax™ VoltagePlus™ XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FPS™

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Surces. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms      |                       |                                                                                                                                                                                                        |  |  |  |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |  |  |  |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |  |  |  |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                                  |  |  |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |  |  |  |

Rev. 166

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor: