# HT7L2103 Anti-EMI, High Efficiency Dimmable LED Lighting Driver with Primary-Side Constant Control and Green Mode

# **Feature**

- · Frequency Jitter for EMI Restriction

- · Integrated Soft-Start Function

- Very Low Operating Current and Start-up Current (<20μA) for satisfying Energy-Star 2.0 "No-Load Mode" (Stand-by) Power standard

- ±5% Trimmed Precision Oscillator

- Non-Audible-Noise Green Mode Control to maintain efficiency for both Light and Heavy Loads

- LEB (Leading-Edge Blanking) on CS Pin

- Internal Slope Compensation

- Cycle-by-Cycle Current Limiting

- Short-Circuit-Protection(SCP) for Short-Circuit and Over-Load Condition

- · Over-Voltage-Protection(OVP) on VCC Pin

- Internal Over-Temperature-Protection(OTP)

- 1~99% PWM Dimming Range

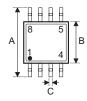

- · 8-pin SOP package

# **Applications**

- Isolation AC-DC LED Lighting

- · AC-DC Switching Power Supply/Adapter

# **General Description**

The HT7L2103 is an advanced, highly integrated LED Lighting Driver using an AC-DC isolation topology. The device provides many protection functions and uses ultra low power circuit design, and is optimized to restrict EMI. By integrating a special multi-function interface, this device can be used for different LED power topologies such as Primary Feedback Isolation Flyback, Secondary Feedback Isolation Flyback, DC-DC Buck/Boost/ Buck-Boost. This device also integrates various protection functions for LED Lighting requirements such as Cycle-by-Cycle Current Limiting, Short-Circuit Protection (SCP), Over-Voltage Protection (OVP), Internal Over-Temperature Protection (OTP), and a Soft-Start function to reduce inrush currents during LED power system initialization for the prevention of device burn-out.

The HT7L2103 provides a 1~99% PWM Dimming Range with duty-cycle scale precision lower than 1%.

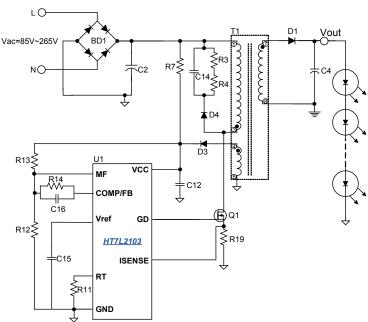

# **Application Circuits**

Rev. 1.00 1 November 04, 2011

# **Block Diagram**

# VCC 7 VCC 7 VCC 7 VCC 7 VCC 7 VCC 8 VCC 9 VC

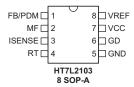

# **Pin Assignment**

# **Pin Description**

| Pin No. | Pin Name | Description                                                                                                                                                                                                      |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | FB/PDM   | Voltage Feedback Pin. Connected to a Photo-Coupler for closed-loop control. This pin also can be used as a PWM Dimming Pin.                                                                                      |

| 2       | MF       | Multi-Function Pin. By Connecting this pin to different system sensing points, the HT7L2013 can be used for different circuit topologies such as Isolation Flyback or Non-Isolation DC-DC Buck/Boost/Buck-Boost. |

| 3       | ISENSE   | A voltage proportional to the inductor current is connected to this input. The Constant Current Controller uses this voltage information to keep the system output current within a narrow range.                |

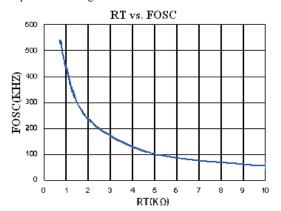

| 4       | RT       | The oscillator frequency is programmed by connecting a resistor RT between this pin and ground. A maximum frequency of 500KHz is possible.                                                                       |

| 5       | GND      | Combined control circuitry and power ground.                                                                                                                                                                     |

| 6       | GD       | Power MOSFET gate driver output.                                                                                                                                                                                 |

| 7       | VCC      | Positive Supply.                                                                                                                                                                                                 |

| 8       | VREF     | A Temperature-Independent Voltage Reference output.                                                                                                                                                              |

# **Absolute Maximum Ratings**

| Supply Voltage VCC                     | 0.3V~30.0V |

|----------------------------------------|------------|

| FB/PDM, RT, ISENSE Pins                | -0.3V~5.5V |

| MF Pin                                 | 0.3V~5.0V  |

| Junction Temperature                   | 150°C      |

| Operating Ambient Temperature          | 40°C~85°C  |

| Storage Temperature Range              | 65°C~150°C |

| Package Thermal Resistance (8-Pin SOP) | 160°C/W    |

| ESD Protection:                        |            |

| Human Body Model                       | 3kV        |

| Machine Model                          | 200V       |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.00 2 November 04, 2011

# **Electrical Characteristics**

Unless otherwise stated, this specifications apply for  $0^{\circ}\text{C} \le \text{Ta} \le 70^{\circ}\text{C}$ ,  $V_{\text{cc}}=15\text{V}$ , RT= $10\text{k}\Omega$

| Symbol                                  | Parameter                       | Test Condition                                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------|---------------------------------|--------------------------------------------------|------|------|------|------|

| Supply Vo                               | Itage (VCC Pin)                 |                                                  |      |      |      |      |

| I <sub>ST</sub>                         | Startup Current                 | V <sub>cc</sub> =12.9V                           | _    | 12   | 30   | μА   |

|                                         |                                 | V <sub>FB/PDM</sub> =0V                          | _    | 2.0  | 3.0  | mA   |

| I <sub>cc</sub>                         | Operating Current               | V <sub>FB/PDM</sub> =3V                          | T —  | 2.5  | _    | mA   |

| V <sub>TL</sub>                         | UVLO (Off)                      | _                                                | 7    | 8    | 9    | V    |

| V <sub>TH</sub>                         | UVLO (On)                       | _                                                | 13   | 14   | 15   | V    |

| V <sub>cc</sub>                         | OVP Trip Level                  | V <sub>cc</sub> (Over Voltage Protection)        | 26.5 | 28.0 | 29.5 | V    |

| t <sub>D-OVP</sub>                      | OVP Strobe Time                 | _                                                | _    | 100  | _    | μS   |

| Voltage Re                              | eference (VREF Pin)             |                                                  |      |      |      |      |

| $V_{REF}$                               | Output Voltage                  | Tj=25°C, I <sub>o</sub> =1mA                     | _    | 5.5  | _    | V    |

| $\Delta V_{REF}$                        | Line Regulation                 | 12V ≤ V <sub>CC</sub> ≤ 25V                      | _    | 3.0  | 20   | mV   |

| $\Delta V_{REF}$                        | Load Regulation                 | 1mA ≤ I <sub>0</sub> ≤ 10mA                      | _    | 4.0  | 25   | mV   |

| Current Se                              | ensing (ISE NSE Pin)            |                                                  |      |      |      |      |

| V <sub>IS(OFF)</sub>                    | Maximum Input Voltage           | _                                                | 0.9  | 1.0  | 1.1  | V    |

| t <sub>LEB</sub>                        | Leading Edge Blanking Time      | _                                                | _    | 350  | _    | ns   |

|                                         | Delay to Output                 | _                                                | T —  | 100  | _    | ns   |

| Oscillator                              | (RT pin)                        |                                                  |      |      |      |      |

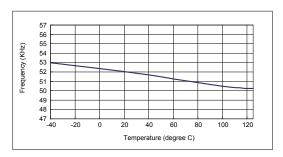

| f <sub>osc</sub>                        | Oscillator Frequency            | Tj=25°C, RT=10kΩ to GND                          | 49   | 52   | 55   | kHz  |

| $\Delta f_{OSC}$                        | To a control of Oto Life        | 4000 40500                                       |      | 5.0  |      | 0/   |

| $\Delta T_A$                            | Temperature Stability           | -40°C ~105°C                                     | _    | 5.0  | _    | %    |

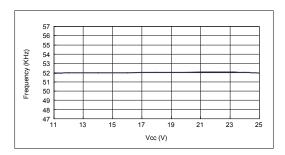

| $\frac{\Delta f_{OSC}}{\Delta V_{REF}}$ | Voltage Stability               | V <sub>cc</sub> =10V~25V                         | _    | 0.2  | 1.0  | %/V  |

| D <sub>MAX</sub>                        | Maximum Duty                    | _                                                | T —  | 75   | _    | %    |

|                                         | Frequency Jitter                | _                                                | _    | ±4   | _    | %    |

| Gate Drive                              | Output (GD Pin)                 |                                                  |      |      |      |      |

| V <sub>OL</sub>                         | Output Low Level                | V <sub>CC</sub> =15V, Isink=20mA                 | _    | _    | 1    | V    |

| V <sub>OH</sub>                         | Output High Level               | V <sub>cc</sub> =15V, Isource=20mA               | 9.0  | _    | _    | V    |

| t <sub>r</sub>                          | Rising Time                     | Tj=25°C, Load Capacitance=1nF                    | _    | 50   | 150  | ns   |

| t <sub>f</sub>                          | Falling Time                    | Tj=25°C, Load Capacitance=1nF                    |      | 50   | 150  | ns   |

| Voltage Fe                              | eedback (FB/PDM Pin)            |                                                  |      |      |      |      |

| I <sub>SINK</sub>                       | Short Circuit Current           | V <sub>FB/PDM</sub> =0V                          | _    | 1.5  | 2.2  | mA   |

| V <sub>FB/PDM</sub>                     | Open Loop Voltage               | FB/PDM pin open                                  | -    | 5.5  | _    | V    |

| SCP (Shor                               | rt Circuit Protection)          |                                                  |      |      |      |      |

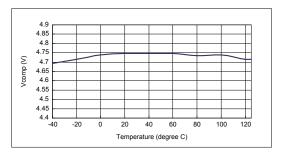

| V <sub>FB/PDM</sub>                     | SCP Trip Level                  | V <sub>FB/PDM</sub> (SCP)                        | -    | 4.7  | _    | V    |

|                                         | SCP Delay Time (See Note)       | f <sub>s</sub> =52kHz                            | _    | 75   | _    | ms   |

| Soft-Start                              |                                 |                                                  |      |      |      |      |

| t <sub>START</sub>                      | Soft-Start Time                 | RT=10kΩ                                          | -    | 10   | _    | ms   |

| Internal O                              | TP(Over Temperature Protection) |                                                  |      |      |      |      |

| t <sub>POn</sub>                        | OTP Trigger Temperature         |                                                  | _    | 150  | _    | °C   |

| t <sub>P-Hys</sub>                      | OTP Temperature Hysteresis      |                                                  |      | 30   | _    | °C   |

| Multi-Fund                              | ction Pin                       |                                                  |      |      |      |      |

| V <sub>REFA</sub>                       | Reference Voltage               | V <sub>FB/PDM</sub> =2.5V                        | 2.42 | 2.50 | 2.58 | V    |

| I <sub>SINKA</sub>                      | Output Sink Current             | V <sub>FB</sub> =2.7V, V <sub>FB/PDM</sub> =1.1V | 2.0  | 7.0  | _    | mA   |

| I <sub>SOURCEA</sub>                    | Output Source Current           | V <sub>FB</sub> =2.3V, V <sub>FB/PDM</sub> =4.8V | -0.5 | -1.0 | _    | mA   |

| $V_{\text{OHA}}$                        | VFB/PDM High Voltage            | $V_{FB}$ =2.3V, RL=15k $\Omega$ to GND           | 4.8  | 5.0  | _    | V    |

| V <sub>OLA</sub>                        | VFB/PDM Low Voltage             | $V_{FB}$ =2.3V, RL=15k $\Omega$ to VREF          | _    | 0.8  | 1.1  | V    |

| $A_{VO}$                                | DC Gain                         |                                                  | _    | 150  | _    | dB   |

Note: These Parameters, although guaranteed, are not 100% tested in production.

Rev. 1.00 3 November 04, 2011

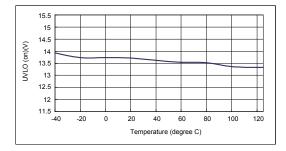

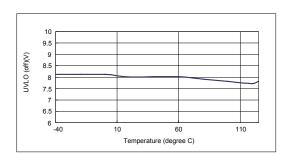

# **Typical Performance Characteristics**

Figure 1. UVLO (on) (V) vs. Temperature

Figure 2. UVLO (off) (V) vs. Temperature

Figure 3. Frequency vs. Temperature

Figure 4. Frequency vs.  $V_{\text{cc}}$

Figure 5.  $V_{\text{FB/PDM}}$  for SCP vs. Temperature

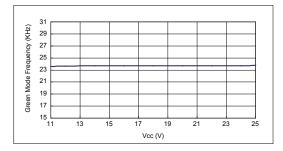

Figure 6. Green Mode Frequency vs. V<sub>cc</sub>

Rev. 1.00 4 November 04, 2011

# **Application Information**

# **Operation Overview**

The HT7L2013 is a highly functionally integrated PWM controller for LED lighting and is optimized to restrict EMI. The device uses a primary side feedback design with constant current control to reduce external component requirements and to maintain current accuracy. It is recommended for E27 retrofit lamp use. The PWM dimming range is 1% to 99% and provides less than 1% dimming precision. Its internal features include Green mode (Non-Acoustic-Noise), internal slope compensation, high efficiency under different load conditions within a wide operating temperature range of -40°C to 85°C. The devices also includes a range of protection functions, SCP, OVP, UVLO, current limit, LEB, soft start, OTP for internal thermal sensing ,not only enhance system excellent performance, but also ensure high stability of the whole circuit application even under extreme environmental conditions such as high temperature or high EMI levels.

# Advanced Precision Oscillator for Green-Mode Switching and Non-Acoustic Noise Requirement

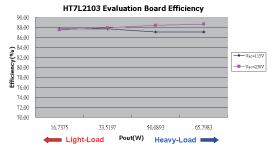

A Trimmed Precision Green Mode Oscillator is implemented in the device to enhance the conversion efficiency under light load conditions. As Figure 7 shows, the efficiency difference between light loads and heavy loads is less than 1%, while the average efficiency is only 89.5%, the peak efficiency is 90%.

Figure 7 Efficiency Performance between Light-Load and Heavy-Load

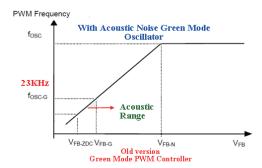

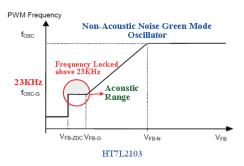

The Green Mode Oscillator types supplied by other PWM Controller providers are plagued by Acoustic-Noise problems. This is because, under light load conditions, the frequency will keep decreasing through the Human Acoustic Range (from 20Hz to 20kHz), and these audio frequencies may create audible noise in the transformer. Holtek's HT7L2103 patented Green Mode Oscillator designed using an advanced Non-Acoustic Noise structure prevents the generation of frequencies in the audio frequency band, thus eliminating any transformer noise.

Figure 8. Oscillator Behavior Compared with HT7L2103 and Other Green Mode PWM Controller

# **Frequency Jitter for EMI Restriction**

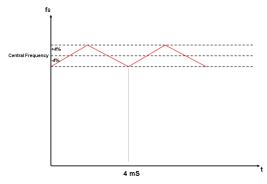

EMI restriction is accomplished using a Frequency Jitter function, which spreads the energy over a wider frequency range than the bandwidth measured by the EMI test equipment. An internal Frequency Jitter circuit changes the switching frequency between +4% and -4% of the central frequency with a period of 4ms.

Figure 9 Frequency Jitter Function Spreads Energy Over a Period to Accomplish EMI Restraining

Rev. 1.00 5 November 04, 2011

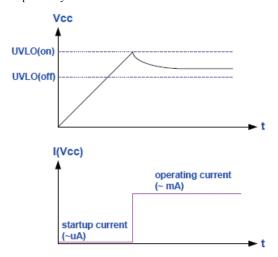

# **Under Voltage Lockout (UVLO)**

An UVLO comparator is implemented in to ensure that the device is fully functional before the output stage is enabled. As shown in Fig. 10, a hysteresis is provided to prevent the PWM Controller from shutting down during any voltage dips which might occur during startup process. The turn-on and turn-off threshold levels are set at 16.0V and 10.0V, respectively.

Figure 10. UVLO Scheme and Start-Up Current

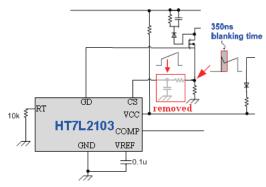

# Current Sense and Leading-Edge Blanking (LEB)

A Leading-Edge Blanking Scheme is integrated in the device to prevent false triggering due to feedback current spikes which may appear on the CS pin, further eliminating the need for an R-C filter which is always a requirement in traditional current mode PWM Controller applications.

Figure 11. LEB with R-C Filter Removed

## **Internal Slope-Compensation**

An important issue with the current mode control structures is the instability due to Sub-Harmonic Oscillation when the Duty-Cycle > 50%. To prevent this problem from occurring, a Slope-Compensation function is always necessary. In traditional current mode PWM Controller application, many external components are necessary to implement a Slope-Compensation function, However in the HT7L2103 the internal Slope-Compensation eliminates the need for these external components resulting in a simplified the application circuit design.

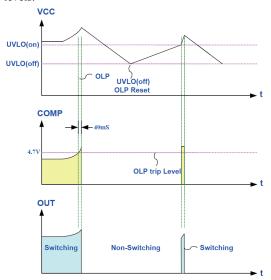

# Short-Circuit Protection (SCP) and Over-Load Protection (OLP)

To protect all the devices in a system from being damaged due to over load or short circuit conditions, a smart SCP function is implemented in the device. Here the feedback system will force the voltage loop to move toward a saturation value and then pull up the voltage on the COMP pin. Whenever the VCOMP increases to the SCP threshold of 4.7V and remains there for longer than 40ms, the protection scheme will activate and then turn off the gate output to stop the power circuit switching. By using such a protection mechanism, the average input power can be reduced to a very low level so that the component temperature and stress can be controlled within safe operating levels.

Figure 12. SCP Function Behavior

Rev. 1.00 6 November 04, 2011

# VCC Pin Over-Voltage Protection (OVP)

VCC Over-Voltage Protection is integrated in the device to prevent components damage due to over voltage conditions on the VCC pin. The OVP is triggered when VCC reaches 28V and lasts for 100µs, The PWM pulses are disabled when OVP is enabled.

# **Internal Over-Temperature Protection (OTP)**

An Internal Over-Temperature Protection (OTP) function is integrated in the device. When the device junction temperature rises higher than the OTP trigger level, the OTP Circuit will turn off the gate drive output thus simultaneously switching off the power MOSFET. The device will recover when the temperature is below the OTP threshold whereupon the PWM signal will resume operation.

# **Oscillator Frequency Tuning**

By choosing an appropriate value of an external resistor between the RT Pin and GND, a suitable operating frequency can be generated. The relationship between the value of RT and the operating frequency is provided in Figure 13.

Figure 13. RT Resistor value vs.

Operating Frequency

Rev. 1.00 7 November 04, 2011

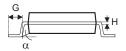

# **Package Information**

# 8-pin SOP (150mil) Outline Dimensions

# MS-012

| Cumbal | Dimensions in inch |       |       |  |

|--------|--------------------|-------|-------|--|

| Symbol | Min.               | Nom.  | Max.  |  |

| А      | 0.228              | _     | 0.244 |  |

| В      | 0.150              | _     | 0.157 |  |

| С      | 0.012              | _     | 0.020 |  |

| C'     | 0.188              | _     | 0.197 |  |

| D      | _                  | _     | 0.069 |  |

| E      | _                  | 0.050 | _     |  |

| F      | 0.004              | _     | 0.010 |  |

| G      | 0.016              | _     | 0.050 |  |

| Н      | 0.007              | _     | 0.010 |  |

| α      | 0°                 | _     | 8°    |  |

| Cumbal | Dimensions in mm |      |      |  |

|--------|------------------|------|------|--|

| Symbol | Min.             | Nom. | Max. |  |

| A      | 5.79             | _    | 6.20 |  |

| В      | 3.81             | _    | 3.99 |  |

| С      | 0.30             | _    | 0.51 |  |

| C'     | 4.78             | _    | 5.00 |  |

| D      | _                | _    | 1.75 |  |

| Е      | _                | 1.27 | _    |  |

| F      | 0.10             | _    | 0.25 |  |

| G      | 0.41             | _    | 1.27 |  |

| Н      | 0.18             | _    | 0.25 |  |

| α      | 0°               | _    | 8°   |  |

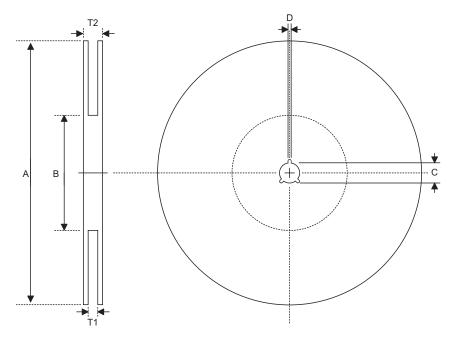

# **Reel Dimensions**

# SOP 8N (150mil)

| Symbol | Description           | Dimensions in mm |

|--------|-----------------------|------------------|

| А      | Reel Outer Diameter   | 330.0±1.0        |

| В      | Reel Inner Diameter   | 100.0±1.5        |

| С      | Spindle Hole Diameter | 13.0 +0.5/-0.2   |

| D      | Key Slit Width        | 2.0±0.5          |

| T1     | Space Between Flange  | 12.8 +0.3/-0.2   |

| T2     | Reel Thickness        | 18.2±0.2         |

Rev. 1.00 9 November 04, 2011

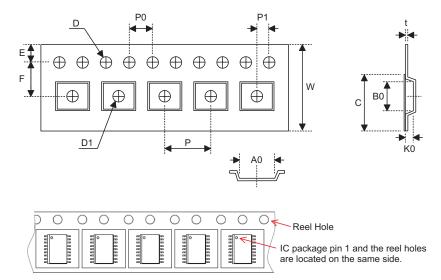

# **Carrier Tape Dimensions**

# SOP 8N (150mil)

| Symbol | Description                              | Dimensions in mm |

|--------|------------------------------------------|------------------|

| W      | Carrier Tape Width                       | 12.0+0.3/-0.1    |

| Р      | Cavity Pitch                             | 8.0±0.1          |

| E      | Perforation Position                     | 1.75±0.10        |

| F      | Cavity to Perforation (Width Direction)  | 5.5±0.1          |

| D      | Perforation Diameter                     | 1.55±0.1         |

| D1     | Cavity Hole Diameter                     | 1.50 +0.25/-0.00 |

| P0     | Perforation Pitch                        | 4.0±0.1          |

| P1     | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| A0     | Cavity Length                            | 6.4±0.1          |

| В0     | Cavity Width                             | 5.2±0.1          |

| K0     | Cavity Depth                             | 2.1±0.1          |

| t      | Carrier Tape Thickness                   | 0.30±0.05        |

| С      | Cover Tape Width                         | 9.3±0.1          |

### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

# Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

# Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057

Tel: 86-755-8616-9908, 86-755-8616-9308

Fax: 86-755-8616-9722

### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538, USA

Tel: 1-510-252-9880 Fax: 1-510-252-9885 http://www.holtek.com

# Copyright<sup>©</sup> 2011 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.00 11 November 04, 2011