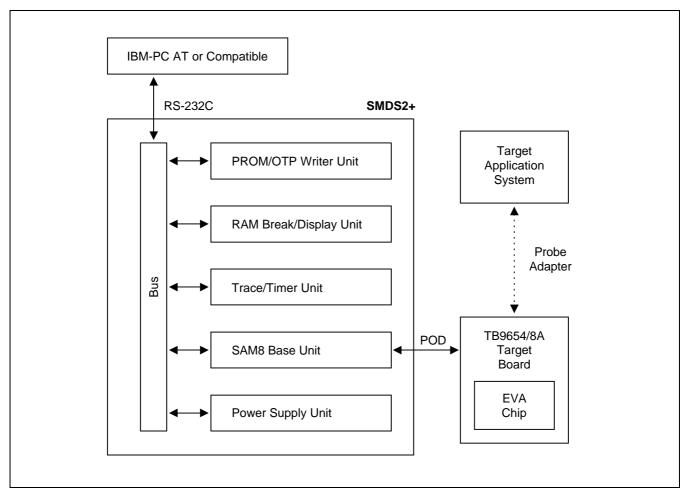

# PRODUCT OVERVIEW

# SAM88RCRI PRODUCT FAMILY

Samsung's SAM88RCRI family of 8-bit single-chip CMOS microcontrollers offer fast and efficient CPU, a wide range of integrated peripherals, and supports OTP device.

A dual address/data bus architecture and bit- or nibble-configurable I/O ports provide a flexible programming environment for applications with varied memory and I/O requirements. Timer/counters with selectable operating modes are included to support real-time operations.

## S3C9654/C9658/P9658 MICROCONTROLLER

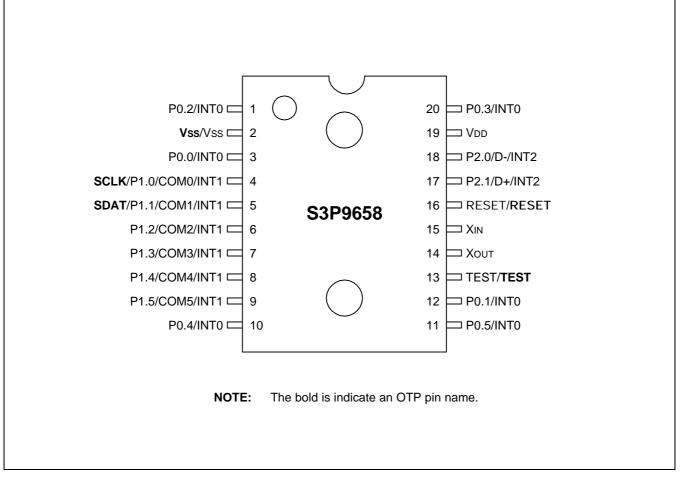

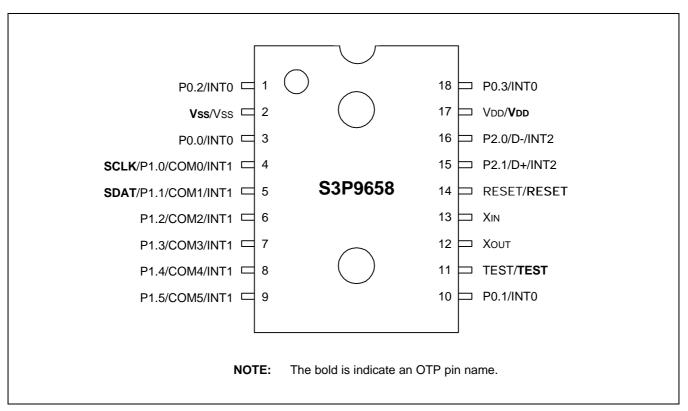

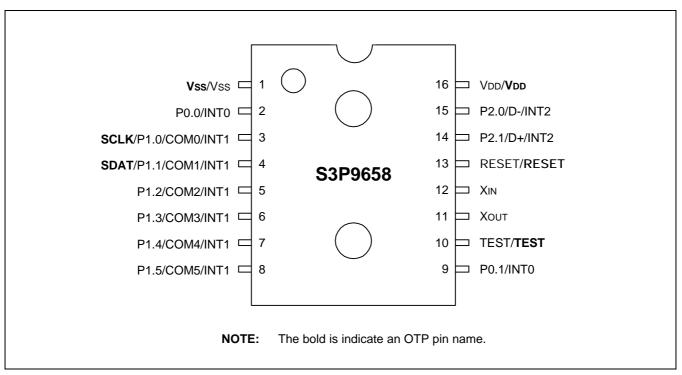

The S3C9654/C9658/P9658 microcontroller with USB function can be used in a wide range of general purpose applications. It is especially suitable for mouse or joystick controller and is available in 16, 18, 20-pin DIP and SOP package.

The S3C9654/C9658/P9658 single-chip 8-bit microcontroller is fabricated using an advanced CMOS process. It is built around the powerful SAM88RCRI CPU core.

Stop and Idle power-down modes were implemented to reduce power consumption. To increase on-chip register space, the size of the internal register file was logically expanded. The S3C9654/C9658/P9658 has 4/8 Kbytes of program memory on-chip (S3C9654/C9658), and 208 bytes of RAM including 16 bytes of working register.

Using the SAM88RCRI design approach, the following peripherals were integrated with the SAM88RCRI core:

- Three configurable I/O ports (14 pin, at 20 pin)

- 14-bit programmable pins for external interrupts (at 20 pin)

- 8-bit timer/counter with two operating modes

# OTP

The S3C9654/C9658 microcontroller is also available in OTP (One Time Programmable) version. S3P9658 microcontroller has an on-chip 4/8 Kbyte one-time-programmable EPROM instead of masked ROM. The S3P9658 is comparable to S3C9654/C9658, both in function and in pin configuration.

# FEATURES

## CPU

SAM88RCRI CPU core

## Memory

- 4-K byte internal program memory (ROM S3C9654)

- 8-K byte internal program memory (ROM S3P9658/C9658)

- 208-byte RAM

- 16 bytes of working register

## **Instruction Set**

- 41 instructions

- IDLE and STOP instructions added for powerdown modes

## Instruction Execution Time

• 0.66 μs at 6 MHz f<sub>OSC</sub>

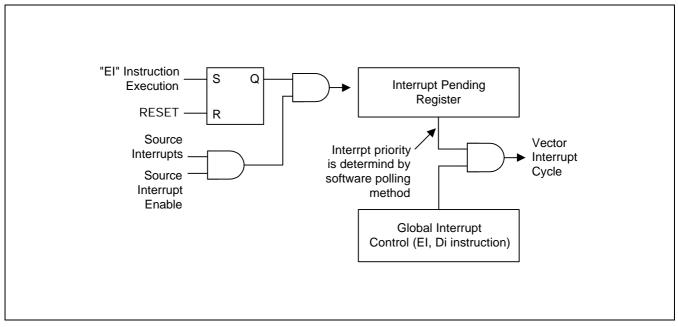

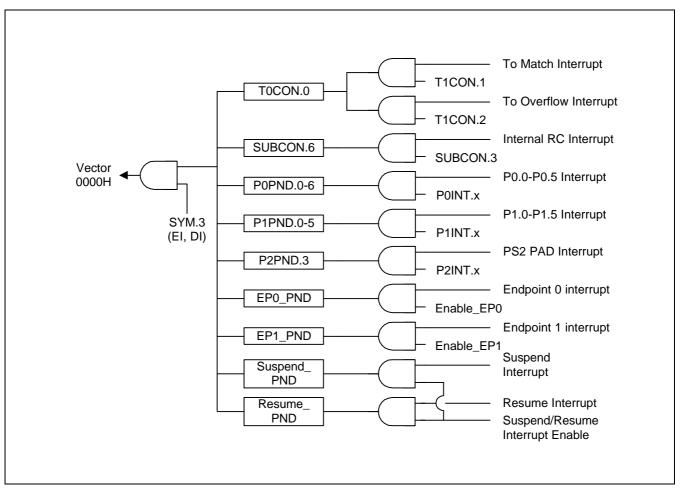

## Interrupts

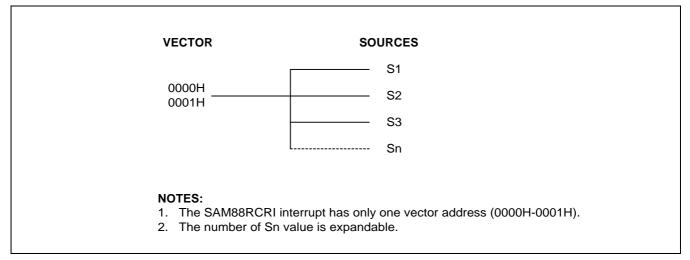

- 14 interrupt sources with one vector (20 pin)

- 12 interrupt sources with one vector (18 pin)

- 10 interrupt sources with one vector (16 pin)

- One level, one vector interrupt structure

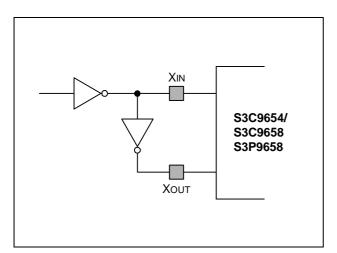

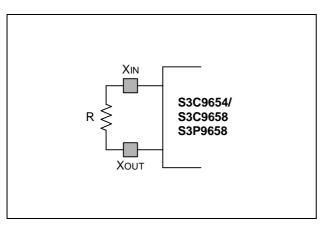

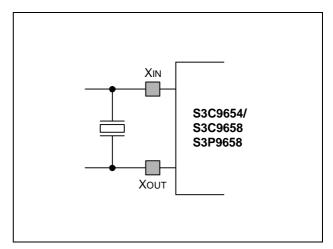

## **Oscillation Circuit Options**

- 6 MHz crystal/ceramic oscillator

- External clock source

- RC oscillator

- Embedded oscillation capacitor (XI, XO, 33pF)

## **General I/O**

- 14 bit-programmable I/O pins (20 pin)

- 12 bit-programmable I/O pins (18 pin)

- 10 bit-programmable I/O pins (16 pin)

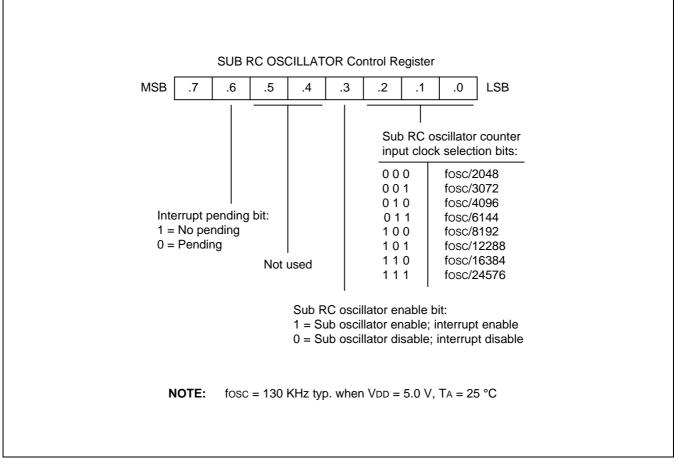

## Sub Oscillator

- Internal RC sub oscillator

- Auto interrupt wake-up

## **Timer/Counter**

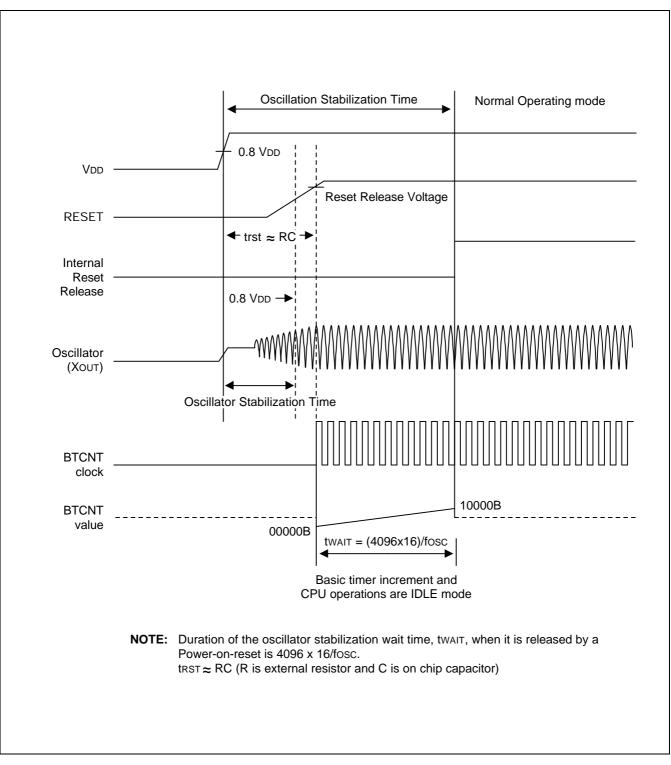

- One 8-bit basic timer for watchdog function and programmable oscillation stabilization interval generation function

- One 8-bit timer/counter with Compare/Overflow counter

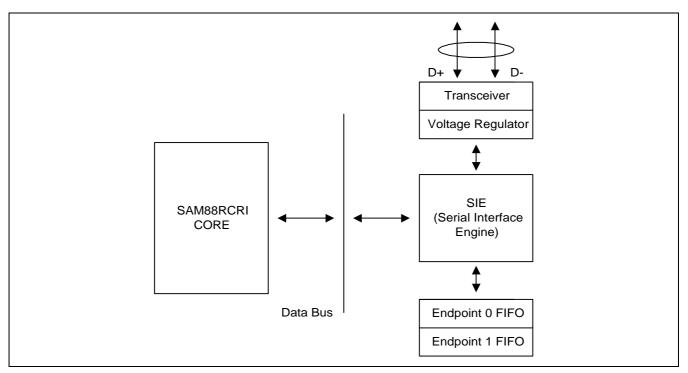

## **USB Serial Bus**

- Compatible to USB low speed (1.5 Mbps) device 1.0 specification.

- Serial bus interface engine (SIE)

- Packet decoding/generation

- CRC generation and checking

- NRZI encoding/decoding and bit-stuffing

- Two 8-byte receive/transmit USB buffer

## **Operating Temperature Range**

•  $-0^{\circ}C$  to  $+85^{\circ}C$

## **Operating Voltage Range**

• 4.0 V to 5.25 V

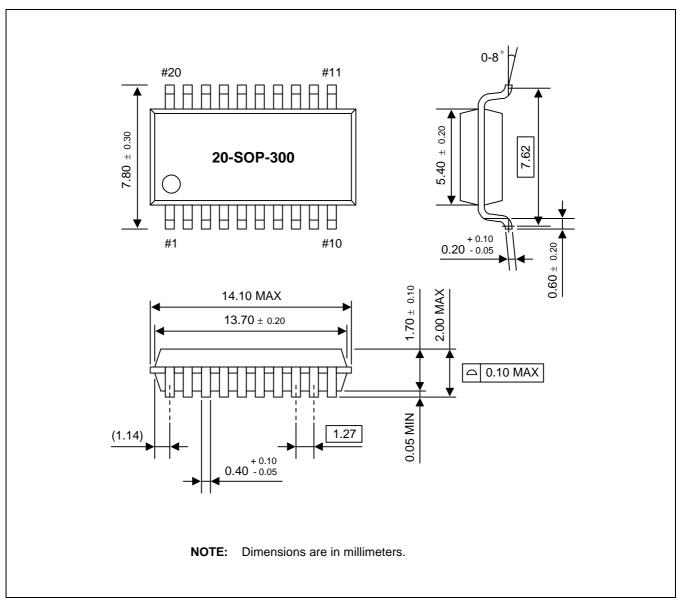

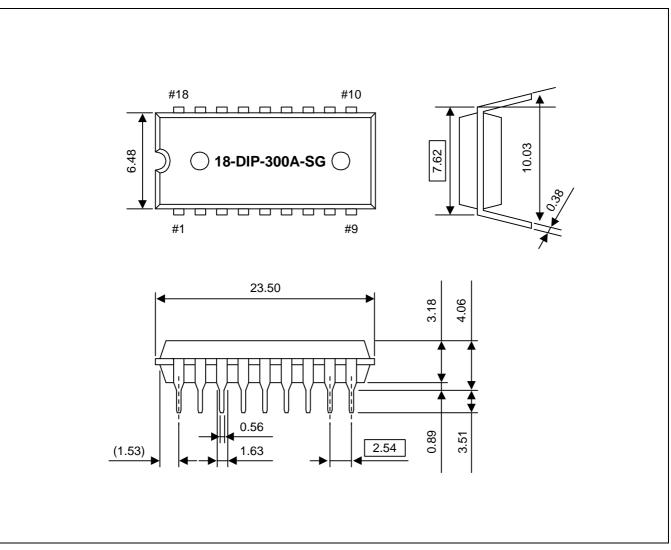

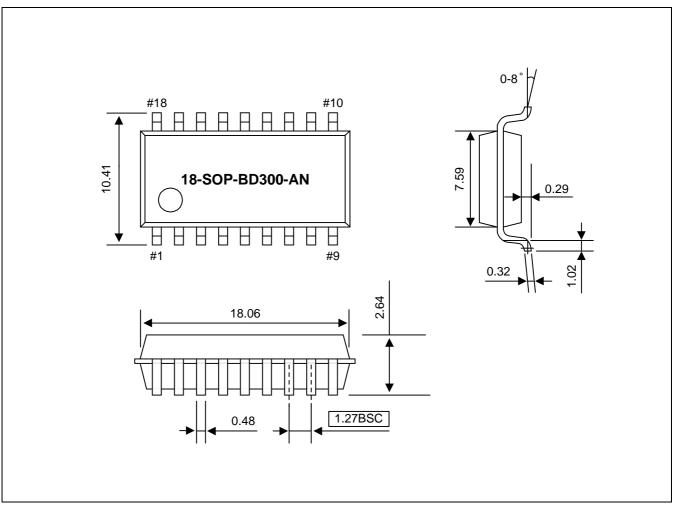

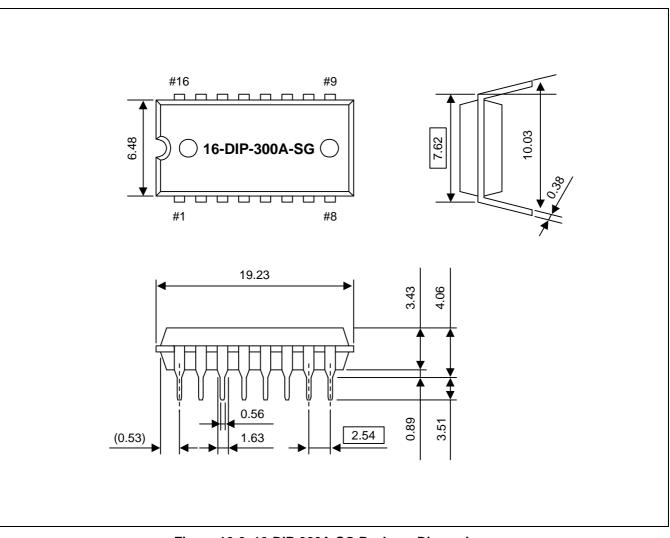

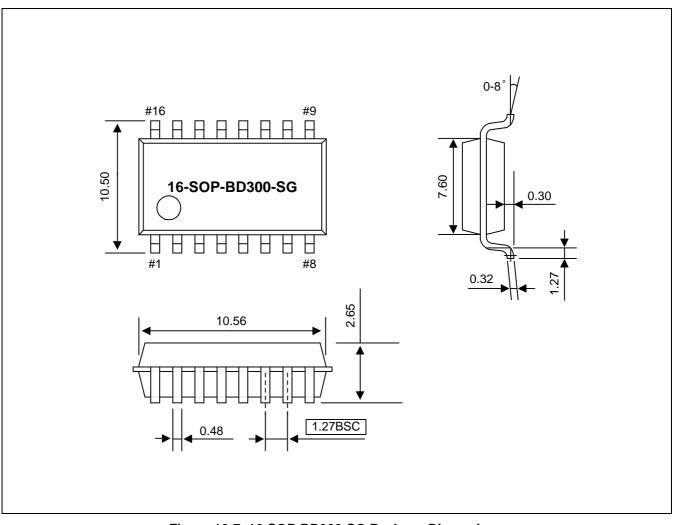

## Package Types

- 16, 18, 20 pin DIP

- 16, 18, 20 pin SOP

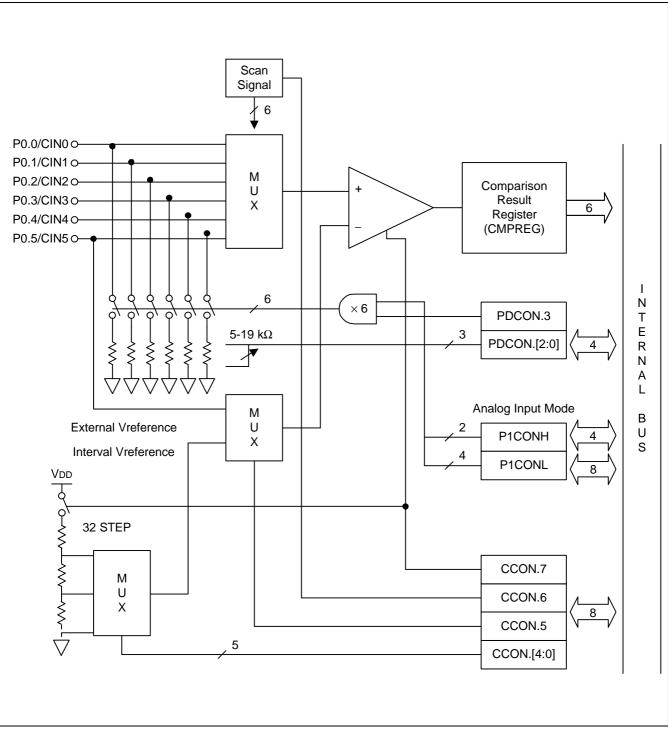

## Comparator

- 6-channel mode, 32 step resolution

- 5-channel mode, external reference

- Low EMI design

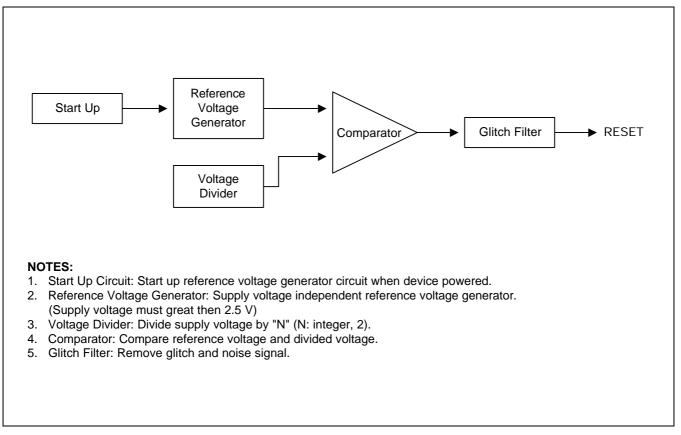

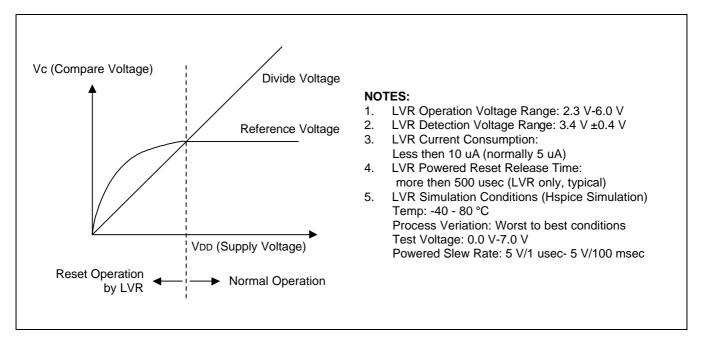

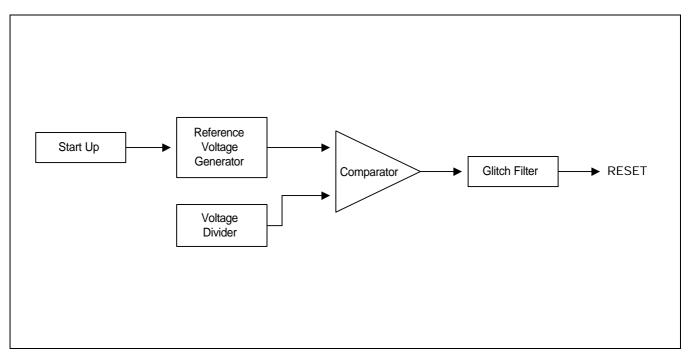

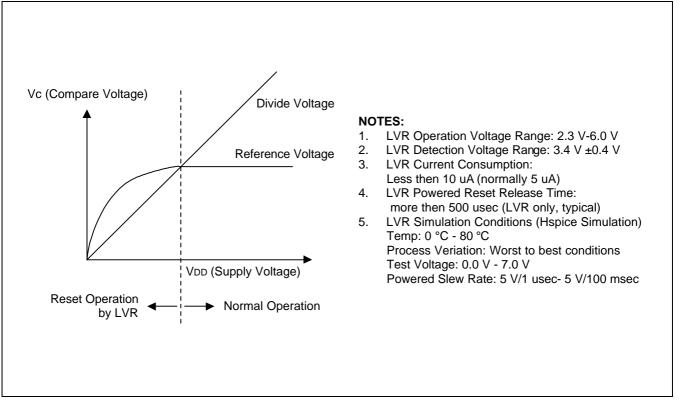

## Low Voltage Reset

- Low voltage Reset

- Power on Reset

## High Sink Current Pin for LED

• P0.0 (V<sub>OL</sub>: 0.4 V, 50mA)

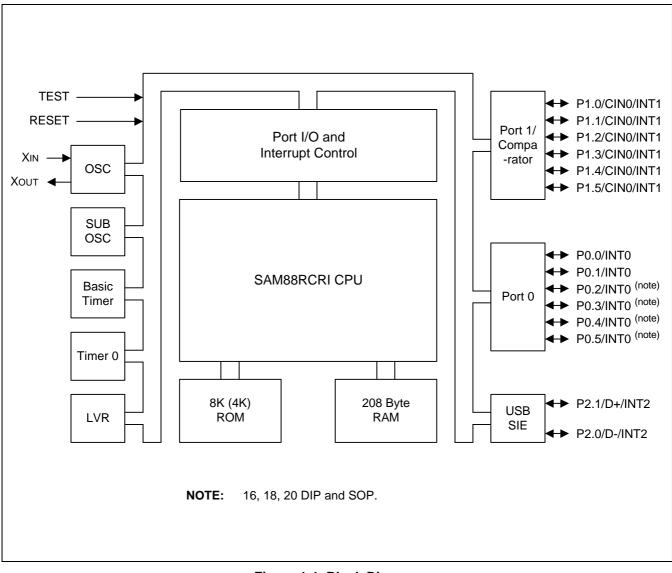

# **BLOCK DIAGRAM**

Figure 1-1. Block Diagram

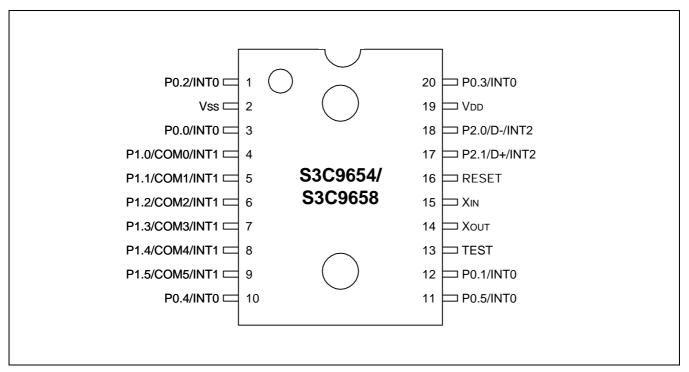

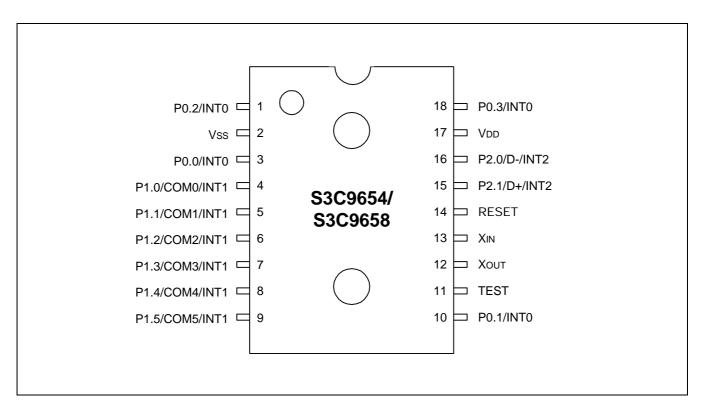

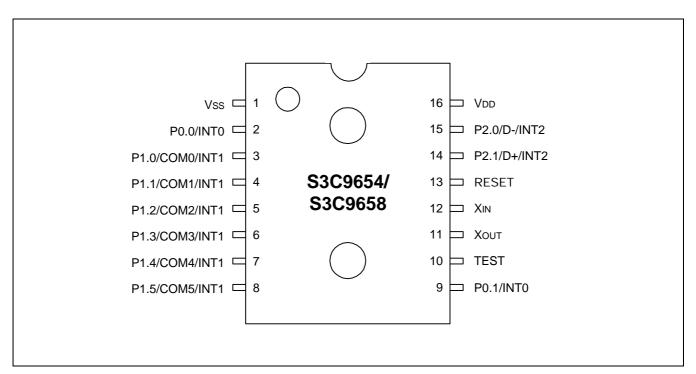

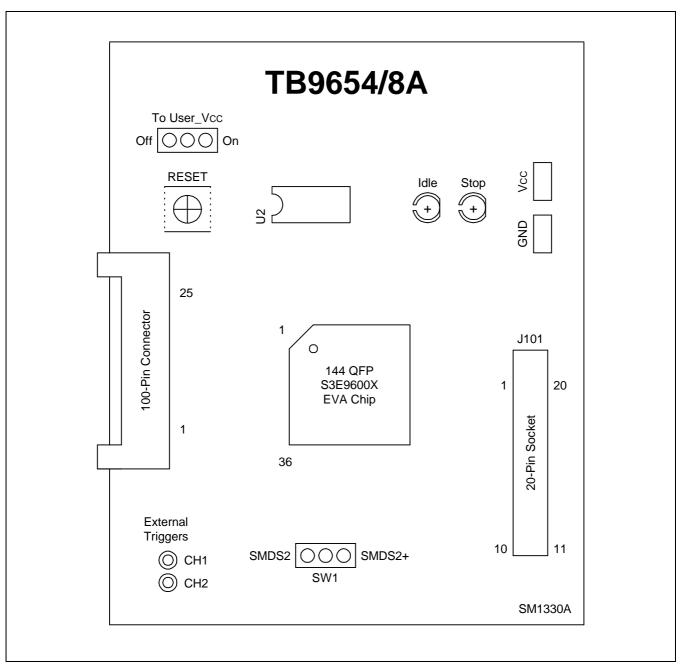

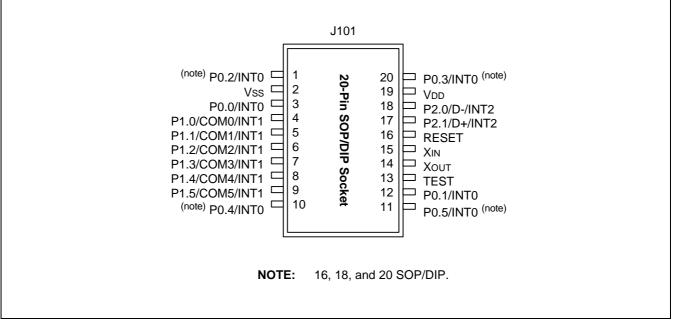

# **PIN ASSIGNMENTS**

Figure 1-2. Pin Assignment (20 Pin)

Figure 1-3. Pin Assignment (18 Pin)

Figure 1-4. Pin Assignment (16 Pin)

| Pin Names                         | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                         | Circuit<br>Number | Pin<br>Numbers          | Share<br>Pins  |

|-----------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|----------------|

| P0.0                              | I/O         | Bit-programmable I/O port for Schmitt trigger<br>input or n-ch open drain output (50 mA).<br>Pull-up resistor is assignable to input pin by<br>software and is automatically disabled for<br>output pin. Port 0 can be individually configured<br>as external interrupt input.                                                          | SK                | 3                       | INTO           |

| P0.1–P0.5                         | I/O         | Bit-programmable I/O port for Schmitt trigger<br>input or push-pull output. Pull-up resistors<br>individually assignable to input pins by software<br>and are automatically disabled for output pins.<br>Port 0 can be individually configured as<br>external interrupt inputs.                                                         | D                 | 1, 10, 11,<br>12, 20    | INTO           |

| P1.0-P1.5                         | I/O         | Bit-programmable I/O port for Schmitt trigger<br>input or push-pull output. Pull-up resistors are<br>individually assignable to input pins by<br>software. Port 1 can be configured as<br>comparator input or external interrupt inputs.<br>Pull-down resistors are individually assignable.<br>(in comparator input)                   | CP                | 4–9                     | CIN0-5<br>INT1 |

| P2.0/D-<br>_<br>P2.1/D+           | I/O         | Bit-programmable I/O port for Schmitt trigger<br>input or n-ch open drain output. Pull-up<br>resistors are individually assignable to input<br>pins by software and are automatically disabled<br>for output pins. Port 2 can be individually<br>configured as external interrupt inputs. Also it<br>can be configured as an USB ports. | CP                | 17, 18                  | INT2           |

| X <sub>OUT,</sub> X <sub>IN</sub> | _           | System clock input and output pin<br>(crystal/ceramic oscillator, or external clock<br>source)                                                                                                                                                                                                                                          | -                 | 14, 15                  | -              |

| INT0                              | Ι           | External interrupt for bit-programmable port 0                                                                                                                                                                                                                                                                                          | D                 | 1, 3, 10,<br>11, 12, 20 | Port 0         |

| INT1                              | Ι           | External interrupt for bit-programmable port 1                                                                                                                                                                                                                                                                                          | D                 | 4–9                     | Port 1         |

| INT2                              | I           | External interrupt for bit-programmable port 2                                                                                                                                                                                                                                                                                          | D                 | 17, 18                  | Port 2         |

| V <sub>DD</sub>                   | -           | Power input pin                                                                                                                                                                                                                                                                                                                         | _                 | 19                      | _              |

| V <sub>SS</sub>                   | Ι           | $V_{SS}$ is a ground power for CPU core.                                                                                                                                                                                                                                                                                                | _                 | 2                       | _              |

| RESET                             | 1           | Reset input pin (Pull-up register embedded)                                                                                                                                                                                                                                                                                             | _                 | 16                      | _              |

# Table 1-1. Signal Descriptions

| Circuit Number | Circuit Type | S3C9654/C9658/P9658 Assignments |

|----------------|--------------|---------------------------------|

| С              | 0            |                                 |

| D              | I/O          | Port 0.1–5, INT0, INT1, INT2    |

| SK             | I/O          | Port 0.0                        |

| СР             | I/O          | Port 1, Port 2                  |

Table 1-2. Pin Circuit Assignments for the S3C9654/C9658/P9658

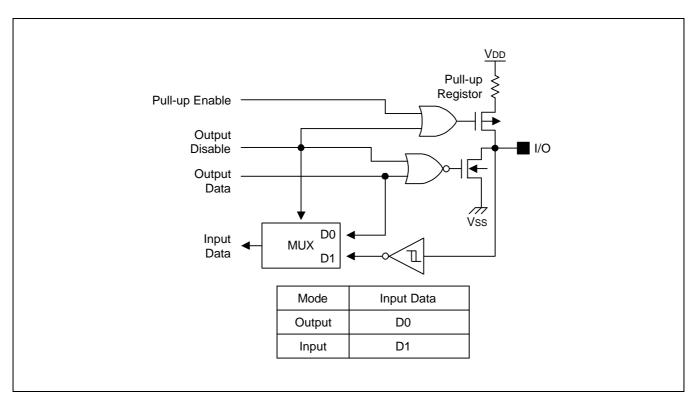

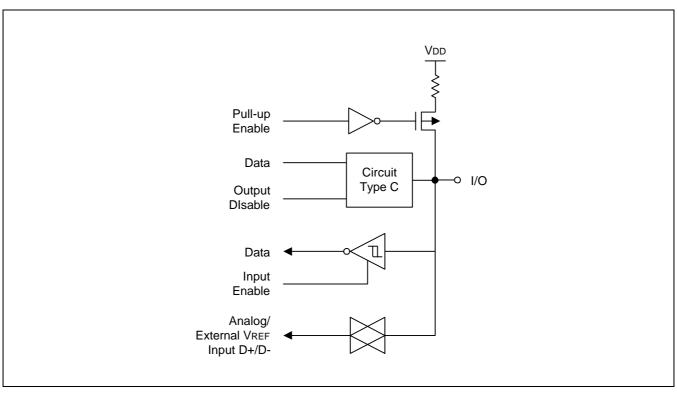

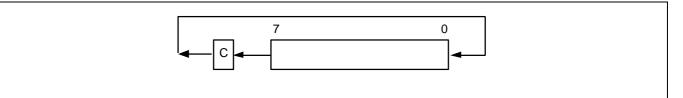

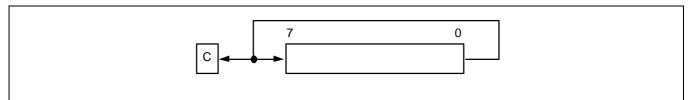

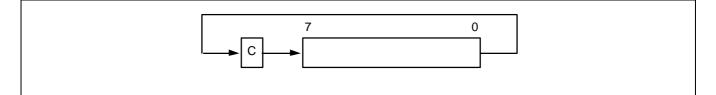

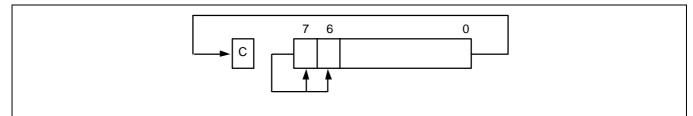

NOTE: Diagrams of circuit types C–D, and F-8 are presented below.

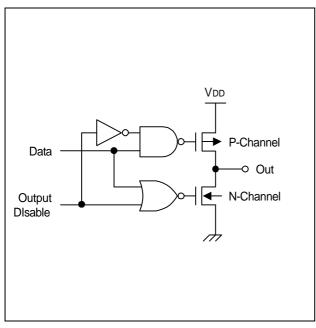

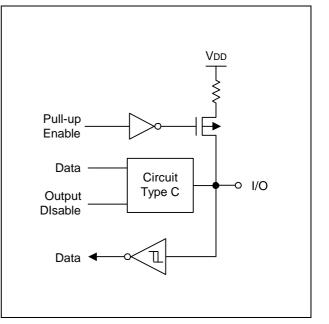

Figure 1-5. Pin Circuit Type C

Figure 1-6. Pin Circuit Type D

Figure 1-7. Pin Circuit Type SK

Figure 1-8. Pin Circuit Type CP

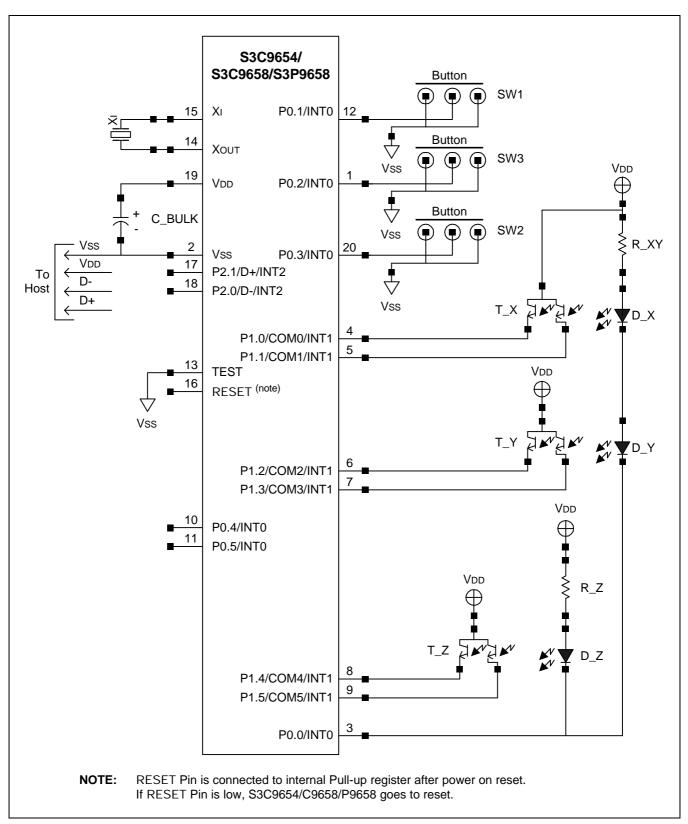

Figure 1-9. USB Mouse Circuit Diagram

NOTES

# **2** ADDRESS SPACES

# **OVERVIEW**

The S3C9654/C9658/P9658 microcontroller has two kinds of address space:

- Program memory (ROM)

- Internal register file

A 13-bit address bus supports both program memory. Special instructions and related internal logic determine when the 13-bit bus carries addresses for program memory. A separate 8-bit register bus carries addresses and data between the CPU and the internal register file.

The S3C9654/C9658 has 4/8 Kbytes of mask-programmable program memory on-chip. The S3C9654/C9658/P9658 microcontroller has 192 bytes general-purpose registers in its internal register file. Forty-eight bytes in the register file are mapped for system and peripheral control functions.

# **PROGRAM MEMORY (ROM)**

## NORMAL OPERATING MODE (INTERNAL ROM)

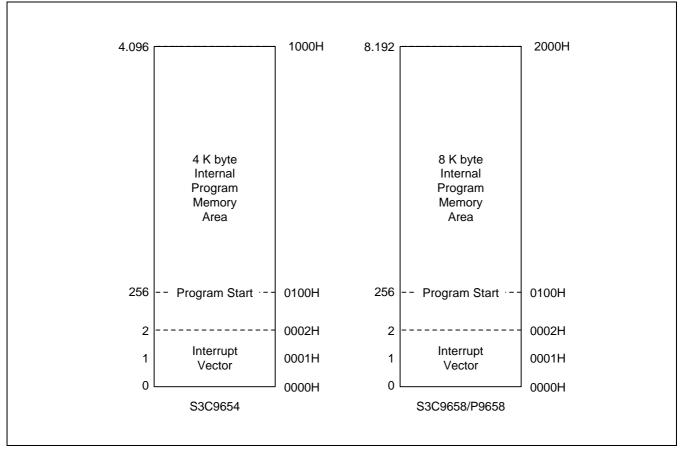

The S3C9654/C9658/P9658 has 4/8 Kbytes of internal mask-programmable program memory. The first 2 bytes of the ROM (0000H–0001H) are an interrupt vector address. The program reset address in the ROM is 0100H.

Figure 2-1. S3C9654/C9658/P9658 Program Memory Address Space

# **REGISTER ARCHITECTURE**

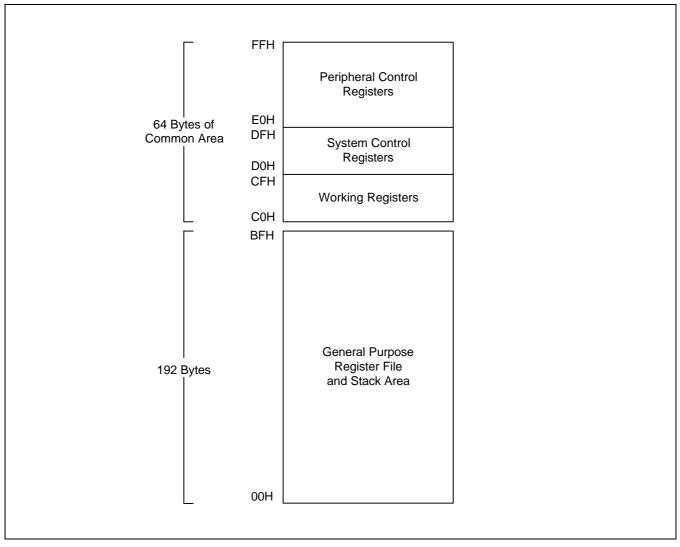

The upper 64 bytes of the S3C9654/C9658/P9658's internal register file are addressed as working registers, system control registers and peripheral control registers. The lower 192 bytes of internal register file (00H–BFH) is called the general purpose register space.

For many SAM88RCRI microcontrollers, the addressable area of the internal register file is further expanded by the additional of one or more register pages at general purpose register space (00H–BFH). This register file expansion is not implemented in the S3C9654/C9658/P9658.

Figure 2-2. Internal Register File Organization

# COMMON WORKING REGISTER AREA (C0H–CFH)

The SAM88RCRI register architecture provides an efficient method of working register addressing that takes full advantage of shorter instruction formats to reduce execution time.

This16-byte address range is called common area. That is, locations in this area can be used as working registers by operations that address any location on any page in the register file. Typically, these working registers serve as temporary buffers for data operations between different pages. However, because the S3C9654/C9658/P9658 uses only page 0, you can use the common area for any internal data operation.

The Register (R) addressing mode can be used to access this area

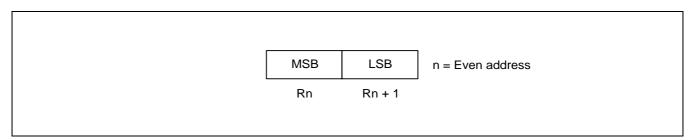

Registers are addressed either as a single 8-bit register or as a paired 16-bit register. In 16-bit register pairs, the address of the first 8-bit register is always an even number and the address of the next register is an odd number. The most significant byte of the 16-bit data is always stored in the even-numbered register; the least significant byte is always stored in the next (+ 1) odd-numbered register.

Figure 2-3. 16-Bit Register Pairs

## PROGRAMMING TIP — Addressing the Common Working Register Area

As the following examples show, you should access working registers in the common area, locations C0H–CFH, using working register addressing mode only.

| Examples: | 1. | LD     | 0C2H,40H                   | ;   | Invalid addressing mode!                        |

|-----------|----|--------|----------------------------|-----|-------------------------------------------------|

|           |    | Use wo | orking register addressing | ins | tead:                                           |

|           |    | LD     | R2,40H                     | ;   | R2 (C2H) $\leftarrow$ the value in location 40H |

|           | 2. | ADD    | 0C3H,#45H                  | ;   | Invalid addressing mode!                        |

|           |    | Use wo | orking register addressing | ins | tead:                                           |

|           |    | ADD    | R3,#45H                    | ;   | R3 (C3H) ← R3 + 45H                             |

## SYSTEM STACK

KS86-series microcontrollers use the system stack for subroutine calls and returns and to store data. The PUSH and POP instructions are used to control system stack operations. The S3C9654/C9658/P9658 architecture supports stack operations in the internal register file.

## STACK OPERATIONS

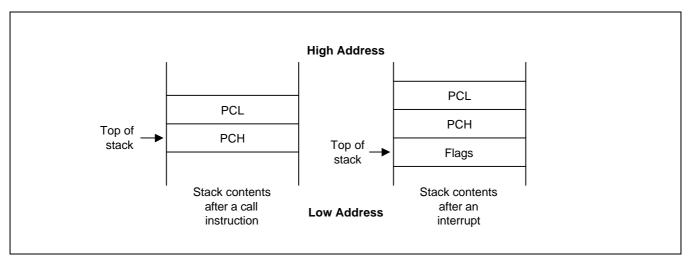

Return addresses for procedure calls and interrupts and data are stored on the stack. The contents of the PC are saved to stack by a CALL instruction and restored by the RET instruction. When an interrupt occurs, the contents of the PC and the FLAGS register are pushed to the stack. The IRET instruction then pops these values back to their original locations. The stack address is always decremented before a push operation and incremented after a pop operation. The stack pointer (SP) always points to the stack frame stored on the top of the stack, as shown in Figure 2-4.

Figure 2-4. Stack Operations

## STACK POINTER (SP)

Register location D9H contains the 8-bit stack pointer (SP) that is used for system stack operations. After a reset, the SP value is undetermined.

Because only internal memory space is implemented in the KS86C6104/P6104, the SP must be initialized to an 8-bit value in the range 00H–BFH.

#### NOTE

In case a Stack Pointer is initialized to 00H, it is decreased to FFH when stack operation starts. This means that a Stack Pointer access invalid stack area.

# PROGRAMMING TIP — Standard Stack Operations Using PUSH and POP

The following example shows you how to perform stack operations in the internal register file using PUSH and POP instructions:

| LD                            | SP,#0C0H                 | ; SP $\leftarrow$ C0H (Normally, the SP is set to 0C0H by the ; initialization routine)                                                                    |

|-------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH<br>PUSH<br>PUSH<br>PUSH  | SYM<br>CCON<br>20H<br>R3 | <ul> <li>Stack address 0BFH ← SYM</li> <li>Stack address 0BEH ← CCON</li> <li>Stack address 0BDH ← 20H</li> <li>Stack address 0BCH ← R3</li> </ul>         |

| •<br>POP<br>POP<br>POP<br>POP | R3<br>20H<br>CCON<br>SYM | <ul> <li>; R3 ← Stack address 0BCH</li> <li>; 20H ← Stack address 0BDH</li> <li>; CCON ← Stack address 0BEH</li> <li>; SYM ← Stack address 0BFH</li> </ul> |

# **3** ADDRESSING MODES

# **OVERVIEW**

Instructions that are stored in program memory are fetched for execution using the program counter. Instructions indicate the operation to be performed and the data to be operated on. Addressing mode is the method used to determine the location of the data operand. The operands specified in SAM88RCRI instructions may be condition codes, immediate data, or a location in the register file, program memory, or data memory.

The SAM88RCRI instruction set supports six explicit addressing modes. Not all of these addressing modes are available for each instruction. The addressing modes and their symbols are as follows:

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Relative Address (RA)

- Immediate (IM)

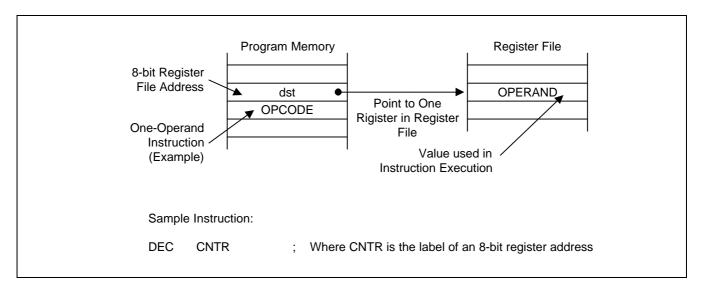

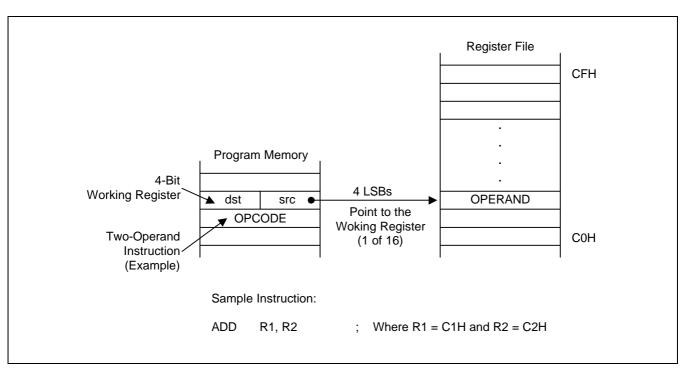

#### **REGISTER ADDRESSING MODE (R)**

In Register addressing mode, the operand is the content of a specified register (see Figure 3-1). Working register addressing differs from Register addressing because it uses a 16-byte working register space in the register file and a 4-bit register within that space (see Figure 3-2).

Figure 3-1. Register Addressing

Figure 3-2. Working Register Addressing

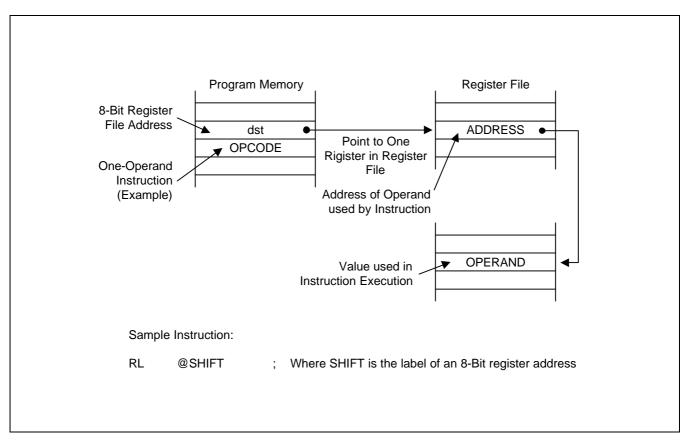

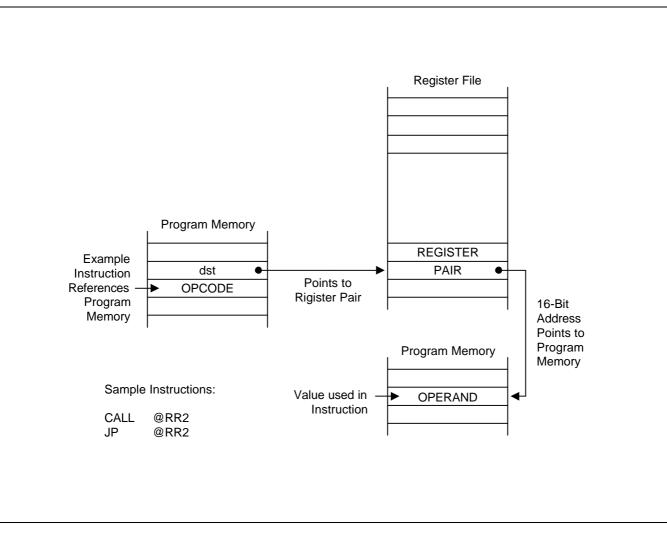

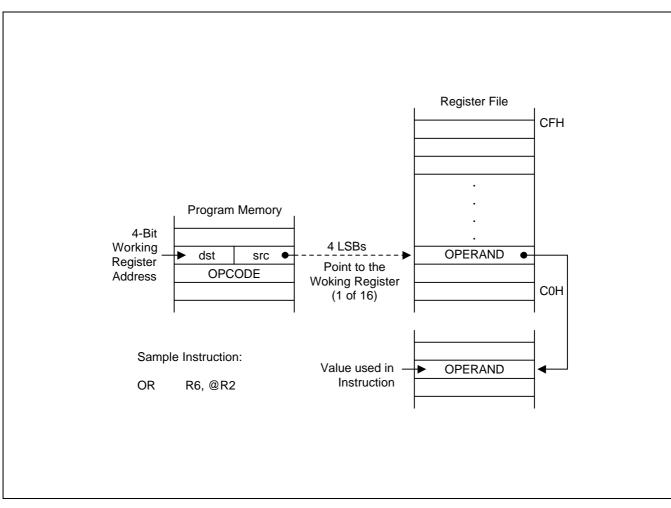

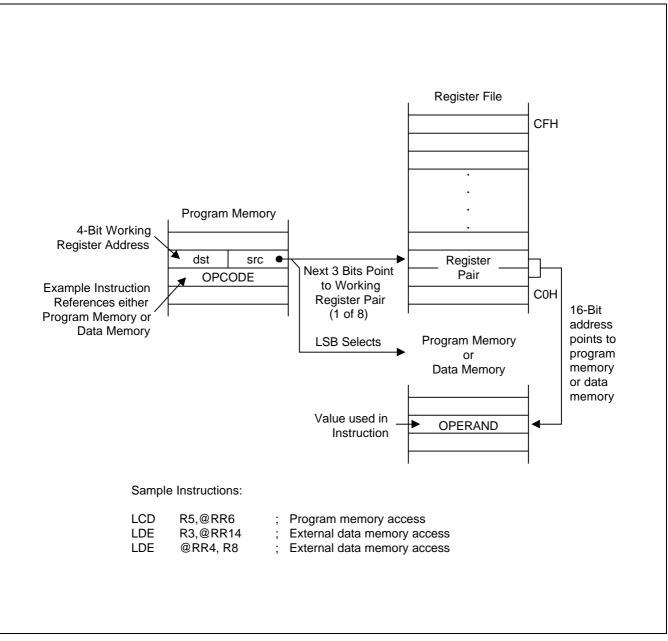

#### INDIRECT REGISTER ADDRESSING MODE (IR)

In Indirect Register (IR) addressing mode, the content of the specified register or register pair is the address of the operand. Depending on the instruction used, the actual address may point to a register in the register file, to program memory (ROM), or to an external memory space (see Figures 3-3 through 3-6).

You can use any 8-bit register to indirectly address another register. Any 16-bit register pair can be used to indirectly address another memory location.

Figure 3-3. Indirect Register Addressing to Register File

## INDIRECT REGISTER ADDRESSING MODE (Continued)

Figure 3-4. Indirect Register Addressing to Program Memory

INDIRECT REGISTER ADDRESSING MODE (Continued)

Figure 3-5. Indirect Working Register Addressing to Register File

Figure 3-6. Indirect Working Register Addressing to Program or Data Memory

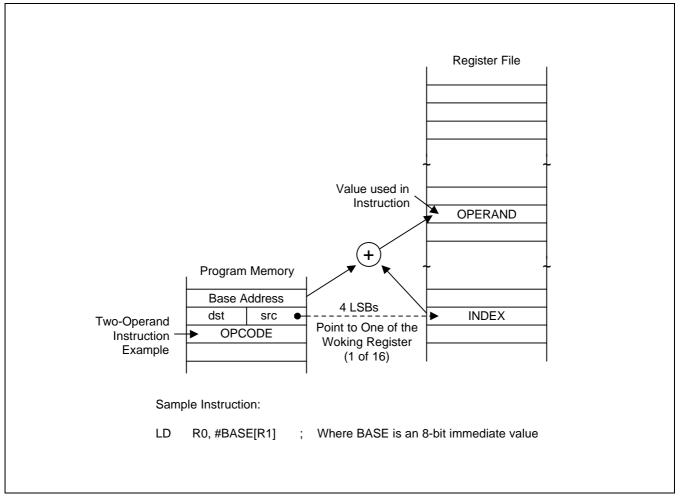

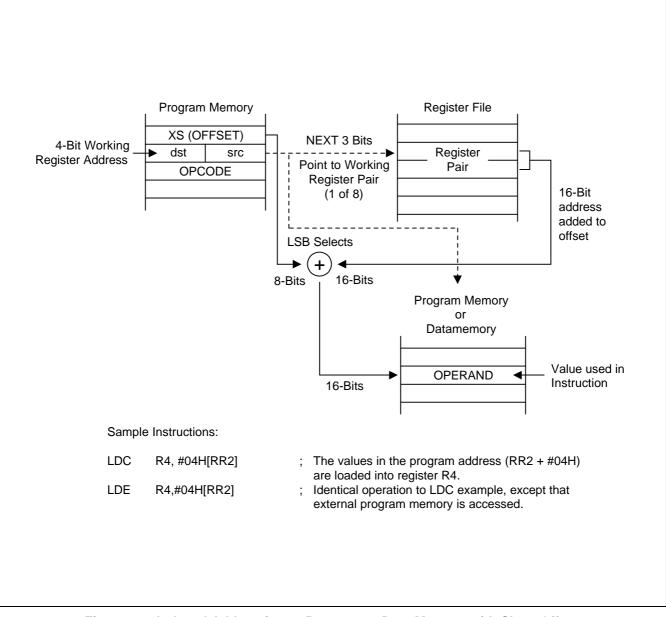

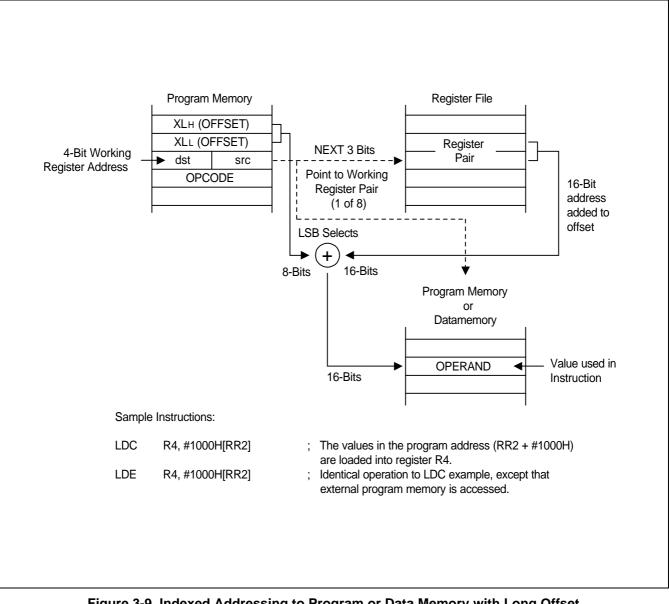

#### **INDEXED ADDRESSING MODE (X)**

Indexed (X) addressing mode adds an offset value to a base address during instruction execution in order to calculate the effective operand address (see Figure 3-7). You can use Indexed addressing mode to access locations in the internal register file or in external memory.

In short offset Indexed addressing mode, the 8-bit displacement is treated as a signed integer in the range of -128 to +127. This applies to external memory accesses only (see Figure 3-8).

For register file addressing, an 8-bit base address provided by the instruction is added to an 8-bit offset contained in a working register. For external memory accesses, the base address is stored in the working register pair designated in the instruction. The 8-bit or 16-bit offset given in the instruction is then added to the base address (see Figure 3-9).

The only instruction that supports Indexed addressing mode for the internal register file is the Load instruction (LD). The LDC and LDE instructions support Indexed addressing mode for internal program memory, external program memory, and for external data memory, when implemented.

Figure 3-7. Indexed Addressing to Register File

## INDEXED ADDRESSING MODE (Continued)

Figure 3-8. Indexed Addressing to Program or Data Memory with Short Offset

## INDEXED ADDRESSING MODE (Concluded)

Figure 3-9. Indexed Addressing to Program or Data Memory with Long Offset

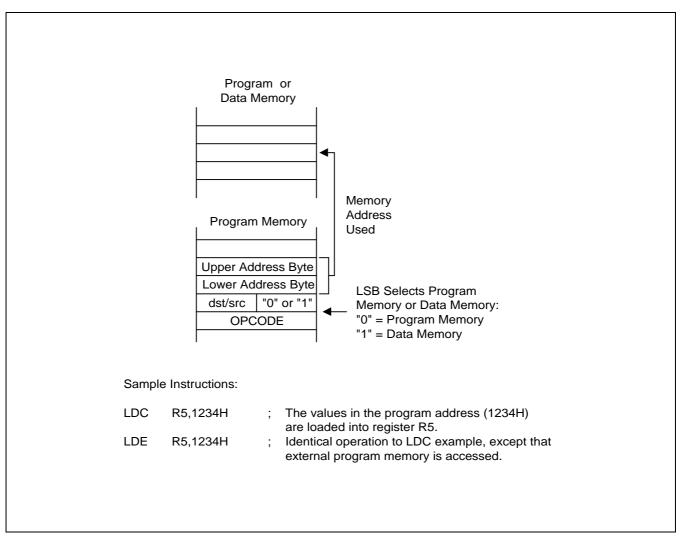

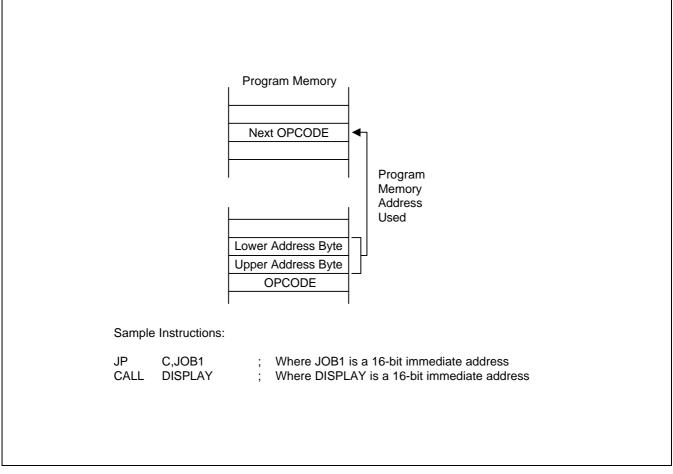

#### **DIRECT ADDRESS MODE (DA)**

In Direct Address (DA) mode, the instruction provides the operand's 16-bit memory address. Jump (JP) and Call (CALL) instructions use this addressing mode to specify the 16-bit destination address that is loaded into the PC whenever a JP or CALL instruction is executed.

The LDC and LDE instructions can use Direct Address mode to specify the source or destination address for Load operations to program memory (LDC) or to external data memory (LDE), if implemented.

Figure 3-10. Direct Addressing for Load Instructions

#### **DIRECT ADDRESS MODE (Continued)**

Figure 3-11. Direct Addressing for Call and Jump Instructions

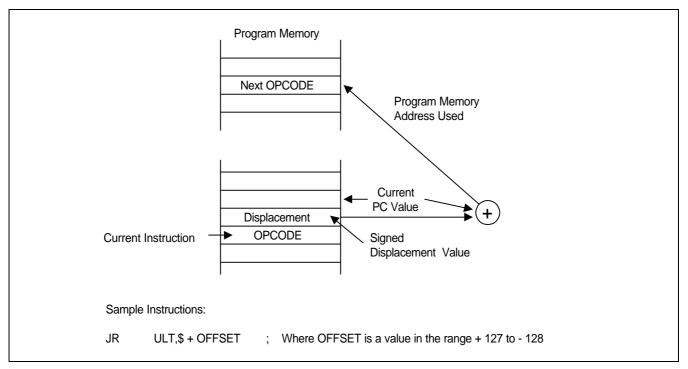

#### **RELATIVE ADDRESS MODE (RA)**

In Relative Address (RA) mode, a two's-complement signed displacement between – 128 and + 127 is specified in the instruction. The displacement value is then added to the current PC value. The result is the address of the next instruction to be executed. Before this addition occurs, the PC contains the address of the instruction immediately following the current instruction.

The instructions that support RA addressing is JR.

Figure 3-12. Relative Addressing

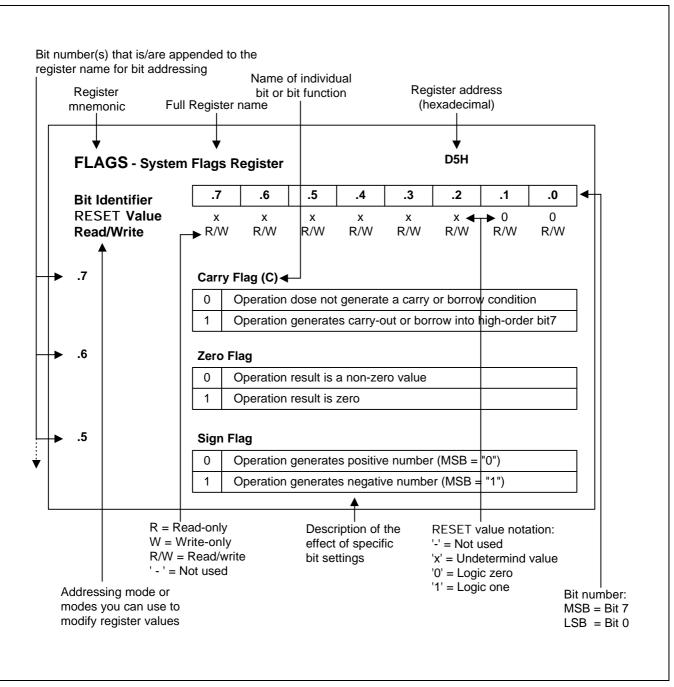

## **IMMEDIATE MODE (IM)**

In Immediate (IM) addressing mode, the operand value used in the instruction is the value supplied in the operand field itself. Immediate addressing mode is useful for loading constant values into registers.

| Program Men                | nory            |

|----------------------------|-----------------|

| OPERANI<br>OPCODE          |                 |

| (The Operand value is in t | he instruction) |

| Sample Instruc             | tion:           |

| LD R0,#0AA                 | λH              |

# 4 CONTROL REGISTERS

# OVERVIEW

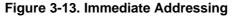

In this section, detailed descriptions of the S3C9654/C9658/P9658 control registers are presented in an easy-toread format. These descriptions will help familiarize you with the mapped locations in the register file. You can also use them as a quick-reference source when writing application programs.

System and peripheral registers are summarized in Table 4-1. Figure 4-1 illustrates the important features of the standard register description format.

Control register descriptions are arranged in alphabetical order according to register mnemonic. More information about control registers is presented in the context of the various peripheral hardware descriptions in Part II of this manual.

| Table 4-1. | System and | Peripheral | <b>Control Registers</b> |  |

|------------|------------|------------|--------------------------|--|

|------------|------------|------------|--------------------------|--|

| Register Name                                         | Mnemonic             | Hex     | R/W |

|-------------------------------------------------------|----------------------|---------|-----|

| General purpose register file & Stack area            | _                    | 00-BFH  | R/W |

| Working register area                                 | _                    | C0H-CFH | R/W |

| Timer 0 Counter register                              | TOCNT                | D0H     | R   |

| Timer 0 data register                                 | TODATA               | D1H     | R/W |

| Timer 0 Control register                              | TOCON                | D2H     | R/W |

| Location D                                            | 3H is not mapped.    |         | ·   |

| Clock control register                                | CLKCON               | D4H     | R/W |

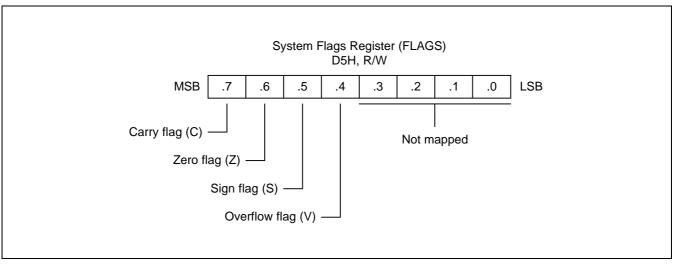

| System FLAG register                                  | FLAGS                | D5H     | R/W |

| Locations D6H                                         | -D8H are not mapped. |         | ·   |

| Stack pointer                                         | SP                   | D9H     | R/W |

| Locations DAH                                         | -DBH are not mapped. |         | ·   |

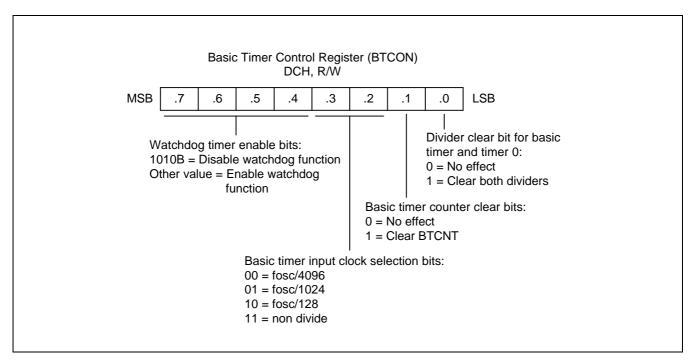

| Basic timer control register                          | BTCON                | DCH     | R/W |

| Basic timer counter                                   | BTCNT                | DDH     | R   |

| Location D                                            | EH is not mapped.    |         | ·   |

| System mode register                                  | SYM                  | DFH     | R/W |

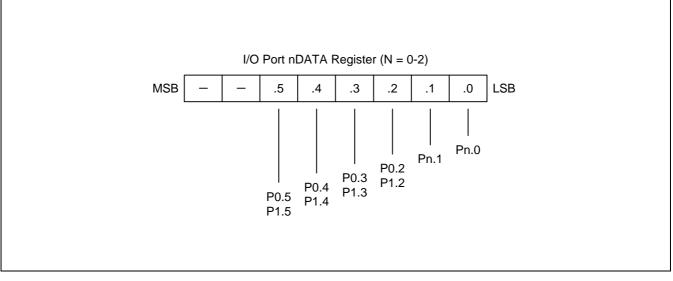

| Port 0 data register                                  | P0                   | E0H     | R/W |

| Port 1 data register                                  | P1                   | E1H     | R/W |

| Port 2 data register                                  | P2                   | E2H     | R/W |

| Port 1 pull-down control                              | PDCON                | E3H     | R/W |

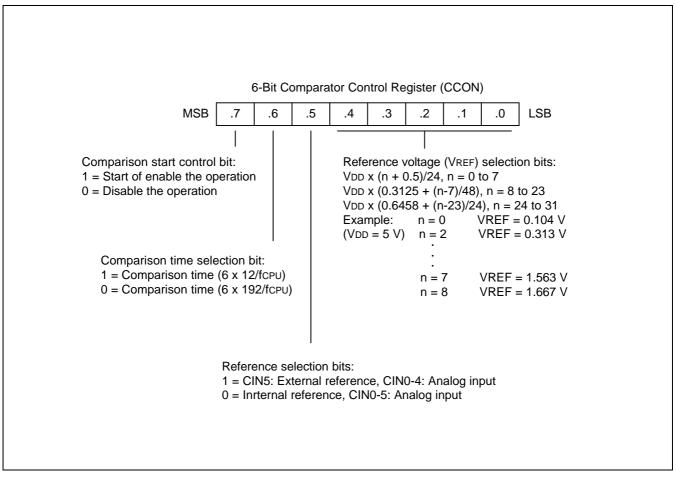

| Comparator control mode register                      | CCON                 | E4H     | R/W |

| Comparison result register                            | CDATA                | E5H     | R   |

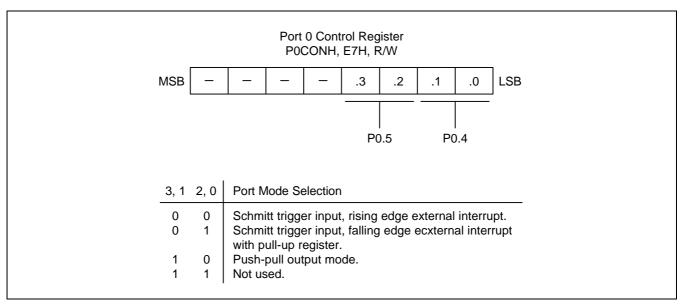

| Port 0 low nibble control register                    | P0CONL               | E6H     | R/W |

| Port 0 high nibble control register                   | P0CONH               | E7H     | R/W |

| Port 1 high nibble control register                   | P1CONH               | E8H     | R/W |

| Port 1 low nibble control register                    | P1CONL               | E9H     | R/W |

| Port 0 interrupt control register                     | POINT                | EAH     | R/W |

| Port 0 interrupt pending register                     | P0PND                | EBH     | R/W |

| Port 1 interrupt control register                     | P1INT                | ECH     | R/W |

| Port 1 interrupt pending register                     | P1PND                | EDH     | R/W |

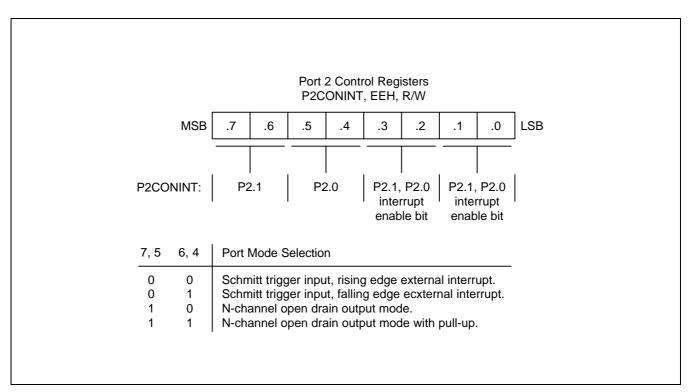

| Port 2 control/interrupt control and pending register | P2CONINT             | EEH     | R/W |

| Sub oscillator control register                       | SUBCON               | EFH     | R/W |

| Register Name                        | Mnemonic            | Hex | R/W |

|--------------------------------------|---------------------|-----|-----|

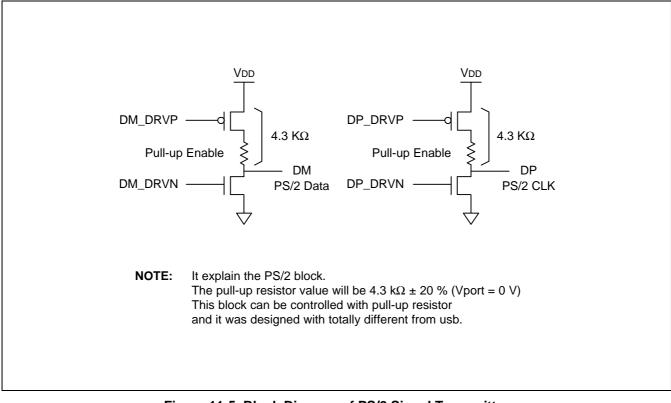

| USB function address register        | FADDR               | F0H | R/W |

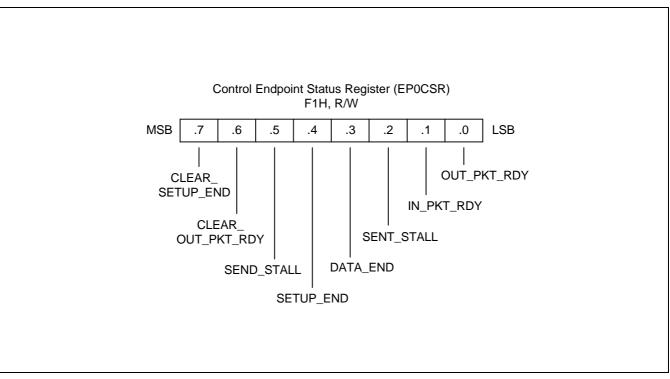

| Control endpoint status register     | EP0CSR              | F1H | R/W |

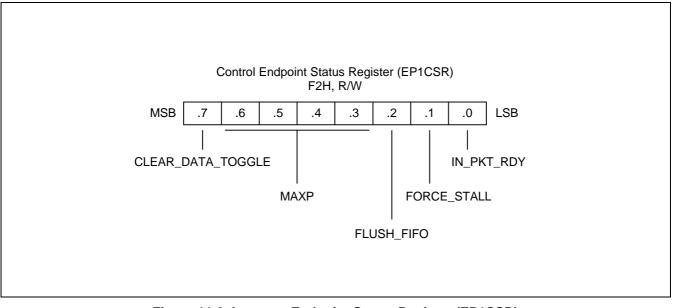

| Interrupt endpoint status register   | EP1CSR              | F2H | R/W |

| Control endpoint byte count register | EP0BCNT             | F3H | R   |

| Control endpoint FIFO register       | EP0FIFO             | F4H | W   |

| Interrupt endpoint FIFO register     | EP1FIFO             | F5H | W   |

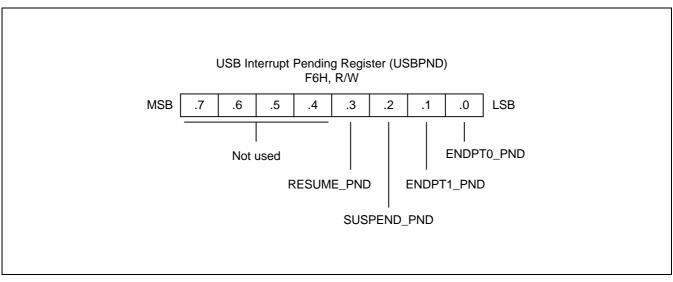

| USB interrupt pending register       | USBPND              | F6H | R/W |

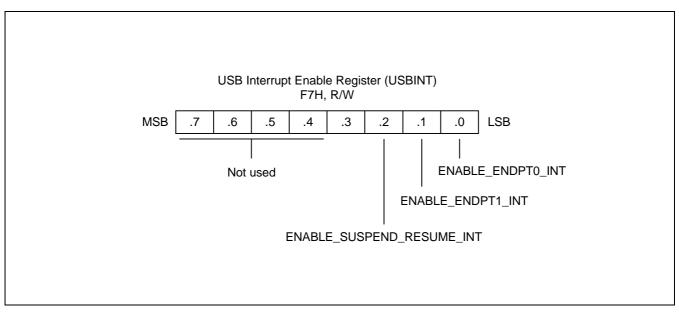

| USB interrupt enable register        | USBINT              | F7H | R/W |

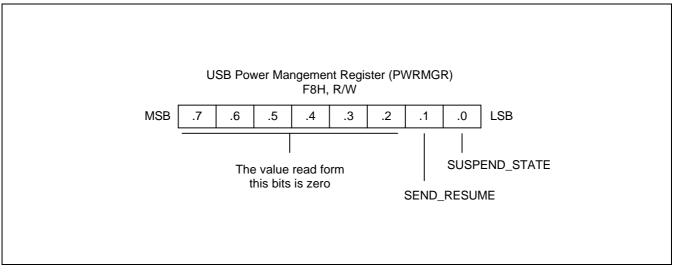

| USB power management register        | PWRMGR              | F8H | R/W |

| Locations                            | s F9H is not mapped |     |     |

| Locations                            | s FAH is not mapped |     |     |

| USB mode select register             | USBSEL              | FBH | R/W |

| Locations                            | FCH is not mapped   |     |     |

| Sink current control register        | SNKCON              | FDH | R/W |

| USB signal control                   | XCON                | FEH | R/W |

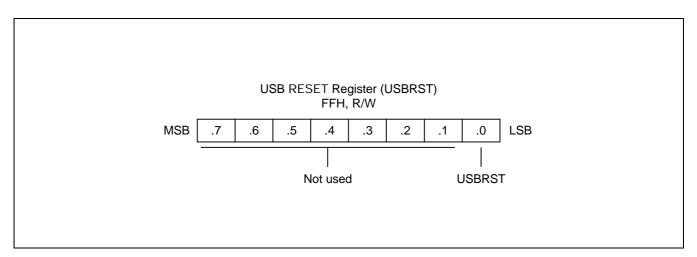

| USB reset register                   | USBRST              | FFH | R/W |

Table 4-1. System and Peripheral Control Registers (Continued)

## NOTES:

1. RESET = value notation

"\_" = Not used.

"x" = Undetermind value.

Figure 4-1. Register Description Format

| BTCON - Basic  | Tim | er C   | ontrol R               | egister               |             |        |     |     | DCH |

|----------------|-----|--------|------------------------|-----------------------|-------------|--------|-----|-----|-----|

| Bit Identifier |     | 7      | .6                     | .5                    | .4          | .3     | .2  | .1  | .0  |

| RESET Value    | (   | 0      | 0                      | 0                     | 0           | 0      | 0   | 0   | 0   |

| Read/Write     | R   | /W     | R/W                    | R/W                   | R/W         | R/W    | R/W | R/W | R/W |

| .7 – .4        | Wat | chdo   | g Timer Ei             | nable Bits            |             |        |     |     |     |

|                | 1   | 0      | 1 0                    | Disable w             | atchdog fu  | nction |     |     |     |

|                | Ar  | ny oth | er value               | Enable wa             | atchdog fur | nction |     |     |     |

|                |     |        |                        |                       |             |        |     |     |     |

| .3 – .2        | Bas | ic Tir | ner Input (            | Clock Sele            | ction Bits  |        |     |     |     |

|                | 0   | 0      | f <sub>OSC</sub> /4096 | 6                     |             |        |     |     |     |

|                | 0   | 1      | f <sub>OSC</sub> /1024 | 1                     |             |        |     |     |     |

|                | 1   | 0      | f <sub>OSC</sub> /128  |                       |             |        |     |     |     |

|                | 1   | 1      | Non divid              | ed (f <sub>OSC)</sub> |             |        |     |     |     |

|                |     | 1      |                        |                       |             |        |     |     |     |

| .1             | Bas | ic Tir | ner Counte             | er Clear Bi           | t (note)    |        |     |     |     |

|                | 0   | No e   | effect                 |                       |             |        |     |     |     |

|                | 1   | Clea   | ar BTCNT               |                       |             |        |     |     |     |

|                |     |        |                        |                       |             |        |     |     |     |

.0

# Basic Timer Divider Clear Bit (note)

| 0 | No effect           |

|---|---------------------|

| 1 | Clear both dividers |

**NOTE:** When you write a "1" to BTCON.0 (or BTCON.1), the basic timer counter (or basic timer divider) is cleared. The bit is then cleared automatically to "0".

| CCON - Con     | nparator        | Mod     | e Regis      | ter           |           |     |     |     | E4ł |

|----------------|-----------------|---------|--------------|---------------|-----------|-----|-----|-----|-----|

| Bit Identifier |                 | 7       | .6           | .5            | .4        | .3  | .2  | .1  | .0  |

| RESET Value    | (               | 0       | 0            | 0             | 0         | 0   | 0   | 0   | 0   |

| Read/Write     | R/              | /W      | R/W          | R/W           | R/W       | R/W | R/W | R/W | R/W |

| .7             | Con             | nparat  | or Enable    | Bit           |           |     |     |     |     |

|                | 0               | Disab   | ole compa    | rator         |           |     |     |     |     |

|                | 1               | Enab    | le compar    | ator          |           |     |     |     |     |

|                |                 |         |              |               |           |     |     |     |     |

| .6             | Con             | versio  | on Time      |               |           |     |     |     |     |

|                | 0               | Conv    | version tim  | e (6 × 192    | /fx)      |     |     |     |     |

|                | 1               | Conv    | ersion tim   | e (4 × 12/f   | x)        |     |     |     |     |

| .5             | Exte            | ernal F | Reference    | Voltage       |           |     |     |     |     |

|                | 0               | 1       |              | ice voltage   | 1         |     |     |     |     |

|                | 1               | Exter   | rnal refere  | nce voltage   | е         |     |     |     |     |

|                |                 |         |              |               |           |     |     |     |     |

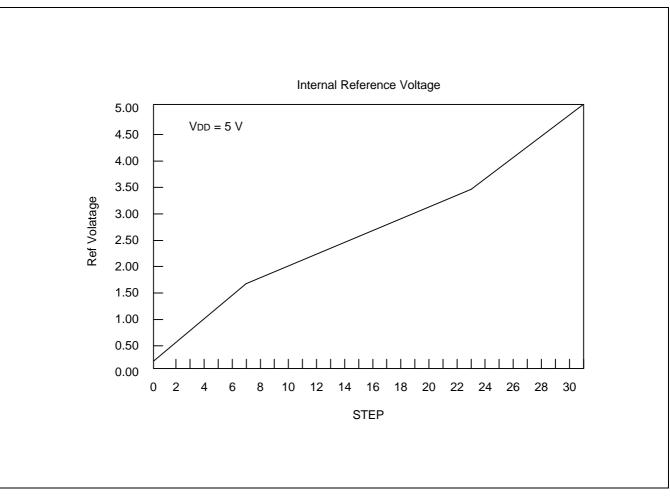

| .4 – .0        | Refe            | erence  | e voltage (  | (Vref) sele   | ction     |     |     |     |     |

|                | $V_{DD}$        | × (n +  | · 0.5)/24, r | n = 0 to 7    |           |     |     |     |     |

|                | <sub>مم</sub> ۷ | × (0.3  | 125 + (n -   | - 7)/48), n = | = 8 to 23 |     |     |     |     |

|                |                 |         |              |               | 04 to 04  |     |     |     |     |

| $V_{DD} \times (0.6458 + (n - 23)/24), n = 24 \text{ to } 31$ |

|---------------------------------------------------------------|

| $V_{\text{DD}} \land (0.0430 + (11 - 23)/24), 11 = 24.031$    |

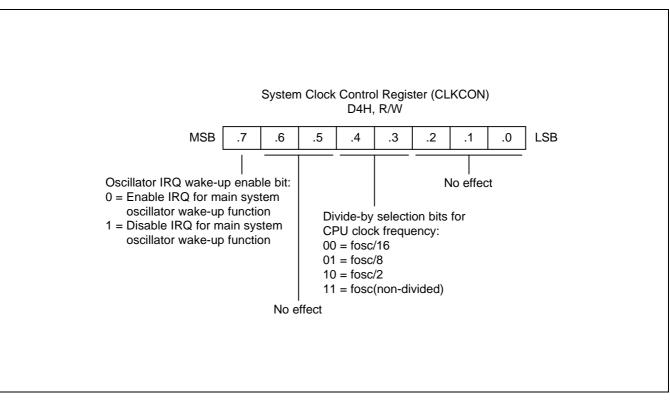

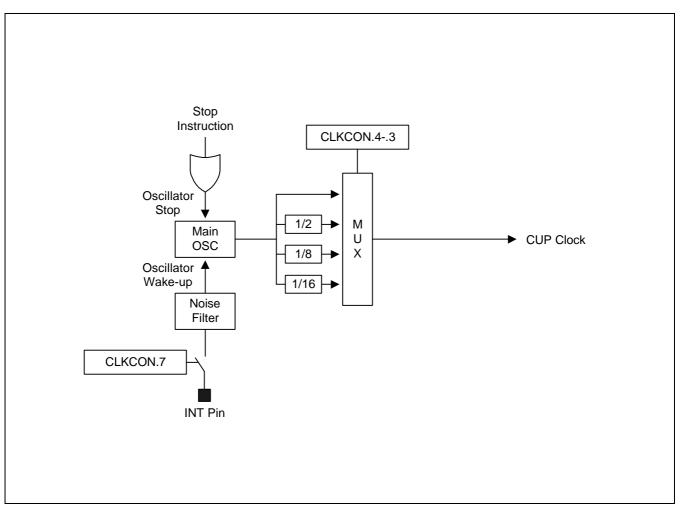

| CLKCON — System Clock Control Register |                                                                                                                          |   |                                       |    |     |     |    |    | D4H |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------|----|-----|-----|----|----|-----|--|--|

| Bit Identifier                         |                                                                                                                          | 7 | .6                                    | .5 | .4  | .3  | .2 | .1 | .0  |  |  |

| RESET Value                            | (                                                                                                                        | ) | -                                     | _  | 0   | 0   | _  | -  | -   |  |  |

| Read/Write                             | R/W                                                                                                                      |   | -                                     | _  | R/W | R/W | _  | -  | -   |  |  |

| .7                                     | Oscillator IRQ Wake-up Function Bit           0         Enable IRQ for main system oscillator wake-up in power down mode |   |                                       |    |     |     |    |    |     |  |  |

|                                        | 1 Disable IRQ for main system oscillator wake-up in power down mode                                                      |   |                                       |    |     |     |    |    |     |  |  |

|                                        |                                                                                                                          |   |                                       |    |     |     |    |    |     |  |  |

| .6 and .5                              | Not used for S3C9654/C9658/P9658                                                                                         |   |                                       |    |     |     |    |    |     |  |  |

| .4 and .3                              | CPU Clock (System Clock) Selection Bits                                                                                  |   |                                       |    |     |     |    |    |     |  |  |

|                                        | 0                                                                                                                        | 0 | 0 Divide by 16 (f <sub>OSC</sub> /16) |    |     |     |    |    |     |  |  |

|                                        | 0                                                                                                                        | 1 | 1 Divide by 8 (f <sub>OSC</sub> /8)   |    |     |     |    |    |     |  |  |

|                                        | 1                                                                                                                        | 0 | Divide by 2 (f <sub>OSC</sub> /2)     |    |     |     |    |    |     |  |  |

|                                        | 1                                                                                                                        | 1 | Non-divided clock (f <sub>OSC</sub> ) |    |     |     |    |    |     |  |  |

| .2 – .0                                | 2 – .0 Not used for S3C9654/C9658/P9658                                                                                  |   |                                       |    |     |     |    |    |     |  |  |

| Bit Identifier         .7         .6         .5         .4         .3         .2         .1         .0           RESET Value         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         <                                                                                                                                                                                                                      | EP0CSR — Control Endpoint Status Register F1H |                                                 |                                                                                 |              |             |               |            |          |     |     |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------|--------------|-------------|---------------|------------|----------|-----|-----|--|

| Read/Write       R/W                                                                                                                                                                                                                                    | Bit Identifier                                |                                                 | 7                                                                               | .6           | .5          | .4            | .3         | .2       | .1  | .0  |  |

| .7       SETUP_END Clear Bit         0       No effect (when write)         1       Clear SETUP_END (bit4) bit         .6       OUT_PKT_RDY Clear Bit         0       No effect (when write)         1       Clear OUT_PKT_RDY (bit0) bit         .5       STALL Signal Sending Bit         0       No effect (when write)         1       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .4       Setup Data End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO                                                     | RESET Value                                   | (                                               | )                                                                               | 0            | 0           | 0             | 0          | 0        | 0   | 0   |  |

| 0       No effect (when write)         1       Clear SETUP_END (bit4) bit         6       OUT_PKT_RDY Clear Bit         0       No effect (when write)         1       Clear OUT_PKT_RDY (bit0) bit         .5       STALL Signal Sending Bit         0       No effect (when write)         1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       SIE sets this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                          | Read/Write                                    | R/W                                             |                                                                                 | R/W          | R/W         | R/W           | R/W        | R/W      | R/W | R/W |  |

| 1       Clear SETUP_END (bit4) bit         .6       OUT_PKT_RDY Clear Bit         0       No effect (when write)         1       Clear OUT_PKT_RDY (bit0) bit         .5       STALL Signal Sending Bit         0       No effect (when write)         1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       SIE sets this bit after loading or unloading the last packet data into the FIFO         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Re                                                    | .7                                            | SETUP_END Clear Bit                             |                                                                                 |              |             |               |            |          |     |     |  |

| .6 OUT_PKT_RDY Clear Bit           0         No effect (when write)           1         Clear OUT_PKT_RDY (bit0) bit           .5         STALL Signal Sending Bit           0         No effect (when write)           1         Send STALL signal to host           .4         Setup Transfer End Bit           0         No effect (when write)           1         SIE sets this bit when a control transfer ends before DATA_END (bit3) is set           .3         Setup Data End Bit           0         No effect (when write)           1         SIE sets this bit when a control transfer ends before DATA_END (bit3) is set           .3         Setup Data End Bit           0         No effect (when write)           1         MCU set this bit after loading or unloading the last packet data into the FIFO           .2         STALL Signal Receive Bit           0         MCU clear this bit to end the STALL condition           1         SIE sets this bit if a control transaction is ended due to a protocol violation           .1         In Packet Ready Bit           0         SIE clear this bit once the packet has been successfully sent to the host           1         MCU sets this bit after writing a packet of data into Endpoint0 FIFO           .0         Out Packet Ready Bit           0 |                                               | 0                                               | No effect (when write)                                                          |              |             |               |            |          |     |     |  |

| 0       No effect (when write)         1       Clear OUT_PKT_RDY (bit0) bit         .5       STALL Signal Sending Bit         0       No effect (when write)         1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                     |                                               | 1                                               | 1 Clear SETUP_END (bit4) bit                                                    |              |             |               |            |          |     |     |  |

| 1       Clear OUT_PKT_RDY (bit0) bit         .5       STALL Signal Sending Bit         0       No effect (when write)         1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                        | .6                                            | OUT_PKT_RDY Clear Bit                           |                                                                                 |              |             |               |            |          |     |     |  |

| .5       STALL Signal Sending Bit         0       No effect (when write)         1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       SIE sets this bit after loading or unloading the last packet data into the FIFO         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                            |                                               | 0 No effect (when write)                        |                                                                                 |              |             |               |            |          |     |     |  |

| 0       No effect (when write)         1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                 |                                               | 1 Clear OUT_PKT_RDY (bit0) bit                  |                                                                                 |              |             |               |            |          |     |     |  |

| 1       Send STALL signal to host         .4       Setup Transfer End Bit         0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                        | .5                                            | STALL Signal Sending Bit                        |                                                                                 |              |             |               |            |          |     |     |  |

| .4 Setup Transfer End Bit           0         No effect (when write)           1         SIE sets this bit when a control transfer ends before DATA_END (bit3) is set           .3         Setup Data End Bit           0         No effect (when write)           1         MCU set this bit after loading or unloading the last packet data into the FIFO           .2         STALL Signal Receive Bit           0         MCU clear this bit to end the STALL condition           1         SIE sets this bit if a control transaction is ended due to a protocol violation           .1         In Packet Ready Bit           0         SIE clear this bit once the packet has been successfully sent to the host           1         MCU sets this bit after writing a packet of data into Endpoint0 FIFO           .0         Out Packet Ready Bit           0         No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               | 0 No effect (when write)                        |                                                                                 |              |             |               |            |          |     |     |  |

| 0       No effect (when write)         1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               | 1 Send STALL signal to host                     |                                                                                 |              |             |               |            |          |     |     |  |

| 1       SIE sets this bit when a control transfer ends before DATA_END (bit3) is set         .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .4                                            | Setup Transfer End Bit                          |                                                                                 |              |             |               |            |          |     |     |  |

| .3       Setup Data End Bit         0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               | 0 No effect (when write)                        |                                                                                 |              |             |               |            |          |     |     |  |

| 0       No effect (when write)         1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               | 1                                               | 1 SIE sets this bit when a control transfer ends before DATA_END (bit3) is set  |              |             |               |            |          |     |     |  |

| 1       MCU set this bit after loading or unloading the last packet data into the FIFO         .2       STALL Signal Receive Bit         0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .3                                            |                                                 |                                                                                 |              |             |               |            |          |     |     |  |

| STALL Signal Receive Bit     O MCU clear this bit to end the STALL condition     SIE sets this bit if a control transaction is ended due to a protocol violation     In Packet Ready Bit     O SIE clear this bit once the packet has been successfully sent to the host     I MCU sets this bit after writing a packet of data into Endpoint0 FIFO     Out Packet Ready Bit     O No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               | 0                                               | No effect (when write)                                                          |              |             |               |            |          |     |     |  |

| 0       MCU clear this bit to end the STALL condition         1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               | 1                                               | MCU set this bit after loading or unloading the last packet data into the FIFO  |              |             |               |            |          |     |     |  |

| 1       SIE sets this bit if a control transaction is ended due to a protocol violation         .1       In Packet Ready Bit         0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .2                                            | STALL Signal Receive Bit                        |                                                                                 |              |             |               |            |          |     |     |  |

| .1 In Packet Ready Bit          0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               | 0 MCU clear this bit to end the STALL condition |                                                                                 |              |             |               |            |          |     |     |  |

| 0       SIE clear this bit once the packet has been successfully sent to the host         1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               | 1                                               | SIE sets this bit if a control transaction is ended due to a protocol violation |              |             |               |            |          |     |     |  |

| 1       MCU sets this bit after writing a packet of data into Endpoint0 FIFO         .0       Out Packet Ready Bit         0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .1                                            | In Packet Ready Bit                             |                                                                                 |              |             |               |            |          |     |     |  |

| .0 Out Packet Ready Bit          0       No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               | 0                                               | 0 SIE clear this bit once the packet has been successfully sent to the host     |              |             |               |            |          |     |     |  |

| 0 No effect (when write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               | 1                                               | MCU sets this bit after writing a packet of data into Endpoint0 FIFO            |              |             |               |            |          |     |     |  |

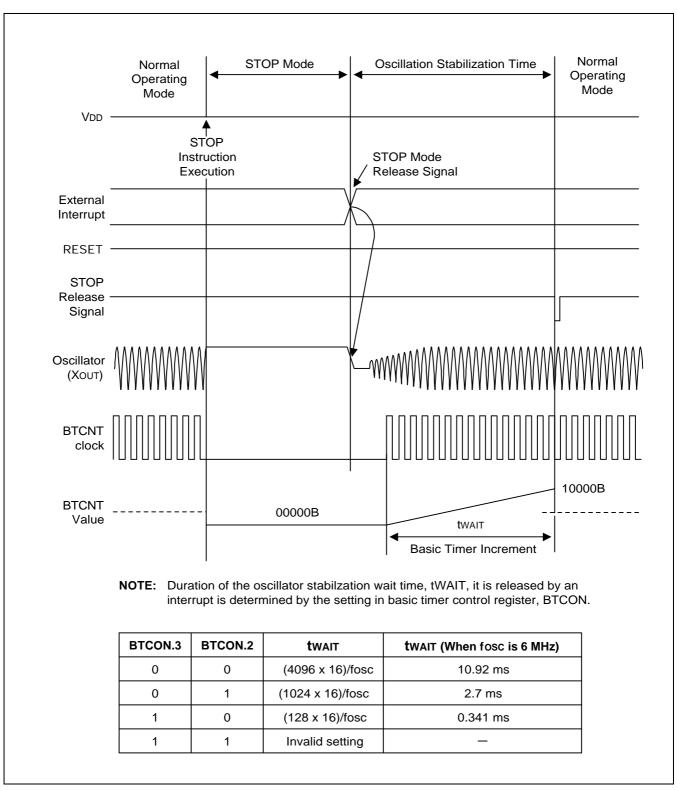

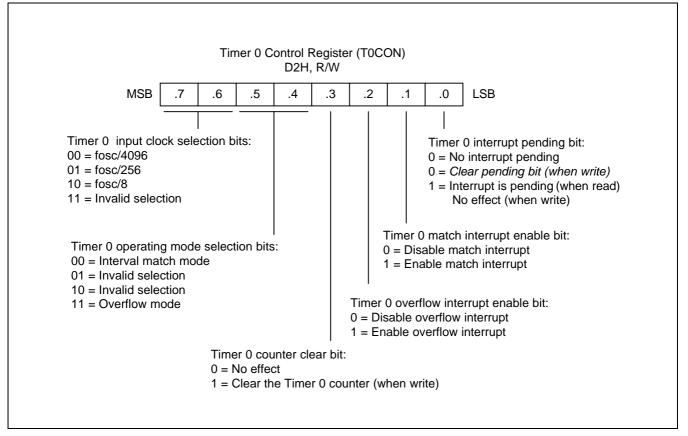

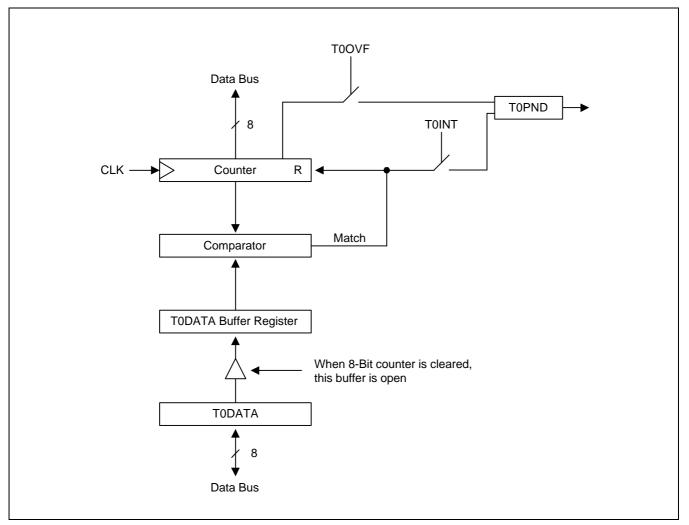

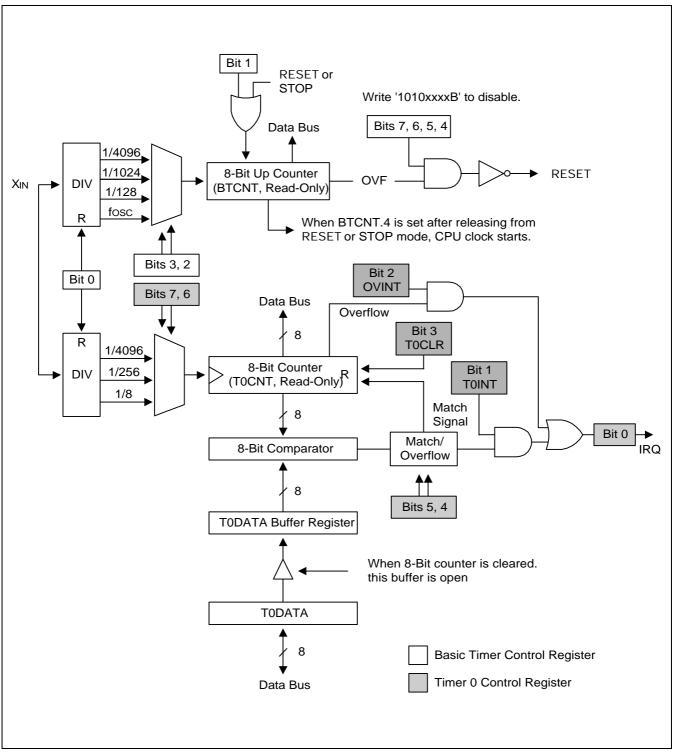

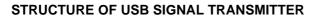

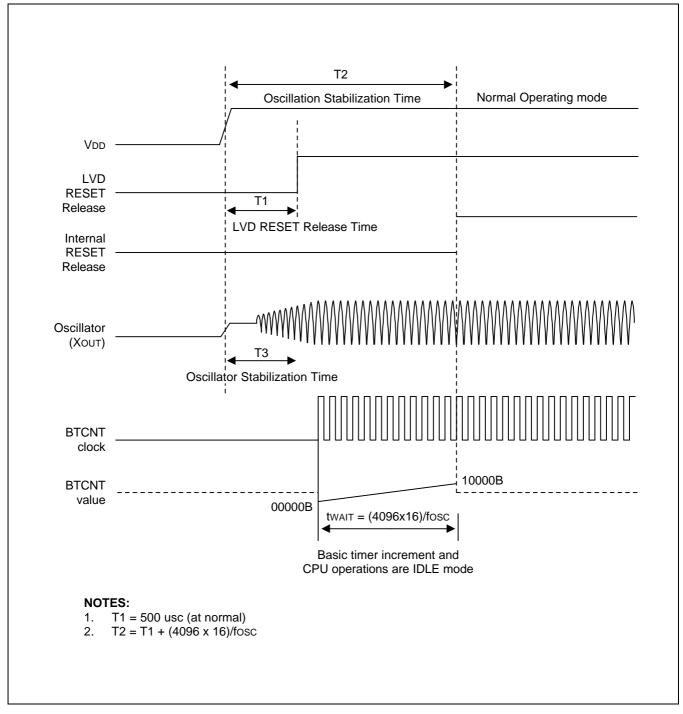

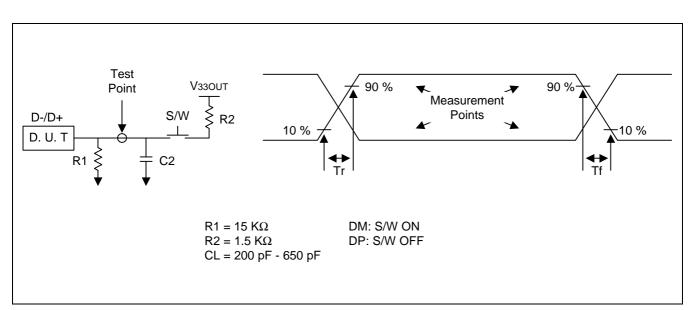

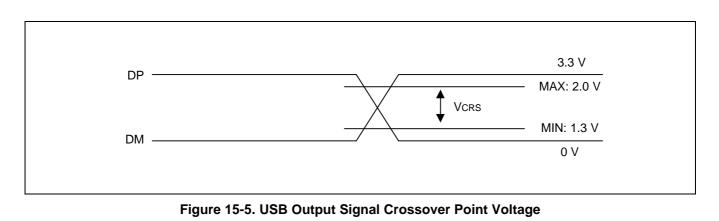

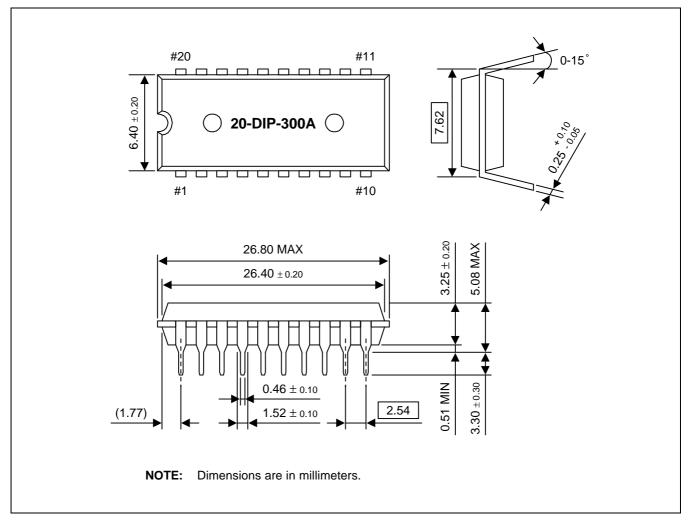

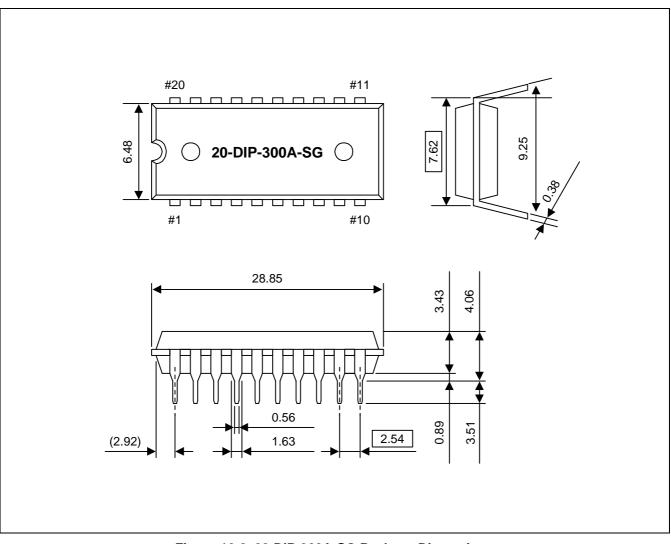

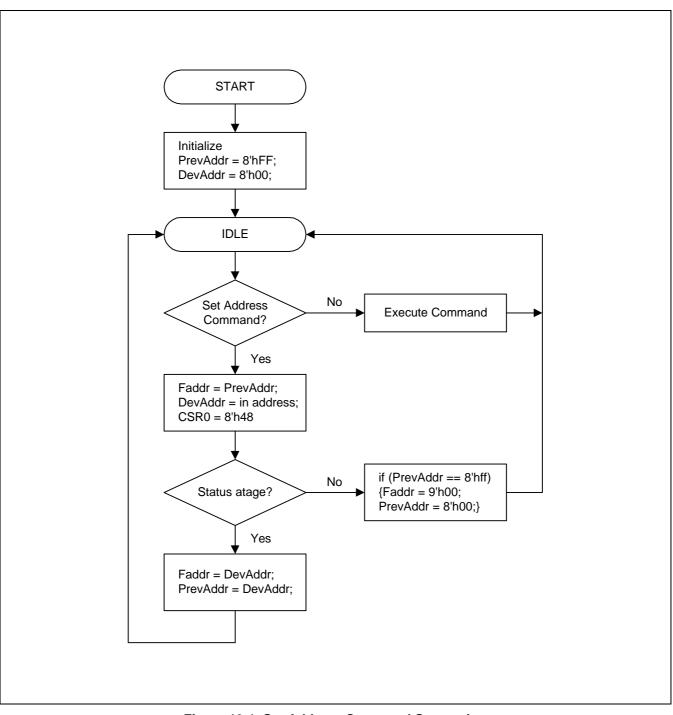

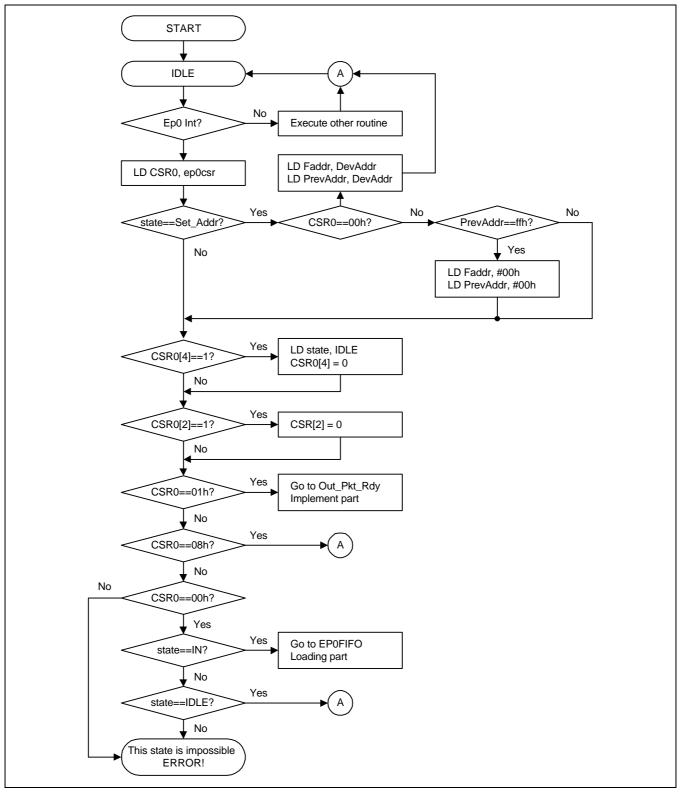

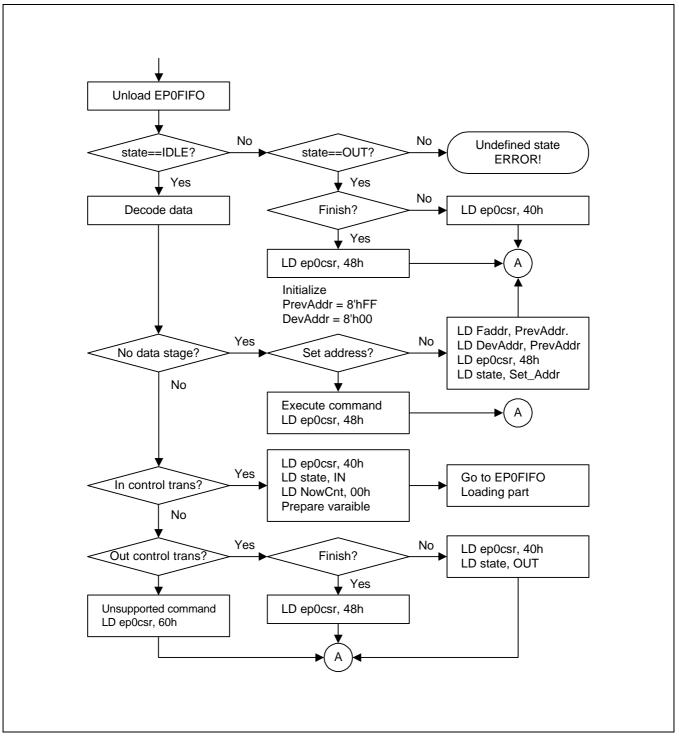

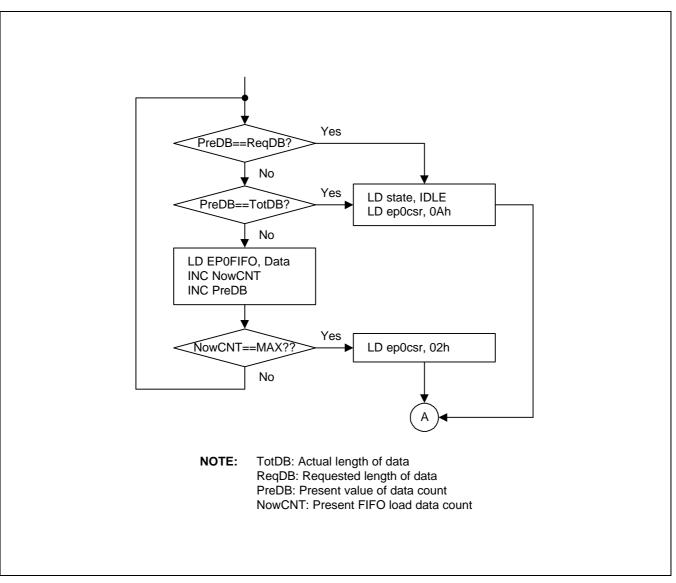

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .0                                            | Out Packet Ready Bit                            |                                                                                 |              |             |               |            |          |     |     |  |