# Z80 Family

# **CPU Peripherals**

**User Manual**

UM008101-0601

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

910 E. Hamilton Avenue

Campbell, CA 95008

Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

©2001 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

UM008101-0601

Disclaimer

iii

# Table of Contents

| Counter/Timer Channels                |    |

|---------------------------------------|----|

| CTC Features                          | 1  |

| CTC General Description               | 1  |

| CTC Architecture                      | 2  |

| Overview                              |    |

| Structure of Channel Logic            |    |

| Interrupt Control Logic               | 7  |

| CTC Pin Description                   | 9  |

| Pin Functions                         | 9  |

| CTC Operating Modes                   | 16 |

| Overview                              |    |

| CTC Counter Mode                      | 16 |

| CTC Timer Mode                        | 17 |

| CTC Programming                       | 18 |

| Overview                              |    |

| Loading The Channel Control Register  |    |

| Loading The Time Constant Register    |    |

| Loading The Interrupt Vector Register |    |

| CTC Timing                            | 24 |

| Overview                              | 24 |

| CTC Write Cycle                       | 24 |

| CTC Read Cycle                        | 25 |

| CTC Counting and Timing               |    |

| CTC Interrupt Servicing               |    |

| Overview                              | 27 |

| Interrupt Acknowledge Cycle           |    |

| Return from Interrupt Cycle           |    |

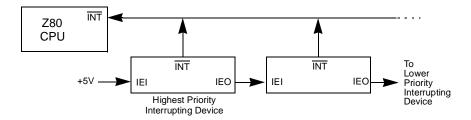

| Daisy-Chain Interrupt Servicing       | 30 |

|                                       |    |

UM008101-0601 Table of Contents

**Direct Memory Access**

i۷

| DMA Overview                 |    |

|------------------------------|----|

| CPU Data Transfers           |    |

| DMA Data Transfers           |    |

| DMA Characteristics          |    |

| DMA Functional Description   | 43 |

| Features                     |    |

| Overview                     |    |

| Programming                  | 45 |

| Classes of Operation         | 46 |

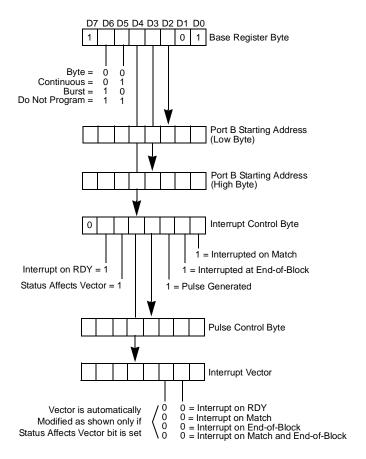

| Modes of Operation           | 49 |

| Transfer Speed               | 56 |

| Address Generation           | 57 |

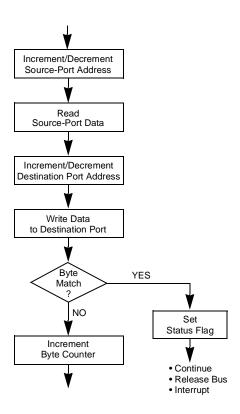

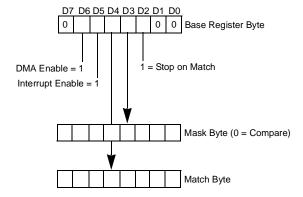

| Byte Matching (Searching)    | 58 |

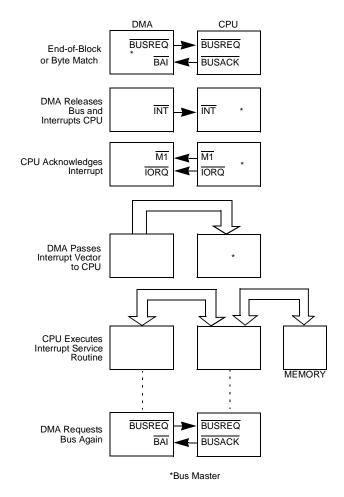

| Interrupts                   |    |

| Auto Restart                 | 60 |

| Pulse Generation             | 60 |

| Variable Cycle               | 60 |

| Events and Actions           | 61 |

| Pin Description              | 62 |

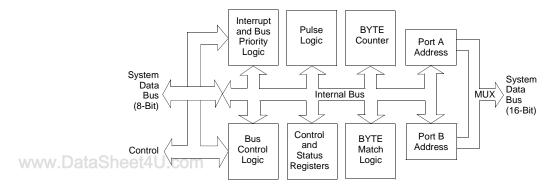

| Internal Structure           | 71 |

| General Organization         | 71 |

| Control And Status Registers |    |

| Address and Byte Counting    |    |

| Bus Control                  |    |

| Interrupts                   |    |

| Programming                  |    |

| Overview                     |    |

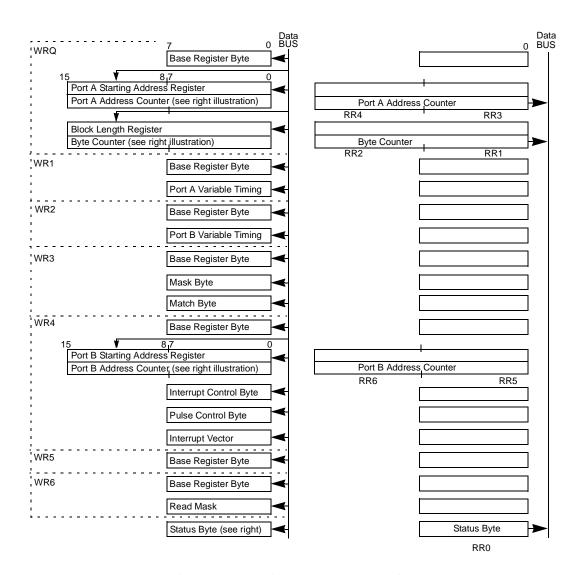

| Write Registers              |    |

| Write Register 0 Group       |    |

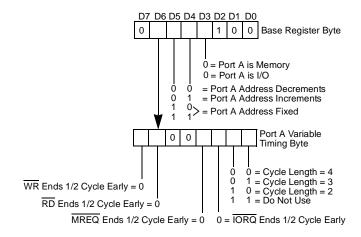

| Write Register 1 Group       |    |

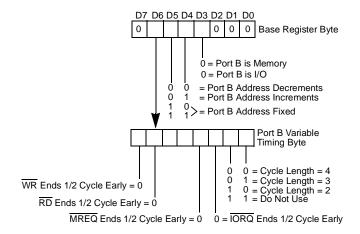

| Write Register 2 Group       |    |

| -                            |    |

UM008101-0601

v

|              | <b>Direct Memory Access (continued)</b> |      |

|--------------|-----------------------------------------|------|

|              | Write Register 3 Group                  | 97   |

|              | Write Register 4 Group                  | 99   |

|              | Write Register 5 Group                  | .102 |

|              | Write Register 6 Group                  | .104 |

|              | Read Registers                          | .113 |

|              | Review of Programming Sequences         | .117 |

|              | Applications                            |      |

|              | Z80 DMA and CPU                         | .128 |

|              | Z80 DMA and Z80 SIO Example             | .138 |

|              | Using The Z80 DMA With Other Processors | .142 |

|              | Performance Limitations                 | .148 |

|              | Bus Contention                          | .148 |

|              | Control Overhead                        | .149 |

|              | Timing                                  |      |

|              | The CPU As Bus Master                   | .150 |

|              | The DMA As Bus Master                   |      |

|              | Register Bit Functions                  |      |

|              | Write Register Bit Functions            |      |

|              | Read Register Bit Functions             | .174 |

|              | Parallel Input/Output                   |      |

|              | Overview                                | .175 |

|              | Features                                | .175 |

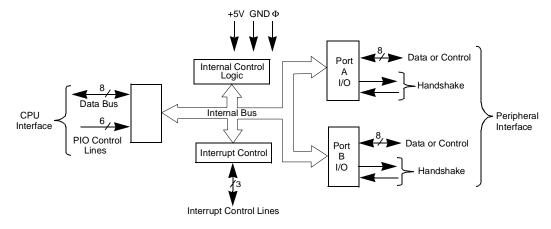

|              | PIO Architecture                        | .176 |

|              | Overview                                |      |

|              | Pin Description                         | .180 |

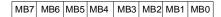

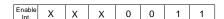

|              | Programming the PIO                     |      |

|              | Reset                                   |      |

| www.Data     | Loading The Interrupt Vector            |      |

| v vv vv.Dalc | Selecting An Operating Mode             |      |

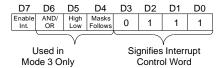

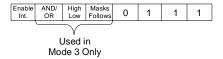

|              | Setting The Interrupt Control Word      | .191 |

|              |                                         |      |

Table of Contents UM008101-0601

νi

UM008101-0601 Table of Contents

vii

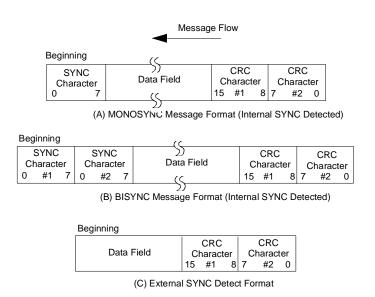

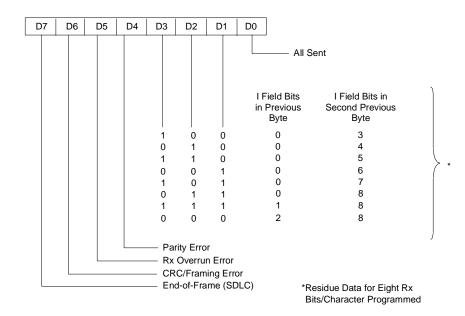

| Synchronous Modes Of Operation240 |

|-----------------------------------|

| Serial Input/Output (continued)   |

| Synchronous Transmit244           |

| Synchronous Receive               |

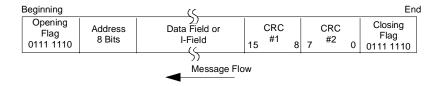

| SDLC (HDLC) Operation             |

| Overview                          |

| SDLC Transmit                     |

| SDLC Receive                      |

| Programming                       |

| Overview                          |

| Write Registers                   |

| Read Registers                    |

| Applications                      |

| Overview                          |

| Timing                            |

| Read Cycle                        |

| Write Cycle                       |

| Interrupt Acknowledge Cycle       |

| Return From Interrupt Cycle       |

| Daisy Chain Interrupt Nesting 308 |

www DataSheet4U com

Table of Contents UM008101-0601

www.DataSheet4U.com

UM008101-0601 Table of Contents

iv

# List of Figures

| Co        | ounter/Tim | er Channels                                              |

|-----------|------------|----------------------------------------------------------|

|           | Figure 1.  | CTC Block Diagram                                        |

|           | Figure 2.  | Channel Block Diagram                                    |

|           | Figure 3.  | Z80 16-Bit Pointer (Interrupt Starting Address)          |

|           | Figure 4.  | CTC Pin Configuration                                    |

|           | Figure 5.  | Package Configuration                                    |

|           | Figure 6.  | 44-Pin Chip Carrier Pin Assignments                      |

|           | Figure 7.  | 44-Pin Quad Flat Pack Pin Assignments                    |

|           | Figure 8.  | Mode 2 Interrupt Operation                               |

|           | Figure 9.  | CTC Write Cycle                                          |

|           | Figure 10. | CTC Read Cycle                                           |

|           | Figure 11. | CTC Counting and Timing                                  |

|           | Figure 12. | Interrupt Acknowledge Cycle                              |

|           | Figure 13. | Return from Interrupt Cycle                              |

|           | Figure 14. | Daisy-Chain Interrupt Servicing                          |

| Di        | rect Memo  | ry Access                                                |

|           | Figure 15. | Typical CPU I/O Sequence                                 |

|           | Figure 16. | Conceptual Comparison of Various I/O Transfer Methods 39 |

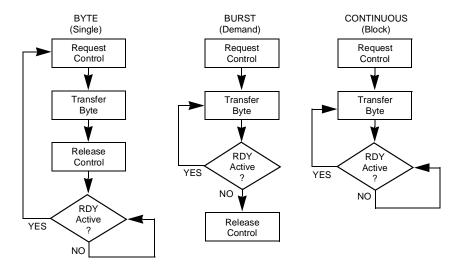

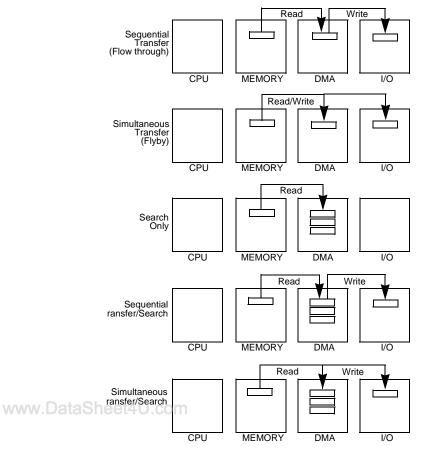

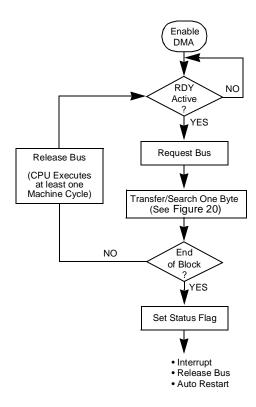

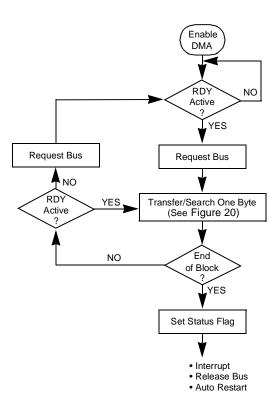

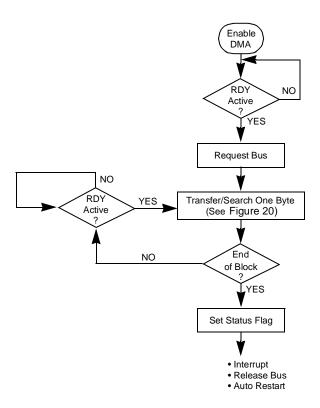

|           | Figure 17. | Modes of Operation                                       |

|           | Figure 18. | Class of Operation                                       |

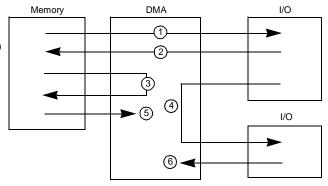

|           | Figure 19. | Basic Functions of the Z80 DMA                           |

|           | Figure 20. | Transfer/Search One Byte                                 |

|           | Figure 21. | Byte Mode                                                |

| ww.DataSh | Figure 22. | Burst Mode                                               |

|           |            | Continuous Mode55                                        |

|           |            |                                                          |

List of Figures UM008101-0601

X

| <b>Direct Memory Access (c</b> | ontinued) |

|--------------------------------|-----------|

|--------------------------------|-----------|

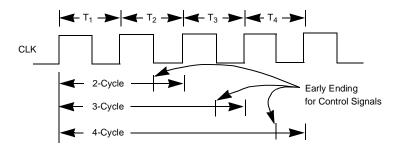

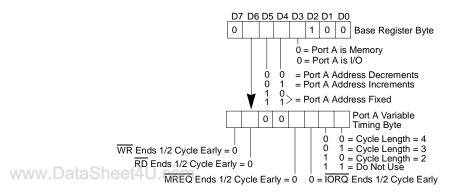

|          | Figure 24.            | variable Cycle Length 61                                                    |

|----------|-----------------------|-----------------------------------------------------------------------------|

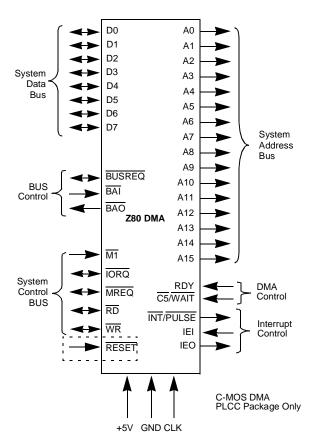

|          | Figure 25.            | Pin Functions (CMOS PLCC Package Only) 67                                   |

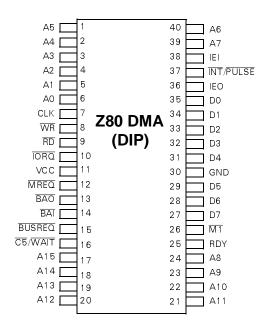

|          | Figure 26.            | 40-Pin DIP Pin Assignments                                                  |

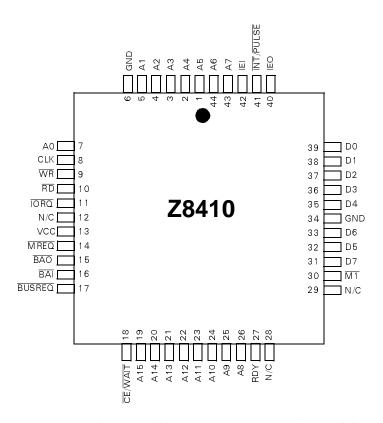

|          | Figure 27.            | 44-Pin PLCC Pin Assignments (Z8410 NMOS) 69                                 |

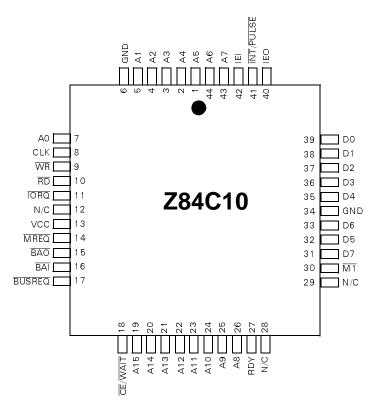

|          | Figure 28.            | 44-Pin PLCC Pin Assignments (Z84C10 NMOS) 70                                |

|          | Figure 29.            | Z80 DMA Block Diagram                                                       |

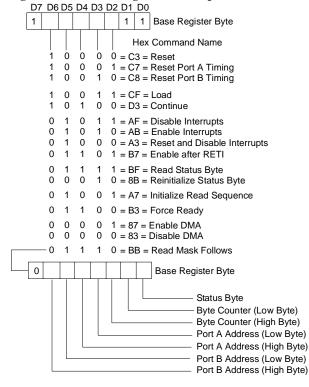

|          | Figure 30.            | Write Register Organization (left) and Read Register Organization (right)74 |

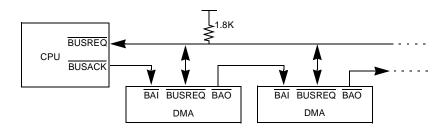

|          | Figure 31.            | Bus-Requesting Daisy-Chain                                                  |

|          | Figure 32.            | Z80 Interrupt Sequence                                                      |

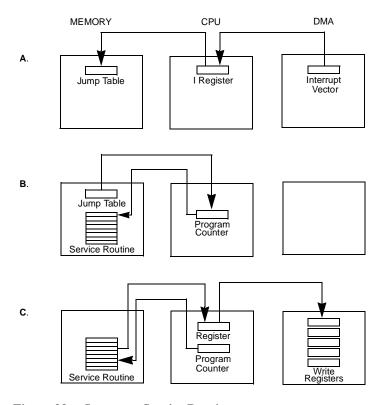

|          | Figure 33.            | Interrupt Service Routine                                                   |

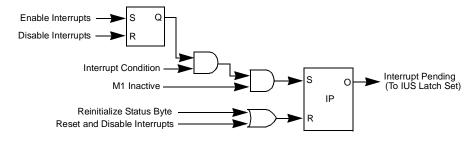

|          | Figure 34.            | Interrupt Pending (IP) Latch 84                                             |

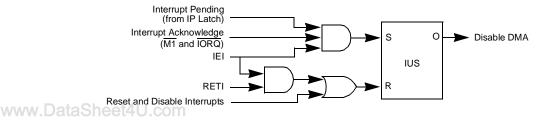

|          | Figure 35.            | Interrupt Under Service (IUS) Latch 84                                      |

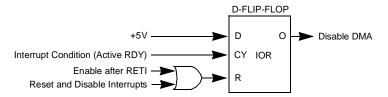

|          | Figure 36.            | Interrupt On Ready (IOR) Latch                                              |

|          | Figure 37.            | Interrupt Daisy-Chain                                                       |

|          | Figure 38.            | Polling for a Service Request Bit                                           |

|          | Figure 39.            | Write-Register Pointing Methods 92                                          |

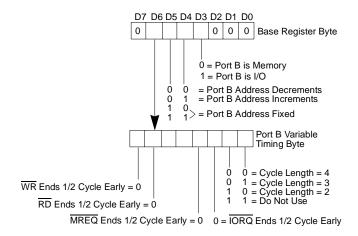

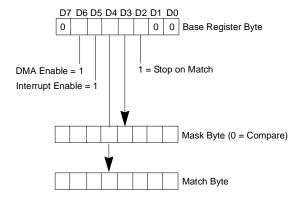

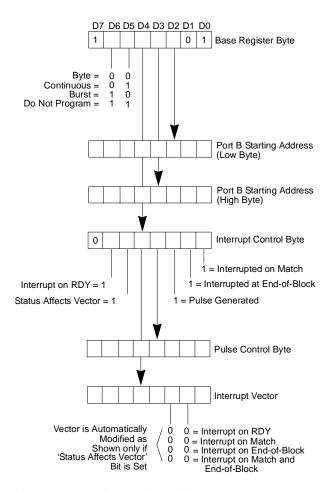

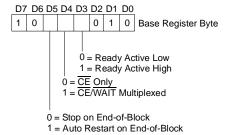

|          | Figure 40.            | Write Register 0 Group                                                      |

|          | Figure 41.            | Write Register 1 Group                                                      |

|          | Figure 42.            | Write Register 2 Group                                                      |

|          | Figure 43.            | Write Register 3 Group                                                      |

|          | Figure 44.            | Write Register 4 Group                                                      |

|          | Figure 45.            | Write Register 5 Group                                                      |

|          | Figure 46.            | Write Register 6 Group                                                      |

| www.Data | Figure 47. Figure 48. | Read Register 0 through Read Register 6                                     |

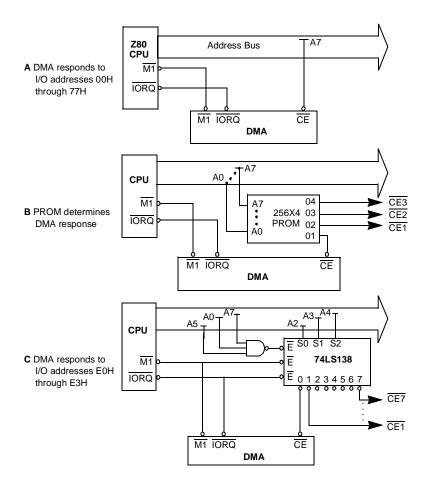

|          | Figure 49.            | Chip Enable Decoding with Z80 CPU                                           |

|          |                       |                                                                             |

UM008101-0601 List of Figures

χi

| Dir       | rect Memory | y Access (continued)                                                       |

|-----------|-------------|----------------------------------------------------------------------------|

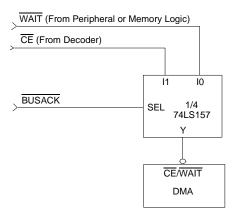

|           | Figure 50.  | CE/WAIT Multiplexer                                                        |

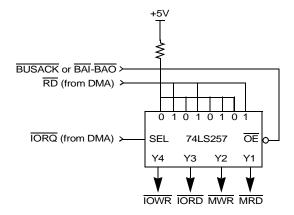

|           | Figure 51.  | Simultaneous Transfer Multiplexer                                          |

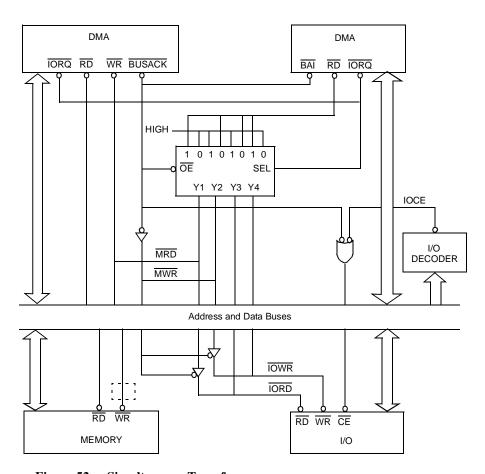

|           | Figure 52.  | Simultaneous Transfer                                                      |

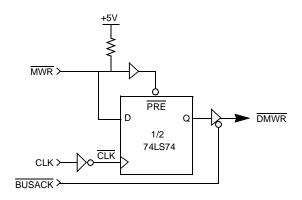

|           | Figure 53.  | Delaying the Leading Edge of MWR                                           |

|           | Figure 54.  | Data Bus Buffer Control Example                                            |

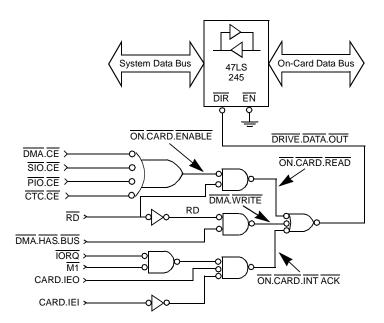

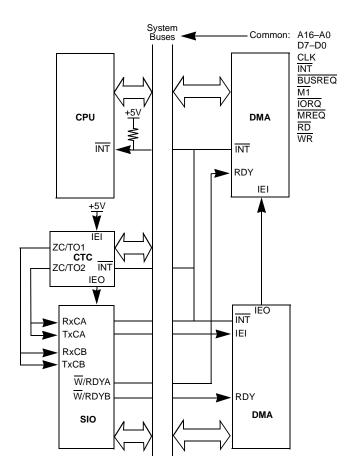

|           | Figure 55.  | DMA-SIO Environment                                                        |

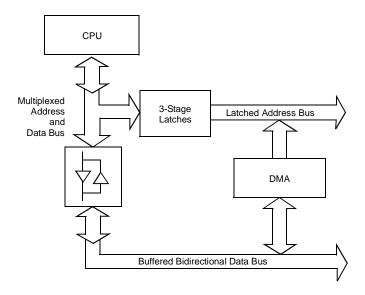

|           | Figure 56.  | Connecting DMA to Demultiplexed Address/Data Buses 145                     |

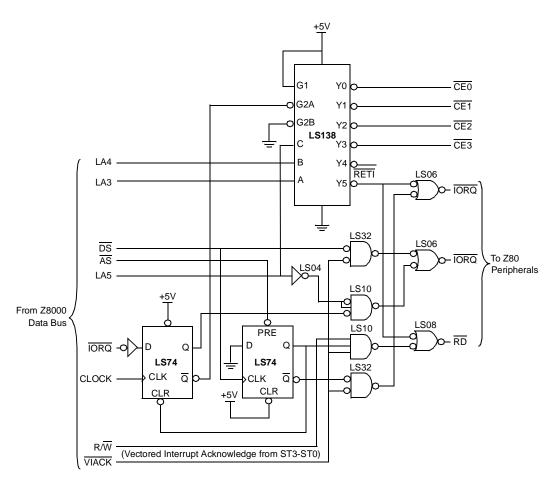

|           | Figure 57.  | Z8000/Z80 Peripheral Interface                                             |

|           | Figure 58.  | DMA Bus-Master Gate (Byte or Burst Modes Only) 149                         |

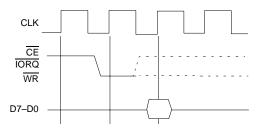

|           | Figure 59.  | CPU-to-DMA Write Cycle Requirements                                        |

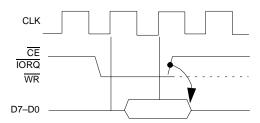

|           | Figure 60.  | CPU-to-DMA Read Cycle Requirements                                         |

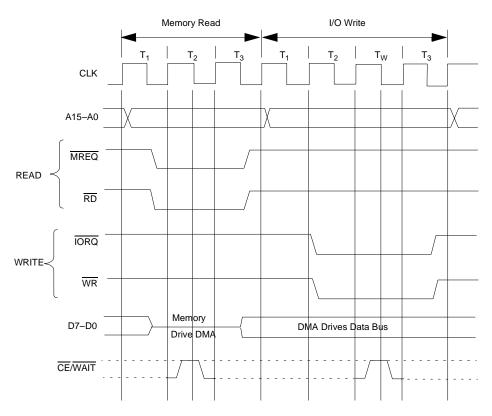

|           | Figure 61.  | Sequential Memory-to-I/O Transfer, Standard Timing (Searching is Optional) |

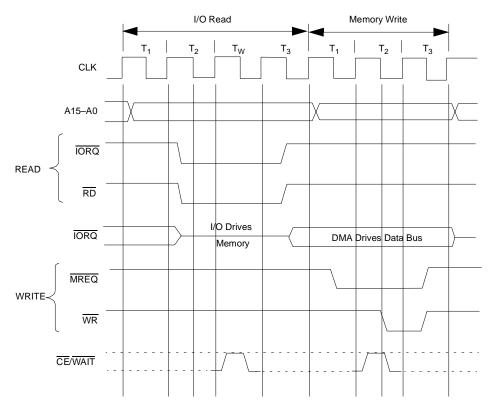

|           | Figure 62.  | Sequential I/O-to-Memory Transfer, Standard Timing (Searching is Optional) |

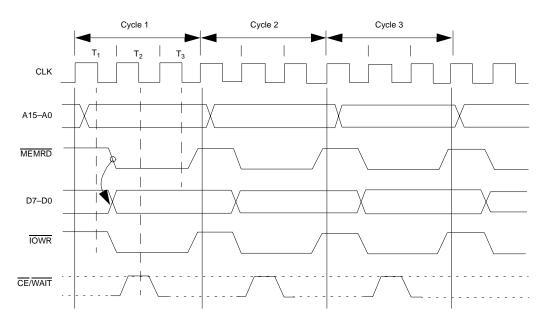

|           | Figure 63.  | Simultaneous Memory-to-I/O Transfer (Burst and Continuous Mode)            |

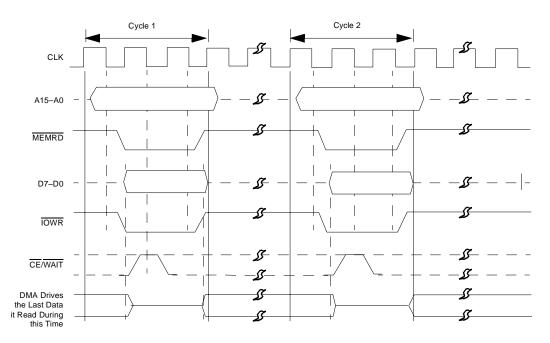

|           | Figure 64.  | Simultaneous Memory-to-I/O Transfer (Byte Mode) 157                        |

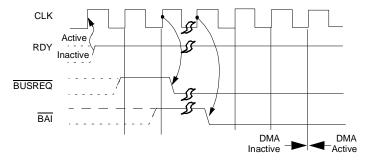

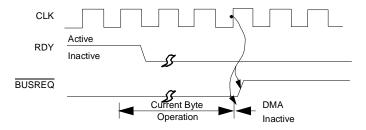

|           | Figure 65.  | Bus Request and Acceptance Timing                                          |

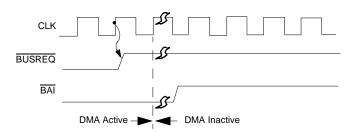

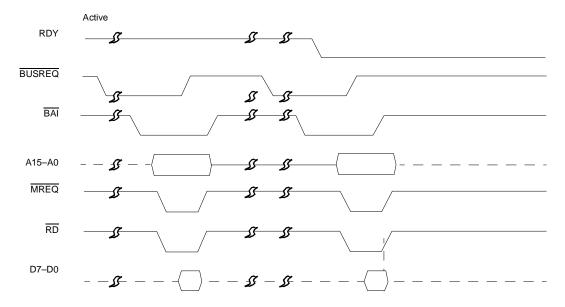

|           | Figure 66.  | Bus Release in Byte Mode                                                   |

|           | Figure 67.  | Bus Release on End-of-Block (Burst and Continuous Modes)                   |

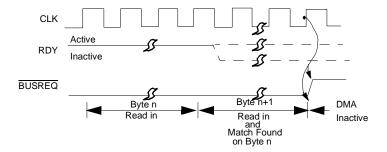

|           | Figure 68.  | Bus Release on Match (Burst and Continuous Modes)161                       |

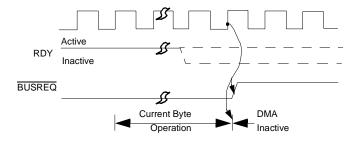

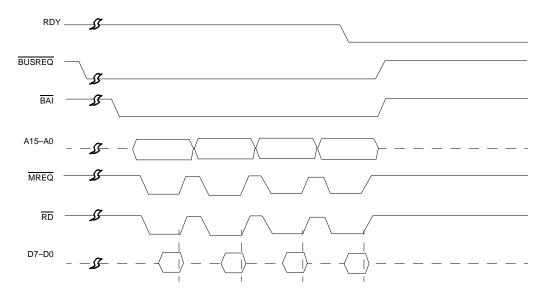

|           | Figure 69.  | Bus Release on Not Ready (Burst Mode)                                      |

|           | Figure 70.  | RDY Line in Byte Mode                                                      |

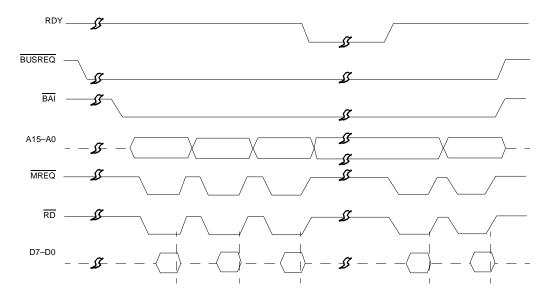

|           | Figure 71.  | RDY Line in Burst Mode164                                                  |

| ww.DataSh | Figure 72.  | RDY Line in Continuous Mode                                                |

|           | Figure 73.  | Variable-Cycle and Edge Timing                                             |

|           |             |                                                                            |

List of Figures UM008101-0601

xii

| Direct Memor  | y Access (continued)                                     |

|---------------|----------------------------------------------------------|

| Figure 74.    | WAIT Line Sampling in Variable-Cycle Timing 167          |

| Figure 75.    | Interrupt Acknowledge                                    |

| Figure 76.    | Write Register 0 Group                                   |

| Figure 77.    | Write Register 1 Group                                   |

| Figure 78.    | Write Register 2 Group                                   |

| Figure 79.    | Write Register 3 Group                                   |

| Figure 80.    | Write Register 4 Group                                   |

| Figure 81.    | Write Register 5 Group                                   |

| Figure 82.    | Write Register 6 Group                                   |

| Figure 83.    | Read Register 0 through 6 Bit Functions                  |

| Parallel Inpu | t/Output                                                 |

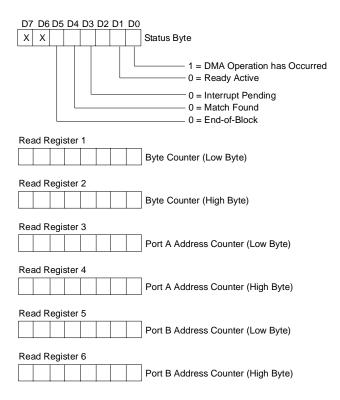

| Figure 84.    | PIO Block Diagram                                        |

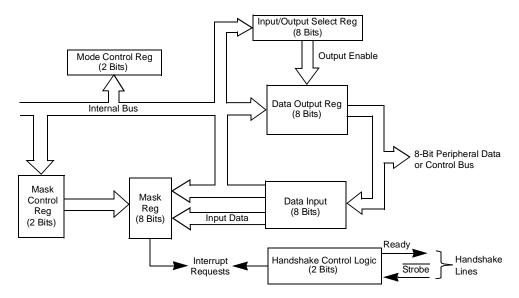

| Figure 85.    | Port I/O Block Diagram                                   |

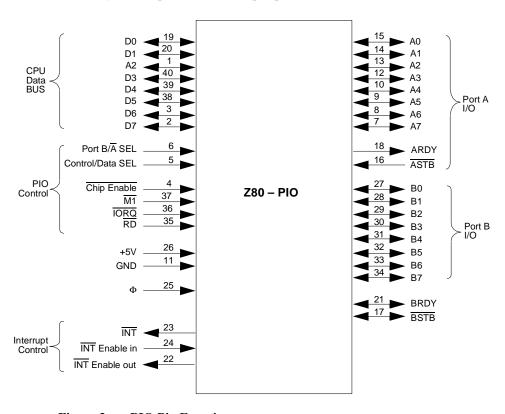

| Figure 86.    | PIO Pin Functions                                        |

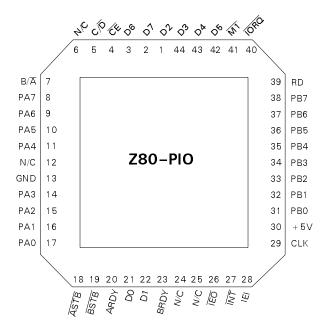

| Figure 87.    | 44-Pin PLCC Pin Assignments                              |

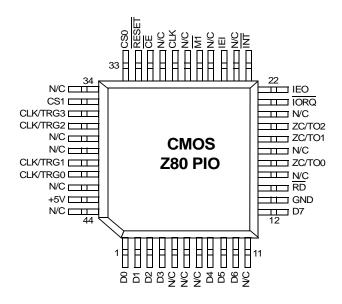

| Figure 88.    | 44-Pin QFP Pin Assignments                               |

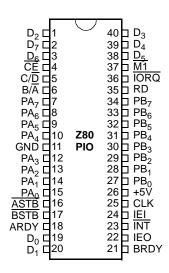

| Figure 89.    | 40-Pin DIP Pin Assignments                               |

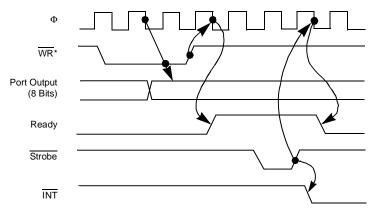

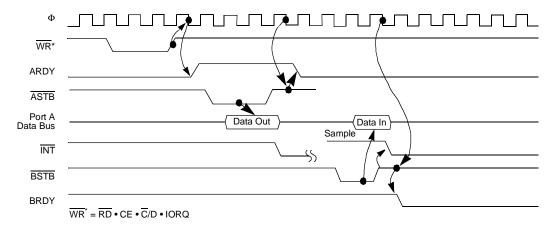

| Figure 90.    | Mode 0 (Output) Timing                                   |

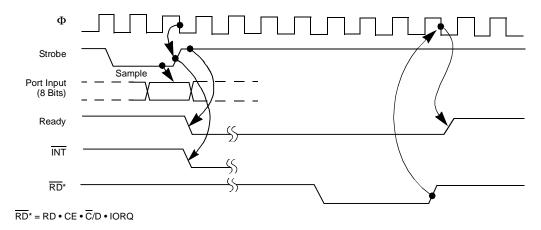

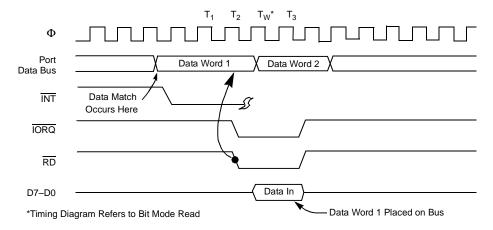

| Figure 91.    | Mode 1 (Input) Timing                                    |

| Figure 92.    | Port A, Mode 2 (Bidirectional) Timing 195                |

| Figure 93.    | Control Mode (Mode 3) Timing                             |

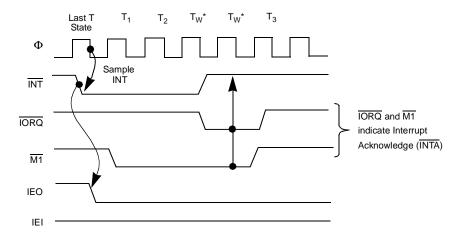

| Figure 94.    | Interrupt Acknowledge Timing                             |

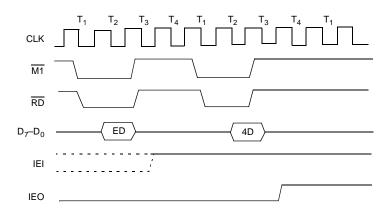

| Figure 95.    | Return from Interrupt Cycle                              |

| Figure 96.    | Daisy-Chain Interrupt Servicing                          |

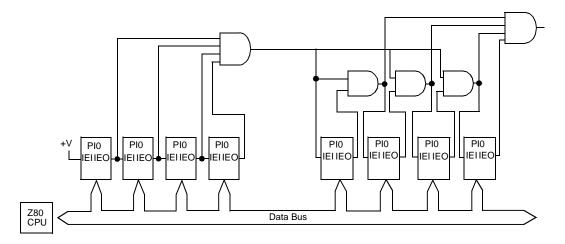

| Figure 97.    | A Method of Extending the Interrupt Priority Daisy-Chain |

UM008101-0601 List of Figures

xiii

| Par     | allel Input/ | Output (continued)                        |      |

|---------|--------------|-------------------------------------------|------|

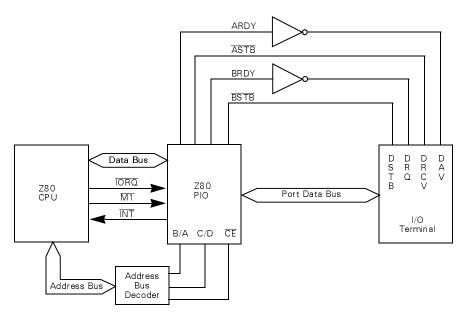

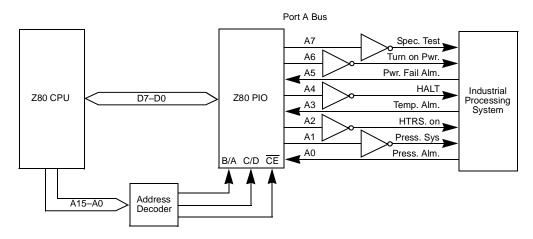

|         | Figure 98.   | Example of I/O Interface                  | .201 |

|         | Figure 99.   | Control Mode Application                  | .204 |

| Se      | rial Input/  | Output                                    |      |

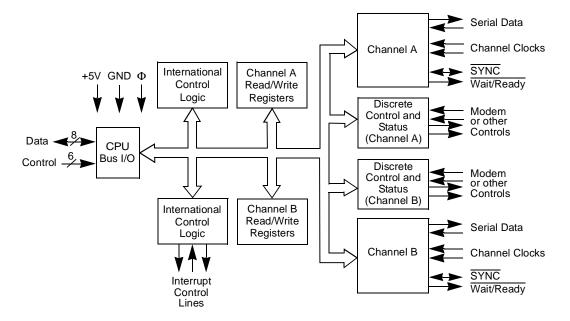

|         | Figure 100.  | Z80 SIO Block Diagram                     | .209 |

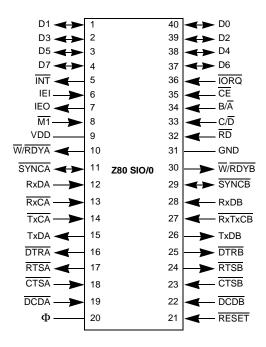

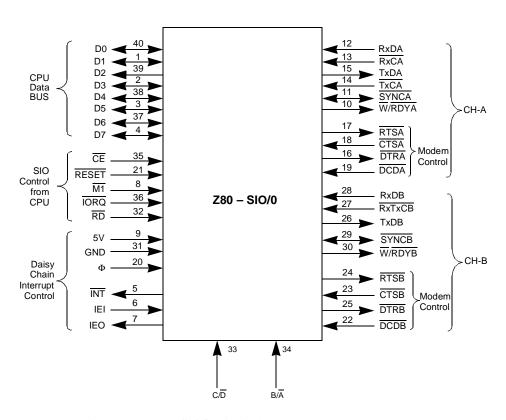

|         | Figure 101.  | Z80 SIO/0 Functions                       | .214 |

|         | Figure 102.  | Z80 ZIO/0 Pin Assignments                 | .215 |

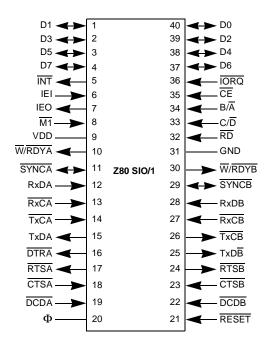

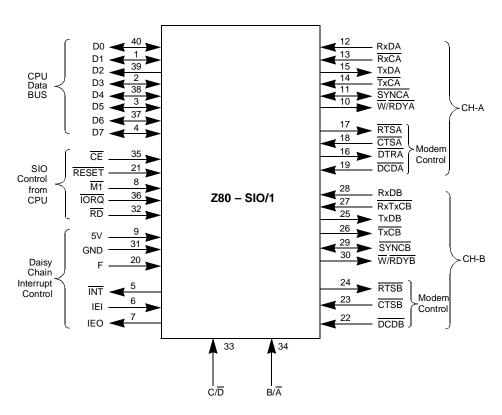

|         | Figure 103.  | Z80 SIO/1 Pin Functions                   | .216 |

|         | Figure 104.  | Z80 ZIO/1 Pin Assignments                 | .217 |

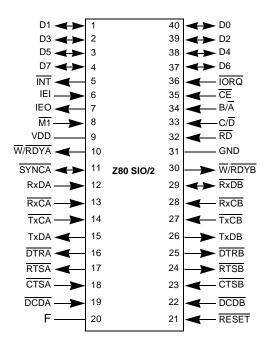

|         | Figure 105.  | Z80 SIO/2 Pin Functions                   | .218 |

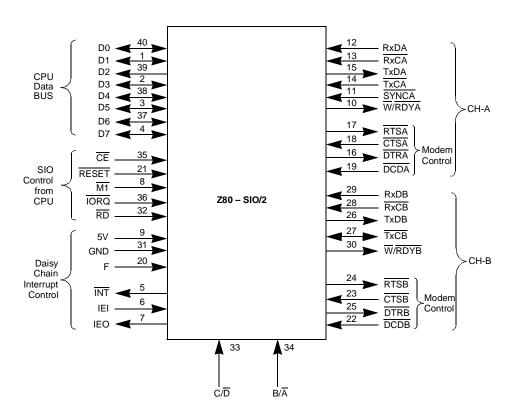

|         | Figure 106.  | Z80 ZIO/2 Pin Assignments                 | .219 |

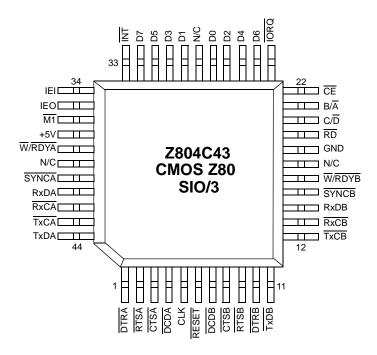

|         | Figure 107.  | Z80 SIO/3 Pin Assignments                 | .220 |

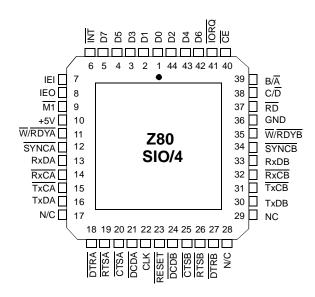

|         | Figure 108.  | Z80 SIO/4 Pin Assignments                 | .221 |

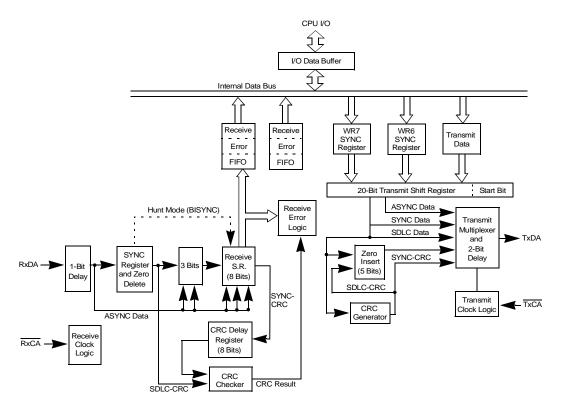

|         | Figure 109.  | Transmit and Receive Data Path            | .226 |

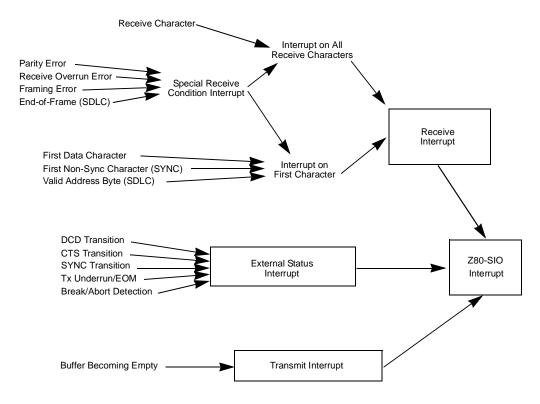

|         | Figure 110.  | Interrupt Structure                       | .230 |

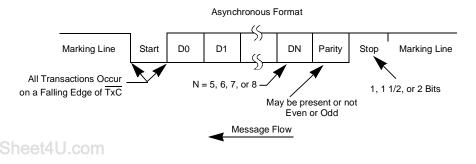

|         | Figure 111.  | Asynchronous Message Format               | .231 |

|         | Figure 112.  | Synchronous Formats                       | .239 |

|         | Figure 113.  | Transmit/Receive SDLC/HDLC Message Format | .256 |

|         | Figure 114.  | Write Register 0                          | .274 |

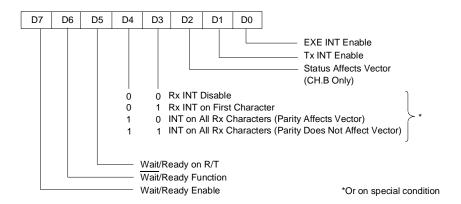

|         | Figure 115.  | Write Register 1                          | .279 |

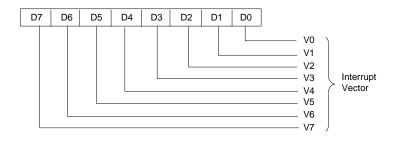

|         | Figure 116.  | Write Register 2                          | .282 |

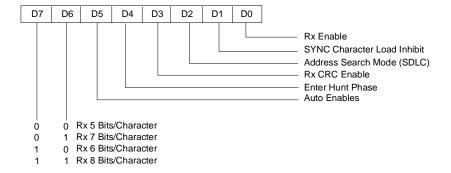

|         | Figure 117.  | Write Register 3                          | .284 |

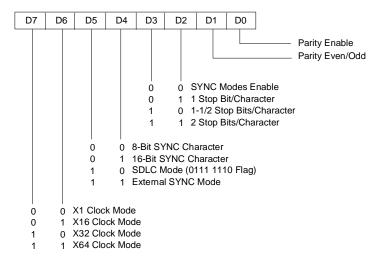

|         | Figure 118.  | Write Register 4                          | .286 |

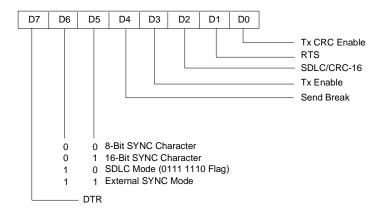

|         | Figure 119.  | Write Register 5                          | .289 |

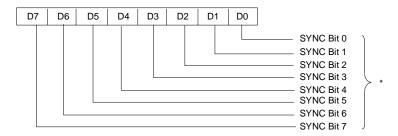

|         | Figure 120.  | Write Register 6                          | .290 |

| D-4-0h  | Figure 121.  | Write Register 7                          | .291 |

| .บataSn | Figure 122.  | Read Register 0                           | .294 |

|         |              | Read Register 1                           |      |

|         |              |                                           |      |

List of Figures UM008101-0601

| Serial Input/ | Output (continued)                                                                                 |

|---------------|----------------------------------------------------------------------------------------------------|

| Figure 12     | 4. Read Register 2 (Channel B Only)                                                                |

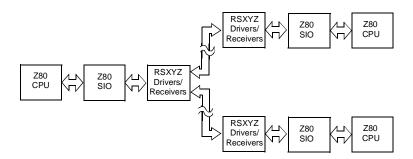

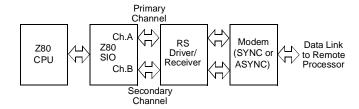

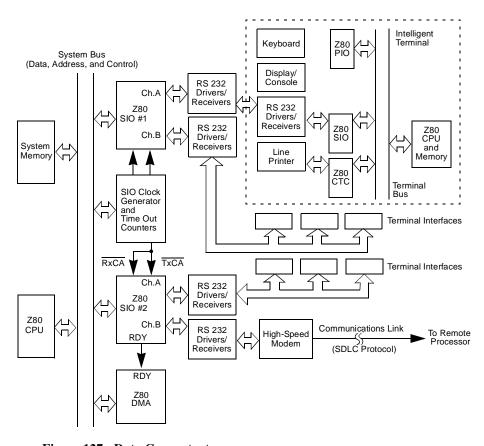

| Figure 12:    | 5. Synchronous/Asynchronous Processor-to-Processor Communication (Direct Wire to Remote Locations) |

| Figure 12     | 5. Synchronous/Asynchronous Processor-to-Processor                                                 |

|               | Communication (Using Telephone Line) 302                                                           |

| Figure 12     | 7. Data Concentrator 304                                                                           |

| Figure 12     | 3. Read Cycle Timing                                                                               |

| Figure 12     | 9. Write Cycle Timing                                                                              |

| Figure 13     | ). Interrupt Acknowledge Cycle Timing 307                                                          |

| Figure 13     | 1. Return from Interrupt Cycle Timing 308                                                          |

| Figure 13     | 2. Typical Interrupt Service                                                                       |

List of Figures UM008101-0601

**V**V/

# List of Tables

| Counte                     | er/Time  | er Channels                                                                                   |

|----------------------------|----------|-----------------------------------------------------------------------------------------------|

| Tab                        | le 1.    | Channel Values                                                                                |

| Tab                        | le 2.    | Channel Control Register5                                                                     |

| Tab                        | le 3.    | Interrupt Vector Register                                                                     |

| Tab                        | le 4.    | Channel Select Truth Table                                                                    |

| Tab                        | le 5.    | Channel Control Register                                                                      |

| Tab                        | le 6.    | Time Constant Register                                                                        |

| Tab                        | le 7.    | Interrupt Vector Register                                                                     |

| Direct                     | Memo     | ry Access                                                                                     |

| Tab                        | le 8.    | Maximum Transfer and Search Speeds (Burst and Continuous Modes)                               |

| Tab                        | le 9.    | Reduction in Z80 CPU Throughput per Kbaud (Byte Mode Transfers)57                             |

| Tab                        | le 10.   | Events and Actions                                                                            |

| Tab                        | le 11.   | Contents of Counters After DMA Stops Because of End-of-Block (Transfer Operations)            |

| Tab                        | le 12.   | Contents of Counters After DMA Stops Due to Byte Match (Search or Transfer/Search Operations) |

| Tab                        | le 13.   | DMA Status                                                                                    |

| Tab                        | le 14.   | Reinitialize Status Byte110                                                                   |

| Tab                        | le 15.   | Control Byte Order                                                                            |

| Tab                        | le 16.   | Sample DMA Program126                                                                         |

| ww.DataSh <del>q</del> ลู่ | le 17.00 | Receive Event Sequence                                                                        |

| Tab                        | le 18.   | Transmit Event Sequence                                                                       |

|                            |          |                                                                                               |

List of Tables UM008101-0601

χvi

| Parallel Inpu             | t/Output                                                      |    |

|---------------------------|---------------------------------------------------------------|----|

| Table 19.                 | PIO Mode Selection                                            | 89 |

| Serial Input/             | Output                                                        |    |

| Table 20.                 | Write Register Functions                                      | 23 |

| Table 21.                 | Read Register Functions                                       | 23 |

| Table 22.                 | Contents of Write Registers 3, 4, and 5 in Asynchronous Modes | 32 |

| Table 23.                 | Asynchronous Mode                                             | 33 |

| Table 24.                 | Contents of Write Registers 3, 4, and 6 In Synchronous Modes  | 41 |

| Table 25.                 | Bisync Transmit Mode                                          | 42 |

| Table 26.                 | Bisync Receive Mode                                           | 52 |

| Table 27.                 | Contents of Write Registers 3, 4, and 5 in SDLC Modes 2       | 58 |

| Table 28.                 | SDLC Transmit Mode                                            | 62 |

| Table 29.                 | SDLC Receive Mode                                             | 68 |

| Table 30.                 | Channel Select Functions                                      | 72 |

| Table 31.                 | Write Register 0                                              | 73 |

| Table 32.                 | Z80 SIO Commands                                              | 75 |

| Table 33.                 | Write Register 1                                              | 77 |

| Table 34.                 | Reset Commands                                                | 77 |

| Table 35.                 | Vector Results                                                | 78 |

| Table 36.                 | Receive Interrupt Modes                                       | 79 |

| Table 37.                 | Wait/Ready Functions                                          | 80 |

| Table 38.                 | Write Register 2 Interrupt Vector                             | 81 |

| Table 39.                 | Write Register 3 Logic Control                                | 82 |

| Table 40.                 | Serial Bits/Character                                         | 84 |

| Data <sub>Table</sub> 41. | Write Register 4 Rx and Tx Control                            | 85 |

| Table 42.                 | Stop Bits                                                     | 85 |

UM008101-0601 List of Tables

vvii

## **Serial Input/Output (continued)**

| Table 43. | Sync Modes                                       |

|-----------|--------------------------------------------------|

| Table 44. | Clock Rate                                       |

| Table 45. | Write Register 5 Transmitter Control287          |

| Table 46. | Transmit Bits                                    |

| Table 47. | Data Character Format                            |

| Table 48. | Write Register 6 Transmit Sync                   |

| Table 49. | Write Register 7 Receive Sync                    |

| Table 50. | Read Register 0 Rx and Tx Buffers                |

| Table 51. | Read Register 1 Special Receive Condition Status |

| Table 52. | Residue Codes                                    |

| Table 53. | Receive Character Length                         |

| Table 54. | Interrupt Vector                                 |

www.DataSheet4U.com

List of Tables UM008101-0601

www.DataSheet4U.com

UM008101-0601 List of Tables

# Counter/Timer Channels

### CTC FEATURES

- Four independently programmable counter/timer channels (CTC), each with a readable down-counter and a selectable 16 or 256 prescaler. Down-counters are reloaded automatically at zero count

- Selectable positive or negative trigger initiates timer operation

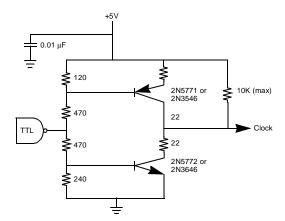

- Three channels have zero count/timeout outputs capable of driving **Darlington transistors**

- NMOS version for high-cost performance solutions

- CMOS version for the designs requiring low power consumption

- NMOS Z0843004 4 MHz, Z0843006 6.17 MHz

- CMOS Z84C3006 dc to 6.17 MHz, Z84C3008 dc to 8 MHz, Z84C3010 - dc to 10 MHz

- Interfaces directly to the Z80 CPU. Interfaces to the Z80 SIO for baud rate generation

- Standard Z80 Family daisy-chain interrupt structure provides fully vectored, prioritized interrupts without external logic. The CTC may also be used as an interrupt controller

- A 6 MHz version supports 6.144 MHz CPU clock operation

# **CTC General Description**

The Z80 CTC is a four-channel counter/timer that can be programmed by system software for a broad range of counting and timing applications. These four independently programmable channels satisfy common

microcomputer system requirements for event counting, interrupt and interval timing, and general clock rate generation.

System design is simplified by connecting the CTC directly to both the Z80 CPU and the Z80 SIO with no additional logic. In larger systems, address decoders and buffers may be required.

The CTC allows easy programming: each channel is programmed with two bytes; a third is necessary when interrupts are enabled. When started, the CTC counts down, automatically reloads its lime constant, and resumes counting. Software timing loops are eliminated. Interrupt processing is simplified because only one vector needs to be specified; the CTC internally generates a unique vector for each channel.

The Z80 CTC requires a single +5V power supply and the standard Z80 single-phase system clock. It is packaged in 28-pin DIPs, a 44-pin plastic chip carrier, and a 44-pin Quad Flat Pack. The QFP package is only available for CMOS versions.

### **CTC ARCHITECTURE**

### **Overview**

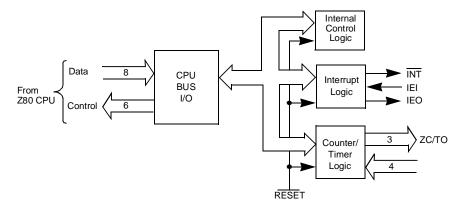

The internal structure of the Z80 CTC consists of:

- A Z80 CPU bus interface, internal control logic

- Four sets of Counter/Timer Channel logic

- Interrupt control logic

The four independent, counter/timer channels are identified by sequential numbers from 0 to 3. The CTC can generate a unique interrupt vector for each separate channel for automatic vectoring to an interrupt service www. Data routine. The four channels can be connected in four contiguous slots in the standard Z80 priority chain with channel number 0 having the highest

priority. The CPU bus interface logic allows the CTC device to interface directly to the CPU with no other external logic. However, port address decoders and/or line buffers may be required for large systems. A block diagram of the Z80 CTC is depicted in Figure 1.

Figure 1. CTC Block Diagram

# **Structure of Channel Logic**

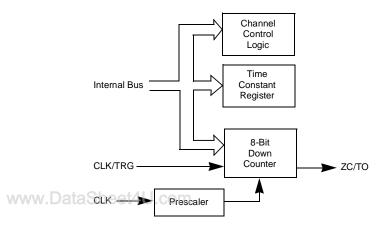

The structure of one of the four sets of Counter/Timer channel logic is illustrated in Figure 2. This logic is composed of:

- Two registers

- Two counters

- Control logic

The registers consist of an 8-bit Time Constant register and an 8-bit Channel Control register. The counters consist of an 8-bit CPU-readable down-counter and an 8-bit prescaler.

### In Channel Control Register and Logic

The Channel Control register (8-bit) and Logic is written to by the CPU to select the modes and parameters of the channel. Within the CTC device, four such registers correspond to the four Counter/Timer channels. The register to be written to is determined by the encoding of two channel select input pins: CS0 and CS1, which are usually attached to A0 and A1 of the CPU address bus. The channel values are described in Table 1.

| <b>Table</b> | 1. | Channel | Values |

|--------------|----|---------|--------|

|              |    |         |        |

|           | CS0 | CS1 |

|-----------|-----|-----|

| Channel 0 | 0   | 0   |

| Channel 1 | 0   | 1   |

| Channel 2 | 1   | 0   |

| Channel 3 | 1   | 1   |

In the control word, which is written to program each Channel Control register, bit 0 is always set; the other seven bits are programmed to select alternatives on the channel's operating modes and parameters. These values are described in Table 2. For a more complete discussion, see "CTC Operating Modes" on page 16 and "CTC Programming" on page 18).

Figure 2. Channel Block Diagram

**Table 2. Channel Control Register**

| 7         | 6    | 5                   | 4                  | 3   | 2                | 1     | 0                    |

|-----------|------|---------------------|--------------------|-----|------------------|-------|----------------------|

| Interrupt | Mode | Prescaler<br>Value* | CLK/TRG<br>Section |     | Time<br>Constant | Reset | Control or<br>Vector |

| R/W       | R/W  | R/W                 | R/W                | R/W | R/W              | R/W   | R/W                  |

| Bit Number | Field             | R/W | Value | Description                                    |

|------------|-------------------|-----|-------|------------------------------------------------|

| 7          | Interrupt         | R/W | 1     | Enable Interrupt                               |

|            | _                 |     | 0     | Disable Interrupt                              |

| 6          | Mode              | R/W | 1     | COUNTER Mode                                   |

|            |                   |     | 0     | TIMER Mode                                     |

| 5          | Prescaler Value*  | R/W | 1     | 256                                            |

|            |                   |     | 0     | 16                                             |

| 4          | CLK/TRG Edge      | R/W | 1     | Rising Edge                                    |

|            | Section           |     | 0     | Falling Edge                                   |

| 3          | Time Trigger*     | R/W | 1     | CLK/TRG Pulse Starts Timer                     |

|            |                   |     | 0     | Automatic trigger when time constant is loaded |

| 2          | Time Constant     | R/W | 1     | Time Constant Follows                          |

|            |                   |     | 0     | No Time Constant Follows                       |

| 1          | Reset             | R/W | 1     | Software Reset                                 |

|            |                   |     | 0     | Continue Operation                             |

| 0          | Control or Vector | R/W | 1     | Control                                        |

|            |                   |     | 0     | Vector                                         |

| *TIMER mod | de only           |     |       |                                                |

#### The Prescaler

The prescaler is an 8-bit device that is used in the TIMER mode only. The prescaler is programmed by the CPU through the Channel Control register www.DataSh to divide its input, the System clock (0), by 16 or 256. The output of the prescaler is then fed as an input to clock the down-counter. Each time that

the down-counter counts to zero, the down-counter is automatically reloaded with the contents of the Time Constant register. This process divides the System clock by an additional factor of the time constant. Each time the down-counter counts to zero, its output, Zero Count/Timeout (ZC/TO), is pulsed High.

### The Time Constant Register

The 8-bit Time Constant register is used in both Counter and Timer modes. It is programmed by the CPU just after the channel control word, with an integer time constant value of 1 through 256. This register loads the programmed value to the down-counter when the CTC is first initialized and reloads the same value into the down-counter automatically whenever it counts down thereafter to zero. If a new time constant is loaded into the Time Constant register while a channel is counting or timing, the present down count is completed before the new time constant is loaded into the down counter. For details about writing a time constant to a CTC channel, see "CTC Programming" on page 18

#### The Down-Counter

The down-counter is an 8-bit register that is used in both COUNTER and TIMER modes. This register is loaded by the Time Constant register both initially, and when it counts down to zero. In the COUNTER mode, the down-counter is decremented by each external clock edge. In the TIMER mode, it is decremented by the clock output of the prescaler. By performing a simple I/O Read at the port address assigned to the selected CTC channel, the CPU can access the contents of the down-counter and obtain the number of counts-to-zero. Any of the four CTC channels may be programmed to generate an interrupt request sequence each time the zero count is reached.

In Channels 0, 1, and 2, a signal pulse appears at the corresponding ZC/TO pin when the zero count condition is reached. Because of package pin limitations, however, Channel 3 does not have this pin and so may be used only in applications where this output pulse is not required.

www.Data

# **Interrupt Control Logic**

The Interrupt Control Logic insures that the CTC acts in accordance with Z80 system interrupt protocol for Nested Priority Interrupting and Return From Interrupt. The priority of any system device is determined by its physical location in a daisy-chain configuration. Two signal lines, CIEI and IEO, are provided in CTC devices to form this system daisy-chain. The device closest to the CPU has the highest priority. Within the CTC, interrupt priority is predetermined by channel number, with Channel 0 having highest and Channel 3 the lowest priority. See Table 3. The purpose of a CTC-generated interrupt, as with any peripheral device, is to force the CPU to execute an interrupt service routine. According to Z80 system interrupt protocol, lower priority devices or channels may not interrupt higher priority devices or channels that have not had their interrupt service routines completed. However, high priority devices or channels may interrupt the servicing of lower priority devices or channels.

Table 3. Interrupt Vector Register

| 7                | 6 | 5 | 4       | 3          | 2    | 1 | 0 |

|------------------|---|---|---------|------------|------|---|---|

| Supplied by User |   |   | Channel | Identifier | Word |   |   |

| R/W              |   |   | R/      | W          | R/W  |   |   |

| Bit Number | Field              | R/W | Value | Description      |

|------------|--------------------|-----|-------|------------------|

| 7–3        | Reserved           | R/W |       | Supplied by User |

| 2–1        | Channel Identifier | R/W | 11    | Channel 3        |

|            | (Automatically     |     | 10    | Channel 2        |

|            | inserted by CTC)   |     | 01    | Channel 1        |

|            |                    |     | 00    | Channel 0        |

| 0          | Word               | R/W | 1     | Control          |

|            |                    |     | 0     | Interrupt Vector |

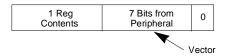

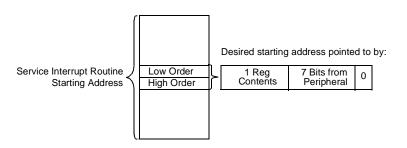

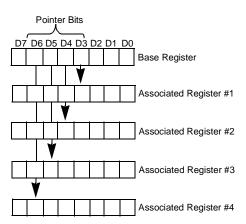

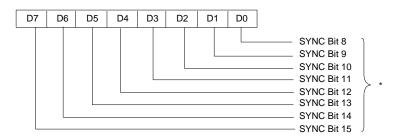

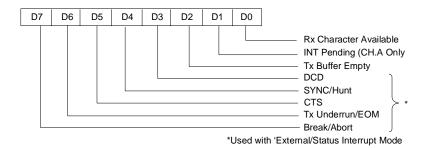

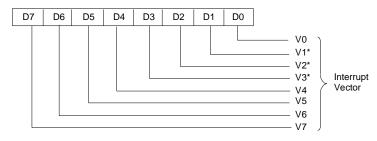

A CTC channel may be programmed to request an interrupt every time its down-counter reaches a count of zero. However, using this feature requires that the CPU be in INTERRUPT Mode 2. After the interrupt request, the CPU sends out an interrupt acknowledge. The CTC's interrupt control logic determines the highest-priority channel requesting an interrupt. If the CTC's IEI input is active, indicating that it has priority within the system daisy-chain, it places an 8-bit interrupt vector on the system data bus as follows:

- 1. The high order five bits of this vector were written to the CTC earlier as part of the CTC initial programming process.

- 2. The next two bits are provided by the CTC's interrupt control logic as a binary code corresponding to the highest-priority channel requesting an interrupt.

- 3. The low-order bit of the vector is always zero according to a convention (Figure 3).

This interrupt vector is used to form a pointer to a location in memory where the address of the interrupt service routine is stored in a table. The vector represents the least-significant eight bits. The CPU reads the contents of the I register to provide the most-significant eight bits of the 16-bit pointer. The address pointed to in memory contains the low-order byte and the next highest address contains the high-order byte of an address, which in turn contains the first Op Code of the interrupt service routine. Thus, in Mode 2, a single 8-bit vector stored in an interrupting CTC can result in an indirect call to any memory location (Figure 3).

Z80 16-Bit Pointer (Interrupt Starting Address)

Figure 3. | Z80 16-Bit Pointer (Interrupt Starting Address)

9

According to Z80 system convention, all addresses in the interrupt service routine table place their low-order byte in an even location in memory, and their high-order byte in the next highest location in memory. This location is always odd so that the least-significant bit of any interrupt vector is always even. Therefore, the least-significant bit of any interrupt vector always zero.

The RETI instruction is used at the end of an Interrupt Service Routine to initialize the Daisy Chain Enable line IEO for control of nested priority interrupt handling. The CTC monitors the system data bus and decodes this instruction when it occurs. Therefore, the CTC channel control logic knows when the CPU has completed servicing an interrupt.

## **CTC PIN DESCRIPTION**

### **Pin Functions**

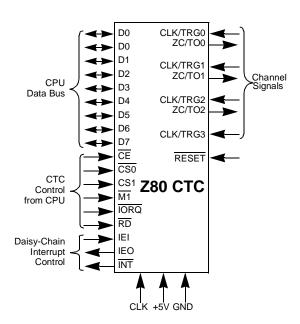

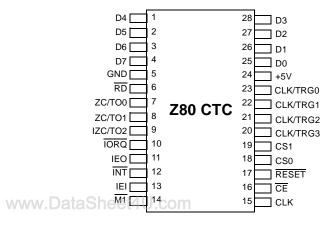

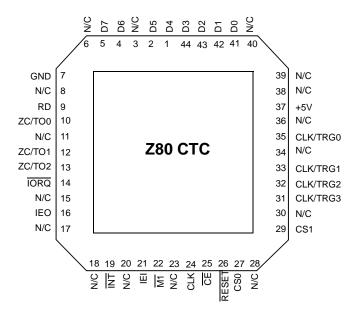

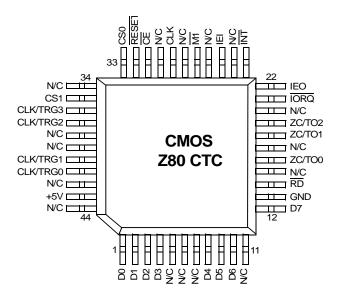

Diagrams of the Z80 CTC Pin Configuration and Z80 CTC Package Configuration are illustrated in Figure 4 through Figure 7, respectively. This section describes the function of each pin.

Figure 4. CTC Pin Configuration

Figure 5. Package Configuration

Figure 6. 44-Pin Chip Carrier Pin Assignments

Figure 7. 44-Pin Quad Flat Pack Pin Assignments

#### Bit 7-Bit 0

**System Data Bus** (bidirectional, tristate). This bus is used to transfer all date and command words between the Z80 CPU and the Z80 CTC. There are eight bits on this bus, of which bit 0 is the least-significant. CSI CSO Channel Select (input, active High). These pins form a 2-bit binary address code for selecting one of the four independent CTC channels for an I/O Write or Read. (See Table 4).

**Table 4. Channel Select Truth Table**

|           | CS1 | CS0 |

|-----------|-----|-----|

| Channel 0 | 0   | 0   |

| Channel 1 | 0   | 1   |

| Channel 2 | 1   | 0   |

| Channel 3 | 1   | 1   |

#### CE

Chip Enable (input, active Low). A Low level on this pin enables the CTC to accept control words, interrupt vectors, or time constant data words from the Z80 data bus during an I/O Write cycle; or to transmit the contents or the down-counter to the CPU during an I/O Read cycle. In most applications this signal is decoded from the eight least-significant bits of the address bus for any of the four I/O port addresses that are mapped to the four Counter/Timer channels.

### $\mathsf{Clock}(\Phi)$

**System Clock (input).** This single-phase clock is used by the CTC to internally synchronize certain signals.

#### М1

Machine Cycle One Signal from CPU (input, active low). When M1 is active and the  $\overline{RD}$  signal is active, the CPU fetches an instruction from memory. When  $\overline{M1}$  is active and the  $\overline{IORQ}$  signal is active, the CPU acknowledges an interrupt, alerting the CTC to place an interrupt vector on the Z80 data bus if it has daisy-chain priority and one of its channels has requested an interrupt.

#### **IORQ**

Input/Output Request from CPU (input, active Low). The  $\overline{IORQ}$  signal is used in conjunction with the  $\overline{CE}$  and  $\overline{RD}$  signals to transfer data and channel control words between the Z80 CPU and the CTC. During a CTC Write cycle,  $\overline{IORQ}$  and  $\overline{CE}$  must be true and  $\overline{RD}$  false. The CTC does not receive a specific write signal. Instead it generates one internally from the inverse of a valid  $\overline{RD}$  signal. In a CTC Read cycle,  $\overline{IORQ}$ ,  $\overline{CE}$ , and  $\overline{RD}$  must be active to place the contents of the down-counter on the Z80 data bus. If  $\overline{IORQ}$  and  $\overline{M1}$  are both true, the CPU is acknowledging an interrupt request, and the highest priority interrupting channel places its interrupt vector on the Z80 data bus.

#### RD

Read Cycle Status from the CPU (input, active Low). The  $\overline{RD}$  signal is used in conjunction with the  $\overline{IORQ}$  and  $\overline{CE}$  signals to transfer data and channel control words between the Z80 CPU and the CTC. During a CTC Write Cycle,  $\overline{IORQ}$  and  $\overline{CE}$  must be true and  $\overline{RD}$  false. The CTC does not receive a specific write signal, instead it generates one internally from the inverse of a valid  $\overline{RD}$  signal. In a CTC Read cycle,  $\overline{IORQ}$   $\overline{CE}$ , and  $\overline{RD}$  must be active to place the contents of the down-counter on the Z80 data bus.

#### IFI

**Interrupt Enable In (input, active High).** This signal is used to form a system-wide interrupt daisy-chain which establishes priorities when more than one peripheral device in the system has interrupting capability. A High level on this pin indicates that no other interrupting devices of higher priority in the daisy chain are being serviced by the Z80 CPU.

#### **IEO**

Interrupt Enable Out (output, active High. The IEO signal, in conjunction with IEI, is used to form a system-wide interrupt priority daisy-chain. IEO is High only if IEI is High and the CPU is not servicing

an interrupt from any CTC channel. Therefore, this signal blocks lower-priority devices from interrupting while a higher-priority interrupting device is being serviced by the CPU.

#### INT

**Interrupt Request (output, open-drain, active Low).** This signal goes true when a CTC channel, which has been programmed to enable interrupts, has a zero-count condition in its down-counter.

#### RESET

**Reset** (input, active Low). This signal stops all channels from counting and resets interrupt enable bits in all control registers, thereby disabling CTC-generated interrupts. The ZC/TO and INT outputs go inactive, IEO reflects IEI, and the CTC's data bus output drivers go to the high-impedance state.

#### CLK/TRG3-CLK/TRG0

**External Clock/Timer Trigger (input, user-selectable active High or Low).** Four CLK/TRG pins correspond to the four independent CTC channels. In the Counter mode, every active edge on this pin decrements the down-counter. In the TIMER mode, an active edge on this pin initiates the timing function. The user may select the active edge to be either rising or falling.

#### ZC/TO2-AC/TO0

**Zero Count/Timeout (output, active High).** Three ZC/TO pins correspond to CTC Channels 2 through 0. (Because of package pin limitations Channel 3 has no ZC/TO pin.) In either COUNTER mode or TIMER mode, when the down-counter decrements to zero, an active High pulse appears at this pin.

### **CTC OPERATING MODES**

### Overview

At power-on, the Z80 CTC state is undefined. Asserting RESET puts the CTC in a known state. Before a channel can begin counting or timing, a channel control word and a time constant data word must be written to the appropriate registers of that channel. Additionally, if a channel has been programmed to enable interrupts, an interrupt vector word must be written to the CTC's interrupt control logic. (For further details, refer the "CTC Programming" on page 18) When the CPU has written all of these words to the CTC, all active channels are programmed for immediate operation in either the COUNTER mode or the TIMER mode.

### **CTC COUNTER Mode**

In CTC COUNTER mode, the CTC counts edges of the CLK/TRG input. This mode is programmed for a channel when its Channel Control Word is written with bit 6 set. The channel's external clock (CLK/TRG) input is monitored for a series of triggering edges. After each, in synchronization with the next rising edge of  $\Phi$  (the System clock), the down-counter (which is initialized with the Time Constant Data word at the start of each sequence of down-counting) is decremented. Although there is no setup time requirement between the triggering edge of the External clock and the rising edge of  $\Phi$  (Clock), the down-counter is not decremented until the following pulse. A channel's External clock input is pre programmed by bit 4 of the channel control word to trigger the decrementing sequence with either a high- or a low-going edge.

In Channels 0, 1, or 2, when the down-counter is successively decremented from the original time constant (until it reaches zero), the Zero Count (ZC/WWW.Data TO) output pin for that channel is pulsed active (High). Due to package pin limitations, this pin does not exist on Channel 3 and so this pin may only be

used in applications where this output pulse is not required. Additionally, if the channel is pre-programmed by bit 7 of the channel control word, an interrupt request sequence is generated. For more details, see the CTC Interrupt Servicing section

The zero-count condition also results in the automatic reload of the down-counter with the original time constant data word in the Time Constant register. There is no interruption in the sequence of continued down-counting. If the Time Constant register is written with a new Time Constant Data Word while the down-counter is decrementing, the present count is completed before the new time constant is loaded into the down-counter.

### **CTC TIMER Mode**

In CTC TIMER mode, the CTC generates timing intervals that are an integer value of the system clock period. This mode is programmed for a channel when its Channel Control Word is written with bit 6 reset. The channel then may be used to measure intervals of time based on the System clock period. The System clock is fed through the prescaler and the down-counter. Depending on the pre programmed bit 5 in the Channel Control Word, the prescaler divides the System clock by a factor of 16 or 256.

The output of the prescaler is then used as a clock to decrement the down-counter, which may be pre programmed with any time constant integer between 1 and 256. The time constant is automatically reloaded into the down-counter at each zero-counter condition. At zero count, the channel's Time Cut (ZC/TO) output (which is the output of the down-counter) is pulsed, resulting in a uniform pulse train of the precise period given by the product as shown below.

Where  $t_c$  is the System clock, P is the prescaler factor of 16 or 256, and TC is the pre-programmed time constant.

Timing may be initialized automatically or with a triggering edge at the channel's Timer Trigger (CLK/TRG) input. This timing is determined by programming bit 3 of the channel control word. If bit 3 is reset?, the timer automatically begins operation at the start of the CPU cycle following the I/O Write machine cycle that loads the time constant data word to the channel.

If bit 3 is set, the timer begins operation on the second succeeding rising edge of  $\Phi$  after the Timer Trigger edge following the loading of the time constant data word.

If no time constant word is to follow, the timer begins operation on the second succeeding rising edge of  $\Phi$  after the Timer Trigger edge and following the control word write cycle. Bit 4 of the channel control word is pre programmed to select whether the Timer Trigger is sensitive to a rising or falling edge. There is no setup requirement between the active edge of the Timer Trigger and the next rising edge of  $\Phi$ .

If the Timer Trigger edge occurs closer than a specified minimum setup time to the rising edge of  $\Phi$ , the down-counter does not begin decrementing until the following rising edge of  $\Phi$ . If bit 7 in the channel control word is set, the zero-count condition in the down-counter causes a pulse at the channel's Time Out pin, and initiates an interrupt request sequence. (For more details, see "CTC Interrupt Servicing" on page 27).

## **CTC PROGRAMMING**

### **Overview**

To begin counting or timing operations, a Channel Control Word and Time Constant Data Word are written to the appropriate channel by the CPU. These words are stored in the Channel Control or Time Constant registers www. Data of each channel. If a channel has been programmed to enable interrupts, an interrupt vector is written to the appropriate register in the CTC. Because of

automatic features in the interrupt control logic, one pre-programmed interrupt vector suffices for all four channels.

# **Loading The Channel Control Register**

To load a Channel Control Word, the CPU performs a normal I/O Write sequence to the port address corresponding to the desired CTC channel. The CTC input pins CS0 and CS1 are used to form a 2-bit binary address to select one of four channels within the device. (See Table 2 on page 5.) In many system architectures, these two input pins are connected to Address Bus lines A0 and A1, respectively, so that the four channels in a CTC device occupy contiguous I/O port addresses. A word written to a CTC channel is interpreted as a channel control word, and loaded into the channel control register (bit 0 is a logic 1). The other seven bits of this word select operating modes and conditions as indicated in Table 2.

**Table 5. Channel Control Register**

| 7         | 6    | 5                   | 4                  | 3   | 2                | 1     | 0                    |

|-----------|------|---------------------|--------------------|-----|------------------|-------|----------------------|

| Interrupt | Mode | Prescaler<br>Value* | CLK/TRG<br>Section |     | Time<br>Constant | Reset | Control or<br>Vector |

| R/W       | R/W  | R/W                 | R/W                | R/W | R/W              | R/W   | R/W                  |

| Bit<br>Number    | Field            | R/W | Value | Description                        |  |

|------------------|------------------|-----|-------|------------------------------------|--|

| 7                | Interrupt        | R/W | 1 0   | Enable Interrupt Disable Interrupt |  |

| 6                | Mode             | R/W | 1 0   | COUNTER Mode<br>TIMER Mode         |  |

| 5                | Prescaler Value* | R/W | 1     | 256                                |  |

| *TIMER mode only |                  |     |       |                                    |  |

| Bit<br>Number | Field             | R/W | Value | Description                                    |

|---------------|-------------------|-----|-------|------------------------------------------------|

| 4             | CLK/TRG Edge      | R/W | 1     | Rising Edge                                    |

|               | Section           |     | 0     | Falling Edge                                   |

| 3             | Time Trigger*     | R/W | 1     | CLK/TRG Pulse Starts Timer                     |

|               |                   |     | 0     | Automatic trigger when time constant is loaded |

| 2             | Time Constant     | R/W | 1     | Time Constant Follows                          |

|               |                   |     | 0     | No Time Constant Follows                       |

| 1             | Reset             | R/W | 1     | Software Reset                                 |

|               |                   |     | 0     | Continue Operation                             |

| 0             | Control or Vector | R/W | 1     | Control                                        |

|               |                   |     | 0     | Vector                                         |

**Bit 7 = 1.** Each channel is enabled to generate an interrupt request sequence when the down-counter reaches a zero-count condition. To set the interrupt bit to 1 in any of the four Channel Control registers an interrupt vector is written to the CTC before operation begins. Channel interrupts may be programmed in either Counter or Timer mode. If an updated channel control word is written to a channel in operation, with bit 7 set, the interrupt enable selection is not retroactive to a preceding zero-count condition.

- Bit 7 = 0. Channel interrupts disabled.

- **Bit 6 = 1.** Counter mode selected. The down-counter is decremented by each triggering edge of the External clock (CLK/TRG) input. The prescaler is not used.

- **Bit 6 = 0.** Timer mode selected. The prescaler is clocked by the System clock  $\Phi$ , and the output of the prescaler in turn clocks the down-counter. The output of the down-counter (the channel's ZC/TO output) is a uniform pulse train of period given by the product as shown below

where t<sub>c</sub> is the period of System clock, P is the prescaler factor of 16 or 256, and TC is the time constant data word.

Bit 5 = 1. Defined for Timer mode only. Prescaler factor is 256.

Bit 5 = 0. Defined for Timer mode only. Prescaler factor is 16.

**Bit 4 = 1.** TIMER Mode: positive edge trigger starts timer operation.

COUNTER Mode: positive edge decrements the down-counter.

Bit 4 = 0. TIMER Mode: negative edge trigger starts timer operation.

COUNTER Mode: negative edge decrements the down-counter.

**Bit 3 = 1.** TIMER Mode only. External trigger is valid for starting timer operation after rising edge of T2 of the machine cycle following the one that loads the tune constant. The prescaler is decremented two clock cycles later if the setup tune is met, otherwise three clock cycles.

Bit 3 = 0. TIMER Mode only. Timer begins operation on the rising edge of T2 of the machine cycle following the one that loads the time constant.

Bit 2 = 1. The time constant data word for the Time Constant register is the next word written to this channel. If an updated channel control word and time constant data word are written to a channel while it, is already in operation, the down-counter continues decrementing to zero before the new time constant is loaded.

**Bit 2 = 0.** No time constant date word for the Time Constant register is to follow. The channel control word updates the status of a channel already in operation to channel will not operate without a correctly programmed data word in the lime Constant register. Bit 2 in the channel control word must be set in order to write to the Time Constant register.

**Bit 1 = 1.** Counting and/or timing operation is terminated and the channel is reset. This is not a stored condition. The bits in the Channel Control register are unchanged. If bits 1 and 2 are set to 1, the channel resumes operation

www.DataSh.upon loading a time constant.

Bit 1 = 0. Channel continues current operation.

## **Loading The Time Constant Register**

A Time Constant Data Word is written to the Time Constant register by the CPU. This event occurs on the I/O Write Cycle following that of the channel control word. The Time Constant Data Word may be any integer value in the range 1-256 (Table 6). If all eight bits in this word are zero, it is interpreted as 256. If a Time Constant Date Word is loaded to a channel already in operation, the down-counter continues decrementing to zero before the new time constant is loaded.

**Table 6. Time Constant Register**

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TC7 | TC6 | TC5 | TC4 | TC3 | TC2 | TC1 | TC0 |

| R/W |

## **Loading The Interrupt Vector Register**

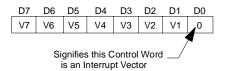

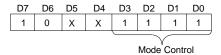

The Z80 CTC operates with the Z80 CPU programmed for mode 2 interrupt response. When a CTC interrupt request is acknowledged, a 16-bit pointer is formed to obtain a corresponding interrupt service routine starting address (Figure 8). The upper eight bits of this pointer are provided by the CPU's I register; the lower eight bits are provided by the CTC in the form of an interrupt vector unique to the requesting channel (Figure 8). For further details, see "CTC Interrupt Servicing" on page 27.

The five high-order bits of the interrupt vector are written to the CTC in advance as part of the initial programming sequence. The CPU writes to the I/O port address corresponding to the CTC Channel 0. A 0 in bit 0 signals the CTC to load the incoming word into the interrupt vector register. When the interrupt vector is placed on the Z80 data bus, the interrupt control logic of the CTC automatically supplies a binary code in bits 1 and 2 identifying thick of the four CTC channels is to be sequiced.

www. Data which of the four CTC channels is to be serviced.

Figure 8. Mode 2 Interrupt Operation

**Table 7. Interrupt Vector Register**

| 7   | 6  | 5            | 4       | 3          | 2    | 1 | 0   |

|-----|----|--------------|---------|------------|------|---|-----|

|     | Su | ipplied by U | Channel | Identifier | Word |   |     |

| R/W |    |              |         |            | R    | W | R/W |

| Bit<br>Number | Field                 | R/W | Value                | Description                             |

|---------------|-----------------------|-----|----------------------|-----------------------------------------|

| 7–3           | Reserved              | R/W |                      | Supplied by User                        |

| 2–1           | Channel<br>Identifier | R/W | 11<br>10<br>01<br>00 | Channel 3 Channel 2 Channel 1 Channel 0 |

| 0             | Word                  | R/W | 1 0                  | Control<br>Interrupt Vector             |

#### **CTC TIMING**

#### **Overview**

This section describes the timing relationships of the relevant CTC pins for the following types of operation:

- Writing a word to the CTC

- Reading a word from the CTC

- Counting and timing

A timing diagram, Figure 12, relating to interrupt servicing is found in "Interrupt Acknowledge Cycle" on page 28.

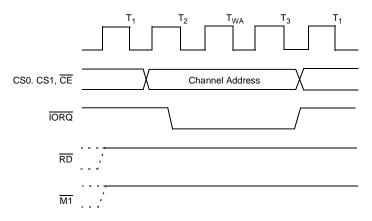

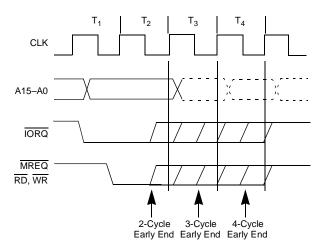

# **CTC Write Cycle**

Figure 9 illustrates the timing associated with the CTC Write cycle. This sequence is applicable to loading a channel control word, an interrupt vector, or a time constant data word.

In the sequence shown, during clock cycle T1, the Z80 CPU prepares for the Write cycle with a false (High) signal at CTC input pin  $\overline{RD}$  (Read). Because the CTC has no separate Write signal input, it generates its own input internally from the false  $\overline{RD}$  input. During clock cycle T2, the Z80 CPU initiates the Write cycle with true (Low) signals at CTC input pins  $\overline{IORQ}$  (I/O Request) and  $\overline{CE}$  (Chip Enable). (See Note below.) A 2-bit binary code appears at CTC inputs CS1 and CS0 (Channel Select 1 and 0), specifying which of the four CTC channels is being written to. At this time, a channel control, interrupt vector, or time constant data word may be loaded to the appropriate CTC internal register in synchronization with the rising edge beginning clock cycle T3.

Note: M1 must be false to distinguish the cycle from an interrupt acknowledge.

Figure 9. CTC Write Cycle

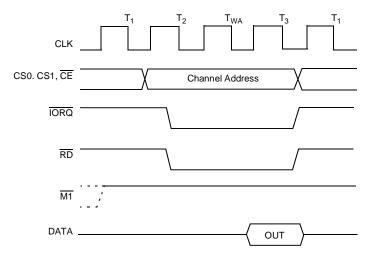

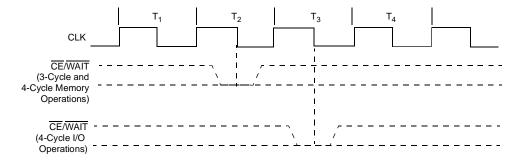

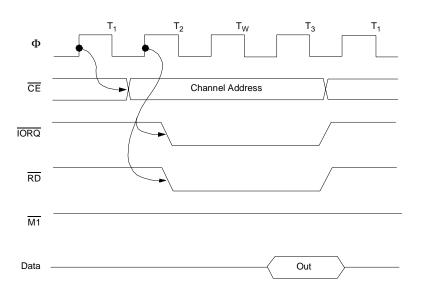

# **CTC Read Cycle**

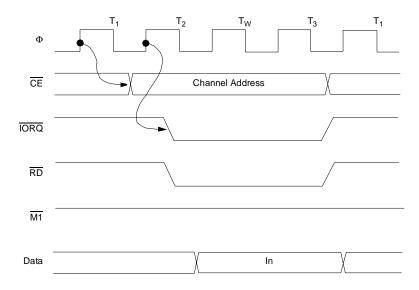

Figure 10 illustrates the timing associated with the CTC Read cycle. This sequence is used when CPU reads the current contents of the down counter. During clock cycle T2, the Z80 CPU initiates the Read cycle with true signals at input pins  $\overline{\text{RD}}$  (Read),  $\overline{\text{IORQ}}$  (I/O Request), and  $\overline{\text{CE}}$  (Chip Enable). A 2-bit binary code appears at CTC inputs CS1 and CS0 (Channel Select 1 and 0), specifying which of the four CTC channels is being read from. (See Note below.) On the rising edge of the cycle T3, the valid contents of the down-counter rising edge of cycle T2 is available on the Z80 data bus. No additional wait states are allowed.

Note:  $\overline{M1}$  must be false to distinguish the cycle from an interrupt acknowledge.

Figure 10. CTC Read Cycle

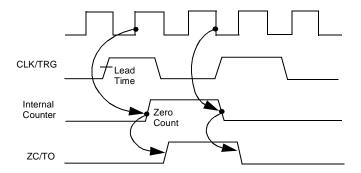

# **CTC Counting and Timing**

Figure 11 illustrates the timing diagram for the CTC Counting and Timing modes.

In the Counter mode, the edge (rising edge is active in this example) from the external hardware connected to pin CLK/TRG, decrements the down-counter in synchronization with the System Clock  $\Phi$ . This CLK/TRG pulse must have a minimum width and the minimum period must not be less than twice the System clock period. Although there is no setup time requirement between the active edge of the CLK/TRG and the rising edge of  $\Phi$ , if the CLK/TRG edge occurs closer than a specified minimum time, the decrement of the down-counter will be delayed one cycle of  $\Phi$ . Immediately after the 1 to 0 decrement of the down-counter, the ZC/TO output is pulsed true.

In the Timer mode, a pulse trigger (user selectable as either active High or active Low) at the CLK/TRG pin enables the timing function on the second succeeding rising edge of Φ. As in the Counter mode, the triggering pulse is

detected asynchronously and must have a minimum width. The timing function is initiated in synchronization with  $\Phi$ . A minimum setup time is required between the active edge of the CLK/TRG and the rising edge of  $\Phi$ . If the CLK/TRG edge occurs closer than this, the initiation of the timer function will be delayed one cycle of  $\Phi$ .

Figure 11. CTC Counting and Timing

## CTC INTERRUPT SERVICING

## **Overview**

Each CTC channel may be individually programmed to request an interrupt every time its down-counter reaches zero. The purpose of a CTC-generated interrupt is to force the CPU to execute an interrupt service routine. To use this feature the Z80 CPU must be programmed for Mode 2 interrupt response. In this mode, when a CTC channel interrupt request is acknowledged, a 16-bit pointer must be formed to obtain a corresponding interrupt service routine. The lower eight bits of the pointer are provided by the CTC in the form of an interrupt vector unique to the requesting

www.DataSh channel. For further details, refer to the Z80 CPU User's Manual.

The CTC's interrupt control logic ensures that it acts in accordance with Z80 system interrupt protocol for nested priority interrupt and proper return from interrupt. The priority of any system device is determined by its physical location in a daisy-chain configuration. Two signal lines (IEI and IEO) are provided in the CTC to form the system daisy chain. The device closest to the CPU has the highest priority. Interrupt priority is predetermined by channel number, with Channel 0 having highest priority. According to Z80 system interrupt protocol, low priority devices or channels may not interrupt higher priority devices or channels that have not had their interrupt service routines completed. High priority devices or channels may interrupt the servicing of lower priority devices or channels. (For further details, see "CTC Architecture" on page 2.)

"Return from Interrupt Cycle" on page 29 and "Daisy-Chain Interrupt Servicing" on page 30 describe the nominal timing relationships of the relevant CTC pins for the Interrupt Acknowledge cycle and the Return from Interrupt cycle. "Daisy-Chain Interrupt Servicing" on page 30 discusses a typical example of daisy-chain interrupt servicing.

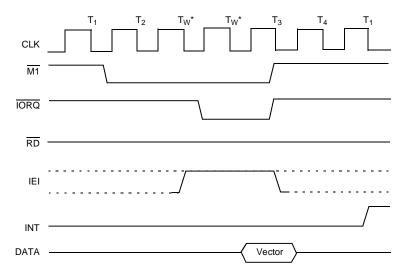

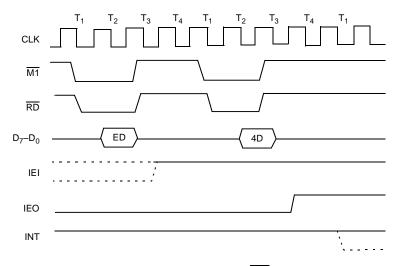

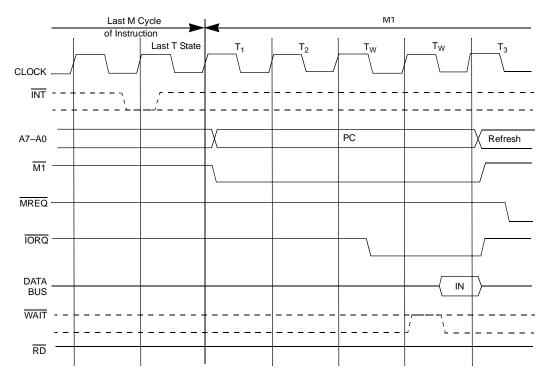

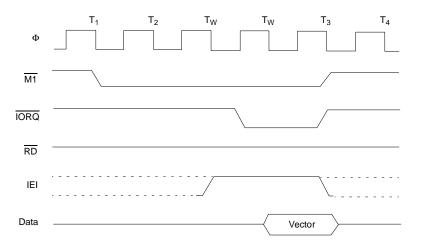

## Interrupt Acknowledge Cycle

Figure 12 illustrates the timing associated with the Interrupt Acknowledge cycle. After an interrupt is requested by the CTC, the CPU sends out an interrupt acknowledge ( $\overline{\text{M1}}$  and  $\overline{\text{IORQ}}$ ). To insure that the daisy-chain enable lines stabilize, channels are inhibited from changing their interrupt request status when  $\overline{\text{M1}}$  is active.  $\overline{\text{M1}}$  is active two clock cycles earlier than  $\overline{\text{IORQ}}$  and  $\overline{\text{RD}}$  is false to distinguish the cycle from an instruction fetch. During this time, the interrupt logic of the CTC determines the highest priority channel requesting an interrupt. If the CTC Interrupt Enable input (IEI) is active, the highest priority interrupting channel within the CTC places its interrupt vector onto the data bus when  $\overline{\text{IORQ}}$  goes active. Two Wait States (TW\*) are automatically inserted at this time to allow the daisy-

Www. Data chain to stabilize. Additional Wait States may be added.

Figure 12. Interrupt Acknowledge Cycle

## **Return from Interrupt Cycle**

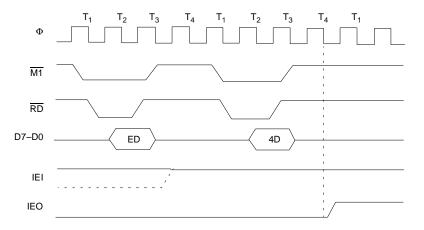

Figure 13 illustrates the timing associated with the RETI Instruction. This instruction is used at the end of an Interrupt Service Routine to initialize the daisy-chain enable lines for control of nested priority interrupt handling. The CTC decodes the two-byte RETI code internally and determines whether it is intended for a channel being serviced.

When several Z80 peripheral chips are in the daisy-chain, IEI becomes active on the chip currently under service when an EDH Op Code is decoded. If the following Op Code is 4DH, the peripheral being serviced is re-initialized and its IEO becomes active.

www DataSheet4U com

\*INT goes Low if more interrupts are pending on the RTC.

Figure 13. Return from Interrupt Cycle

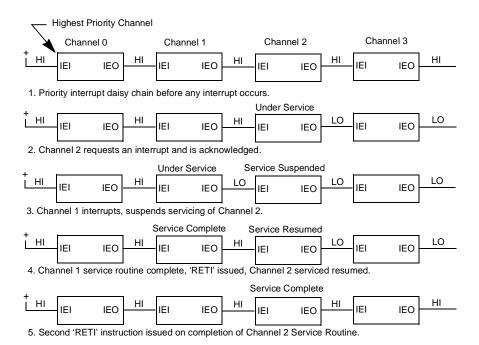

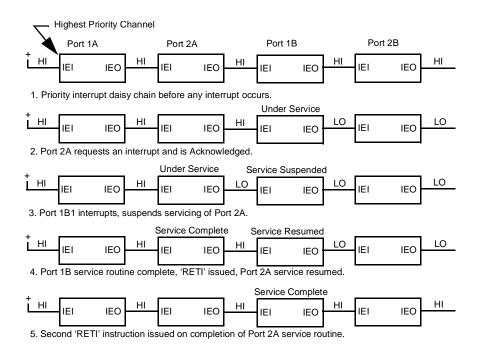

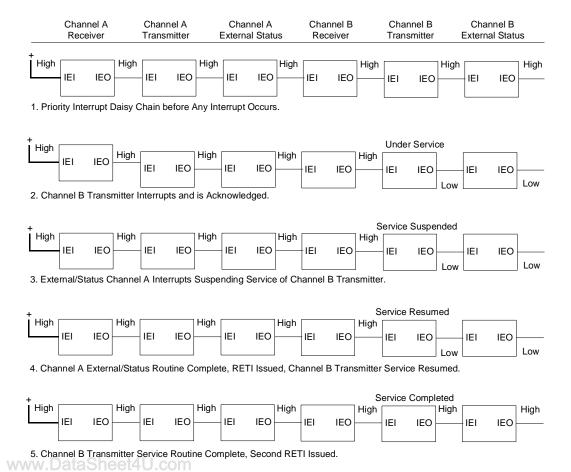

# **Daisy-Chain Interrupt Servicing**

Figure 14 illustrates a typical nested interrupt sequence that may occur in the CTC. In this example, Channel 2 interrupts and is granted service. While this channel is being serviced, higher priority Channel 1 interrupts and is granted service. The service routine for the higher priority channel is completed, and a RETI instruction is executed to signal the channel that its routine is complete (see "Return from Interrupt Cycle" on page 29 for further details). At this time, the service routine of the lower priority Channel 2 is resumed and completed.

Figure 14. Daisy-Chain Interrupt Servicing

www DataSheet4U com

# Direct Memory Access

#### **DMA OVERVIEW**

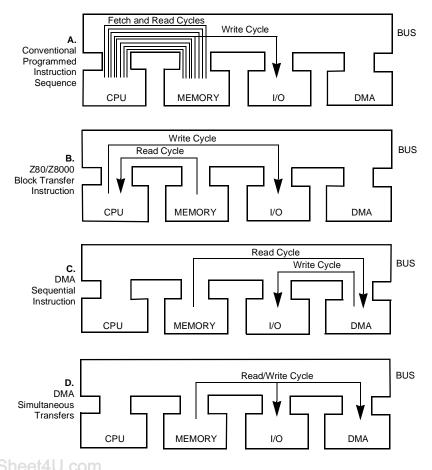

Direct Memory Access (DMA) and DMA Controllers are dedicated to controlling high-speed block transfers of data independently of the CPU.

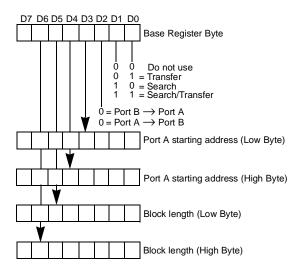

DMA data transfers are usually between memory and I/O, or vice versa. A DMA controller (DMAC) also performs some transfers that have traditionally been done by the CPU. For example, the Z80 DMA can perform memory-to-memory, memory-to-I/O, and I/O-to-memory transfers, as well as search for particular patterns of bits in a byte either simultaneously with or independently of transfers.

The advantages of DMA transfers are:

- Transfers bypass the CPU

- Transfers are fast

## **CPU Data Transfers**

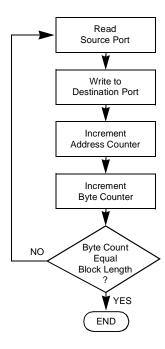

In systems without DMA, data transfers must pass through the CPU and be implemented in software. Data transfers through the CPU include executing an instruction sequence for input and output, and tracking each byte of data in the block to be transferred.

Figure 15 illustrates the minimum sequence of instructions that must be fetched from memory and executed by conventional CPUs to transfer a block of data one byte at a time. Most CPUs require many more instructions.

CPU transfers are relatively slow and tie up the CPU. In addition response time (startup time for the first byte) is also usually slow because the I/O device typically uses interrupts to signal its readiness, and the CPU interrupt service routine causes a significant time lag in transferring the first byte.

Figure 15. Typical CPU I/O Sequence

The Z80 and Z8000 CPUs both have block-transfer and string-search instructions that can operate on up to 64 Kbytes of data with a single instruction.

A single block transfer instruction repetitively performs all of the functions illustrated in Figure 15 on an entire sequence of bytes. Therefore, transfer rates are significantly faster. The 4 MHz Z80A CPU can transfer at about 200 Kbytes/sec and the 4 MHz Z8000 CPU can reach 800 Kbytes/sec.

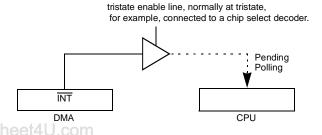

The problem with CPU block transfers in the Z80 and Z8000 devices is not transfer speed but response time at startup. One of the following methods is www. Data normally used to set up executing a block transfer instruction:

- The I/O device interrupts the CPU and the block transfer instruction is executed in the CPU interrupt service routine. This method has a response time of at least 5 to 10 μs, even in 4 MHz Z80A and Z8000 devices.

- The CPU begins executing the device service routine before the I/O device is ready, and a flag bit is constantly polled by the CPU. When the flag bit indicates that the device is ready, the CPU jumps to the block transfer instruction. This method sometimes produces a response time of less than 5 µs, but it uses the entire capability of the CPU.

- The CPU begins executing the block transfer instruction in an interrupt service routine before the I/O device is actually ready. The I/O device idles the CPU with the Wait line just after the Read and Chip-Select lines become active. When the I/O device is ready, it releases the wait line and the transfer is completed. This method gives the best response time (250 ns in a 4 MHz Z80A or Z8000 CPU) but ties up the bus.

Both transfer and response times on most CPUs are often too slow. While transfer speed can be quite high with the Z80 and Z8000 CPUs, the response time can be too long in interrupt-driven transfer situations.

#### **DMA Data Transfers**

A DMA controller (DMAC) performs direct data transfers between the source and destination without going through the CPU, and without the instruction fetches required by the CPU. It performs all of the steps illustrated in Figure 15 through hardware.

for example, in a memory-to-I/O transfer, the starting address in memory and the length of the block to be transferred are written to the DMA by the CPU before to the transfer. The DMAC begins transferring data when the CPU enables the DMAC and the Ready line I/O of the device becomes active. In most cases, the CPU is idle during a DMA transfer. When the transfer is complete, the DMAC signals the CPU and releases control.

UM008101-0601

DMACs are used when one or more of the following situations or requirements are present:

- CPU has too much I/O and cannot perform other tasks properly

- Data transfer must be faster than the CPU can perform

- Transfer response tune (startup) must be faster than the CPU can provide

Small and low-performance systems generally run without DMA. Medium-performance systems can also be designed without DMA if the CPU can handle transfers fast enough and still perform other operations.

When systems require fast transfers or fast response, DMACs are strong candidates for performance enhancement. Not only do DMACs transfer faster than most CPUs, but the response time is better. Response times can even be improved using the techniques described above for CPU response.

The following examples are cases in which DMA is usually the best choice:

- Disk and diskette controllers

- Scanning operations, such as CRT I/O

- Data acquisition

- Memory-to-memory transfers

- Memory searches

- Backup storage (I/O-to-I/O)

- Parallel bus systems such as the IEEE 488

- Fiber optic links

- Block transfers in networking, multiprocessing, or multiprogramming

The trade-off for speed is that the CPU typically remains idle and lacks full or partial control of the system bus while the DMA is operating. This condition can affect total system throughput, and can also affect such things as memory refresh and other interrupts.

#### **DMA Characteristics**