## P33PCT825A/B BUS INTERFACE REGISTER

ADVANCE INFORMATION

T-52-09

#### **FEATURES**

- 3.3V ±0.2V Power Supply

- Center Power and Ground Pins

- **■** Full CMOS Implementation

- **Low Ground Bounce**

- Fully TTL Compatible Input and Output Levels

- High Speed Parallel Registers with positive edge-triggered D-type Flip-Flops

- Buffered Common Clock Enable (EN) and Asynchronous Clear Input (CLR)

- I<sub>oL</sub> = 48mA (Commercial) and 32mA (Military)

- Clamp Diodes on all inputs for Ringing Suppression

- **Compact Pinout**

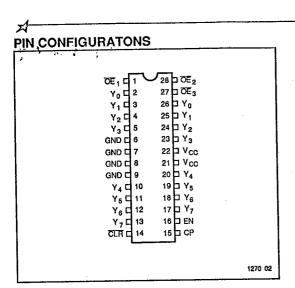

- 28-Pin 300 mil DIP, SOIC

#### **DESCRIPTION**

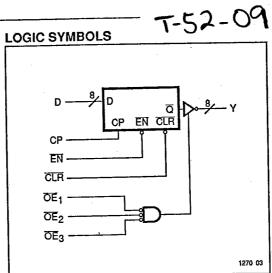

The P33PCT825 bus interface registers are designed to eliminate the extra packages required to buffer existing registers and provide extra data width for wider address/data paths or buses carrying parity. The P33PCT825 is a 8-bit buffered register with Clock Enable ( $\overline{\text{EN}}$ ) and Clear ( $\overline{\text{CLR}}$ ) controls plus multiple enables ( $\overline{\text{OE}}_1$ ,  $\overline{\text{OE}}_2$ ,  $\overline{\text{OE}}_3$ ) to allow multiuser control of the interface, e.g.,  $\overline{\text{CS}}$ ,  $\overline{\text{DMA}}$  and RD/ $\overline{\text{WR}}$ . It is ideal for use as an output port requiring high  $I_{\text{OL}}/I_{\text{OH}}$ .

The P33PCT825 is designed for high-capacitance load drive capability, while providing low-capacitance bus loading at both inputs and outputs. All inputs have clamp diodes and all outputs are designed for low-capacitance bus loading in the high impedance state.

The P33PCT825 is manufactured with PACE III Technology™ which is Performance Advanced CMOS Engineered with two-level metal and epitaxial substrates to use 0.4 micron effective channel lengths giving 250 picosecond loaded⁺ internal gate delays. The nominal supply voltage is reduced from the conventional 5.0V to 3.3V, thus reducing output swings dramatically. This, together with the (lower inductance) center power and ground pins, and the extra power and extra ground pins, significantly reduces noise and ground bounce that would otherwise occur for very high speed circuitry.

\*For a fan-in/fan-out of 4, at 85°C junction temperature and 3.3V supply.

# 7

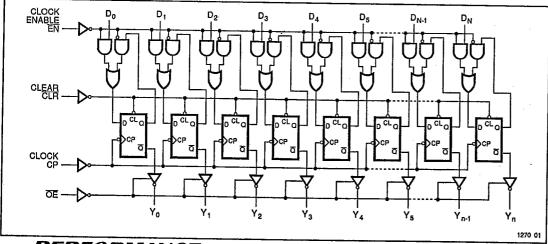

### **FUNCTIONAL BLOCK DIAGRAM**

PERFORMANCE

SEMICONDUCTOR CORPORATION

Means Quality, Service and Speed

©1989 Performance Semiconductor Corporation

TECHDOC 1270