# Preliminary Data Sheet December 2000

## microelectronics group

# TLMA0110G 10 Gbits/s Limiting Amplifier

#### **Features**

- 8 mV typical input sensitivity, BER ≤ 10<sup>-10</sup>

- 32 dB gain, 38 dB differential

- Complementary 50 Ω I/Os

- Adjustable threshold control

- Single –5.2 V power supply

- 24-lead surface-mount package

#### **Applications**

- Data/clock main amplifier in SONET/SDH OC-192/ STM-64 transmission systems and DWDM systems

- Digital video transmission

- SONET/SDH test equipment

#### **Functional Description**

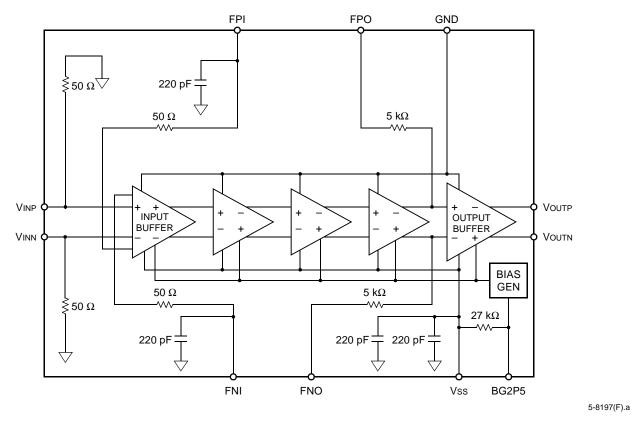

The Lucent Technologies Microelectronics Group TLMA0110G is a wideband limiting amplifier with differential inputs and outputs. It provides 32dB of gain (38 dB differential) and 9 GHz of bandwidth in a 50  $\Omega$ environment. The TLMA0110G consists of a 50  $\Omega$ input buffer followed by three gain stages and a 50  $\Omega$ output buffer. The threshold level can be adjusted by inserting an external voltage source into the amplifier's positive or negative feedback loops. At input levels below 20 mVp-p (single-ended), the device acts as a linear amplifier. For input levels from 20 mVp-p up to 800 mVp-p, the device operates in its limiting mode, providing a constant typical output of 550 mVp-p (single-ended).

The TLMA0110G is designed for use in SONET OC-192 and SDH STM-64 receiver/regenerator applications. Amplifier operation is from a single –5.2 V power supply. The TLMA0110G is available in a 24-lead, hermetic, surface-mount package.

## Functional Description (continued)

Figure 1. Block Diagram

#### **Pin Information**

5-8198(F)r.5

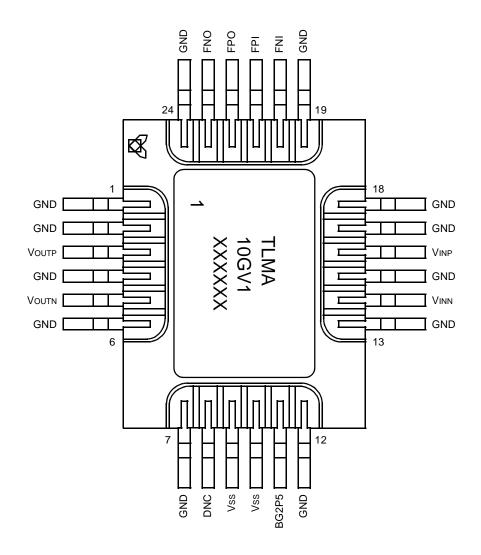

Figure 2. Package Pinout (Top View)

Lucent Technologies Inc.

#### Pin Information (continued)

#### Table 1. Pin Descriptions

| Symbol | Pin                    | Description                                                          |  |

|--------|------------------------|----------------------------------------------------------------------|--|

| GND    | 1, 2, 4, 6, 7, 12, 13, | Ground. For optimal performance, the package bottom must be soldered |  |

|        | 15, 17, 18, 19, 24,    | to the ground plane.                                                 |  |

|        | Package Bottom         |                                                                      |  |

| Voutp  | 3                      | Data Output. ac couple for optimal performance.                      |  |

| Voutn  | 5                      | Complementary Data Output. ac couple for optimal performance.        |  |

| DNC    | 8                      | Do Not Connect. Reserved for testing or future use.                  |  |

| Vss    | 9, 10                  | Power Supply Voltage. –5.2 V dc nominal supply voltage.              |  |

| BG2P5  | 11                     | -2.5 V Bandgap Reference. Connect to Si bandgap reference, such as   |  |

|        |                        | <i>National Semiconductor</i> <sup>*</sup> part number LM4040.       |  |

| Vinn   | 14                     | Complementary Data Input. (ac coupling required.)                    |  |

| Vinp   | 16                     | Data Input. (ac coupling required.)                                  |  |

| FNI    | 20                     | Feedback Negative Input. Threshold level control.                    |  |

| FPI    | 21                     | Feedback Positive Input. Threshold level control.                    |  |

| FPO    | 22                     | Feedback Positive Output. Threshold level control.                   |  |

| FNO    | 23                     | Feedback Negative Output. Threshold level control.                   |  |

\* National Semiconductor is a registered trademark of National Semiconductor Corporation.

Nodes FPI, FPO, FNI, and FNO complete the positive and negative internal feedback loops that are used to control the threshold level. FPI should be shorted to FPO, and FNI should be shorted to FNO. This configuration will center the threshold level. The threshold level can be shifted by forcing a change in voltage on either side of the feedback loop using a voltage source.

#### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| TCASE = 25 °C unless | otherwise specified. |

|----------------------|----------------------|

|----------------------|----------------------|

| Parameter                 | Symbol | Min | Max | Unit |

|---------------------------|--------|-----|-----|------|

| Supply Voltage            | Vss    | -7  | 0.5 | V    |

| Input Voltage             | Vin    | GND | Vss | V    |

| Power Dissipation         | Pd     |     | 1.0 | W    |

| Storage Temperature Range | Tstg   | -40 | 125 | °C   |

| Case Temperature Range    | TCASE  | 0   | 100 | °C   |

#### **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used in the defined model. No industry-wide standard has been adopted for the CDM. However, a standard HBM (resistance =  $1500 \Omega$ , capacitance = 100 pF) is widely accepted and, therefore, can be used for comparison purposes:

| Device    | Voltage |  |

|-----------|---------|--|

| TLMA0110G | ≥75 V   |  |

#### **Operating Conditions**

#### **Table 2. Recommended Operating Conditions**

| Parameter                        | Symbol | Min   | Max  | Unit |

|----------------------------------|--------|-------|------|------|

| Power Supply Voltage             | Vss    | -4.75 | -5.5 | V    |

| Operating Case Temperature Range | TCASE  | 0     | 70   | °C   |

### **Electrical Characteristics**

#### **Table 3. Limiting Amplifier Characteristics**

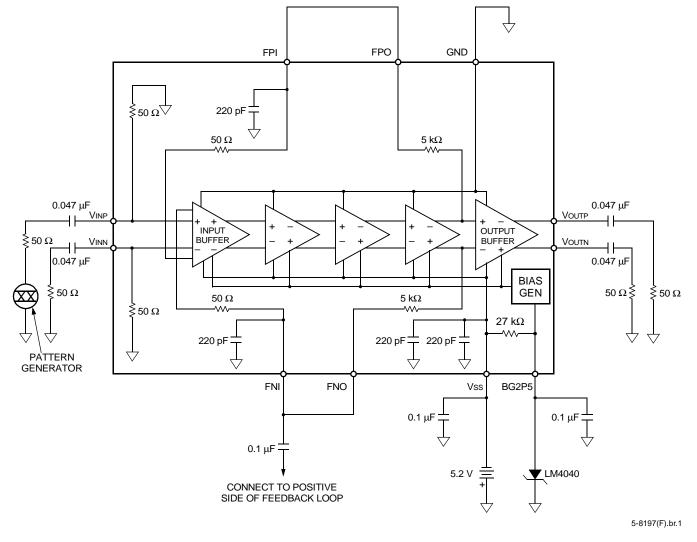

TCASE = 25 °C, VSS = -5.2 V, and RLOAD = 50  $\Omega$ . Inputs and outputs are ac-coupled and tested as shown in Figure 3. Bit rate = 9953.28 Mbits/s NRZ and data pattern =  $2^{31}$  - 1 PRBS, unless otherwise indicated. Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements.

| Parameter              | Symbol | Conditions                        | Min | Тур | Max  | Unit  |

|------------------------|--------|-----------------------------------|-----|-----|------|-------|

| Input Sensitivity      | Sen    | Single-ended, BER $\leq 10^{-10}$ | —   | 8   | _    | mVp-p |

| Maximum Input Voltage  | Vin    | Single-ended                      | —   | _   | 800  | mVp-p |

|                        |        | Differential                      | —   | _   | 1600 | mVp-p |

| Output Voltage         | Vout   | Single-ended,<br>Vın ≥ 30 mVp-p   | 400 | 550 | 700  | mVp-p |

| Eye Crossing           |        | 30 mVp-p ≤ VıN<br>< 100 mVp-p     | 35  | 50  | 65   | %     |

|                        |        | 100 mVp-p ≤ VIN<br>≤ 800 mVp-p    | 40  | 50  | 60   | %     |

| Rise/Fall Time 20%—80% | tR, tF | VIN = 100 mVp-p                   | —   | 20  | 35   | ps    |

| Jitter (rms)           | —      | VIN = 100 mVp-p                   | —   | 2   | 3    | ps    |

| Small Signal Gain      | G      | Single-ended,<br>Pın = −35 dBm    | —   | 32  | —    | dB    |

| Small Signal Bandwidth | f3dB   | PIN = −35 dBm                     | —   | 9   | —    | GHz   |

| Input Return Loss      | S11    | 50 MHz—7.5 GHz                    | 8   | 10  | —    | dB    |

| Output Return Loss     | S22    | 50 MHz—7.5 GHz                    | 8   | 10  |      | dB    |

| Supply Current         | lss    | Vss = -5.2 V                      | —   | 145 | 170  | mA    |

Note: Input return loss and output return loss are guaranteed by design or characterization and not production tested.

## **Test Circuit**

Figure 3. Test Circuit

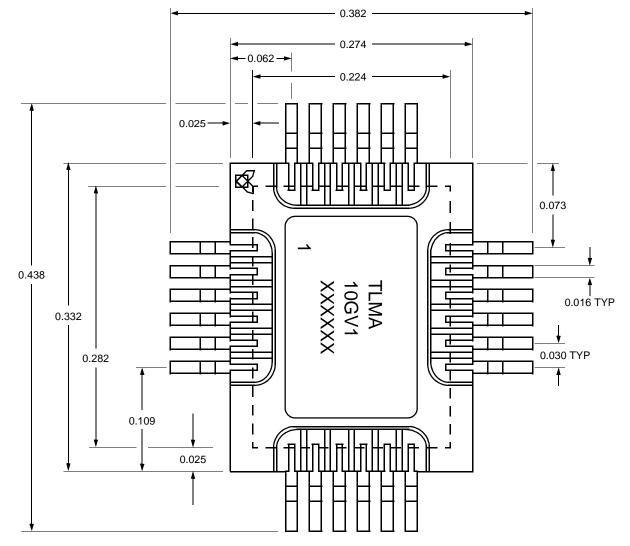

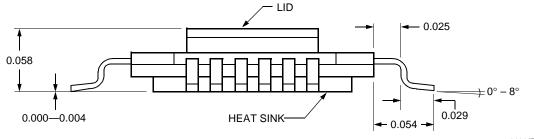

## **Outline Diagram**

#### 24-Pin, Surface-Mount Package (Top, Side Views)

Dimensions are in inches.

5-8199(F).ar.2

## **Ordering Information**

| Device    | Туре           | Comcode   |

|-----------|----------------|-----------|

| TLMA0110G | 24-Pin Package | 108499369 |

For additional information, contact your Microelectronics Group Account Manager or the following: INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106) ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495 CHINA: Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai 200233 P. R. China Tel. (86) 21 6440 0468, ext. 325, FAX (86) 21 6440 0652 JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 Data Requests: MICROELECTRONICS GROUP DATALINE: **Tel. (44) 7000 582 368**, FAX (44) 1189 328 148 Technical Inquiries: GERMANY: **(49) 89 95086 0** (Munich), UNITED KINGDOM: **(44) 1344 865 900** (Ascot), FRANCE: **(33) 1 40 83 68 00** (Paris), SWEDEN: **(46) 8 594 607 00** (Stockholm), FINLAND: **(358) 9 3507670** (Helsinki), EUROPE: ITALY: (39) 2 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information. This device is manufactured in qualified Lucent facilities—Lucent reserves the right to change qualified locations of manufacture.

Copyright  $\ensuremath{\textcircled{C}}$  2000 Lucent Technologies Inc. All Rights Reserved

December 2000 DS00-182HSPL (Replaces DS99-312HSPL) microelectronics group

Lucent Technologies

Bell Labs Innovat