#### PAC107 SINGLE-CHIP CMOS QQVGA IMAGE SENSOR with EMBEDDED TWIN-TURBO 8032 MICRO-PROCESSOR

#### **General Description**

The PAC107 is a QQVGA CMOS imager sensor with an embedded 40Mhz Twin-Turbo 8032 Micro Control Unit (MCU). To have excellent application flexibility, the PAC107 controls the embedded CMOS imager through 8032's SFR. A one-cycle execution multiplier is available for instruction "MUL". It's suitable for recognition applications.

The PAC107 had on-chip 16KB program ROM and 1KB on-chip SRAM. There are two 8-bit PWM ports with pre-scale function. Hence melody play and simple board level control function can be implemented. A dedicate image data write to External SRAM sequence is provided to have a fast and efficient image data caption through Port0 of 8032. The exposure-time control of imager can be done by on-chip real time hardware control, and extend the operation luminance range through firmware.

#### Features

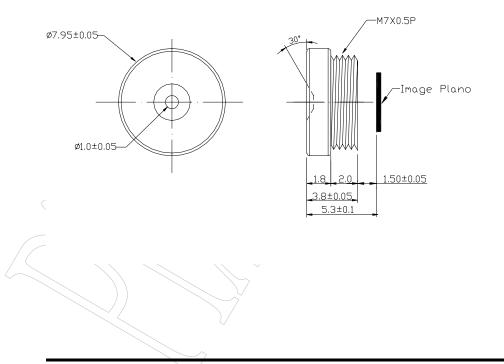

| 164x124 pixels, 1/11" Lens                 | RISC-like Twin-turbo 8032              |

|--------------------------------------------|----------------------------------------|

| Auto/Manual exposure-gain control.         | 2 UART with programmable baud-rate     |

| Automatic de-flicker                       | 2 PWM                                  |

| Firmware controlled imager power down      | 1 cycle execution MUL instruction      |

| On-chip 10-bit ADC                         | Software controllable Sensor shut down |

| Continuous variable exposure time          | MOVX direct dump image data to SRAM    |

| Continuous variable frame time(1/2s~1/30s) | 1KB on-chip SRAM                       |

| Crystal mode: 4~40 MHz                     | 16KB on-chip program ROM               |

| Operating voltage: 2.6V ~ 3.6V             | External program ROM bus supported     |

|                                            |                                        |

| <b>Power Supply</b>   | 2.6V ~ 3.6V      | FPN                 | < 0.2% saturation |

|-----------------------|------------------|---------------------|-------------------|

| Array Elements        | 164 x 124        | PGA Gain            | 16X (24dB)        |

| <b>Optical Format</b> | 1/11 "           | <b>Digital Gain</b> | 4X(12dB)          |

| Pixel Size            | 7.25 μm x 7.25μm | Frame Rate          | 60fps             |

| Master Clock          | Up to 40MHz      | Scan Mode           | Progressive       |

|                       |                  |                     | 80-pin LCC and    |

| Max. Pixel Rate       | 1.5MHz           | Package             | 48-pin LCC        |

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission. **PixArt Imaging Inc.**

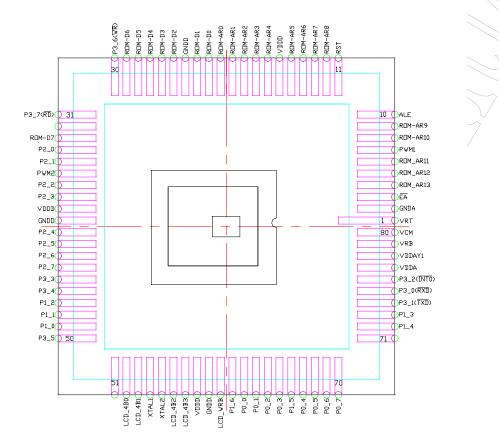

# 1. Pin Description

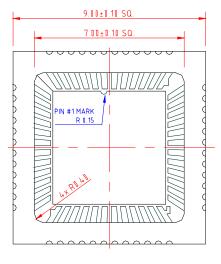

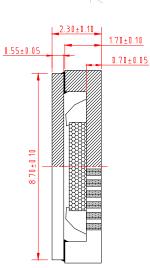

# 1.1 80-pin LCC

| Pin No. | Name              | Туре     | Definition                                       |

|---------|-------------------|----------|--------------------------------------------------|

| 1       | VRT               | Bypass   | Top-voltage reference for analog circuit         |

| 2       | GNDA              | G        | Analog ground                                    |

| 3       | /EA               | Ι        | Enable bar of external ROM, "1" for internal ROM |

| 4       | ROM_AR13          | 0        | Address for external ROM, bit 13                 |

| 5       | ROM_AR12          | 0        | Address for external ROM, bit 12                 |

| 6       | ROM_AR11          | 0        | Address for external ROM, bit 11                 |

| 7       | PWM1              | 0        | 8032, Programmable Pulse-width-modulation output |

| 8       | ROM_AR10          | 0        | Address for external ROM, bit 10                 |

| 9       | ROM_AR9           | 0        | Address for external ROM, bit 9                  |

| 10      | ALE               | 0        | Address latch pulse for SRAM-address             |

| 11      | RST               | Ι        | Chip reset                                       |

| 12      | ROM_AR8           | 0        | Address for external ROM, bit 8                  |

| 13      | ROM_AR7           | 0        | Address for external ROM, bit 7                  |

| 14      | ROM_AR6           | 0        | Address for external ROM, bit 6                  |

| 15      | ROM_AR5           | 0        | Address for external ROM, bit 5                  |

| 16      | VDDD <sub>N</sub> | Р        | Digital power                                    |

| 17      | ROM_AR4           | <b>O</b> | Address for external ROM, bit 4                  |

| 18      | ROM_AR3           | 0        | Address for external ROM, bit 3                  |

| 19      | ROM_AR2           | 0        | Address for external ROM, bit 2                  |

| 20      | ROM_AR1           | 0        | Address for external ROM, bit 1                  |

| 21      | ROM_AR0           | 0        | Address for external ROM, bit 0                  |

| 22      | ROM_D0            | I        | Data from external ROM, bit 0                    |

| 23      | ROM_D1            | I        | Data from external ROM, bit 1                    |

| 24      | GNDD              | G        | Digital ground                                   |

| 25      | ROM_D2            | I        | Data from external ROM, bit 2                    |

| 26      | ROM_D3            | I        | Data from external ROM, bit 3                    |

| 27      | ROM_D4            | I        | Data from external ROM, bit 4                    |

| 28      | ROM_D5            | J.       | Data from external ROM, bit 5                    |

| 29      | ROM_D6            | I        | Data from external ROM, bit 6                    |

| 30      | P3_6(/WR)         | 0        | 8032, P3_6 (/WR) – Write pulse of SRAM           |

| 31      | P3_7(/RD)         | 0        | 8032, P3_7 (/RD) – Read pulse of SRAM            |

| 32 /    | NC                | NC       | Not connected                                    |

| 33 🤇    | ROM_D7            | Ţ        | Data from external ROM, bit 7                    |

| _34     | P2_0              | IO       | 8032, P2_0                                       |

| 35      | P2_1              | Ю        | 8032, P2_1                                       |

| 36      | PWM2              | Ο        | 8032, Programmable Pulse-width-modulation output |

| 37      | P2_2              | ΙΟ       | 8032, P2_2                                       |

| 38      | P2_3              | Ю        | 8032, P2_3                                       |

| 39      | VDDD              | Р        | Digital power                                    |

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission. **PixArt Imaging Inc.**

|   |      | I           | 1      |                                                  |

|---|------|-------------|--------|--------------------------------------------------|

|   | 40   | GNDD        | G      | Digital ground                                   |

|   | 41   | P2_4        | ΙΟ     | 8032, P2_4                                       |

|   | 42   | P2_5        | ΙΟ     | 8032, P2_5                                       |

|   | 43   | P2_6        | ΙΟ     | 8032, P2_6                                       |

|   | 44   | P2_7        | ΙΟ     | 8032, P2_7                                       |

|   | 45   | P3_3(/INT1) | ΙΟ     | 8032, P3_3                                       |

|   | 46   | P3_4(T0)    | ΙΟ     | 8032, P3_4                                       |

|   | 47   | P1_2(/RXD1) | ΙΟ     | 8032, P1_2(/RXD1) – UART1 Rxd                    |

|   | 48   | P1_1(T2EX)  | ΙΟ     | 8032, P1_1                                       |

|   | 49   | P1_0(T2)    | ΙΟ     | 8032, P1_0                                       |

|   | 50   | P3_5(T1)    | IO     | 8032, P3_5                                       |

|   | 51   | NC          | NC     | Not connected                                    |

|   | 52   | LCD_4B0     | 0      | Specific data pin connect to color LCM           |

|   | 53   | LCD_4B1     | 0      | Specific data pin connect to color LCM           |

|   | 54   | XTAL1       | Clock  | Differential input of Crystal Oscillator         |

|   | 55   | XTAL2       | Clock  | Differential output of Crystal Oscillator        |

|   | 56   | LCD_4B2     | 0      | Specific data pin connect to color LCM           |

|   | 57   | LCD_4B3     | 0      | Specific data pin connect to color LCM           |

|   | 58   | VDDD        | Р      | Digital power                                    |

|   | 59   | GNDD        | G      | Digital ground                                   |

|   | 60   | LCD_WRB     | 0      | Specific write pulse pin connect to color LCM    |

|   | 61   | P1_6        | ΙΟ     | 8032, P1_6                                       |

|   | 62   | P0_0        | IO     | 8032, P0_0                                       |

|   | 63   | P0_1        | ΙΟ     | 8032, P0_1                                       |

|   | 64   | P0_2        | ΙΟ     | 8032, P0_2                                       |

|   | 65   | P0_3        | ΙΟ     | 8032, P0_3                                       |

|   | 66   | P1_5        | 10     | 8032, P1_5                                       |

|   | 67   | P0_4        | ΙΟ     | 8032, P0_4                                       |

|   | 68   | P0_5        | ΙΟ     | 8032, P0_5                                       |

|   | 69   | P0_6        | ΙΟ     | 8032, P0_6                                       |

|   | 70   | P0_7        | IO     | 8032, P0_7                                       |

|   | 71   | NC          | NC     | Not connected                                    |

|   | 72   | P1_4        | 10     | 8032, P1_4                                       |

|   | 73   | P1_3(/TXD1) | ΙΟ     | 8032, P1_3(/TXD1) – UART1 Txd                    |

|   | 74   | P3_1(/TXD0) | 10     | 8032, P3_1(/TXD0) – UART0 Txd                    |

|   | 75   | P3_0(/RXD0) | ΙΟ     | 8032, P3_0(/RXD0) – UART0 Rxd                    |

|   | 76 🔿 | P3_2(/INT0) | I      | P3_2(/INT0) – INT0 to ASIC                       |

|   | 77 🦾 | VDDA        | -P     | Analog power                                     |

|   | 78   | VDDAY1      | Bypass | Sensor power                                     |

| ~ | 79   | VRB         | Bypass | Bottom-voltage reference for analog circuit      |

|   | 80   | VCM         | Bypass | Common-mode-voltage reference for analog circuit |

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission. **PixArt Imaging Inc.** V1.4, Aug, 2005

3

E-mail: fae service@pixart.com.tw

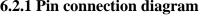

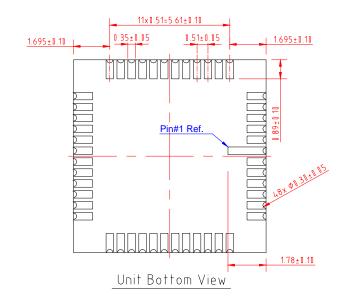

# 1.2 48-pin LCC

| in No. | Name         | Туре   | Definition                                       |

|--------|--------------|--------|--------------------------------------------------|

|        |              |        |                                                  |

| 1      | VDDA         | P      | Analog power                                     |

| 2      | VDDAY1       | Bypass | Sensor power                                     |

| 3      | VRB          | Bypass | Bottom-voltage reference for analog circuit      |

| 4      | VCM          | Bypass | Common-mode-voltage reference for analog circuit |

| 5      | VRT          | Bypass | Top-voltage reference for analog circuit         |

| 6      | GNDA         | G      | Analog ground                                    |

| 7      | /EA          | I      | Enable bar of external ROM, "1" for internal ROM |

| 8      | NC           | NC     | Not connected                                    |

| 9      | NC           | NC     | Not connected                                    |

| 10     | ALE          | 0 (    | Address latch pulse for SRAM-address             |

| 11     | RST          | I      | Chip reset                                       |

| 12     | VDDD         | Р      | Digital power                                    |

| 13     | NC           | NC     | Not connected                                    |

| 14     | NC           | NC     | Not connected                                    |

| 15     | GNDD         | G      | Digital ground                                   |

| 16     | P3_6 (/WR)   | Ο      | 8032, P3_6 (/WR) – Write pulse of SRAM           |

| 17     | P3_7 (/RD)   | 0      | 8032, P3_7 (/RD) – Read pulse of SRAM            |

| 18     | P2_0         | IO     | 8032, P2_0                                       |

| 19     | P2_1         | IO     | 8032, P2_1                                       |

| 20     | PWM2         | 0      | 8032, Programmable Pulse-width-modulation output |

| 21     | P2_2         | ΙΟ     | 8032, P2_2                                       |

| 22     | P2_3         | 10     | 8032, P2_3                                       |

| 23     | P2_4         | IO     | 8032, P2_4                                       |

| 24     | P2_5         | ΙΟ     | 8032, P2_5                                       |

| 25     | <br>P2_6     | ΙΟ     | 8032, P2_6                                       |

| 26     | <br>P2_7     | 01     | 8032, P2_7                                       |

| 27     | P1_2         | ΙΟ     | 8032, P1_2                                       |

| 28     | <br>P1_1     | 10     | 8032, P1_1                                       |

| 29     | P1_0         | 10     | 8032, P1_0                                       |

| 30     | <br>P3_5     | ΙΟ     | 8032, P3_5                                       |

| 31     | XTAL1        | Clock  | Differential input of Crystal Oscillator         |

| 32     | XTAL2        | Clock  | Differential input of Crystal Oscillator         |

| 33     | VDDD         | Р      | Digital power                                    |

| 34     | P1_6         | IO     | 8032, P1_6                                       |

| 35     | P0_0         |        | 8032, P0_0                                       |

| 36     | P0_1         |        | 8032, P0_1                                       |

| 37     | P0_1<br>P0_2 | IO     | 8032, P0_2                                       |

| 38     | P0_2<br>P0_3 | IO     | 8032, P0_2<br>8032, P0_3                         |

| 39     | P0_3<br>P0_4 | IO     | 8032, P0_5<br>8032, P0_4                         |

| 40     | P0_4<br>P0_5 | IO     | 8032, P0_4<br>8032, P0_5                         |

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission. **PixArt Imaging Inc.**

| 41 | P0_6        | IO | 8032, P0_6                  |

|----|-------------|----|-----------------------------|

| 42 | P0_7        | ΙΟ | 8032, P0_7                  |

| 43 | GNDD        | G  | Digital ground              |

| 44 | P1_4        | IO | 8032, P1_4                  |

| 45 | P1_3        | ΙΟ | 8032, P1_3                  |

| 46 | P3_1(/TXD)  | ΙΟ | 8032, P3_1(/TXD) – UART/Txd |

| 47 | P3_0(/RXD)  | ΙΟ | 8032, P3_0(/RXD) – UART Rxd |

| 48 | P3_2(/INT0) | Ι  | P3_2(/INT0) – INT0 to ASIC  |

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission.

PixArt Imaging Inc.

E-mail: <u>fae\_service@pixart.com.tw</u> V1.4,

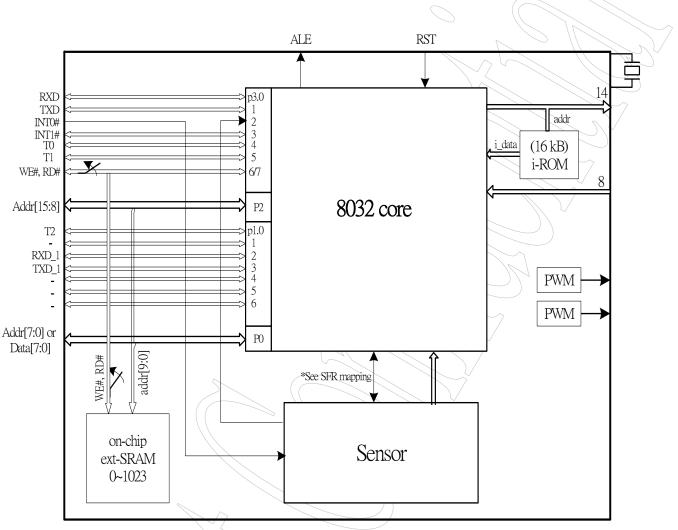

# 2. Block Diagram

# Fig 2.1 – Block diagram of PAC107

As the block diagram of PAC107 is shown in Figure 2.1. By pulling the CSB register in SFR(Special function register) to low, the 164x124 sensor starts to produce a signal according to the amount of the light integrated in pixels. The integrated analog signal will be readout and amplifier with ADC output in 8-bit. The output 8 bit digital sensor data then be received by 8051 core by software.

16KB program ROM and 1kB SRAM is provided in PAC107 and two PWM ports are supported.

| Address                                           | Name             | R/W Default |           | Recommended    | Description                               |  |

|---------------------------------------------------|------------------|-------------|-----------|----------------|-------------------------------------------|--|

| Reg_0[7:0]                                        | Pdct_id[11:4]    | R           | 0000_0001 | setting        | Product ID                                |  |

| $\frac{\text{Reg}_0[7:0]}{\text{Reg}_1[7:4]}$     | pdct_id[3:0]     | R           | 1001      |                | Product ID                                |  |

| $\frac{\text{Reg}_1[7:4]}{\text{Reg}_1[3:0]}$     | ver id[3:0]      | R           | 0000      | -              | Version ID                                |  |

| Reg_2[7:1]                                        | Ysum_report[6:0] | R           | -         | -              | Ysum report in AE/AG                      |  |

| -                                                 | s_valid          | R           | _         |                | calculation<br>Youm valid flag            |  |

| Reg_2[0]                                          | RSV              | К           | -         | $\frown$       |                                           |  |

| Reg_3[7]                                          | KSV              | -           | -         | - (            | Reserved<br>Frame wait for AE/AG          |  |

| Reg_3[6:0]                                        | AE_wait[6:0]     | R/W         | 000_0001  | 0              | calculation                               |  |

| Reg_4[7:4]                                        | Ysum_hi[3:0]     | R/W         | 1010      |                | Ysum high threshold                       |  |

| Reg_4[3:0]                                        | Ysum_lo[3:0]     | R/W         | 1000      | ((- /          | Ysum low threshold                        |  |

| Reg_5[7:6]                                        | AE_max[1:0]      | R/W         | 11        | -              | Maximum AE index in Auto mode             |  |

| Reg_5[5:1]                                        | AG_max[4:0]      | R/W         | 1_1111    | -              | Maximum Gain index in Auto mode           |  |

| Reg_5[0]                                          | dac[8]           | R/W         | 0         | -              | Sign bit of DAC                           |  |

| Reg_6[7:0]                                        | dac[7:0]         | R/W         | 0000_0000 |                | Magnitude of DAC                          |  |

| Reg_7[7]                                          | RSV              | -           | - //      | · · · · ·      | Reserved                                  |  |

| Reg_7[6:0]                                        | ny3[6:0]         | R/W         | 000_1011  | 0              | Raw exposure set #4 for AE                |  |

| Reg_8[7:0]                                        | ne3[7:0]         | R/W         | 0101_1000 | 0              | Fine exposure set #4 for AE               |  |

| Reg_9[7]                                          | RSV              | /           | - //      | $\bigcirc$     | Reserved                                  |  |

| Reg_9[6:0]                                        | ny2[6:0]         | R/W         | 010_1000  | 0              | Raw exposure set #3 for AE                |  |

| Reg_10[7:0]                                       | ne2[7:0]         | R/W         | 0000_1000 | 0              | Fine exposure set #3 for AE               |  |

| Reg_11[7]                                         | RSV              | -           | -         | $\overline{)}$ | Reserved                                  |  |

| Reg_11[6:0]                                       | ny1[6:0]         | R/W         | 100_0100  | 010_1011       | Raw exposure set #2 for AE                |  |

| Reg_12[7:0]                                       | ne1[7:0]         | R/W         | 1000_1101 | 0              | Fine exposure set #2 for AE               |  |

| Reg_13[7:6]                                       | RSV              |             |           | - ()           | Reserved                                  |  |

| Reg_13[5:0]                                       | np[5:0]          | R/W         | 00 0110   | 01_0000        | pxclk = sysclk / np                       |  |

| Reg_14[7:0]                                       | lpf[7:0]         | R/W         | 0111 1101 | 0111_1111      | Line per frame                            |  |

| Reg_15[7]                                         | adc8b            | R/W         |           | 1              | 1: ADC 8_bit valid<br>0: ADC 10_bit valid |  |

| Reg_15[6:4]                                       | comp[2:0]        | R/W         | 011       | _              | Companding curve selection                |  |

| Reg_15[3:2]                                       | cgn_B[1:0]       | R/W         | 10        | 11             | Color gain for Blue                       |  |

| Reg_15[1:0]                                       | cgn_R[1:0]       | R/W         | 10        | 01             | Color gain for Red                        |  |

| Reg_16[7:5]                                       | RSV              |             | -         |                | Reserved                                  |  |

| Reg_16[4:0]                                       | pga[4:0]         | R/W         | 0_0100    | _              | PGA global gain                           |  |

| $\frac{\text{Reg}_{10[10]}}{\text{Reg}_{17[7]}}$  | RSV              | -           | -         | _              | Reserved                                  |  |

| $Reg_{17[6:0]}$                                   | ny0[6:0]         | R/W         | 110_0001  | 101_0110       | Raw exposure set #1 for AE                |  |

| Reg_18[7:0]                                       | ne0[7:0]         | R/W         | 0100_0111 | 0              | Fine exposure set #1 for AE               |  |

| $Reg_{19[7:1]}$                                   | RSV              |             | -         | -              | Reserved                                  |  |

| Reg_19[0]                                         | flag             | R/W         | 0         | -              | Synchronization flag for I2C<br>update    |  |

| Reg_20[7:0]                                       | RSV              | _           | 1000_0000 | -              | Reserved                                  |  |

| Reg_21[7]                                         | Col_reverse      | R/W         | 0         | _              | Line readout reverse                      |  |

| $\frac{\text{Reg}_{21[7]}}{\text{Reg}_{21[6:5]}}$ | Pack[1:0]        | R/W         | 00        |                | 8, 4, 2, 1 bit packing selection          |  |

# 3. Register table of CMOS Image Sensor

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission. **PixArt Imaging Inc.**

| Toyt            | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Toy timing enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| aegenh          | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AE/AG enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Edge-gn[1:0]    | R/W                                                                                                                                                                                                  | 00                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Edge gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Vlrst_outh      | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External virst enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Shr_we2         | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CDS extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Intvddy         | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Internal array vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Intvref         | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Internal voltage reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cdsenh          | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CDS enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dacenh          | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DAC enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pgaenh          | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PGA enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Adcenh          | R/W                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ADC enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dqioenl         | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | - (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DQIO enable / tri-stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| vlrst_enh       | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vlrst enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Vr              | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | ) /L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Vref option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Vy              | R/W                                                                                                                                                                                                  | $\bigcirc 0$                                                                                                                                                                                                                                                                                                                                        | (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Array vdd option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Regfast[1:0]    | R/W                                                                                                                                                                                                  | 00                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fast mode for Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Cdsfast         | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | /- /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fast mode for CDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pgafast         | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fast mode for PGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Adcfast         | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Fast mode for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RSV             | R/W                                                                                                                                                                                                  | - </td <td> /</td> <td>Reserved</td>                                                                                                                                                                                                                                                                                                                | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Dacscan         | R/W                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DAC test mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pgascan         | R/W                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     | - //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PGA test mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |