# **AK2301**

## 3.3V シングルチャネル PCMコーデック LSI

#### 既 要

AK2301は、8kHzサンプリングの8bit単チャンネル PCMコーデックです。欧州を中心とする地域で用いられる**A-Law**圧伸則と北米・日本で用いられる $\mu$ -law 圧伸則とをピンで選択可能です。

帯域制限フィルタ、A/D及びD/A変換器、A-law/μ-law変換器を内蔵しており、実装スペース、 実装工数及び消費電力の削減に最適です。

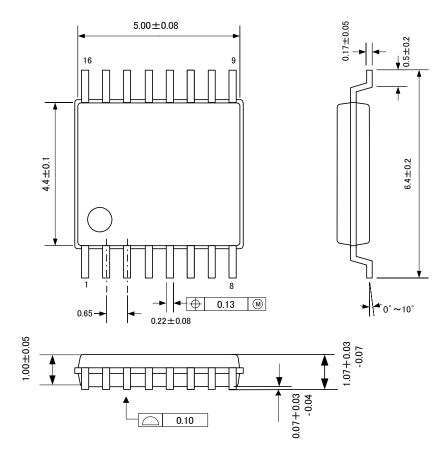

### パッケージ

- 16ピンTSSOPパッケージ

- ・ピン端 5.0\*6.4mm

- ・ピンピッチ 0.65mm

#### 特長

- 単チャンネル・PCMコーデック/フィルタ内蔵

- 設定可能な機能;

- ミュート

- ・ A-law, μ-lawの圧伸則選択

- PCMデータインタフェース LongFrame/ShortFrameに対応

- PCMデータ転送レート 64k\*N(N=1~32)Hz (64~2048kHz)

- パワーダウン (BCLK=L時)

- 入出力ゲイン調整用オペアンプ内蔵

- 差動にて600 Ωライン駆動可能

- +3.0~+3.6V単一電源

- 低消費電流

- 動作時 8mA(typ)

- ・ パワーダウン時 5uA(typ)

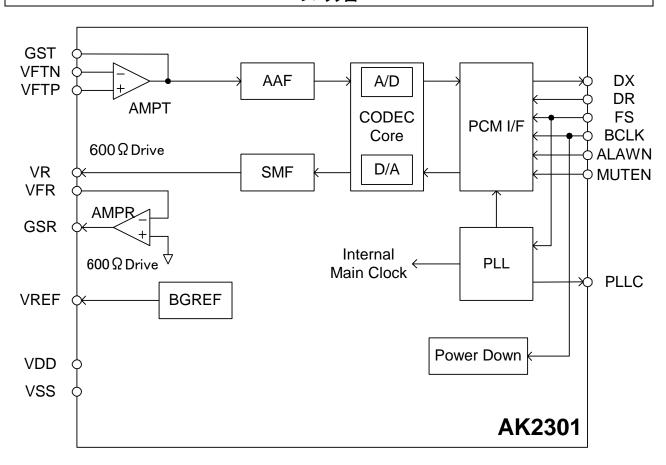

#### ブロック図

## 目 次

|   | 項目                   | 頁  |

|---|----------------------|----|

|   |                      |    |

| _ | ブロック図                | 1  |

| - | 端子条件                 | 3  |

| _ | 端子機能                 | 4  |

| - | 絶対最大定格               | 5  |

| _ | 推奨動作条件               | 5  |

| _ | 電気的特性                | 5  |

| _ | パッケージ外形寸法図           | 10 |

| _ | パッケージ・ピン配置           | 11 |

| - | マーキング仕様              | 11 |

| - | 回路構成                 | 12 |

| - | 機能説明                 | 13 |

| _ | PCMコーデック             | 13 |

| - | PCMインタフェース           | 13 |

| - | LongFrame/ShortFrame | 14 |

| - | ミュート・パワーダウン          | 15 |

| - | 電源起動時推奨動作手順          | 16 |

| - | 外付け推奨回路図(例)          | 17 |

## 端子条件

| 端子<br>番号 | 端子名   | I/O | 端子<br>タイプ | 最大<br>容量負荷 | 最小<br>抵抗負荷           | ミュート時出力状態        | パワーダウン<br>出力状態 | 備考                                 |

|----------|-------|-----|-----------|------------|----------------------|------------------|----------------|------------------------------------|

| 10       | VFTN  | I   | Analog    |            |                      |                  |                |                                    |

| 11       | VFTP  | I   | Analog    |            |                      |                  |                |                                    |

| 9        | GST   | 0   | Analog    | 50pF       | AC負荷(*1)<br>10kΩ(*2) |                  | Hi-Z           |                                    |

| 6        | GSR   | 0   | Analog    | 40pF       | AC負荷<br>600Ω(*2,*3)  |                  | Hi-Z           |                                    |

| 7        | VFR   | ı   | Analog    |            |                      |                  |                |                                    |

| 8        | VR    | 0   | Analog    | 40pF       | AC負荷<br>600Ω(*2,*3)  | Analog<br>ground | Hi-Z           |                                    |

| 5        | VDD   | -   |           |            |                      |                  |                |                                    |

| 13       | VSS   | -   |           |            |                      |                  |                |                                    |

| 4        | FS    | I   | CMOS      |            |                      |                  |                | オープン不可                             |

| 2        | BCLK  | I   | CMOS      |            |                      |                  |                | オープン不可                             |

| 1        | DX    | 0   | CMOS      | 50pF       |                      | Hi-Z             | Hi-Z           |                                    |

| 3        | DR    | -   | CMOS      |            |                      |                  |                | オープン不可                             |

| 16       | MUTEN | I   | CMOS      |            |                      |                  |                | オープン不可                             |

| 15       | ALAWN | I   | CMOS      |            |                      |                  |                | オープン不可                             |

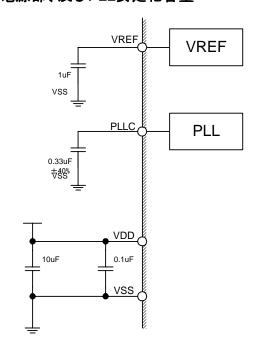

| 12       | VREF  | 0   | Analog    |            |                      |                  | VSS            | 外付容量<br>1.0uF以上                    |

| 14       | PLLC  | 0   | Analog    |            |                      |                  | VSS            | 外付容量<br>0.33uF±<br>40%(温度<br>特性込み) |

<sup>\*2)</sup>最小負荷抵抗は帰還抵抗込の値です。

<sup>\*3)</sup>差動の場合、GSRとVR間のAC負荷です。

[AK2301] ASAHI KASEI

## 端子機能

タイプの詳細

DIN: デジタルインプット TOUT: トライステートアウトプット PWR: 電源・グランド AIN: アナログインプット AOUT: アナログアウトプット

|      | ナログインブ                                  | ツト    | AOUT: アナログアウトブット                                             |

|------|-----------------------------------------|-------|--------------------------------------------------------------|

| 端子番号 | 端子名称                                    | タイプ   | 機能                                                           |

| 10   | VFTN                                    | AIN   | A/Dへの入力ゲイン調整用オペアンプの反転差動入力。                                   |

|      |                                         |       | VFTP端子と外部抵抗で、差動またはシングルエンド入力アンプを構成しゲ                          |

|      |                                         |       | イン調整を行います。                                                   |

| 11   | VFTP                                    | AIN   | A/Dへの入力ゲイン調整用オペアンプの正転差動入力。                                   |

|      |                                         |       | VFTN端子と外部抵抗で、差動またはシングルエンド入力アンプを構成しゲ                          |

|      |                                         |       | イン調整を行います。                                                   |

| 9    | GST                                     | AOUT  | A/D入力ゲイン調整用オペアンプの出力。                                         |

|      |                                         |       | 外部抵抗で差動入力アンプを構成しゲイン調整を行います。                                  |

| 6    | GSR                                     | AOUT  | D/A出力ゲイン調整用オペアンプの出力。                                         |

|      |                                         |       | 外部抵抗で反転アンプを構成しゲイン調整を行います。VR出力を使って作                           |

|      |                                         |       | 動出力を構成することも出来ます。                                             |

| 7    | VFR                                     | AIN   | D/A出力ゲイン調整用オペアンプの反転入力。                                       |

|      |                                         |       | 外部抵抗で反転アンプを構成しゲイン調整を行います。ただし入力ゲイン                            |

|      |                                         |       | オペアンプを差動アンプとして構成する場合、このオペアンプは差動アン                            |

|      |                                         |       | プのアナログGND用のバッファとして使用されます。この場合、このアンプ                          |

|      |                                         |       | を用いた出力ゲイン調整、および差動ドライブ回路構成は出来ません。                             |

| 8    | VR                                      | AOUT  | D/Aアナログ出力。                                                   |

|      |                                         |       | GSR出力を使って作動出力を構成することも出来ます。                                   |

| 5    | VDD                                     |       | 正電源端子。                                                       |

| 13   | VSS                                     |       | <b>負電源端子。</b>                                                |

| 4    | FS                                      | DIN   | PCMデータ送受同期信号入力。                                              |

|      |                                         |       | PCMデータ入出力タイミングを制御します。パワーダウン時を除き、BCLKと                        |

|      |                                         |       | 同期した8kHz の信号を常に入力してください。FSを停止する場合は、BCLK=L                    |

|      | 5011                                    | DIM   | として、AK2301をパワーダウンモードにして下さい。                                  |

| 2    | BCLK                                    | DIN   | PCMデータ転送レート制御クロック入力。                                         |

|      |                                         |       | BCLK=Lで、AK2301はパワーダウンします。通常動作時は、64k*N(N=1~32)Hz              |

| 1    | DX                                      | TOLIT | (64k~2048kHz) のクロックをduty40~60%で常に入力してください。                   |

| 1    | DX                                      | 1001  | <b>PCMデータ出力端子。</b><br>BCLKに同期してA/DされたPCMデータを出力します。この端子は送信データ |

|      |                                         |       | が存在する8ビット期間以外は、ハイインピーダンスとなります。                               |

|      |                                         | DIN   |                                                              |

| 3    | DR                                      |       | PCMデータの入力端子。                                                 |

| 1.6  | N41 175N                                |       | BCLKに同期してPCMデータを入力します。                                       |

| 16   | MUTEN                                   | DIN   | ミュート設定端子。                                                    |

| 1.5  | A 1 A 1 A 1 A 1 A 1 A 1 A 1 A 1 A 1 A 1 | DIN   | Lでミュートが起動されます。                                               |

| 15   | ALAWN                                   | DIN   | A/μ-law切替端子。<br>"" - " - " - " - " - " - " - " - " - "       |

| 12   | VREF                                    | AOLTT | " L" =A-law," H" =μ-law 通常使用時は、H or Lに固定してください。              |

| 12   | VKEF                                    | AUUI  | アナロググランド電源出力端子。                                              |

| 14   | DLLC                                    | AOUT  | 1.0 uF以上の容量を外付して下さい。                                         |

| 14   | PLLC                                    | AUUI  | <b>PLL用 容量接続端子。</b><br>0.33uF±40%(温度特性込み)の容量を外付して下さい。        |

|      |                                         |       | U. 33U「エチリル(値皮が注处か) 57 年をクトヤリ しし「さい。                         |

<MS0416-J-02> 2013/05 4

## 絶対最大定格

| パラメータ          | 記号   | min  | max     | 単位                     |

|----------------|------|------|---------|------------------------|

| 電源電圧           |      |      |         |                        |

| アナログ/デジタル電源    | VDD  | -0.3 | 4.6     | V                      |

| デジタル端子印加電圧     | VTD  | -0.3 | VDD+0.3 | V                      |

| アナログ端子印加電圧     | VTA  | -0.3 | VDD+0.3 | V                      |

| 入力電流 (電源ピンを除く) | IIN  | -10  | 10      | m A                    |

| 保存温度           | Tstg | -55  | 125     | $^{\circ}\!\mathbb{C}$ |

注) この値を超えた条件で使用した場合、デバイスを破壊することがあります。 またこの範囲内全てでの通常動作は保証されません。

## 推奨動作条件

| パラメータ            | 記号  | min   | typ | max   | 単位              |

|------------------|-----|-------|-----|-------|-----------------|

| 電源電圧 アナログ/デジタル電源 | VDD | 3.0   | 3.3 | 3.6   | V               |

| 動作温度範囲           | Ta  | -40   |     | 85    | $_{\mathbb{C}}$ |

| フレームシンク周波数*)     | FS  | -1.0% | 8   | +1.0% | kHz             |

注)電圧は全て接地端子基準: VSS=0V

#### 電気的特性

特記のない限り、規格値はVDD = +3.0 V~+3.6V、Ta = -40~+85°C、FS=8kHzにおいて保証されます。

### ■ DC特性

| 項目               | 記号       | 条件             | min    | typ | Max    | 単位      |

|------------------|----------|----------------|--------|-----|--------|---------|

| 消費電流             | IDD1(注1) | 出力端子はすべて無負荷    |        | 8   | 13     | mA      |

|                  | IDD2     | パワーダウン(BCLK=L) |        | 5   | 100    | $\mu$ A |

| デジタル高レベル<br>出力電圧 | Vон      | Iон=-1.6mA     | 0.8VDD |     |        | V       |

| デジタル低レベル<br>出力電圧 | Vol      | IoL=1.6mA      |        |     | 0.4    | V       |

| デジタル高レベル<br>入力電圧 | VIH      |                | 0.7VDD |     |        | V       |

| デジタル低レベル<br>入力電圧 | VIL      |                |        |     | 0.3VDD | V       |

| 入力漏洩電流           | ILL      |                | -10    |     | +10    | $\mu$ A |

| 出力漏洩電流           | ILT      | トライステート時       | -10    |     | +10    | $\mu$ A |

| アナロググランド<br>出力電圧 | VRG      | 上型フル人で何なせ      | 1.4    | 1.5 | 1.6    | V       |

<sup>(</sup>注1) 測定条件: BCLK=2.048MHz、出力端子は全て無負荷。

VFTN,VFTP(差動入力)より1020Hz@0dBm0入力、DRより1020Hz@0dBm0 Codeを入力。

<sup>\*)</sup>CODECの諸特性は8kHzでの定義となります。

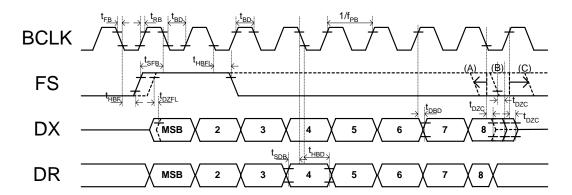

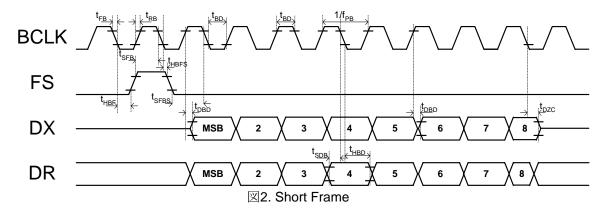

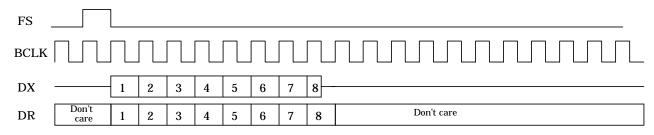

## **◆**PCMインタフェース (Long Frame, Short Frame)

特記なき場合、Ta=-40 to +85°C, VDD=3.0~3.6V, VSS=0V, FS=8kHzにおいての定義となります。全ての出力ピンのタイミングパラメータはVOH=0.8VDD及びVOL=0.4Vにて測定されます。全ての入力ピンのタイミングパラメーターはVIH=0.7VDD及びVIL=0.3VDDにて測定されます。

### ■AC特性

| パラメータ                                                                                              | 記号                | Min   | Тур                            | Max   | 単位   | 参照図   |

|----------------------------------------------------------------------------------------------------|-------------------|-------|--------------------------------|-------|------|-------|

| FS Frequency                                                                                       | f <sub>PF</sub>   | -1.0% | 8                              | +1.0% | kHz  |       |

| BCLK Frequency                                                                                     | f <sub>PB</sub>   | -     | $f_{PF} \times 8N$<br>(N=1~32) | -     | kHz  |       |

| BCLK Duty Cycle                                                                                    | t <sub>WB</sub>   | 40    |                                | 60    | %    |       |

| Rising/Falling Time: (BCLK,FS, DX,DR)                                                              | t <sub>RB</sub>   |       |                                | 40    | ns   |       |

| Hold Time: BCLK Low to FS High                                                                     | t <sub>HBF</sub>  | 60    |                                |       | ns   | 図1, 2 |

| Setup Time: FS High to BCLK Low                                                                    | t <sub>SFB</sub>  | 60    |                                |       | ns   | ⊠1, 2 |

| Setup Time: DR to BCLK Low                                                                         | t <sub>SDB</sub>  | 60    |                                |       | ns   |       |

| Hold Time: BCLK Low to DR                                                                          | t <sub>HBD</sub>  | 60    |                                |       | ns   |       |

| Delay Time: BCLK High to DX valid 注1)                                                              | t <sub>DBD</sub>  | 0     |                                | 60    | ns   |       |

| Delay Time: (A) BCLK Low to DX High-Z or (B) FS Low to DX High-Z or (C) BCLK High to DX High-Z 注1) | t <sub>DZC</sub>  | 0     |                                | 60    | ns   |       |

| Long Frame                                                                                         |                   |       |                                |       |      |       |

| Hold Time: 2 <sup>nd</sup> period of BCLK Low to FS Low                                            | t <sub>HBFL</sub> | 60    |                                |       | ns   |       |

| Delay Time: FS or BCLK High, whichever is later,to DX valid 注1)                                    | t <sub>DZFL</sub> |       |                                | 60    | ns   | 図1    |

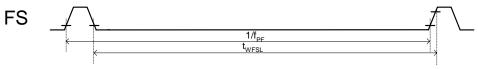

| FS Pulse Width Low                                                                                 | t <sub>WFSL</sub> | 1     |                                |       | BCLK |       |

| Short Frame                                                                                        |                   |       |                                |       |      |       |

| Hold Time: BCLK Low to FS Low                                                                      | t <sub>HBFS</sub> | 60    |                                |       | ns   | 図2    |

| Setup Time: FS Low to BCLK Low                                                                     | t <sub>SFBS</sub> | 60    |                                |       | ns   |       |

<sup>(</sup>注1) 50pFの負荷容量、及び0.2mA駆動

## Interface Timing

図1. Long Frame

## **♦**CODEC

## \*送受信用オペアンプのゲインはOdB設定にて測定しています。

\*FSが8kHzからずれた場合の諸周波数特性は 使用FS 8k[Hz] ×測定条件周波数 = 実効周波数 で読み替えて下さい。

### ■絶対ゲイン特性

| 項 目       |               | 測定条件                 | min  | typ   | max | 単位   |

|-----------|---------------|----------------------|------|-------|-----|------|

| アナログ入力レベル | VFTP,VFTN     | 0dBm0@1020Hz 入力      |      | 0.531 |     | Vrms |

| 絶対入力ゲイン   | (差動) →        | odbinoe rozoriz /(/) | -0.6 | _     | 0.6 | dB   |

| 絶対入力レベル   | DX (*1)       | 3.14dBm0入力           |      | 0.762 |     | Vrms |

| アナログ出力レベル | DR            | 0dBm0@1020Hz 入力      |      | 0.531 |     | Vrms |

| 絶対出力ゲイン   | $\rightarrow$ | Oubline 102011Z /(/) | -0.6 | _     | 0.6 | dB   |

| 最大入出力レベル  | VR            | 3.14dBm0相当值          |      | 0.762 |     | Vrms |

<sup>(\*1)</sup>差動で0dBm0=0.531Vrms

## ■伝送レベル特性

| 項 目                 | 測定条件        |                 | min  | typ | max | 単位 |

|---------------------|-------------|-----------------|------|-----|-----|----|

| 送信伝送レベル特性           | 基準レベル:      | -55dBm0∼-50dBm0 | -1.2 |     | 1.2 |    |

| $(A \rightarrow D)$ | -10dBm0     | -50dBm0∼-40dBm0 | -0.4 | _   | 0.4 | dB |

| VFTP,VFTN → DX      | 1020Hz Tone | -40dBm0∼ 3dBm0  | -0.2 | _   | 0.2 |    |

| 受信伝送レベル特性           | 基準レベル:      | -55dBm0∼-50dBm0 | -1.2 | 1   | 1.2 |    |

| $(D \rightarrow A)$ | -10dBm0     | -50dBm0∼-40dBm0 | -0.4 | _   | 0.4 | dB |

| $DR \rightarrow VR$ | 1020Hz Tone | -40dBm0∼ 3dBm0  | -0.2 |     | 0.2 |    |

## ■伝送損失周波数特性

| 項 目                 | 測定条件         |            | min   | typ | max  | 単位 |

|---------------------|--------------|------------|-------|-----|------|----|

| 伝送損失周波数特性           | 基準:          | 0.05kHz    | _     | _   | -30  |    |

| $(A \rightarrow D)$ | 0dBm0@1020Hz | 0.06kHz    | _     |     | -26  |    |

|                     |              | 0.2kHz     | -1.8  |     | 0    |    |

| VFTP,VFTN(差動) → DX  |              | 0.3~3.0kHz | -0.15 |     | 0.15 | dB |

|                     |              | 3.4kHz     | -0.8  |     | 0    |    |

|                     |              | 4.0kHz     | _     |     | -14  |    |

| 伝送損失周波数特性           | 基準:          | 0∼3.0kHz   | -0.15 |     | 0.15 |    |

| $(D \rightarrow A)$ | 0dBm0@1020Hz | 3.4kHz     | -0.8  |     | 0    | dB |

| $DR \rightarrow VR$ |              | 4.0kHz     | _     | _   | -14  |    |

## ■歪み特性

| 項 目                 | )           | 測定条件            |    | typ | max | 単位 |

|---------------------|-------------|-----------------|----|-----|-----|----|

| 信号対総合電力歪比           | 1020Hz Tone | -40dBm0~-45dBm0 | 25 | _   | _   |    |

| $(A \rightarrow D)$ |             | -30dBm0∼-40dBm0 | 30 | _   | _   | dB |

| VFTP,VFTN(差動) → DX  |             | 0dBm0∼-30dBm0   | 36 | _   | _   |    |

| 信号対総合電力歪比           | 1020Hz Tone | -40dBm0∼-45dBm0 | 25 | _   |     |    |

| $(D \rightarrow A)$ |             | -30dBm0∼-40dBm0 | 30 | _   |     | dB |

| $DR \rightarrow VR$ |             | 0dBm0∼-30dBm0   | 36 | _   | _   |    |

注1) μ-Law時はC-message,A-Law時はPsophometricフィルタ使用。

## ■ノイズ特性

| 項 目                 | 測定条件                                 | min | typ | max | 単位     |

|---------------------|--------------------------------------|-----|-----|-----|--------|

| 無通話時雑音 A→D (注1)     | $\mu$ -law, C-message                | _   | 8   | 13  | dBrnC0 |

| VFTP,VFTN(差動)→DX    | A-law, Psophometric                  | _   | -85 | -80 | dBm0p  |

| 無通話時雑音 D→A (注2)     | $\mu$ -law, C-message                | _   | 5   | 10  | dBrnC0 |

| $DR \rightarrow VR$ | A-law, Psophometric                  | _   | -85 | -80 | dBm0p  |

| 電源雑音除去比(送信)         | 変調レベル:<br>VDD=3.3V/±66mVop f=0~10kHz | ı   | 55  | _   | dB     |

| 電源雑音除去比(受信)         | 変調レベル:同上                             |     | 55  | _   | dB     |

注1) アナログ入力 = アナロググランドレベル

注2) ディジタル入力 (DR) = +0 CODE

## ■同一チャンネル内漏話

| 項 目                          | 測定条件                                           | min | typ | max | 単位 |

|------------------------------|------------------------------------------------|-----|-----|-----|----|

| 送信側→受信側<br>VFTP → VR,GSR(差動) | VFTP 0dBm0@1020Hz<br>DR = PCM 0-Code           | _   | _   | -75 | dB |

| 受信側→送信側<br>DR → DX           | DR=PCM 0dBm0 Code@1020Hz<br>VFTP,VFTN = 0 Vrms | _   | _   | -75 | dB |

## ■送信オペアンプ特性:AMPT

| 項目     | 測定条件                            | min | typ | max | 単位 |

|--------|---------------------------------|-----|-----|-----|----|

| 出力負荷抵抗 | AC負荷、帰還抵抗含む                     | 10  | _   | _   | kΩ |

| 出力負荷容量 |                                 | _   | _   | 50  | pF |

| 利得     | 反転増幅<br>(帰還容量100pF、fc=80kHz設定時) | -12 | _   | 6   | dB |

## ■受信信号出力特性:VR

| 項 目           | 項 目 測定条件       |     | typ | max | 単位 |

|---------------|----------------|-----|-----|-----|----|

| 出力電圧(AGNDレベル) | PCM +0 code入力時 | _   | 1.5 |     | V  |

| 出力負荷抵抗        | AC負荷           | 600 | _   | _   | Ω  |

| 出力負荷容量        |                |     |     | 40  | pF |

### ■受信オペアンプ特性:AMPR

| = 文旧が N D D 特任.AMI N |                                                       |       |      |     |      |  |

|----------------------|-------------------------------------------------------|-------|------|-----|------|--|

| 項目                   | 測定条件                                                  | min   | typ  | max | 単位   |  |

| 出力負荷抵抗               | AC負荷、帰還抵抗含む                                           | 600 - |      | _   | Ω    |  |

| 出力負荷容量               |                                                       |       |      | 40  | pF   |  |

| SINAD                | 0dB設定、1020Hz@0dBm0入力<br>VR,GSR差動出力時(600Ω負荷) C-message | 50    | 70 – |     | - dB |  |

| SINAD                | 0dB設定、1020Hz@0dBm0入力<br>VR,GSR差動出力時(5kΩ負荷) C-message  |       | 80   |     | ub   |  |

| 利得                   | 反転增幅(帰還容量100pF、fc=40kHz設定時)                           | -12   | _    | 6   | dB   |  |

| 最大出力振幅               | 3.14dBm0デジタルコードDR入力時                                  | _     | 2.15 | _   | Vp-p |  |

## パッケージ外形寸法図

16pin TSSOP

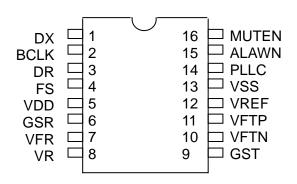

### パッケージ・ピン配置

## 16ピンTSSOP

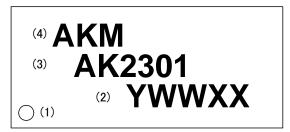

### マーキング仕様

- (1) 1ピン表示

- (2) 日付コード: YWWXX (5桁)

Y: 製造年(西暦年)の下一桁

WW: 製造週

XX: 社内管理コード

- (3) マーケティングコード: AK2301

- (4) 旭化成ロゴ

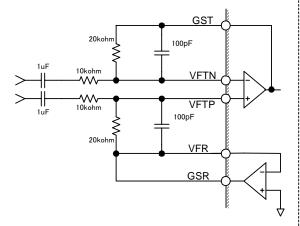

## 回路構成

| ブロック    | 機 能                                                                                  |

|---------|--------------------------------------------------------------------------------------|

| AMPT    | 送信用システムOdB(伝送Oレベルポイント)のゲイン調整用オペアンプです。                                                |

|         | 外付けの抵抗で差動もしくはシングルエンドのゲインアンプを構成します。帰還                                                 |

|         | 抵抗は $10 k\Omega$ 以上にして下さい。各端子の構成は次のようになっています。                                        |

|         | VFTN: オペアンプ反転入力                                                                      |

|         | VFTP: オペアンプ正転入力                                                                      |

|         | GST: オペアンプ出力                                                                         |

| AMPR    | 受信用システム <b>0dB</b> (伝送 <b>0</b> レベルポイント)のゲイン調整用オペアンプです。                              |

|         | 反転アンプとして使用し、外付けの抵抗で差動もしくはシングルエンドのゲイン                                                 |

|         | アンプを構成します。各端子の構成は次のようになっています。                                                        |

|         | VFR:オペアンプ反転入力 GSR:オペアンプ出力                                                            |

|         | 受信出力のVR端子と差動回路を構成する場合は、外付けの負荷と帰還抵抗を合わ                                                |

|         | せて $600\Omega$ 以上のAC負荷になるようにして下さい。                                                   |

| AAF     | 折り返し雑音防止用フィルタです。2次のRCローパスフィルタで構成されてお                                                 |

|         | り、A/Dコンバータのサンプリング周波数帯における雑音を除去します。                                                   |

| CODEC   | 入力されたアナログ信号を圧伸則に従い8ビットのPCMデータに変換します。圧伸                                               |

| A/D     | 則として、ITU-T G.711に準拠したA-Lawまたは $\mu$ -Lawをサポートします。                                    |

|         | A-Lawでは偶数ビットの反転もおこないます。                                                              |

|         | 圧伸則の選択は、ALAWNピンでおこないます。                                                              |

|         | "H": $\mu$ -Law "L": A-Law                                                           |

|         | また、帯域制限用フィルタを内蔵しています。                                                                |

| CODEC   | DR端子より取り込まれた8ビットのPCMデータを圧伸則に従い伸張し再生しま                                                |

| D/A     | す。圧伸則として、ITU-T G.711に準拠した $A$ -Law $e$ μ-Law $e$ |

|         | A-Lawでは偶数ビットの反転もおこないます。                                                              |

|         | 圧伸則の選択は、ALAWNピンでおこないます。                                                              |

|         | "H": μ-Law "L": A-Law                                                                |

| SMF     | D/Aコンバータの出力から帯域内の周波数成分を取り出すためのフィルタです。                                                |

| BGREF   | 温度補償されたバンドギャップ電圧発生器により、安定なアナロググランド電圧                                                 |

|         | を発生します。(1.5 $V$ typ) 安定化の為、1.0 $\mu$ F以上の容量を接続して下さい。                                 |

|         | 但し、外部負荷は接続しないで下さい。外部負荷を接続した場合の諸特性は保証                                                 |

|         | 致しかねます。この電圧を外部でご利用になる場合は、バッファした出力をご利                                                 |

|         | 用下さい。                                                                                |

| PCM I/F | BCLKで定められるデータレートでPCMデータを入出力します。PCMインタフェ                                              |

|         | ースにはLongFrame,ShortFrameの2つのモードがあります。この2つのモードは                                       |

|         | LSIが自動判定します。                                                                         |

|         | PCMデータはDR,DX端子から入出力されます。                                                             |

<MS0416-J-02> 12 2013/05

#### 機能説明

### ■PCMコーデック

#### ◆A/D

AMPTより入力されたアナログ信号は、折り返し雑音防止用フィルタ(AAF)を通過して、8ビットのPCM データに変換されます。変換されたPCMデータは、8ページの伝送損失周波数特性(A/D)に示す様な帯域制限 フィルタを通過後、DX端子よりBCLKの立ち上がりに同期してMSBから順に出力されます。この時出力されるPCMデータはA/ $\mu$ -law形式で、+フルスケールが3.14dBm0として定義され、アナログ入力側で 0.762Vrmsの入力が3.14dBm0のデジタルコードに変換されます。

#### ◆D/A

DR端子よりBCLKに同期して入力されたPCMデータは、8ページの伝送損失周波数特性(D/A)の様な特性を持ったデジタルフィルタを通過後、アナログ信号に変換され、さらにSMF(fc=30kHz typ)にて高調波成分を取り除いてVR端子より出力されます。入力するPCMデータの信号は、出力時と同様にA/ $\mu$ -law形式で、+フルスケールが3.14dBm0として定義されます。出力されるアナログ信号のレベルは、3.14dBm0入力時に0.762Vrmsとなります。

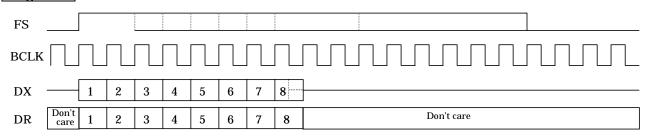

## ■ PCMインタフェース

AK2301は以下の2つのPCMデータインタフェースをサポートしています。

- Long Frame Sync(LF)

- Short Frame Sync(SF)

PCMデータは端子(DR,DX)から順次入出力されます。 いずれの場合もデータはMSBファーストで入出力されます。

#### ◆PCMインタフェースの選択

Long Frame/ Short frame はFSからLSIが自動的に判定します。

#### ● LONG FRAME (LF) / SHORT FRAME (SF)

#### ◆LF/SFの判定方法

単チャネルCODECは、以下のように入力されたFSの"H"期間によりLong Frame, Short Frameかを自動的に判断します。

| FS="H"の期間  | フレーム構成 |  |

|------------|--------|--|

| BCLKの2周期以上 | LF     |  |

| BCLKの1周期   | SF     |  |

#### ◆インタフェースタイミング

PCMデータは、フレーム同期信号FSに同期して、1フレーム区間( $125 \mu s$ )毎にそれぞれ8ビットずつDX,DR 端子より入出力されます。1フレーム区間には最大32個のタイムスロット(BCLK=2.048MHz時)がありますが、本LSIはそのうちの最初のタイムスロットを使ってPCMデータを入出力します。

## ◆FS (Frame Sync:フレーム同期信号)

8kHzの基準入力信号です。1フレーム(125us)毎に8ビットのPCMデータが入出力されます。BCLKと同期していることが必要です。

## !注意事項 <重要>

FSを停止する際は、BCLK=LとしてAK2301をパワーダウン状態にして下さい。

## ♦BCLK (Bit Clock)

PCMデータレートを定めます。BCLKは64\*N(N=1~32)kHzで選択可能です。

## LongFrame

## ShortFrame

<MS0416-J-02> 14 2013/05

### ■ミュート

ピン設定によってPCM CODECの出力をミュートすることが可能です。

#### ミュートピンの設定

| MUTEN端子 | 動作   | DX端子           | VR端子      |

|---------|------|----------------|-----------|

| L       | ミュート | High-Impedance | アナロググランド  |

| Н       | 信号出力 | PCMデータ出力       | アナログデータ出力 |

#### [DX端子]

MUTEN=L時にデータ出力中の場合、データを全ビット出力した後、次のFSの先頭からミュート状態に移行します。

### [VR端子]

MUTEN=LによりDACデジタルフィルタに0コードが入力され、D/A出力はミュート状態に移行します。

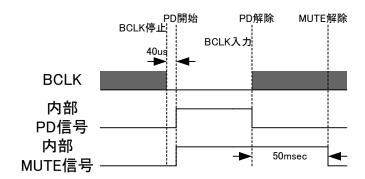

## ■パワーダウン

BCLK入力を「L」で停止するとパワーダウンモードに入ります。

#### ◆手順及び動作概要

#### 1)PD時

BCLK停止(L固定)後40usec(typ)経過すると、AK2301はパワーダウン(PD)モードに入ります。パワーダウン中、出力ピンGST,DX,GSR,VRはHi-Z、VREF,PLLCはVSSになります。

#### 2)PD解除時

PD中にBCLKとFS入力をするとPDモードが解除されます。異音出力防止の為、PD解除後50msec(typ)の間MUTE状態(DX=High-Z、VR=AGND)になります。

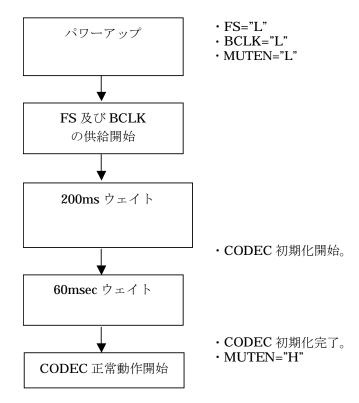

## ■パワーオン時の推奨動作手順

電源立ち上げ後AK2301を動作させる際、以下の様な手順で動作を開始されることを推奨致します。

## 外付け推奨接続図(例)

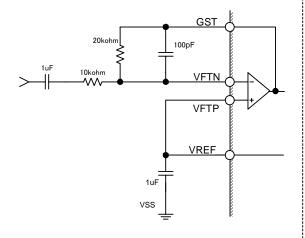

## 送信アンプ

## ◎差動構成

## ◎シングルエンド

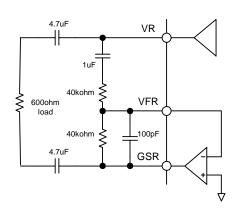

## 受信アンプ

## ◎差動構成

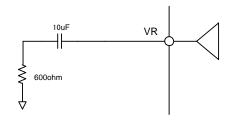

## ◎シングルエンド

## 電源部、及びPLL安定化容量

### 重要な注意事項

- 0. 本書に記載された弊社製品(以下、「本製品」といいます。)、および、本製品の仕様につきましては、本製品改善のために予告なく変更することがあります。従いまして、ご使用を検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社特約店営業担当にご確認ください。

- 1. 本書に記載された情報は、本製品の動作例、応用例を説明するものであり、その使用に際して弊社および第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。お客様の機器設計において当該情報を使用される場合は、お客様の責任において行って頂くとともに、当該情報の使用に起因してお客様または第三者に生じた損害に対し、弊社はその責任を負うものではありません。

- 2. 本製品は、医療機器、航空宇宙用機器、輸送機器、交通信号機器、燃焼機器、原子力制御用機器、各種安全装置など、その装置・機器の故障や動作不良が、直接または間接を問わず、生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性を要求される用途に使用されることを意図しておらず、保証もされていません。そのため、別途弊社より書面で許諾された場合を除き、これらの用途に本製品を使用しないでください。万が一、これらの用途に本製品を使用された場合、弊社は、当該使用から生ずる損害等の責任を一切負うものではありません。

- 3. 弊社は品質、信頼性の向上に努めておりますが、電子製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により、生命、身体、財産等が侵害されることのないよう、お客様の責任において、本製品を搭載されるお客様の製品に必要な安全設計を行うことをお願いします。

- 4. 本製品および本書記載の技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。本製品および本書記載の技術情報を輸出または非居住者に提供する場合は、「外国為替及び外国貿易法」その他の適用ある輸出関連法令を遵守し、必要な手続を行ってください。本製品および本書記載の技術情報を国内外の法令および規則により製造、使用、販売を禁止されている機器・システムに使用しないでください。

- 5. 本製品の環境適合性等の詳細につきましては、製品個別に必ず弊社営業担当までお問合せください。本製品のご使用に際しては、特定の物質の含有・使用を規制するRoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようにご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、弊社は一切の責任を負いかねます。

- 6. お客様の転売等によりこの注意事項に反して本製品が使用され、その使用から損害等が生じた場合はお客様にて当該損害をご負担または補償して頂きますのでご了承ください。

- 7. 本書の全部または一部を、弊社の事前の書面による承諾なしに、転載または複製することを禁じます。

<MS0416-J-02> 18 2013/05