#### **Advance Information**

This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

# MediaStream Controller

#### **Applications**

- Microsoft Windows<sup>™</sup> 3.1, Win '95<sup>™</sup>, and NT<sup>™</sup> GUI acceleration

- IBM OS/2<sup>TM</sup> GUI acceleration

- Xwindow System<sup>™</sup> acceleration

- Video for Windows<sup>™</sup> and Microsoft Windows MPC Audio<sup>™</sup>

- High Resolution Color Graphics

- Video-conferencing

**Brooktree**®

- Multimedia Applications

- Video Playback Acceleration

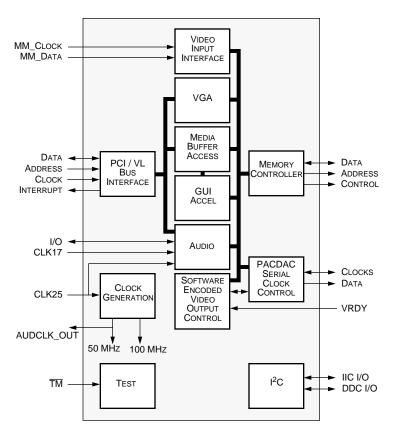

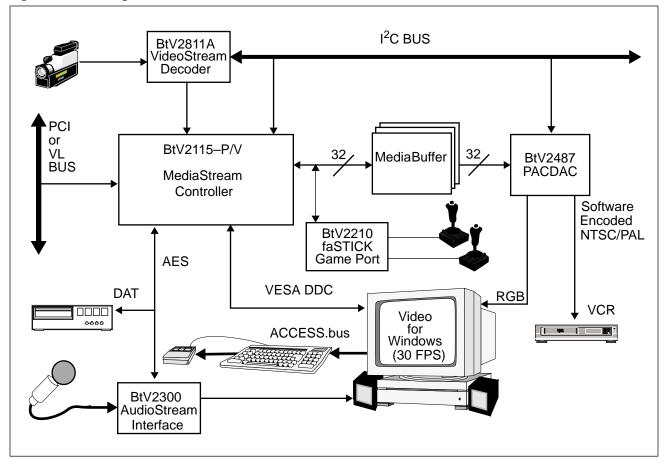

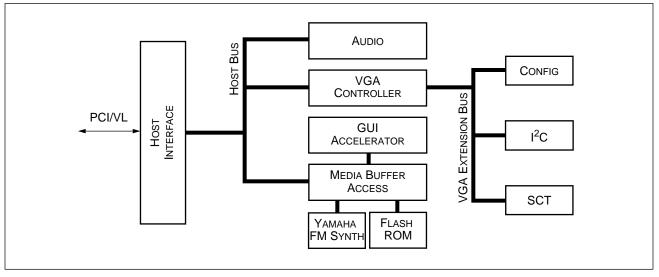

#### **Functional Block Diagram**

#### **Related Products**

- BtV2487 PACDAC

- BtV2811A VideoStream Decoder

- BtV2300 AudioStream Interface

#### **Distinguishing Features**

- Local Bus Graphics Controller (glueless for):

- PCI 2.0 bus

- VESA VL 2.0 bus (32 bit)

- 32 bit VRAM (1MB to 4MB) - Samsung™256Kx8: -8,-7,-6 128Kx16:-8.-7,-6

- Texas Instruments<sup>™</sup> 256Kx16:-8,-7,-6

- NEC™, Toshiba™, IBM™ 256Kx16:-8,-7,-6

- Up to 1MB of Flash ROM

- Supports Yamaha 2 and 4 operator mode FM synthesizer family

- Resolutions:

- 640x480: 4, 8, 16, 24, 32 b/pixel up to 76 Hz

- 800x600: 4, 8, 16, 32 b/pixel up to 76 Hz

- 1024x768: 4, 8, 16, 24 b/pixel up to 75 Hz

- 1280x1024: 4, 8, 16 b/pixel up to 75 Hz

- VGA compatibility for modes 0x00 0x07 and 0x0D - 0x13

- Multimedia Solution

- Glueless connection BtV2811A VideoStream Decoder

- Acceleration of two video planes with hardware double buffering

- Hardware-accelerated video playback

- Stereo audio in/out

- Software encoded NTSC/PAL video out to VCR

- Stretch Blt and raster scaling

- Legacy AudioPro<sup>™</sup> compatibility

- Digital Interface to consumer digital audio tape, minidisc, etc.

- Standard Interfaces

- PCI bus 2.0 compatible

- VESA VL bus 2.0

- AES/EBU S/PDIF CP-340 (with full access to channel/user bits)

- I<sup>2</sup>C/ ACCESS.bus

- VESA DDC1, DDC2A/B

- VESA DPMS

- 208 pin Power Quad package

Brooktree Corporation • 9868 Scranton Road • San Diego, CA 92121-3707 • 619-452-7580 1-800-2-BT-APPS • FAX: 619-452-1249 • Internet: apps@brooktree.com • L211501 Rev. C

## **Ordering Information**

| Model Number | Package          | Ambient Temperature Range |

|--------------|------------------|---------------------------|

| BtV2115KSF   | 208 PQFP         | 0°C to +70°C              |

| BtV2115AHF   | 208 plastic MQFP | 0°C to +50°C              |

## Trademarks

Brooktree and BtV are registered trademarks of Brooktree Corporation.

The following are trademarks of Brooktree Corporation: VIDEODAC, RAMDAC, Video CacheDAC, VideoCache, PACDAC, ByteStream, faSTICK, and MediaBuffer.

WinBench is a registered trademark and Winstone is a trademark of Ziff-Davis Publishing Company, L.P. In compliance with Ziff-Davis' licensing agreement: benchmark tests were obtained with WinBench 4.0 run on a Dell Dimension XPS P90 Minitower Pentium 90MHz, 256K SRAM cache, 16M system memory, and the BtV2115KSF PCI-bus graphics adapter.

Dell is a registered trademark and Dimension XPS P90 is a trademark of Dell Computer Corporation.

COMPAQ and DESKPRO are registered trademarks and EISA is a trademark of Compaq Computer Corporation.

Intel is a registered trademark and Pentium is a trademark of Intel Corporation.

Microsoft and MS-DOS are registered trademarks and Windows, Win '95, Windows NT, Plug and Play, Windows MPC Audio, and Video for Windows are trademarks of Microsoft Corporation.

Philips is a registered trademark of Philips International B.V.

ACCESS.bus is a trademark of Digital Equipment Corporation.

Tri-state is a trademark of National Semiconductor.

Micro Channel Architecture (MCA) and OS/2 are trademarks of IBM Corporation.

VESA is a registered trademark of and VL-Bus and VBE are trademarks of Video Electronics Standards Association.

Xwindow System is a trademark of Massachusetts Institute of Technology.

Yamaha OPL2/3/4 are trademarks of Yamaha Corporation.

Samsung is a trademark of Samsung Electronics Co., LTD

NEC is a trademark of NEC Corporation.

Toshiba is a trademark of Toshiba Corporation.

IBM is a trademark of IBM Corporation.

All other marks mentioned herein belong to their respective companies.

Copyright © 1994, 1995 Brooktree Corporation. All rights reserved. Print date: 08/30/95

Brooktree reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished by Brooktree Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Brooktree Corporation for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or patent rights of Brooktree Corporation. Brooktree is a registered trademark of Brooktree Corporation.

Brooktree Products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Brooktree Product can reasonably be expected to result in personal injury or death. Brooktree customers using or selling Brooktree Products for use in such applications do so at their own risk and agree to fully indemnify Brooktree for any damages resulting from such improper use or sale.

Brooktree and Bt are registered trademarks of Brooktree Corporation. Ultralock and ByteStream are trademarks of Brooktree Corporation. All other marks mentioned herein are the property of their respective holders.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

| List of Fig | j <b>ures</b>                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Tab | olesxxi                                                                                                                                                                                                                                                                            |

| Preface     | xxvii                                                                                                                                                                                                                                                                              |

| Wha         | It this Document Contains xxvii                                                                                                                                                                                                                                                    |

| Rela        | ited Documents xxix                                                                                                                                                                                                                                                                |

| Nota        | ation Conventions xxx                                                                                                                                                                                                                                                              |

| Product D   | escription 1                                                                                                                                                                                                                                                                       |

| Intro       | oduction                                                                                                                                                                                                                                                                           |

| Inte        | rface Description       7         CPU/HOST Interface       7         VRAM Interface       7         PACDAC Interface       8         Multimedia Interface       8         I <sup>2</sup> C Interface       8         Serial Audio Interface       8         Test Interface       8 |

| Dist        | inguishing Features                                                                                                                                                                                                                                                                |

| Арр         | lications and Related Products 10                                                                                                                                                                                                                                                  |

| BtV         | 2115 VL-Bus Pin List Summary 11                                                                                                                                                                                                                                                    |

| BtV         | 2115 PCI-Bus Pin List Summary 15                                                                                                                                                                                                                                                   |

| VGA Implementation                                                                                                                                                                                                                                                                                                                |                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| VGA Compatibility                                                                                                                                                                                                                                                                                                                 |                                                                            |

| VGA Operation                                                                                                                                                                                                                                                                                                                     | 20                                                                         |

| VGA Extension Registers.         Enable VGA CRT Controller Mechanism         Enable VGA CRT Controller Structure Generation         PACDAC Pointer         25 MHz PLL Select.         28 MHz PLL Select.         Attribute Index Status.         VGA CRT Generation Status         VGA Vertical Sync Select.         VGA DAC Mode | 25<br>25<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>26<br>26<br>26 |

| Configuration for VGA                                                                                                                                                                                                                                                                                                             |                                                                            |

| Support for VESA BIOS Extension Modes         VBE Modes         Frame Buffer Models         Timing Structures and High Resolution Modes         Mode Setting Procedure         Logical Window Control         DAC Palette Format                                                                                                  |                                                                            |

| Register Definitions                                                                                                                                                                                                                                                                                                              |                                                                            |

| Introduction                                                                                                                                                                                                                                                                                                                      |                                                                            |

| VGA Graphics Registers (I/O Mapped)                                                                                                                                                                                                                                                                                               |                                                                            |

| Graphics Index Port                                                                                                                                                                                                                                                                                                               |                                                                            |

| Graphics Data Port                                                                                                                                                                                                                                                                                                                |                                                                            |

| Set/Reset Register                                                                                                                                                                                                                                                                                                                |                                                                            |

| Enable Set/Reset Register                                                                                                                                                                                                                                                                                                         |                                                                            |

| Color Compare Register                                                                                                                                                                                                                                                                                                            |                                                                            |

| Data Rotate Register                                                                                                                                                                                                                                                                                                              |                                                                            |

| F        | Read Map Select Register                                                   | 40 |

|----------|----------------------------------------------------------------------------|----|

| Ν        | Mode Register                                                              | 41 |

| C        | Graphics Miscellaneous Register                                            | 42 |

| C        | Color Don't Care Register                                                  | 42 |

| E        | Bit Mask Register                                                          | 43 |

| Extensio | on Registers Accessed Via VGA Space (I/O Mapped)                           | 44 |

| ٧        | /GA Configuration Register                                                 | 44 |

| C        | Chip ID Registers                                                          | 44 |

| F        | ROM Page Register                                                          | 44 |

| F        | PLL25 Select Registers                                                     | 44 |

| F        | PLL28 Select Registers                                                     | 45 |

| C        | GUI Base Registers                                                         | 45 |

| C        | DAC Alias Pointer Registers                                                | 46 |

| F        | Read Latch Registers                                                       | 46 |

| V        | /GA Status Register                                                        | 47 |

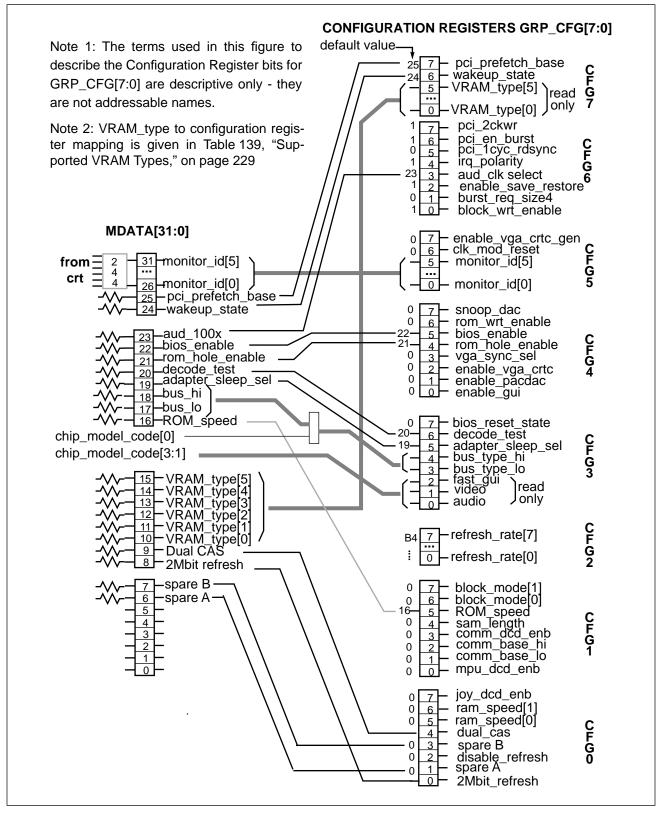

| C        | Configuration Registers                                                    | 47 |

| Ľ        | 2C Control Register                                                        | 54 |

| Ľ        | 2C Slave Control Register<br>register name: GRP_I2C_SCTRLR, GRP_I2C_SCTRLW | 54 |

| Ľ        | 2C Slave Data Register                                                     | 55 |

| Ľ        | 2C Master Control Register                                                 | 55 |

| Ľ        | 2C Master Data Register                                                    | 55 |

| Ν        | Master Structure A Address Register                                        | 55 |

| Ν        | Master Structure B Address Register                                        | 56 |

Bt

|        | PACDAC Controller Status Register                          | 6 |

|--------|------------------------------------------------------------|---|

|        | PACDAC Controller Control Register                         | 7 |

| VGA PO | CI Configuration Space (I/O Mapped)59                      | 9 |

|        | Read PCI Prefetchable Base Address Register                | Э |

|        | Read PCI ROM Base Address Register                         | Э |

|        | Read PCI Enable Registers                                  | C |

| SEV Re | egisters (I/O Mapped)6 <sup>.</sup>                        | 1 |

|        | Softvideo Controller Write Register                        | 1 |

|        | Softvideo Controller Read Register                         | 1 |

| VGA Se | equencer Registers (I/O Mapped)                            | 2 |

|        | Sequencer Index Register                                   | 2 |

|        | Sequencer Data Port                                        | 2 |

|        | Reset Register                                             | 2 |

|        | Clocking Mode Register                                     | 2 |

|        | Map Mask Register                                          | 4 |

|        | Character Map Select Register 64<br>register name: SEQ_CFS | 4 |

|        | Memory Mode Register                                       | ô |

| VGA Se | equencer Extension Registers (I/O Mapped)6                 | 7 |

|        | Unlock Register                                            | 7 |

| VGA CF | RT Controller (I/O Mapped)69                               | 9 |

|        | CRTC Color Index                                           | 9 |

|        | CRTC Monochrome Index                                      | Э |

|        | CRTC Color Data                                            | Э |

|        | CRTC Monochrome Data                                       | 9 |

| Horizontal Total Register       |

|---------------------------------|

| Horizontal Display End Register |

| Start Horizontal Blank Register |

| End Horizontal Blank Register   |

| Start Horizontal Sync Register  |

| End Horizontal Sync Register    |

| Vertical Total Register         |

| Overflow Register               |

| Preset Row Scan Register        |

| Character Height Register       |

| Cursor Start Register           |

| Cursor End Register             |

| Start Address High Register     |

| Start Address Low Register      |

| Cursor Location High Register   |

| Cursor Location Low Register    |

| Start Vertical Sync Register    |

| End Vertical Sync Register      |

| Vertical Display End Register   |

| Offset Register                 |

| Underline Register              |

| Start Vertical Blank Register   |

| End Vertical Blank Register     |

| Mode Control Register                                            | 77 |

|------------------------------------------------------------------|----|

| Line Compare Register                                            | 78 |

| VGA Attribute Controller (I/O Mapped)                            | 79 |

| Attribute Index and Data Port                                    | 79 |

| Read Data Port                                                   | 80 |

| Palette Registers                                                | 80 |

| Mode Control Register                                            | 80 |

| Overscan Color Register                                          | 81 |

| Color Plane Enable Register                                      | 82 |

| Horizontal Panning Register K<br><i>register name:</i> ATT_HPAN  | 82 |

| Color Select Register                                            | 83 |

| VGA General / External Registers (I/O Mapped)                    | 84 |

| POS102 Register                                                  | 84 |

| Adapter Sleep Register 8<br><i>register name:</i> ADAPT_SLEEP    | 84 |

| Motherboard Sleep Register K register name: MBD_SLEEP            | 85 |

| Input Status #0 Register 8<br>register name: INP_STAT0           | 86 |

| Color Input Status #1 Register                                   | 86 |

| Monochrome Input Status #1 Register                              | 86 |

| Write Miscellaneous Output Register                              | 87 |

| Read Miscellaneous Output Register                               | 87 |

| Feature Control Register       8         register name:       FC | 88 |

| VGA Color Registers (I/O Mapped)                                 | 89 |

| DAC Mask Register                                                | 89 |

| DAC State Register                                               | 89 |

|        | DAC Read Address Register                                    | 89 |

|--------|--------------------------------------------------------------|----|

|        | DAC Write Address Register register name: DAC_WRADDR         | 90 |

|        | DAC Data Register                                            | 90 |

| Legacy | y Audio FM Registers (I/O Mapped)                            | 91 |

|        | OPL Bank 0 Address                                           | 92 |

|        | register name: ADLIB_BNK0_ADDR                               |    |

|        | register name: OPL3_BNK0_ADDR2                               |    |

|        | register name: OPL2_BNK_ADDR2                                |    |

|        | register name: OPL3_BNK0_ADDR4                               |    |

|        | register name: OPL2_BNK_ADDR4                                |    |

|        | OPL Bank 0 Dataregister name: OPL3_BNK0_DATA2                | 92 |

|        | register name: OPL2_BNK_DATA2                                |    |

|        | register name: OPL3_BNK0_DATA4                               |    |

|        | register name: OPL2_BNK_DATA4                                |    |

|        | OPL Bank 1 Address                                           | 93 |

|        | register name: ADLIB_BNK1_ADDR                               |    |

|        | register name: OPL3_BNK1_ADDR2                               |    |

|        | register name: OPL3_BNK1_ADDR4                               |    |

|        | OPL Bank 1 Data                                              | 93 |

|        | register name: ADLIB_BNK1_DATA                               |    |

|        | register name: OPL3_BNK1_DATA2                               |    |

|        | register name: OPL3_BNK1_DATA4                               |    |

| Legacy | y Audio Mixer Registers (I/O Mapped)                         | 94 |

|        | Mixer Address                                                | 94 |

|        | register name: LA_MIX_ADDR2                                  |    |

|        | register name: LA_MIX_ADDR4                                  |    |

|        | Mixer Data                                                   | 94 |

|        | register name: LA_MIX_DATA2                                  |    |

|        | register name: LA_MIX_DATA4                                  |    |

| Legacy | y Audio DSP Registers (I/O Mapped)                           | 95 |

|        | DSP Reset<br>register name: LA_DSP_RESET2                    | 95 |

|        | register name: LA_DSP_RESET4                                 |    |

|        | DSP Read Data                                                | 95 |

|        | register name: LA_DSP_READ4                                  |    |

|        | DSP Command-Data / Command Status register name: LA_DSP_CMD2 | 95 |

|        | register name: LA_DSP_CMD4                                   |    |

|        |                                                              |    |

| DSP Read Status                                                                          | 96         |

|------------------------------------------------------------------------------------------|------------|

| register name: LA_READY4                                                                 |            |

| Audio Registers (Memory Mapped)                                                          | 96         |

| GUI Aperture Registers (Memory Mapped)                                                   | 96         |

| GUI Accelerator Registers (Memory Mapped)                                                | 96         |

| Video Input Registers (Memory Mapped)                                                    |            |

| PU Address Space Apertures                                                               | 97         |

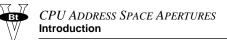

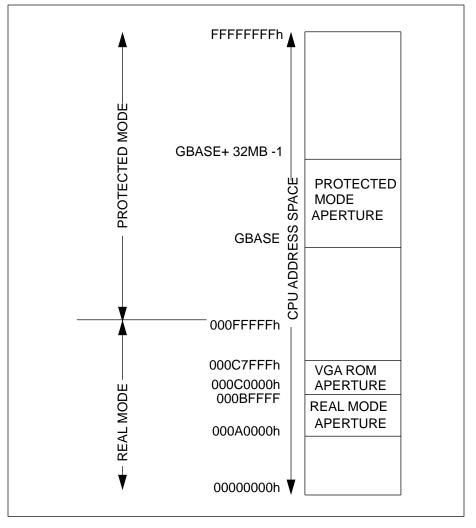

| Introduction                                                                             | 97         |

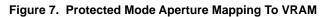

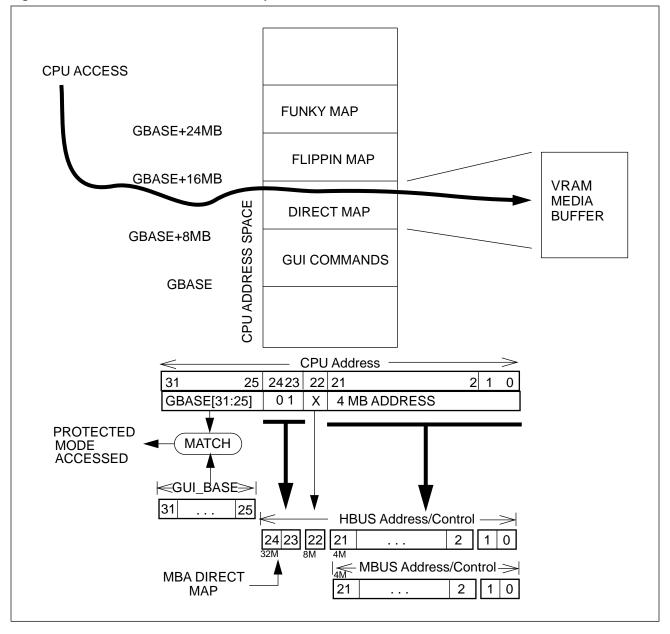

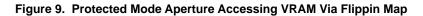

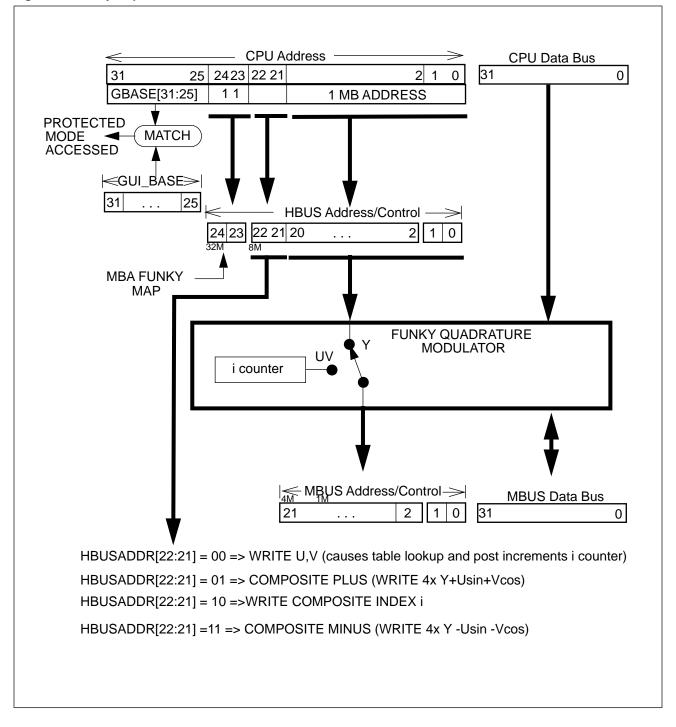

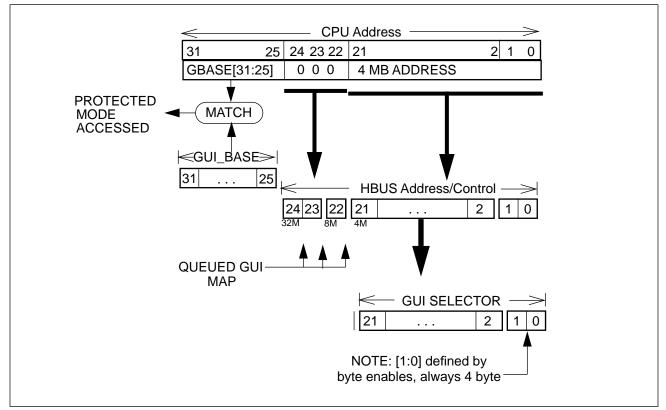

| Protected Mode Aperture                                                                  | 101        |

| Direct Map<br>Flippin Map<br>Funky Map<br>Funky Map Support for SEV                      | 105<br>107 |

| GUI Command/Register Map                                                                 | 112        |

| GUI FIFO Register                                                                        | 112        |

| GUI FIFO Depth Register                                                                  | 114        |

| Flash Rom Support                                                                        | 117        |

| Yamaha Support                                                                           |            |

| Audio Subsystem       GUI Base Address Register         register name: GRP_GUI_BASE[3:0] |            |

| MBA Control Register                                                                     | 125        |

| Real Mode Aperture                                                                       | 127        |

| VGA ROM Aperture                                                                         | 129        |

| CPU Apertures In a PCI-Bus Environment                                                   | 130        |

| PM_BASE Field<br>Prefetch Base<br>PCI Constraints on GBASE                               | 130        |

| Configuration Registers 133                                                                                        |

|--------------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                       |

| <b>Register Initialization</b> 134                                                                                 |

| I <sup>2</sup> C Master and Slave Controllers 137                                                                  |

| Introduction                                                                                                       |

| I <sup>2</sup> C Control WRITE Register 138<br><i>register name:</i> GRP_I2C_CTRLW                                 |

| I <sup>2</sup> C Control READ Register                                                                             |

| I <sup>2</sup> C Master Module Software Interface                                                                  |

| I <sup>2</sup> C Master Data Register                                                                              |

| I <sup>2</sup> C Master Control Read Register                                                                      |

| I <sup>2</sup> C Master Control Write Register                                                                     |

| I <sup>2</sup> C Slave Module Software Interface                                                                   |

| I <sup>2</sup> C Slave Data Register                                                                               |

| I <sup>2</sup> C Slave Control Read Register 152<br>register name: GRP_I2C_SCTRLR                                  |

| I <sup>2</sup> C Slave Control Write Register                                                                      |

| GUI Accelerator                                                                                                    |

| GUI Theory Of Operation                                                                                            |

| Retained Bitmap Context.       161         Raster Operation       161                                              |

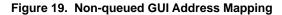

| CPU Addressing of GUI                                                                                              |

| GUI Commands167RWREGISTER Command168BITBLT Command169RWGUIDATA Command170LINE Draw Command171STRETCHBLT Command171 |

| GUI Registers                                                             |

|---------------------------------------------------------------------------|

| Bitmap Context Registers                                                  |

| Foreground Color Register                                                 |

| Background Color Register 179 <i>register name:</i> GUI_BG_COLOR          |

| Destination XY Increment Register                                         |

| BLT Control Register (Direction)                                          |

| LINE Control Register 180<br>register name: GUI_LINE_CONTROL              |

| Line Pattern Register                                                     |

| Bresenham 0, Address Register                                             |

| Bresenham 0, Error Register                                               |

| Bresenham 0, K1 Register 182<br>register name: GUI_BRES0_K1               |

| Bresenham 0, K2 Register                                                  |

| Bresenham 0, Increment 1 Registers                                        |

| Bresenham 0, Increment 2 Registers                                        |

| Bresenham 0, Length Register 184<br>register name: GUI_BRES0_LENGTH       |

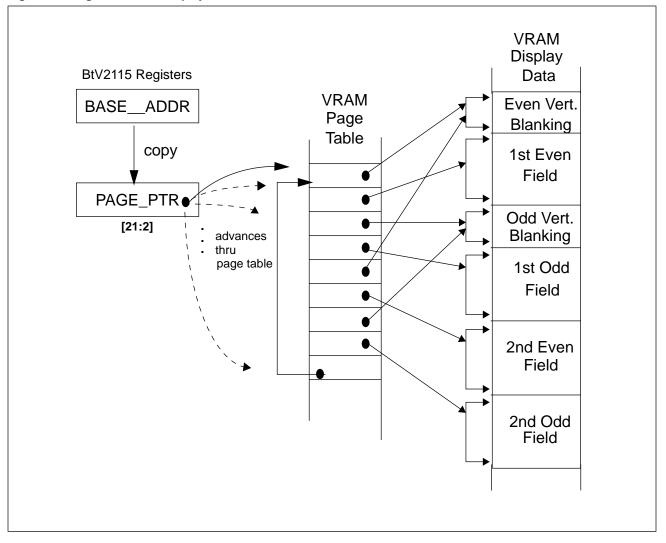

| Software Encoded Video (SEV) Player 185                                   |

| Introduction                                                              |

| Organization of Display Data In Memory                                    |

| Programming the SEV Block                                                 |

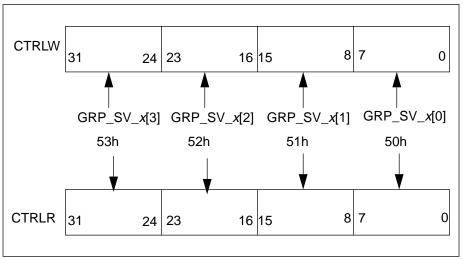

| SEV Controller Write Register 189 <i>register name:</i> GRP_SV_CTRLW[3:0] |

| SEV Controller Read Register                                              |

| Accessing SEV Registers 193                                               |

| PACDAC Controller 195 |                                                                       |  |

|-----------------------|-----------------------------------------------------------------------|--|

| Intr                  | oduction                                                              |  |

| PAC                   | CDAC Data Types 196                                                   |  |

| Mas                   | ster Structure                                                        |  |

|                       | Packet Ordering. 200                                                  |  |

|                       | Graphics Data                                                         |  |

|                       | Cursor Data         201           Video Data         201              |  |

|                       | Timing Structure Data                                                 |  |

|                       | DAC Data                                                              |  |

| San                   | nple Master Structure Setup 208                                       |  |

| CPU Host              | Bus Interface                                                         |  |

|                       |                                                                       |  |

| VES                   | SA Local Bus Interface                                                |  |

|                       | VL Address Bus                                                        |  |

|                       | VL Byte Enables                                                       |  |

|                       | VL Data Bus.         211           VL Address Strobe.         211     |  |

|                       | VL Address Strobe                                                     |  |

|                       | VL Clock                                                              |  |

|                       | VL Memory or IO Status                                                |  |

|                       | VL Data or Code Status                                                |  |

|                       | VL Read or Write Status 212                                           |  |

|                       | VL Identifier Pin                                                     |  |

|                       | VL Ready Return                                                       |  |

|                       | VL Local Device Select                                                |  |

|                       | VL Local Ready                                                        |  |

|                       | Interrupt Request Line 9 212                                          |  |

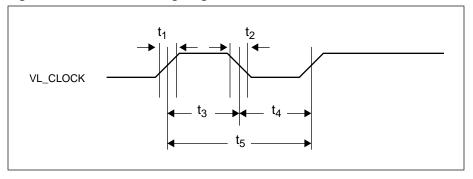

| VL                    | Bus Timing                                                            |  |

| PCI                   | <b>Bus Interface</b>                                                  |  |

|                       | PCI Address and Data Bus 216                                          |  |

|                       | PCI Bus Command and Byte Enables                                      |  |

|                       | PCI Parity                                                            |  |

|                       | PCI Clock                                                             |  |

|                       | PCI Reset                                                             |  |

|                       | PCI Cycle Frame         217           PCI Initiator Ready         217 |  |

|                       | PCI Target Ready                                                      |  |

|                       | PCI Stop                                                              |  |

|                       | PCI Initialization Device Select                                      |  |

|              | PCI Device Select                                                    |     |

|--------------|----------------------------------------------------------------------|-----|

|              | PCI Interrupt A PCI High Speed Read                                  |     |

| PCI Co       | nfiguration Space                                                    | 219 |

|              | PCI Vendor ID Registers                                              | 220 |

|              | PCI Device ID Registers                                              | 220 |

|              | PCI Command Registers                                                | 220 |

|              | PCI Status Registers                                                 | 221 |

|              | PCI Revision ID Register                                             | 221 |

|              | PCI Class Code Registers                                             | 221 |

|              | PCI Base Address Registers                                           | 222 |

|              | PCI Prefetchable Base Address Registers                              | 222 |

|              | PCI ROM Base Address Register                                        |     |

|              | PCI Interrupt Line Register                                          |     |

|              | PCI Interrupt Pin Register register name: PCI_INT0_PIN, PCI_INT1_PIN | 224 |

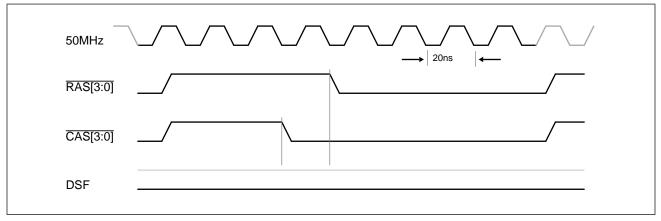

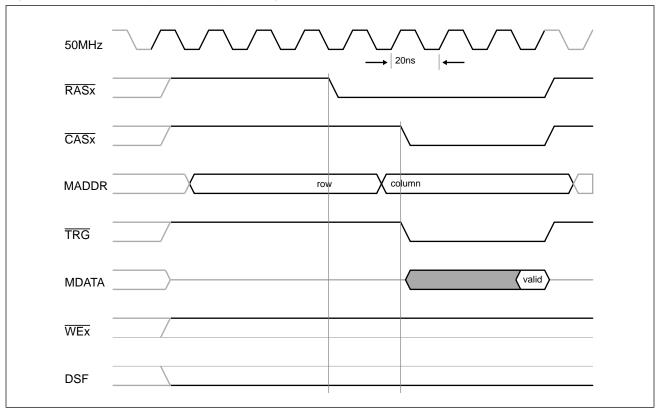

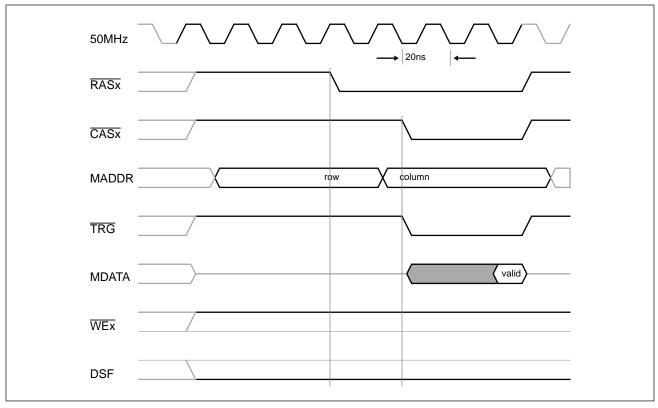

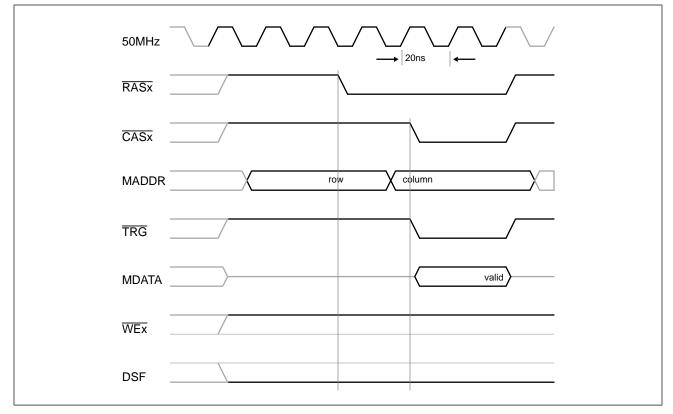

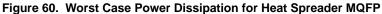

| Video RAM II | nterface                                                             | 225 |

| Introdu      | ction                                                                | 225 |

| VRAMS        | Signal Description                                                   | 226 |

| VRAM         | Configurability                                                      | 228 |

|              | VRAM Types Supported                                                 | 228 |

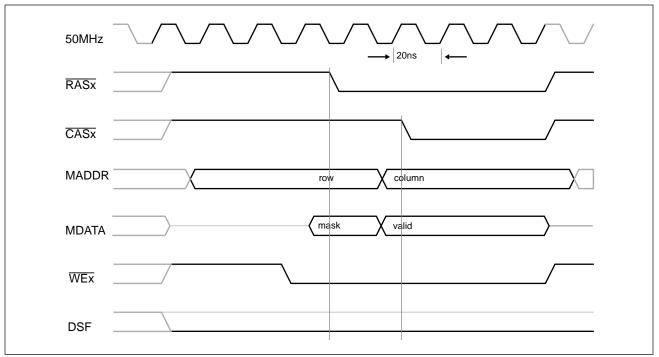

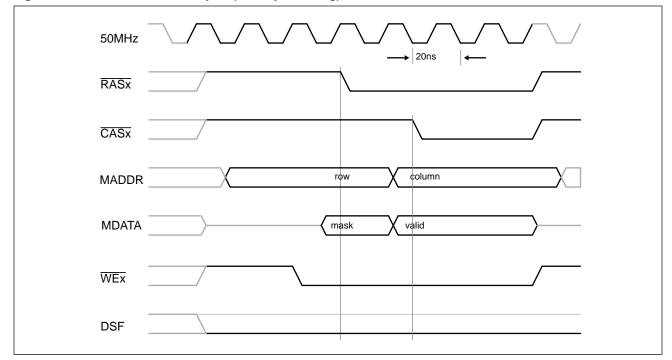

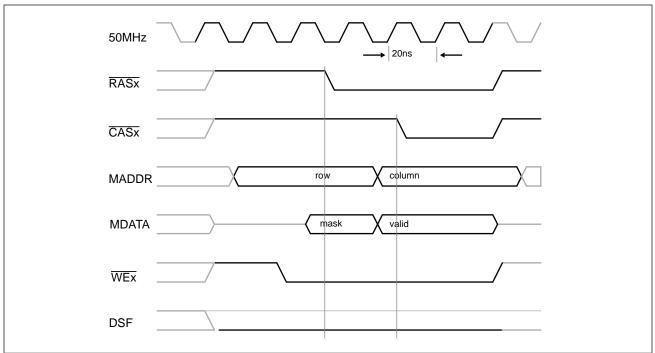

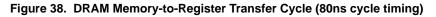

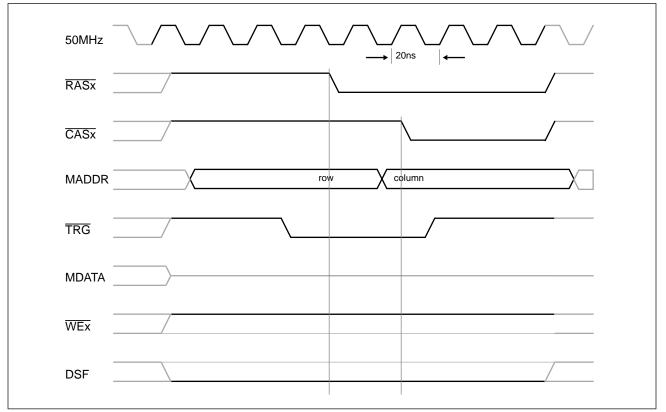

|              | Parallel Data Cycle Types Supported.                                 |     |

|              | REFRESH Cycle                                                        |     |

|              |                                                                      |     |

|              | DRAM Write                                                           |     |

|              | DRAM Non-masked Block Write                                          |     |

|              | Register Transfer (DRAM to SAM).                                     |     |

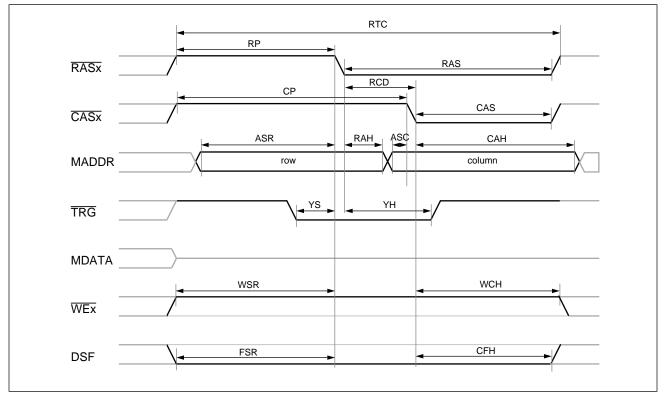

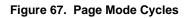

|              | Page Mode Cycles                                                     |     |

|              | VRAM Timing Considerations                                           |     |

| NON        | -VRAM Attachment                                                                           |

|------------|--------------------------------------------------------------------------------------------|

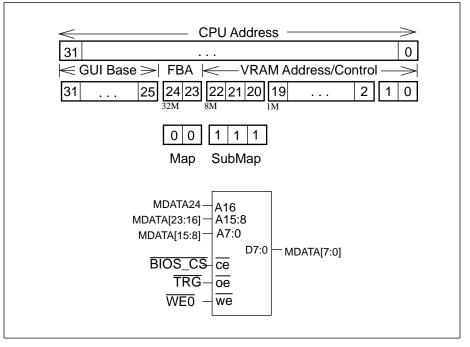

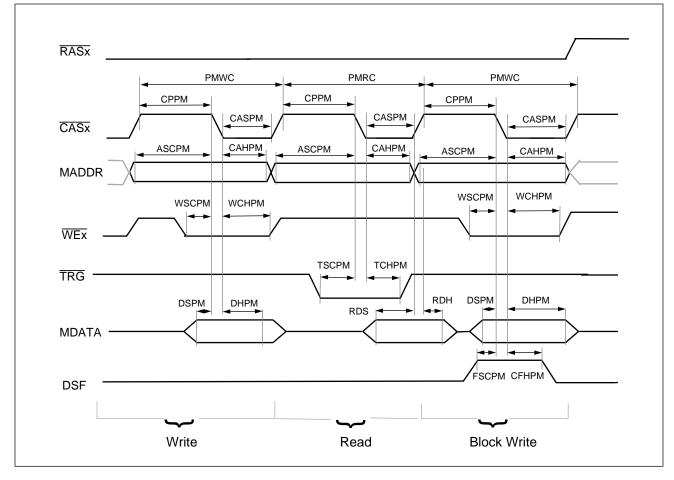

|            | ROM Configurability                                                                        |

|            | ROM Connection                                                                             |

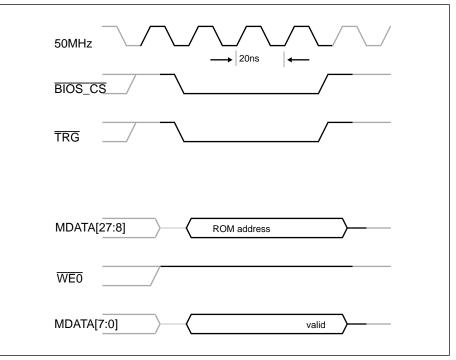

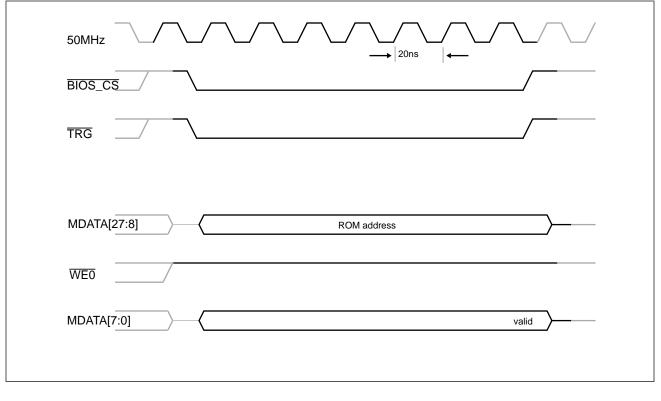

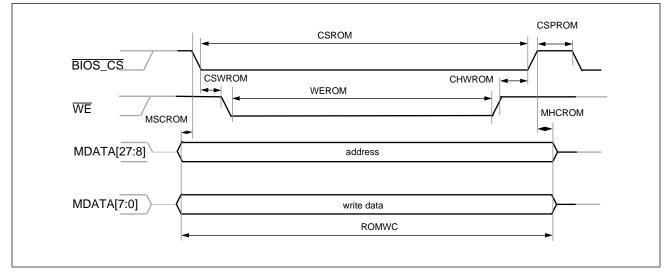

|            | ROM READ Cycle                                                                             |

|            | Flash ROM Write Cycle                                                                      |

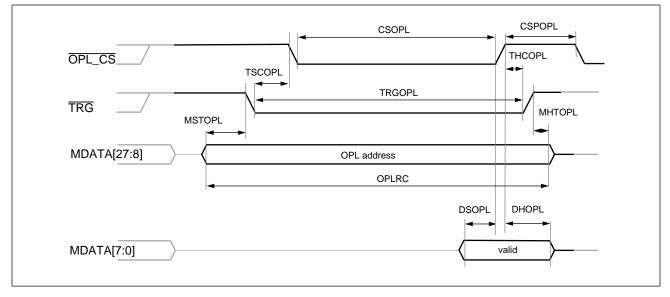

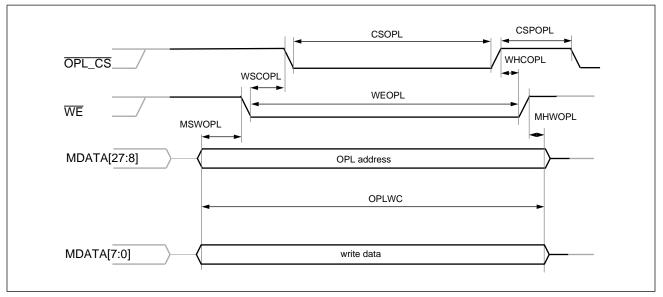

|            | Yamaha Configurability 252                                                                 |

|            | Yamaha FM Synthesizer Connection 252                                                       |

| Video Inpu | it Subsystem 253                                                                           |

| Intro      | duction                                                                                    |

| Buffe      | er Management Hardware 256                                                                 |

|            | Video Control Register                                                                     |

|            | Video One Register                                                                         |

|            | Video Two Register                                                                         |

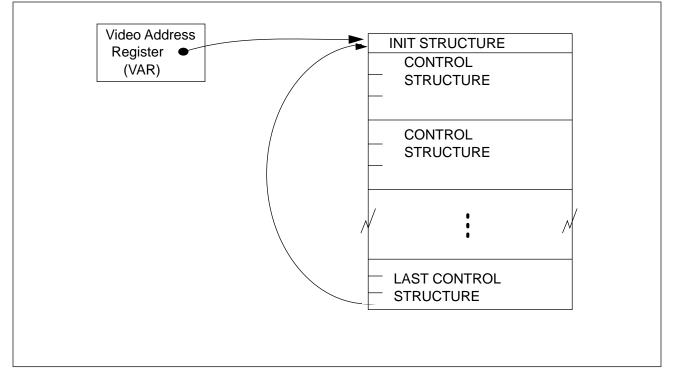

|            | Video Address Register                                                                     |

|            | Init Structure Definition       258         Capture Control Structure Definition       259 |

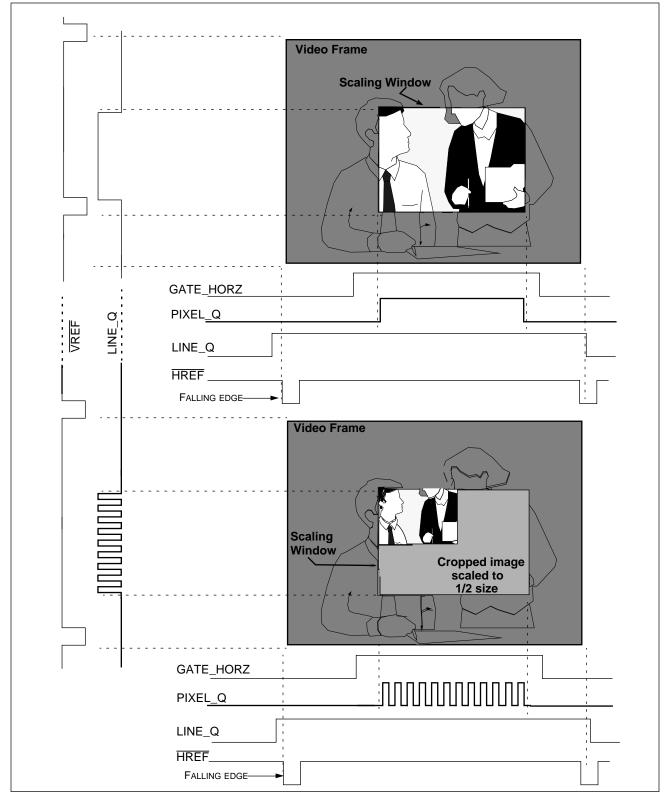

| Line       | Numbering System                                                                           |

| Live       | Video Input                                                                                |

| Clos       | ed Captioning Capture With A Video Icon                                                    |

| Sing       | le Frame Record Example                                                                    |

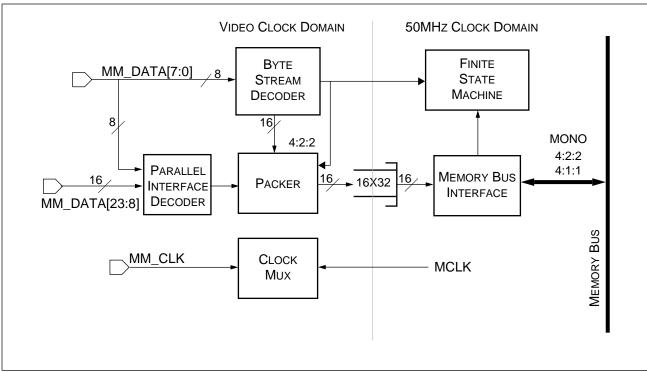

| Para       | Ilel Decoder Interface                                                                     |

|            | Signal Definitions    268      Video Interface Timing    269                               |

| Audio Inte | <b>rface</b>                                                                               |

| Intro      | duction                                                                                    |

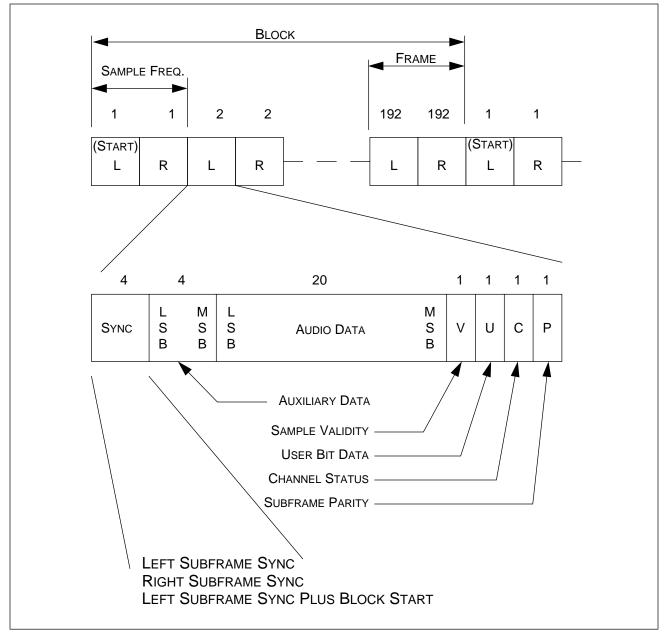

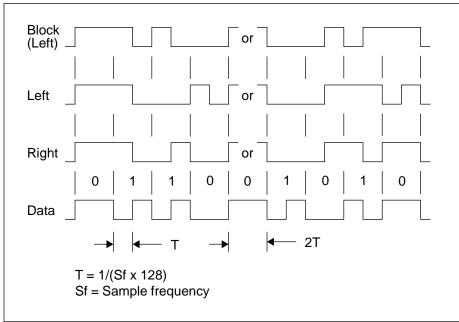

| AES/       | /EBU Format                                                                                |

|            | AES References 274                                                                         |

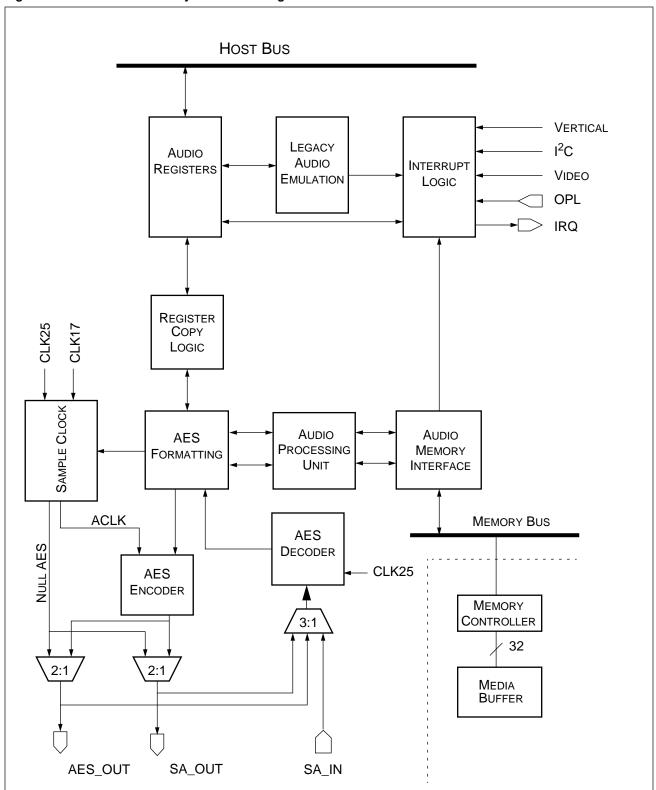

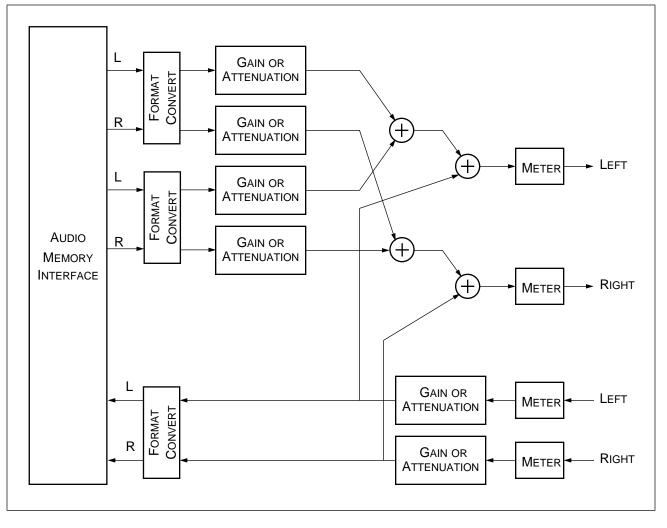

| Audi       | o Subsystem                                                                                |

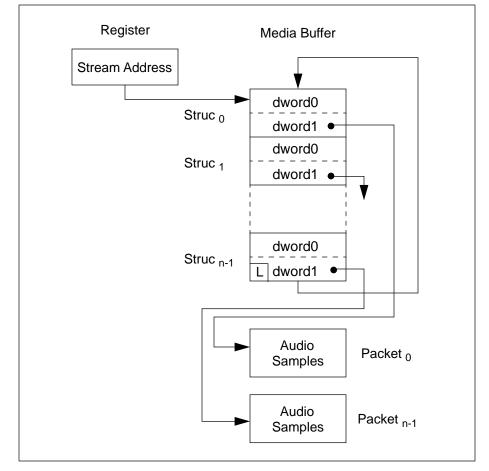

|            | Audio Data Formats In the Media Buffer                                                     |

| Audio Registers 2                                                       | 289 |

|-------------------------------------------------------------------------|-----|

| Interrupt Status Register                                               | 291 |

| Interrupt Mask Register 2<br><i>register name:</i> AUD_IMR              | 292 |

| Interrupt State Register 2<br><i>register name:</i> AUD_ISTR            | 292 |

| Application Port Read Data Register 2<br><i>register name:</i> AUD_APPR | 293 |

| BtV2300 Chip ID Register 2<br><i>register name:</i> AUD_CID             | 293 |

| Serial Data Control Register 2<br><i>register name:</i> AUD_SDCR        | 293 |

| Encoder Block Length Register                                           | 294 |

| Encoder Block Position Register 2<br><i>register name:</i> AUD_EBP      | 295 |

| Decoder Status Register 2<br><i>register name:</i> AID_DSR              | 295 |

| Reserved                                                                | 295 |

| Channel Status Byte 0 Register                                          | 295 |

| Channel Status Byte 1 Register 2<br><i>register name:</i> AUD_CH1       | 295 |

| Channel Status Byte 2 Register                                          | 296 |

| Channel Status Byte 3 Register 2<br><i>register name:</i> AUD_CH3       | 296 |

| Reserved                                                                | 296 |

| Primary Stream Address Register 2<br><i>register name:</i> AUD_PSA      | 296 |

| Primary Stream Counter Register 2<br><i>register name:</i> AUD_PSC      | 297 |

| Secondary Stream Address Register                                       | 298 |

| Secondary Stream Counter Register                                       | 299 |

| Level Registers                                                         | 300 |

| Primary Level Registers                                                 | 300 |

| Secondary Level Registers                                               | 301 |

| Record Monitoring Level Registers                                       | 301 |

| Number Summed Register<br>register name: AUD_NS[1:0]                    |   |

|-------------------------------------------------------------------------|---|

| Right/Left Playback Sum Registers<br>register name: AUD_LPSUM, A        |   |

| Right/Left Playback Max Registers<br>register name: AUD_LPMAX, A        |   |

| Right/Left Record Sum Registers .<br><i>register name:</i> AUD_LRSUM, A |   |

| Right/Left Record Max Registers<br>register name: AUD_LRMAX, A          |   |

| Legacy Audio Emulation Registers<br>register name: LA_EMULATION         |   |

| BtV2300 Address Register <i>register name:</i> AUD_CAR                  |   |

| BtV2300 Register Shadows                                                |   |

| Clock Register                                                          |   |

| Filter Clock Divisor Register<br>register name: AUD_FCLK                |   |

| Codec Mode Register                                                     |   |

| Application Port Direction Register<br>register name: AUD_APPO          |   |

| Application Port Write Data Registe<br>register name: AUD_APPD          | r |

| BtV2300 Mixer Control Register<br>register name: AUD_MIX                |   |

| BtV2300 MUX Selector Register<br>register name: AUD_MUX                 |   |

| CD Left Attenuation Register<br>register name: AUD_CDL                  |   |

| CD Right Attenuation Register<br>register name: AUD_CDR                 |   |

| Line Left Attenuation Register<br><i>register name:</i> AUD_LL          |   |

| Line Right Attenuation Register<br><i>register name:</i> AUD_LR         |   |

| FM Left Attenuation Register<br><i>register name:</i> AUD_FML           |   |

| FM Right Attenuation Register <i>register name:</i> AUD_FMR             |   |

| MIC Left Gain Register<br>register name: AUD_MICL                       |   |

| MIC Right Gain Register<br>register name: AUD_MICR                      |   |

Bt

| DAC Left Attenuation Register                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|

| DAC Right Attenuation Register                                                                                             |

| Channel Status                                                                                                             |

| perating Specifications                                                                                                    |

| VRAM Timing Parameters                                                                                                     |

| BtV2115 Subsystem VRAM Load Limits                                                                                         |

| Absolute Maximum Ratings 324                                                                                               |

| Recommended Operating Conditions                                                                                           |

| Target DC Characteristics    326                                                                                           |

| Target AC Characteristics    328                                                                                           |

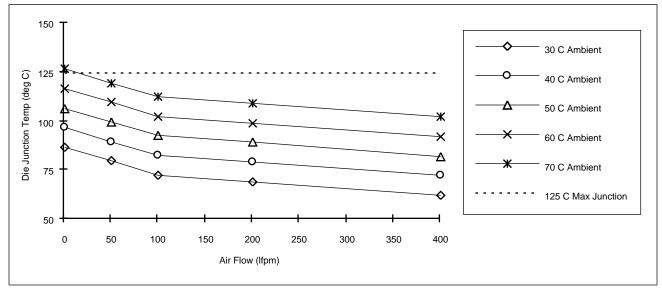

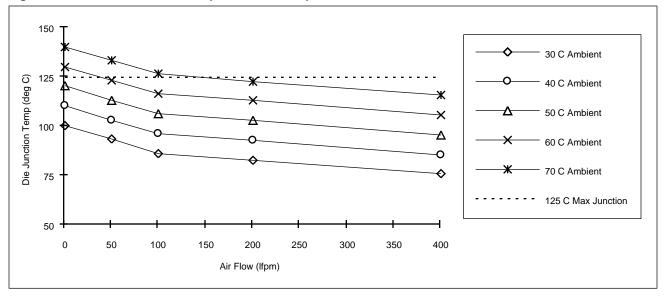

| Power Dissipation330Introduction330Power Dissipation330Thermal Resistance330Package Power Dissipation330Recommendations332 |

| Timing Diagrams                                                                                                            |

| Packaging Specifications                                                                                                   |

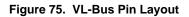

| BtV2115 VL-Bus Pin Layout                                                                                                  |

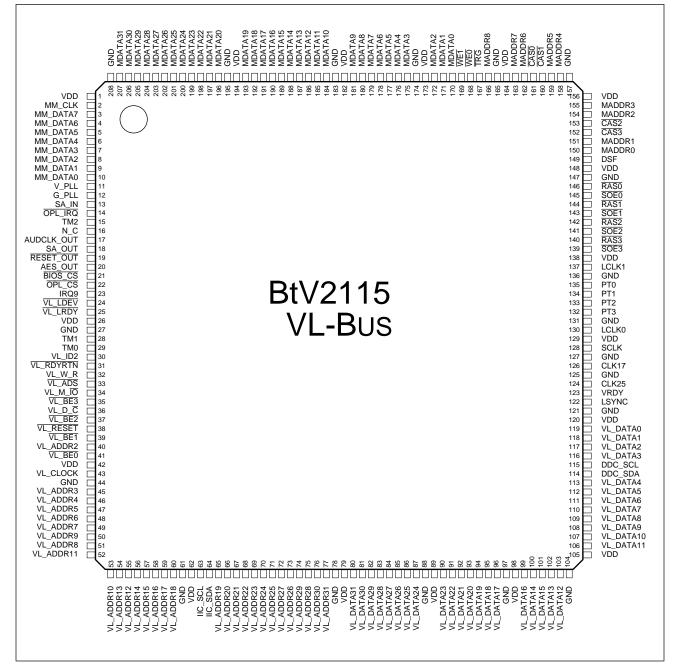

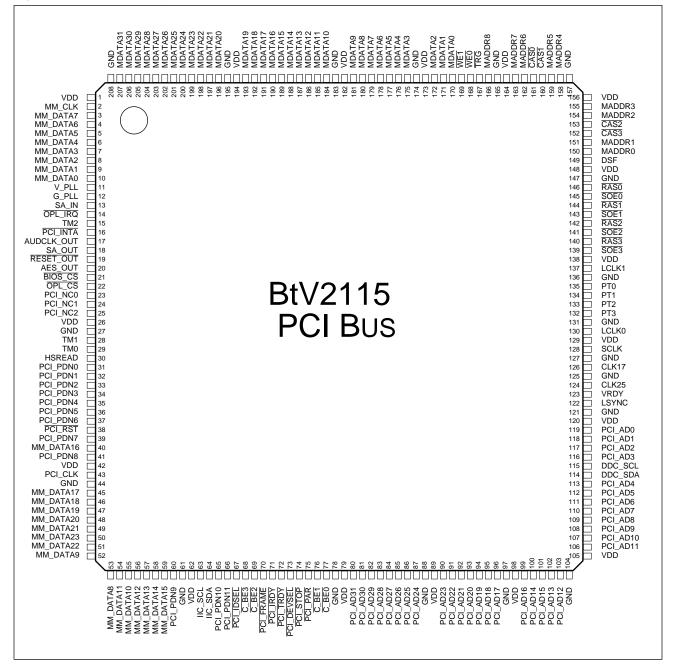

| BtV2115 PCI-Bus Pin Layout                                                                                                 |

| Revision History                                                                                                           |

# LIST OF FIGURES

| Figure 1.  | BtV Configuration                                      | 2     |

|------------|--------------------------------------------------------|-------|

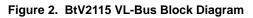

| Figure 2.  | BtV2115 VL-Bus Block Diagram                           | 5     |

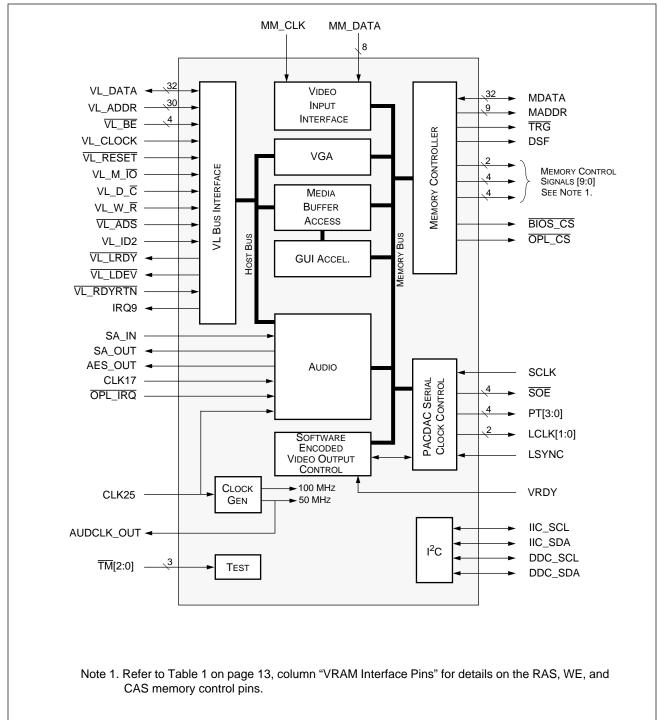

| Figure 3.  | BtV2115 PCI-Bus Block Diagram                          | 6     |

| Figure 4.  | CPU Apertures on a VL System                           | 98    |

| Figure 5.  | CPU Apertures on a PCI System.                         | . 100 |

| Figure 6.  | HBUS Agents                                            | . 101 |

| Figure 7.  | Protected Mode Aperture Mapping To VRAM                | . 102 |

| Figure 8.  | Media Buffer Access Via Direct Map                     | . 104 |

| Figure 9.  | Protected Mode Aperture Accessing VRAM Via Flippin Map | . 106 |

| Figure 10. | Funky Map SEV                                          | . 108 |

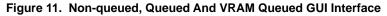

| Figure 11. | Non-queued, Queued And VRAM Queued GUI Interface       | . 115 |

| Figure 12. | GUI Command/Register Map                               | . 116 |

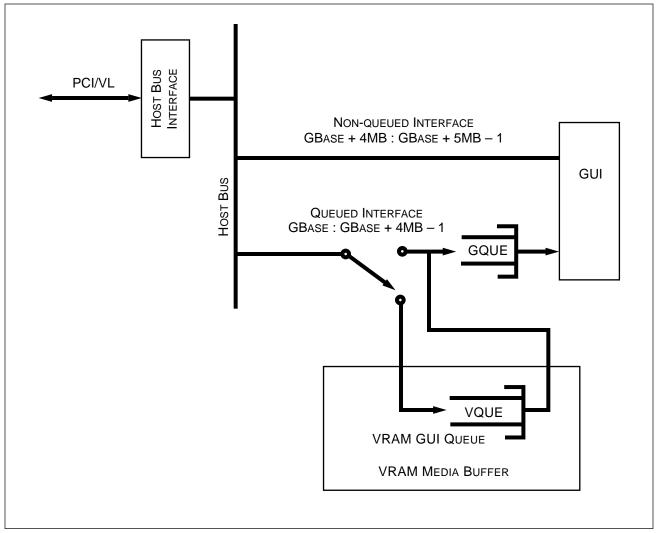

| Figure 13. | Flash ROM Access Address Mapping                       | . 119 |

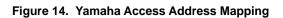

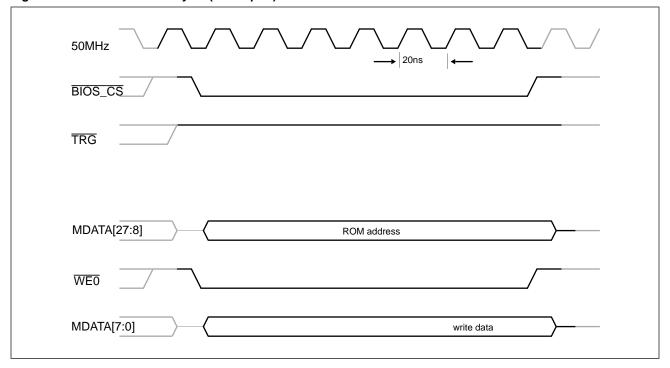

| Figure 14. | Yamaha Access Address Mapping                          | . 121 |

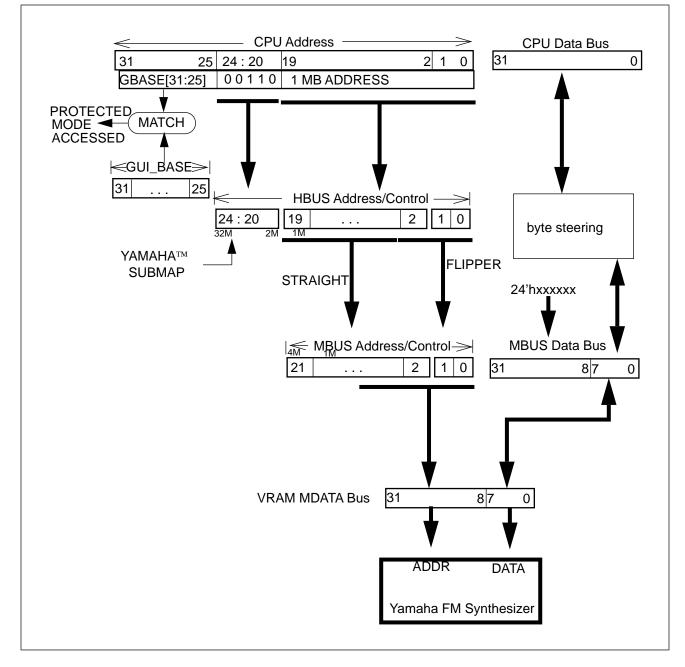

| Figure 15. | Audio Access Address Mapping                           | . 122 |

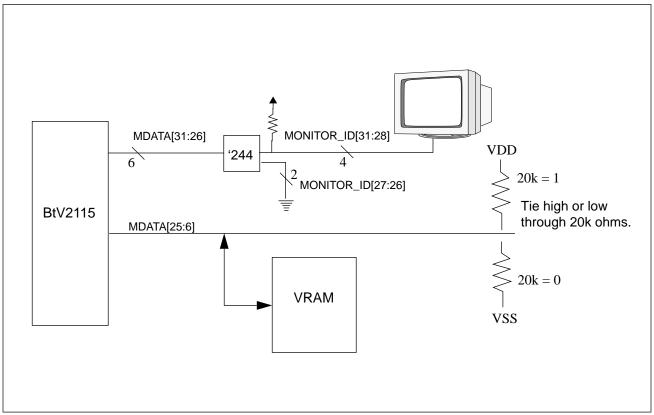

| Figure 16. | Configuration Resistor Straps                          | . 134 |

| Figure 17. | Configuration Registers and Strapping Bits for BtV2115 | . 136 |

| Figure 18. | Queued GUI Address Mapping                             | . 163 |

| -          | Non-queued GUI Address Mapping                         |       |

| Figure 20. | Organization of Display Data                           | . 186 |

| Figure 21. | Accessing SEV Registers Through VGA Extension Bus      | . 193 |

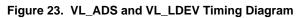

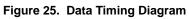

| Figure 22. | VL_CLOCK Timing Diagram                                | . 214 |

| Figure 23. | VL_ADS and VL_LDEV Timing Diagram.                     | . 214 |

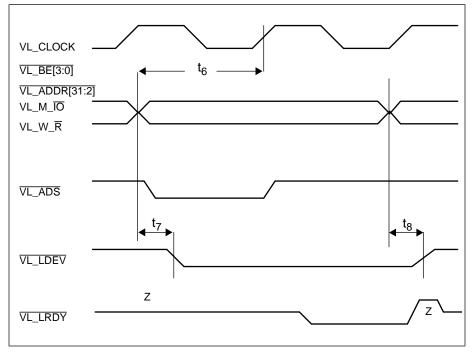

| Figure 24. | VL_LRDY Delay Timing Diagram                           | . 215 |

| -          | Data Timing Diagram                                    |       |

| Figure 26. | PCI Configuration Space Header                         | . 219 |

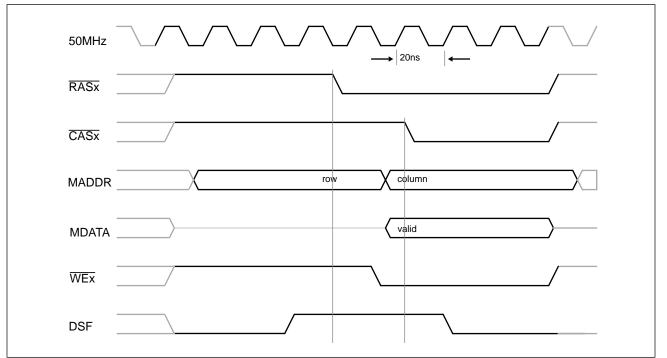

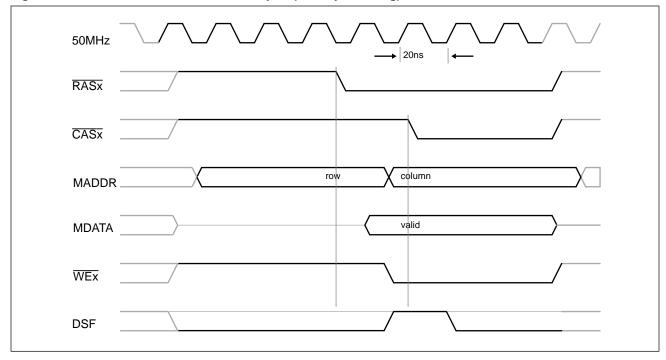

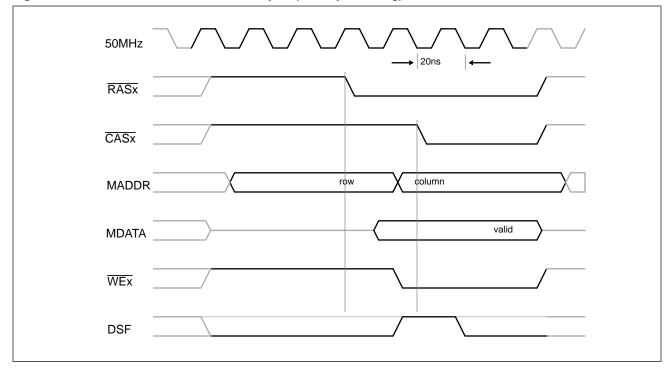

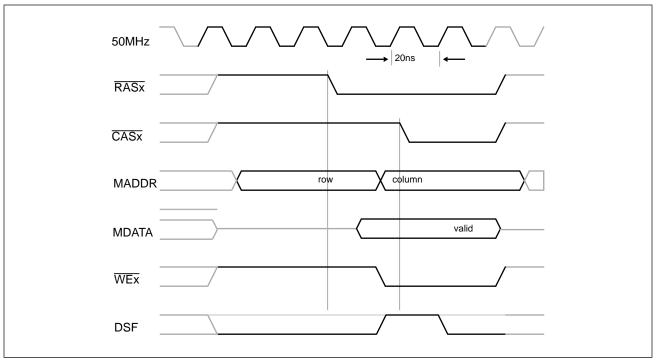

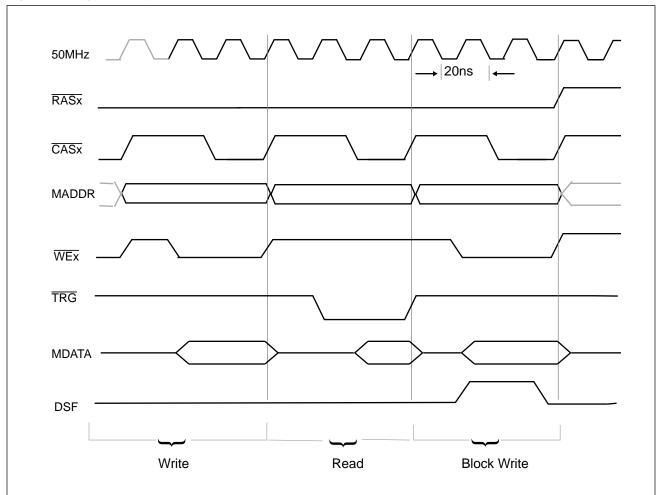

| Figure 27. | VRAM Refresh Cycle                                     | . 231 |

| Figure 28. | VRAM Read Cycle (80ns cycle timing)                    | . 232 |

| Figure 29. | VRAM Read Cycle (70ns cycle timing)                    | . 233 |

| Figure 30. | VRAM Read Cycle (60ns cycle timing)                    | . 234 |

| Figure 31. | DRAM Masked Write Cycle (80ns cycle timing)            | . 235 |

| Figure 32. | DRAM Masked Write Cycle (70ns cycle timing)            | . 236 |

| Figure 33. | DRAM Write Cycle (60ns cycle timing)                   | . 237 |

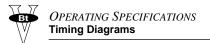

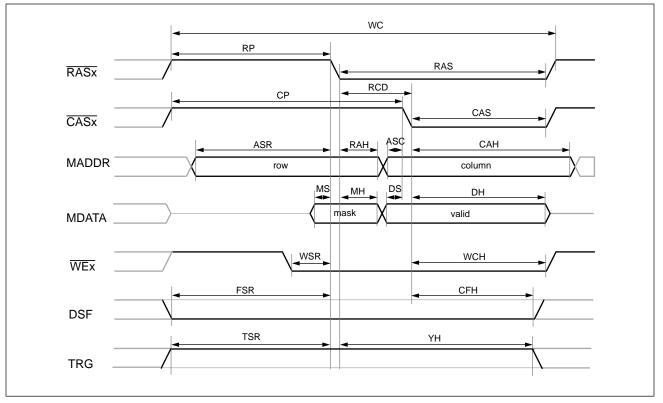

| Figure 34. | Load Color Register Cycle (all speeds)                 | . 238 |

| Figure 35. | DRAM Non-Masked Block Write Cycle (80ns cycle timing)  | . 239 |

| Figure 36. | DRAM Non-Masked Block Write Cycle (70ns cycle timing)  | . 240 |

| Figure 37 | DRAM Non-Masked Block Write Cycle (60ns cycle timing)      |

|-----------|------------------------------------------------------------|

| -         | DRAM Memory-to-Register Transfer Cycle (80ns cycle timing) |

| -         | VRAM Memory-to-Register Transfer Cycle (70ns cycle timing) |

| -         | VRAM Memory-to-Register Transfer Cycle (60ns cycle timing) |

| Figure 41 | Page Mode Cycles                                           |

| Figure 42 | ROM Connection                                             |

| -         | ROM Read Cycle (70ns part)                                 |

|           | ROM Read Cycle (120ns part)                                |

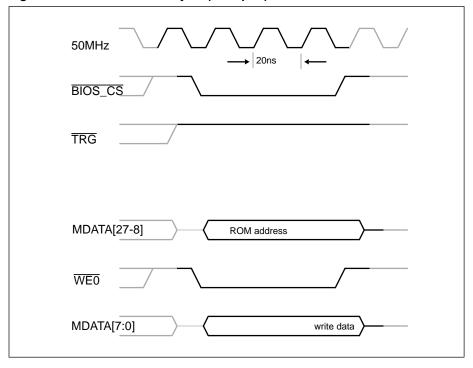

| Figure 45 | Flash ROM Write Cycle (70ns part) 250                      |

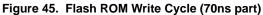

|           | Flash ROM Write Cycle (120ns part)                         |

| Figure 47 | BtV2115 Connections to Yamaha FM Synthesizer               |

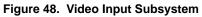

| Figure 48 | Video Input Subsystem                                      |

| Figure 49 | Video Input Control Structures                             |

| Figure 50 | Video Input Subsystem Block Diagram                        |

| Figure 51 | Reference Signals for Scaling Window                       |

| Figure 52 | Video Interface Timing Diagram                             |

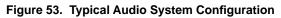

| Figure 53 | Typical Audio System Configuration                         |

| Figure 54 | AES Framing                                                |

| Figure 55 | AES Timing Diagram                                         |

| Figure 56 | BtV2115 Audio Subsystem Block Diagram                      |

| Figure 57 | Audio Processing Unit                                      |

| Figure 58 | Stream and Data Structure                                  |

| Figure 59 | Worst Case Power Dissipation for Power Quad                |

| Figure 60 | Worst Case Power Dissipation for Heat Spreader MQFP        |

| Figure 61 | VRAM Read Cycle                                            |

| Figure 62 | VRAM Masked Write Cycle                                    |

| Figure 63 | Load Color Register Cycle                                  |

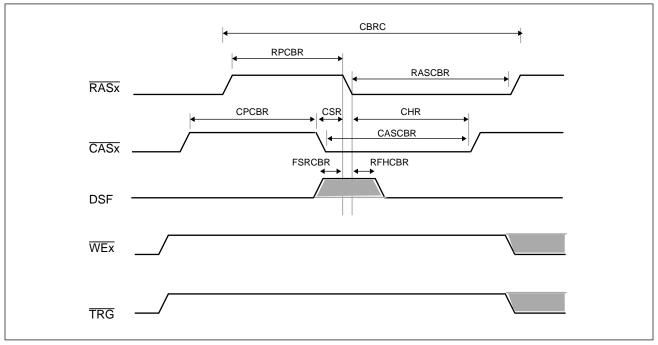

| Figure 64 | CAS-Before-RAS Refresh Cycles                              |

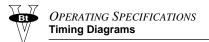

| Figure 65 | VRAM Non-Masked Block Write Cycle                          |

| Figure 66 | VRAM Memory-to-Shift Register Transfer Cycle               |

| Figure 67 | Page Mode Cycles                                           |

| Figure 68 | . ROM Read Cycle                                           |

| Figure 69 | ROM Write Cycle, FLASH ROM 338                             |

| Figure 70 | OPL Read Cycle                                             |

| Figure 71 | OPL Write Cycle                                            |

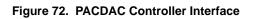

| Figure 72 | PACDAC Controller Interface                                |

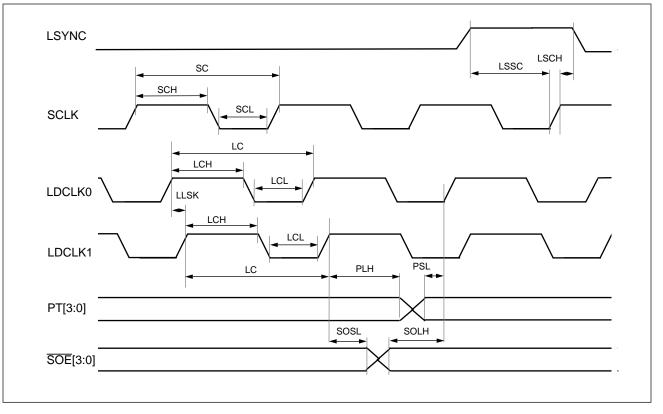

| Figure 73 | BtV2115KSF Packaging Diagram                               |

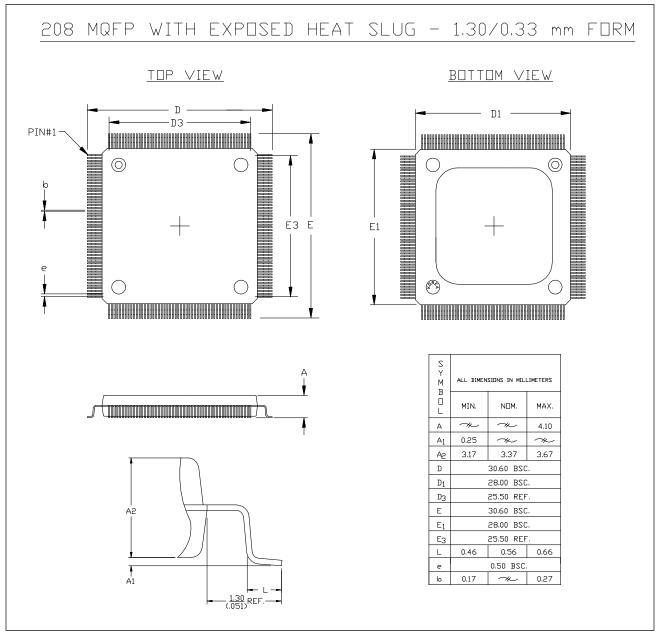

| Figure 74 | BtV2115AHF Packaging Diagram                               |

| -         | VL-Bus Pin Layout                                          |

| Figure 76 | PCI-Bus Pin Layout                                         |

|           |                                                            |

# LIST OF TABLES

| Table 1.  | BtV2115 VL-Bus Pin List Summary 11             |

|-----------|------------------------------------------------|

| Table 2.  | BtV2115 PCI-Bus Pin LIst Summary 15            |

| Table 3.  | VGA Modified Fields                            |

| Table 4.  | DAC Register Offset                            |

| Table 5.  | Recommended Master Structure Fields 27         |

| Table 6.  | Typical DAC Structure                          |

| Table 7.  | BtV2115 I/O Address Map 34                     |

| Table 8.  | Set/Reset Register                             |

| Table 9.  | Enable Set/Reset Register                      |

| Table 10. | Color Compare Register                         |

| Table 11. | Data Rotate Register 40                        |

| Table 12. | Read Map Select Register 40                    |

| Table 13. | Mode Register                                  |

| Table 14. | Graphics Controller: Miscellaneous Register 42 |

| Table 15. | Color Don't Care Register 42                   |

| Table 16. | Bit Mask Register 43                           |

| Table 17. | PLL 25MHz and 28MHz Select Registers 45        |

| Table 18. | GRP_PDAC Registers 46                          |

| Table 19. | Configuration Register <7> (GRP_CFG7) 47       |

| Table 20. | Configuration Register <6> (GRP_CFG6) 48       |

| Table 21. | Configuration Register <5> (GRP_CFG5) 49       |

| Table 22. | Configuration Register <4> (GRP_CFG4) 50       |

| Table 23. | Configuration Register <3> (GRP_CFG3) 52       |

| Table 24. | Configuration Register <2> (GRP_CFG2) 53       |

| Table 25. | Configuration Register <1> (GRP_CFG1) 53       |

| Table 26. | Configuration Register <0> (GRP_CFG0) 54       |

| Table 27. | Master Structures A and B Address Registers 56 |

| Table 28. | PACDAC Controller Status Register 57           |

| Table 29. | PACDAC Controller Control Register 58          |

| Table 30. | Read PCI Prefetch Base Address 59              |

| Table 31. | Read PCI ROM Base Address 59                   |

| Table 32. | Read PCI Enable Registers                      |

| Table 33. | Clocking Mode Register                         |

| Table 34. | Shift & Load Control Bits 63                   |

| Table 35. | Map Mask Register                              |

| Table 36. | Character Map Select Register 64               |

Bt

| T-11-07   | Develop Field Oxford                           |

|-----------|------------------------------------------------|

|           | Secondary Font Selection                       |

|           | Primary Font Selection                         |

|           | Memory Mode Register                           |

|           | Sequencer Unlock Register                      |

|           | End Horizontal Blank Register                  |

|           | End Horizontal Sync Register                   |

|           | Overflow Register                              |

|           | Preset Row Scan Register                       |

|           | Character Height Register                      |

|           | Cursor Start Register                          |

|           | Cursor End Register                            |

|           | End Vertical Sync Register                     |

| Table 49. | Underline Register                             |

| Table 50. |                                                |

|           | Attribute Index/Data Port Register             |

| Table 52. | Read Data Port Register                        |

| Table 53. | Palette Registers                              |

| Table 54. | Mode Control Register                          |

| Table 55. | Color Plane Enable Register                    |

| Table 56. | Horizontal Panning Register                    |

| Table 57. | Allowable Pixel Pans                           |

| Table 58. | Color Select Register                          |

| Table 59. | POS102 Register                                |

| Table 60. | Adapter Sleep Register                         |

| Table 61. | Motherboard Sleep Register                     |

| Table 62. | Input Status #0 Register                       |

| Table 63. | Input Status #1 Register                       |

| Table 64. | Miscellaneous Output Register (Read and Write) |

| Table 65. | Color Registers: DAC State Register            |

| Table 66. | Legacy Audio FM Register Addresses             |

| Table 67. | WRITE U/V ([22:21]=00)                         |

| Table 68. | Composite Plus ([22:21]=01)                    |

| Table 69. | WRITE Composite Index ([22:21]=10)             |

| Table 70. | Composite Minus ([22:21]=11)                   |

| Table 71. | Quadrature Modulator CPU bus Example 111       |

| Table 72. | GUI FIFO Register (GUIREG_FIFO)                |

| Table 73. | GUI FIFO Depth Register (GUIREG_DEPTH)         |

|           | Submap Read/Write Characteristics              |

|           | GRP_GUI_BASE Address Register                  |

|           | GUI MBA Control Register                       |

|           | Bus Type Encode                                |

|           |                                                |

| Table 78. | Chip Model Coding.                                            | 135 |

|-----------|---------------------------------------------------------------|-----|

| Table 79. | GRP_I2C_CTRLW Control Register                                | 138 |

| Table 80. | GRP_I2C_CTRLR Control Register                                | 139 |

| Table 81. | I <sup>2</sup> C Master Receive Data GRP_I2C_MDATA            | 141 |

| Table 82. | I <sup>2</sup> C Master Read Control Register GRP_I2C_MCTRLR  | 142 |

| Table 83. | GRP_I2C_MCTRLR Current Bit                                    | 144 |

| Table 84. | Example of Reading GRP_I2C_MCTRLR Register                    | 144 |

| Table 85. | I <sup>2</sup> C Master Write Control Register GRP_I2C_MCTRLW | 145 |

| Table 86. | Example of writing to GRP_I2C_MCTRLW                          | 147 |

| Table 87. | I <sup>2</sup> C Slave Receive DATA GRP_I2C_SDATA             | 151 |

|           | I <sup>2</sup> C Slave Read Control Register GRP_I2C_SCTRLR   |     |

|           | GRP_I2C_SCTRLR Current Bit                                    |     |

|           | Examples of Reading GRP_I2C_SCTRLR                            |     |

| Table 91. | I <sup>2</sup> C Slave Write Control Register GRP_I2C_SCTRLW  | 155 |

|           | Example of writing to GRP_I2C_SCTRLW                          |     |

|           | Address Fields For GUI Accesses                               |     |

|           | GUI Commands                                                  |     |

|           | BLT Command                                                   |     |

|           | XY Address Format                                             |     |

|           | RWGUIDATA Command                                             |     |

|           | RWGUIDATA_LENGTH                                              |     |

|           | LINE Command                                                  |     |

|           | STRETCHBLT Command                                            |     |

|           | . GUI Registers                                               |     |

|           | Bitmap Context Registers.                                     |     |

|           | Bitmap Register TYPE Field.                                   |     |

|           | .Bitmap Register OFFSET Field                                 |     |

|           | Bitmap Register PITCH Field                                   |     |

|           | Example Bitmap Context Register Allocation                    |     |

|           | GUI Configuration Register (GUIREG_CFG)                       |     |

|           | . Foreground Color Register                                   |     |

|           | Background Color Register                                     |     |

|           | Destination XY Increment.                                     |     |

|           | .BLT Control Register                                         |     |

|           | Line Control Register                                         | 180 |

|           | B.Bresenham 0, Address Register                               |     |

|           | Bresenham 0, Error Register                                   |     |

|           | Bresenham 0, Constant K1                                      |     |

|           | Bresenham 0, Constant K2                                      | 183 |

|           | Bresenham 0, Increment 1 and 2 Registers.                     |     |

| Table 118 | Bresenham 0 Length Register                                   | 184 |

| Table 119. Page Table Entry    186                        |   |

|-----------------------------------------------------------|---|

| Table 120.SEV GRP_SV_CTRLW Register    189                | ) |

| Table 121. Packet Size Used    190                        | ) |

| Table 122.SEV GRP_SV_CTRLR Register.    191               |   |

| Table 123. PT[3:0] Data Type Assignments    196           | ; |

| Table 124. Master Structure Entry Format    198           | ; |

| Table 125. UP_MODE Bit Definitions    202                 | • |

| Table 126. Timing Atom Bit Definitions.    205            | , |

| Table 127. Timing Structure Format    206                 |   |

| Table 128. VL-Bus Timing    213                           | } |

| Table 129. PCI Command Register - Function 0    220       | ) |

| Table 130. PCI Command Register - Function 1    220       | ) |

| Table 131.PCI Status Register    221                      |   |

| Table 132. PCI Class Code Register - Function 0    221    |   |

| Table 133. PCI Class Code Register - Function 1    222    | • |

| Table 134. PCI Base Register - Function 0    222          | • |

| Table 135. PCI Prefetch Base Register - Function 0    223 | 5 |

| Table 136. PCI ROM Base Register - Function 0             | 5 |

| Table 137. VRAM Dual WE/Dual CAS Modes    226             | ; |

| Table 138. VRAM Bus Signals    227                        |   |

| Table 139. Supported VRAM Types    229                    | ) |

| Table 140. Flash ROM Types Supported    246               | ; |

| Table 141. Video Control Register    256                  | ; |

| Table 142. Video One Register    257                      |   |

| Table 143. Video Two Register    257                      |   |

| Table 144. Video Address Register    258                  |   |

| Table 145. Init Structure    258                          |   |

| Table 146. Capture Control Structure DWORD0    259        |   |

| Table 147. Capture Control Structure DWORD1    260        |   |

| Table 148. Capture Control Structure DWORD2    261        |   |

| Table 149. Parallel Decoder Interface    266              |   |

| Table 150. BtV2300 Register to AUX Mapping    278         | ; |

| Table 151. Audio Structure Dword 0.    282                | , |

| Table 152. Audio Structure Dword 1                        | 5 |

| Table 153.16-bit Format    284                            |   |

| Table 154.8-bit Format    284                             |   |

| Table 155.4-bit ADPCM Format with Reference    284        |   |

| Table 156. 4-bit ADPCM Format    285                      | ) |

| Table 157.2.6-bit ADPCM Format with Reference    285      | ) |

| Table 158.2.6-bit ADPCM         286                       | j |

| Table 159.2-bit ADPCM Format With Reference.    286       | i |

|                                                           |   |

| Table 201. Absolute Maximum Ratings    324                                            |

|---------------------------------------------------------------------------------------|

| Table 202. Recommended Operating Conditions.    325                                   |

| Table 203. Target DC Characteristics.    326                                          |

| Table 204. DC Characteristics for IIC_SDA and IIC_SCL I/O (Fast Mode) 326             |

| Table 205. DC Characteristics for DDC_SDA and DDC_SCL I/O (Standard Mode) 327         |

| Table 206. AC Characteristics for IIC_SDA and IIC_SCL Bus Lines (Fast Mode) 328       |

| Table 207. AC Characteristics for DDC_SDA and DDC_SCL Bus Lines (Standard Mode) . 328 |

| Table 208. Package Thermal Resistance                                                 |

| Table 209. BtV2115 Datasheet Revision History    345                                  |

# What this Document Contains

This hardware specification contains the following chapters.

- **Product Description** Provides an overview of the BtV2115 MediaStream Controller, including a summary of the PCI and VL pin assignments. For a summary of the BtV MediaStream Family of chips, refer to the beginning of this Technical Reference binder.

- **VGA Implementation** Contains a description of the compatibility and operation of the VGA within the BtV2115 controller.

- **Register Definitions** Contains the definitions of or references to all of the BtV2115 registers, including both I/O mapped and memory mapped registers.

- **CPU Address Space Apertures** Describes the programming interface to the BtV2115 MediaStream accelerator, the Media Buffer, the audio subsystem, the flash ROM, and the Yamaha 2 and 4 operator mode FM synthesizer family.

- **Configuration Registers** Contains a summary of the registers that specify operating parameters for interaction of internal and external multimedia subsystem components.

- I<sup>2</sup>C Master and Slave Controllers Specifies the programming interface between the BtV2115 and the I<sup>2</sup>C master and slave modules.

- **GUI Accelerator** Describes the CPU addressing to the GUI and defines the GUI commands registers.

- **Softvideo Player** Describes the interface between the BtV2115 software encoded video module and the BtV2487 PACDAC via the VRAM serial port.

- **CPU Host Bus Interface** Describes the VESA Local bus and PCI bus interface between the BtV2115 and the host CPU. Defines the VESA and PCI signal pins and provides timing diagrams.

- Video Input Subsystem Describes the interfaces between the BtV2115 and the BtV2811A VideoStream Decoder, and between the BtV2115 and the memory controller and VRAM via the memory bus.

- Audio Interface Describes the interface between the BtV2115 and the AudioStream subsystem.

- **Operating Specifications** Provides the operating specifications for the BtV2115, including electrical, thermal, packaging, and signal pin layout.

# BI

#### **Related Documents**

BtV2300 AudioStream Specification

BtV2811A VideoStream Decoder Specification

BtV2487 PACDAC Specification

PCI Local Bus Specification, Revision 2.0

Video Electronics Standards Association (VESA) Local Bus Specification, Version 2.0

Yamaha YMF-262 Product Information bulletin

Philips Semiconductor, Data Sheet SAA7194, Digital Video Decoder and Scalar Circuit (DESC)

Philips I<sup>2</sup>C-Bus and How to Use It

ACCESS.bus Specification - Version 2.0

Richard F. Ferraro, *Programmer's Guide to the EGA and VGA Cards*, Second Edition (Addison-Wesley Publishing Company, Inc., 1990)

Bradley Dyck Kliewer, *EGA/VGA: A Programmer's Reference Guide* (Intertext Publications, McGraw-Hill Publishing Company, New York, 1990)

# **Notation Conventions**

Notation conventions used in this book are listed below.

| Example    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VL_RESET   | The overbar above a signal or pin (or a portion of the signal or pin) indicates active-LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8'hAD      | Hexadecimal notation used by hardware designers, in the format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | <num bits="">'h<value></value></num>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

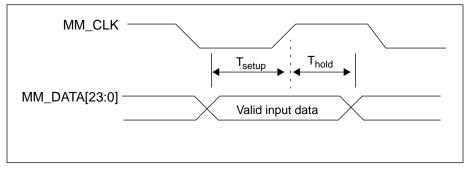

|            | Where:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |