## **LinkSwitch**—HP Family

# Energy Efficient, High-Power Off-Line Switcher With Accurate Primary-Side Regulation (PSR)

## **Product Highlights**

## EcoSmart<sup>™</sup>- Energy Efficient

- Multi-mode control maximizes efficiency over full load range

- No-load consumption below 30 mW at 230 VAC (LNK67xx)

- >75% efficiency with 1 W input at 230 VAC

- >50% efficiency with 0.1 W input at 230 VAC

#### **High Design Flexibility for Low System Cost**

- · Dramatically simplifies power supply designs

- Eliminates optocoupler and all secondary control circuitry

- ±5% or better output voltage tolerance

- 132 kHz operation reduces transformer and power supply size

- · Accurate programmable current limit

- Compensation over line limits overload power

- · Frequency jittering reduces EMI filter cost

- Fully integrated soft-start for minimum start-up stress

- 725 V MOSFET simplifies meeting derating requirements (LNK677x)

- 650 V MOSFET for lowest system cost (LNK676x/LNK666x)

- Fast transient response family option (LNK666x)

#### **Extensive Protection Features**

- · Auto-restart limits power delivery to 3% during overload faults

- Output short-circuit protection (SCP)

- Output overload/over-current protection (OPP, OCP)

- · Optional extended shutdown delay time

- · Output overvoltage protection (OVP), auto-restart or latching

- Line brown-in/out protection (line UV)

- Line overvoltage (OV) shutdown extends line surge withstand

- · Accurate thermal shutdown (OTP), hysteretic or latching

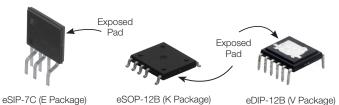

## **Advanced Green Package Options**

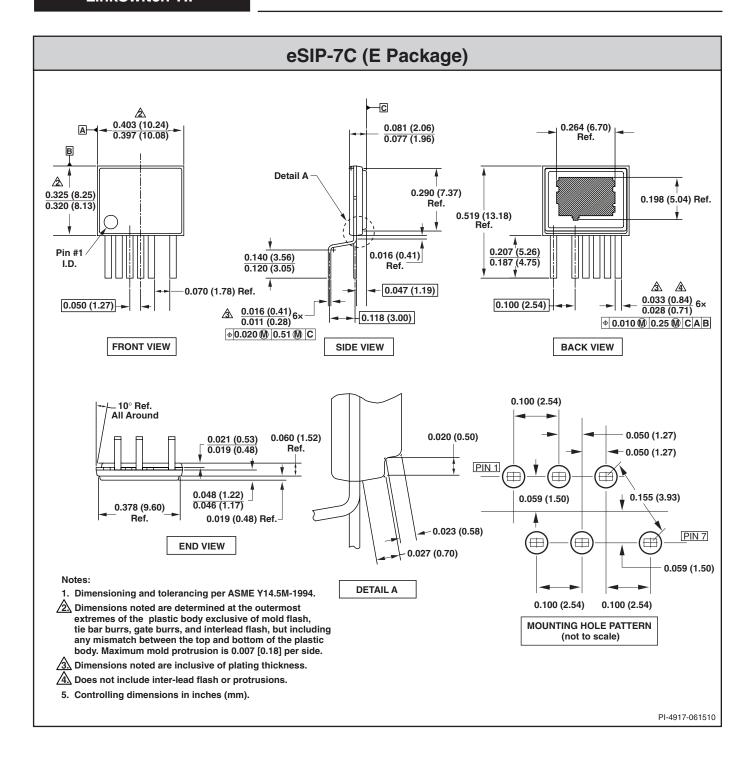

- eSIP™-7C package:

- · Vertical orientation for minimum PCB footprint

- · Simple heat sink mounting using clip or adhesive pad

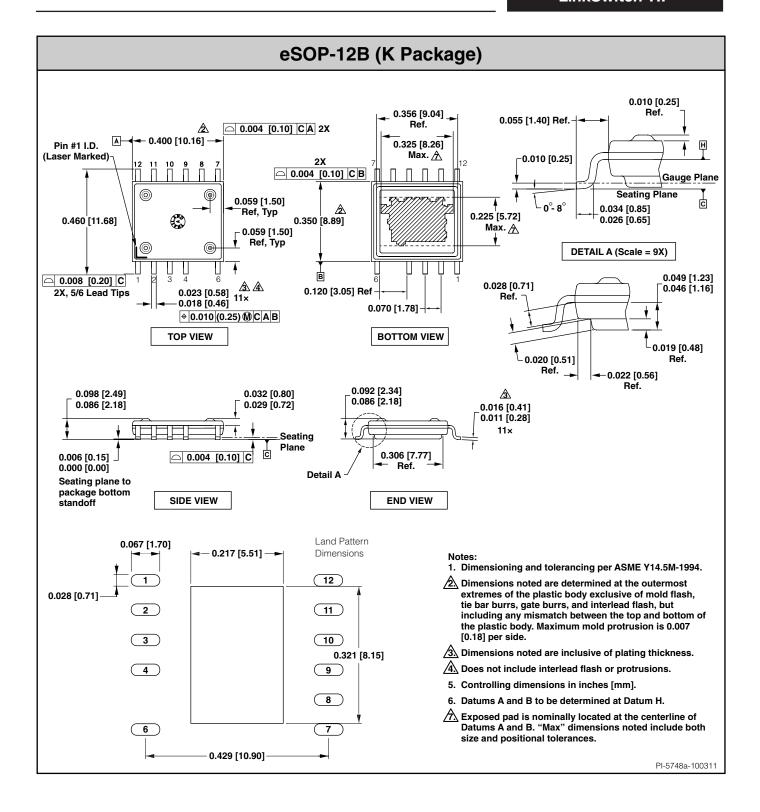

- eSOP<sup>™</sup>-12B package:

- · Low profile surface mounted for ultra-slim designs

- Heat transfer to PCB via exposed pad and SOURCE pins

- · Supports either wave or IR reflow soldering

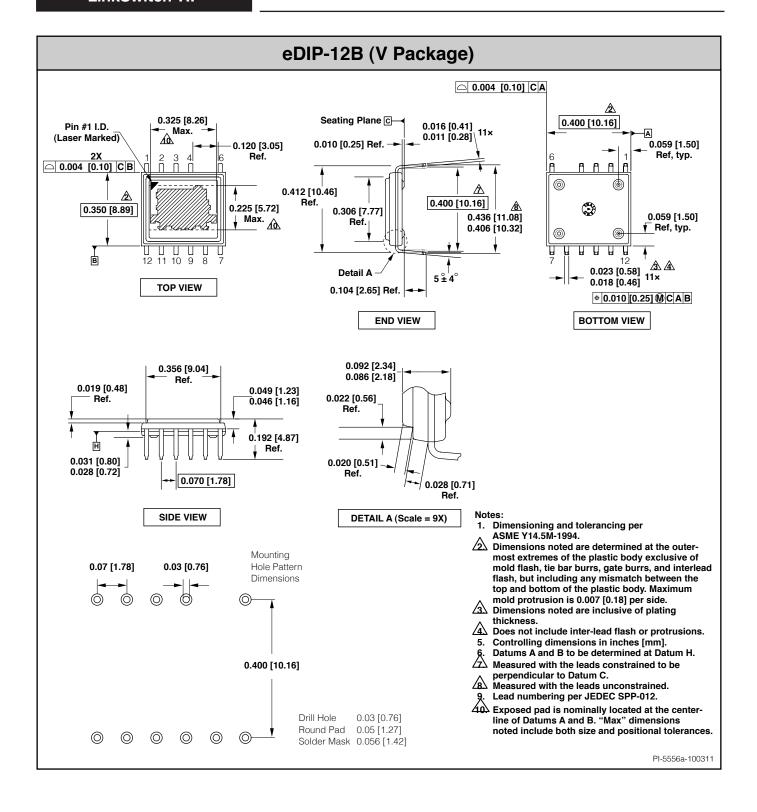

- eDIP™-12B package:

- Low profile through-hole mounted for ultra-slim designs

- Heat transfer to PCB via exposed pad or optional metal heat sink

- Extended creepage to DRAIN pin

- · Heat sink is connected to SOURCE for low EMI

- Halogen free and RoHS compliant

#### Typical Applications

- LCD Monitor and TV

- Adapter

- Appliances

- Embedded power supplies (DVD, set-top box)

- Industrial

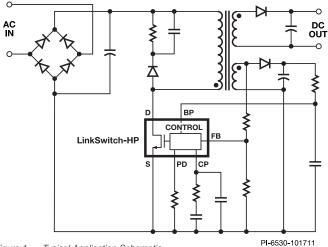

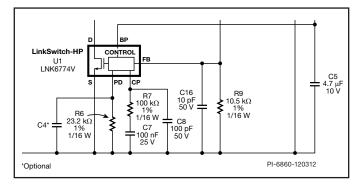

Figure 1. Typical Application Schematic.

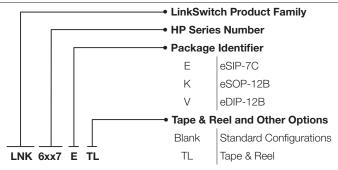

Figure 2. Package Options.

Output Power Table

| •          |                    |                   |                    |            |                   |  |

|------------|--------------------|-------------------|--------------------|------------|-------------------|--|

|            |                    | 230 VA            | C ±15%             | 85-265 VAC |                   |  |

| Product⁴   | Heat Sink          | Adapter           | Open<br>Frame      | Adapter    | Open<br>Frame     |  |

| LNK6xx3K/V | PCB-W <sup>1</sup> | 15 W              | 25 W               | 9 W        | 15 W              |  |

| LNK6xx3K   | PCB-R <sup>2</sup> | 21 W              | 35 W               | 12 W       | 21 W              |  |

| LNK6xx3E   | Metal              | 21 W              | 35 W               | 13 W       | 27 W              |  |

| LNK6xx4K/V | PCB-W <sup>1</sup> | 16 W              | 28 W               | 11 W       | 20 W              |  |

| LNK6xx4K   | PCB-R <sup>2</sup> | 22 W              | 39 W               | 15 W       | 28 W              |  |

| LNK6xx4E   | Metal              | 30 W              | 47 W               | 20 W       | 36 W              |  |

| LNK6xx5K/V | PCB-W <sup>1</sup> | 19 W              | 30 W               | 13 W       | 22 W              |  |

| LNK6xx5K   | PCB-R <sup>2</sup> | 26 W              | 42 W               | 18 W       | 31 W              |  |

| LNK6xx5E   | Metal              | 40 W              | 593 W              | 26 W       | 45 W              |  |

| LNK6xx6K/V | PCB-W <sup>1</sup> | 21 W              | 34 W               | 15 W       | 26 W              |  |

| LNK6xx6K   | PCB-R <sup>2</sup> | 30 W              | 48 W               | 22 W       | 37 W              |  |

| LNK6xx6E   | Metal              | 60 W              | 883 W              | 40 W       | 68 <sup>3</sup> W |  |

| LNK6xx7K/V | PCB-W <sup>1</sup> | 25 W              | 41 W               | 19 W       | 30 W              |  |

| LNK6xx7K   | PCB-R <sup>2</sup> | 36 W              | 59 W               | 27 W       | 43 W              |  |

| LNK6xx7E   | Metal              | 85 <sup>3</sup> W | 117 <sup>3</sup> W | 55 W       | 90 <sup>3</sup> W |  |

Table 1. Output Power Table.

#### Notes

- 1. PCB heat sink with wave soldering.

- 2. PCB heat sink with IR reflow soldering (exposed pad thermally connected to PCB).

- 3. Maximum power specified based on proper thermal dissipation.

- 4. Packages: E: eSIP-7C, K: eSOP-12B, V: eDIP-12B. See Table 2 for all device options.

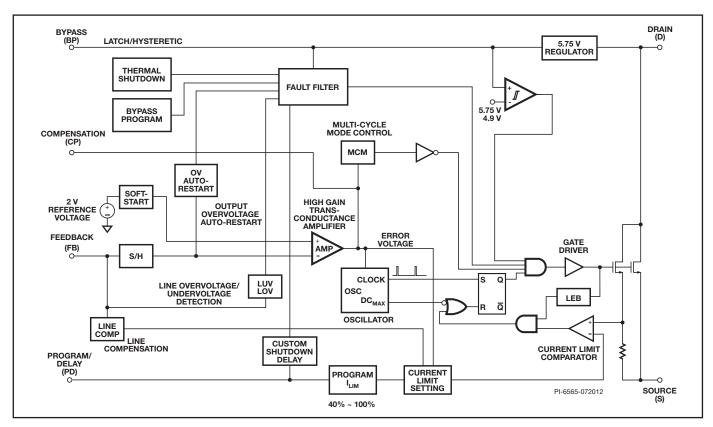

Figure 3. Block Diagram.

| LNK          | <u>6</u> | <u>X</u>                                                       | <u>X</u>                                                 | <u>X</u>       | E/V/K                                   |

|--------------|----------|----------------------------------------------------------------|----------------------------------------------------------|----------------|-----------------------------------------|

| Part Number  | Series   | T <sub>MCM(OFF)</sub> <sup>2</sup><br>6 = 0.5 ms<br>7 = 4.0 ms | BV <sub>DSS</sub> <sup>1</sup><br>6 = 650 V<br>7 = 725 V | Power          | Packages                                |

| LNK6663E/V/K |          | 0.5 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6664E/V/K |          | 0.5 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6665E/V/K |          | 0.5 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6666E/V/K |          | 0.5 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6667E/V/K |          | 0.5 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6763E/V/K |          | 4.0 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6764E/V/K |          | 4.0 ms                                                         | 650 V                                                    | <u> </u>       | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6765E/V/K | 6        | 4.0 ms                                                         | 650 V                                                    | Device<br>Size | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6766E/V/K |          | 4.0 ms                                                         | 650 V                                                    | SIZE           | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6767E/V/K |          | 4.0 ms                                                         | 650 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6773E/V/K |          | 4.0 ms                                                         | 725 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6774E/V/K |          | 4.0 ms                                                         | 725 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6775E/V/K |          | 4.0 ms                                                         | 725 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6776E/V/K |          | 4.0 ms                                                         | 725 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

| LNK6777E/V/K |          | 4.0 ms                                                         | 725 V                                                    |                | eSIP-7C (E), eDIP-12B (V), eSOP-12B (K) |

Table 2. Device Part Numbers and Options.

<sup>1.</sup> Minimum breakdown voltage at  $T_J = +25$  °C.

<sup>2.</sup>  $T_{MCM(OFF)} = 0.5$  ms for fastest transient response,  $T_{MCM(OFF)} = 4$  ms for <30 mW no-load input power.

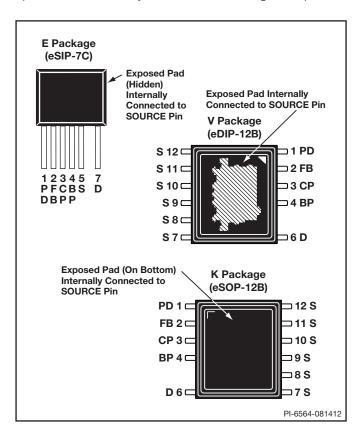

#### **Pin Functional Description**

### BYPASS (BP) Pin:

An external bypass capacitor is connected to this pin for the internally generated 5.75 V supply. Based on the connected capacitance determined at start-up, it will provide either auto-restart or latching shutdown option dependant on the fault condition. Please see Table 3.

#### COMPENSATION (CP) Pin:

This pin is the output of transconductance amplifier. An RC compensation network on this pin provides control loop compensation.

## DRAIN (D) Pin:

This pin is the high-voltage power MOSFET drain connection. It also provides internal operating current for start-up until output is in regulation.

## FEEDBACK (FB) Pin:

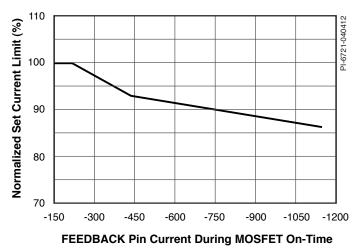

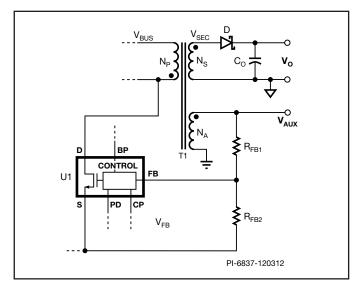

The FEEDBACK pin is used to sense output and input voltage by sensing the auxiliary winding voltage. During MOSFET on-time, the current out of the FEEDBACK pin is sensed to detect the line voltage. During the secondary rectifier conduction time, the feedback voltage is proportional to the output voltage via the turns ratio between the bias and secondary windings.

#### PROGRAM (PD) Pin:

This MULTI-FUNCTIONAL pin sets device current limit and optional shutdown delay time extension. During start-up, the

Figure 4. Pin Configuration.

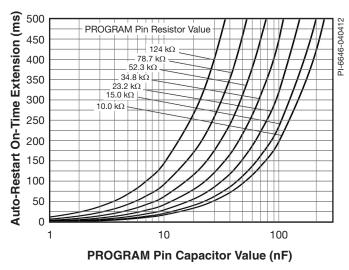

internal circuit decodes the current limit based on resistor loaded on the PROGRAM pin. Please see Table 4. It can also be used for optionally extending shutdown delay time by changing the capacitance on the pin. See Figure 6.

## SOURCE (S) Pin:

This pin is the power MOSFET source connection. It is also the ground reference for the BYPASS, FEEDBACK, PROGRAM and COMPENSATION pins.

#### **Functional Description**

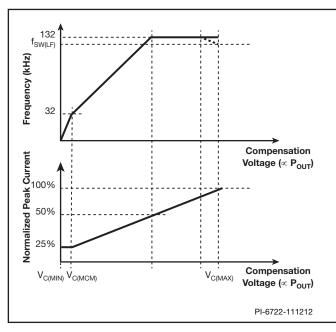

A LinkSwitch-HP device monolithically integrates a controller and high-voltage power MOSFET into one package. It has a newly developed analogue control scheme, which enables continuous conduction mode (CCM), primary side regulated (PSR) power supplies up to 90 W without the efficiency limitation of DCM or audible noise. It uses an enhanced peak current mode PWM control scheme with multi-mode operation. The multi-mode control engine uses the error amplifier output signal voltage at the COMPENSATION pin to set the operating peak current and switching frequency to maintain the output voltage in regulation as shown in Figure 5. For COMPENSATION pin voltages lower than  $V_{\text{c(MCM)}}$  (typ. 1.25 V) the device enters multi-cycle modulation (MCM) with a fixed peak current of 25% of the programmed current limit. Several innovative improvements have been added to the peak current mode control to allow primary side regulated CCM operation with no instability. The device meets less than 30 mW input power with no-load at high-line (LNK67xx families).

It also offers extensive built-in features:

- External current limit selection.

- Optional programmable shutdown delay time extension.

- Optional remote On/Off.

- Optional fast AC reset.

- Primary-side sensed output overvoltage protection (OVP) .

- Lost regulation protection during output overload or short-circuit (auto-restart).

- Internal current limit over line compensation for constant overload power over line.

- High-voltage bus overvoltage sense (line OV) for extended line surge withstand.

- High-voltage bus undervoltage sense (line UV) for brown-in/ out protection.

- Accurate over-temperature protection (OTP).

- Output OVP/OCP/OTP shutdown type selection (hysteretic/ latching).

- Optional external latching shutdown input (current threshold)

- Cycle-by-cycle current limit control.

## Regulator/Shunt Voltage Clamp

The internal 5.75 V regulator charges the bypass capacitor connected to the BYPASS pin to 5.75 V by drawing a current from DRAIN whenever the power MOSFET is off. When the power MOSFET is on, the device operates from the energy stored in the bypass capacitor. In addition, there is a shunt regulator clamping the bypass at 6.4 V when supply current is provided by a bias winding through an external resistor. This makes the device insensitive to bias winding voltage variations.

Figure 5. Compensation Pin Characteristics (Multi-Mode Operation).

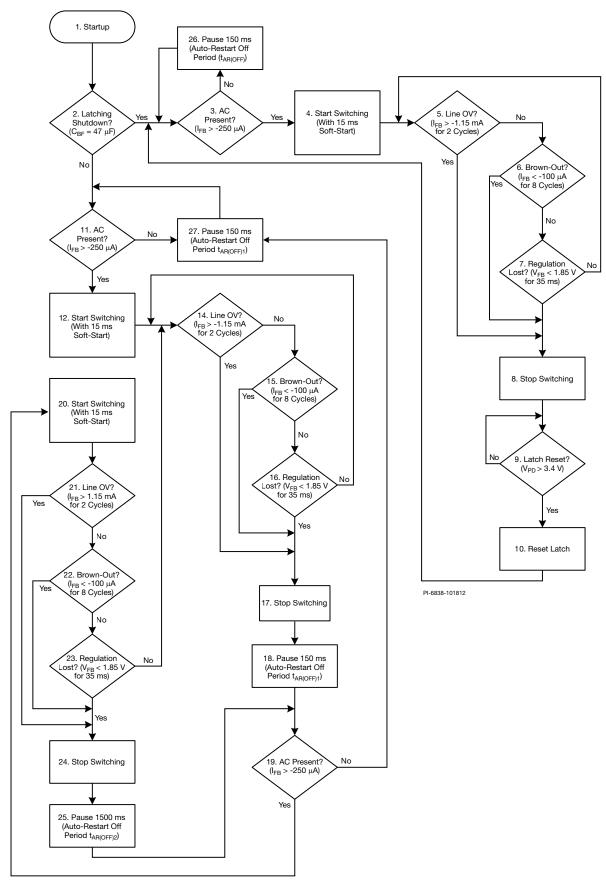

#### Auto-Restart

In the event of an open-loop fault (no connection between the feedback winding and the feedback divider network or the FEEDBACK pin to the feedback network), the sensed current out of FEEDBACK pin will be zero during MOSFET on-time. the device enters into line brown-out protection (line UV). In the event of output short-circuit or overload condition, the device enters into auto-restart mode. Auto-restart minimizes the power dissipation under fault conditions, the device will turn on and off at duty cycle of typically 3% as long as the fault condition persists. In auto-restart switching is disabled for  $t_{\mbox{\tiny ARIOFFI1}}$ (typ. 150 ms) when the FEEDBACK pin voltage has dropped below the auto-restart threshold  $V_{\mbox{\tiny FB(AR)}}$  for the shutdown default delay time t<sub>AR(ON)</sub> (typ. 35 ms). After this period switching is enabled again with the device entering soft-start (typ. 15 ms). For the first auto-restart off-period switching is disabled for a reduced time t<sub>ARIOFF12</sub> (typ. 1500 ms) to reduce the power supply restart time during line cycling. Optionally the default shutdown delay time can be extended by adding a capacitor to the PROGRAM pin.

## **Hysteretic Thermal Shutdown**

The thermal shutdown circuitry senses the controller die temperature. The threshold is set at 142 °C with a 75 °C hysteresis (both typical). Once the device temperature rises above 142 °C, the power MOSFET is disabled and remains disabled until the die temperature falls by 75 °C, at which point the device is re-enabled. The large hysteresis maintain the average temperature below the temperature rating of low cost CEM type PCB material in most cases.

### Safe Operating Area (SOA) Protection

The device features a safe operating area (SOA) protection mode which disables MOSFET switching for 4 consecutive cycles in the event the peak switching current reaches the

current limit in less than time  $t_{\mbox{\tiny ON(SOA)}}.$  This prevents excessive drain currents during start-up and output short-circuit conditions by providing additional time for the primary inductance to reset. The SOA protection is disabled when the output voltage is within 7.5% of regulation voltage.

#### Sample and Hold (S/H)

The sample and hold block senses the output voltage at auxiliary winding during secondary rectifier on-time. The FEEDBACK pin voltage is sampled after the turn-off of the internal switch to compensate for diode conduction time differences. Sampling time increases monotonically from 1.2 µs at no or light load to 2.5 µs at full load. Sampled voltage is held until the next clock cycle. The output of S/H is fed to the error amplifier, once in regulation the sampled voltage is 2 V.

#### BYPASS (BP) Programming

This feature selects either hysteretic or latching OVP/OCP and OTP protection based on capacitor loading on the BYPASS pin.

The shutdown type is determined at the device power-up as shown in Table 3.

| C <sub>BP</sub>          | <b>0.47</b> μ <b>F</b> | <b>4.7</b> μ <b>F</b> | <b>47</b> μ <b>F</b> |

|--------------------------|------------------------|-----------------------|----------------------|

| OVP                      | Latching               | Auto-Restart          | Latching             |

| Lost Regulation (SC, OC) | Auto-Restart           | Auto-Restart          | Latching             |

| OTP                      | Latching               | Hysteretic            | Latching             |

Shutdown Type vs. Value of BYPASS Pin Capacitance. Table 3.

#### **Current Limit Setting**

During power-up the cycle-by-cycle current limit is determined by measuring the resistor value connected to the PROGRAM pin by the measurement is performed by applying 1.25 V (see Figure 10). The current limit can be set between 40% to 100% in steps of 10% as shown in Table 4. After the current limit is set the PROGRAM pin voltage is reduced to ~0 in order to minimize power dissipation.

| I <sub>PD</sub> | $\mathbf{R}_{\mathtt{PD}}$ | I <sub>LIMIT(NORM)</sub> | I <sub>PD</sub> | $\mathbf{R}_{\mathtt{PD}}$ | I <sub>LIMIT(NORM)</sub> |

|-----------------|----------------------------|--------------------------|-----------------|----------------------------|--------------------------|

| μΑ              | kΩ                         | %                        | μΑ              | kΩ                         | %                        |

| 10              | 124                        | 100                      | 54              | 23.2                       | 60                       |

| 16              | 78.7                       | 90                       | 83              | 15.0                       | 50                       |

| 24              | 52.3                       | 80                       | 125             | 10.0                       | 40                       |

| 36              | 34.8                       | 70                       |                 |                            |                          |

Table 4. Current Limit Selection vs. Program Pin Resistor Value.

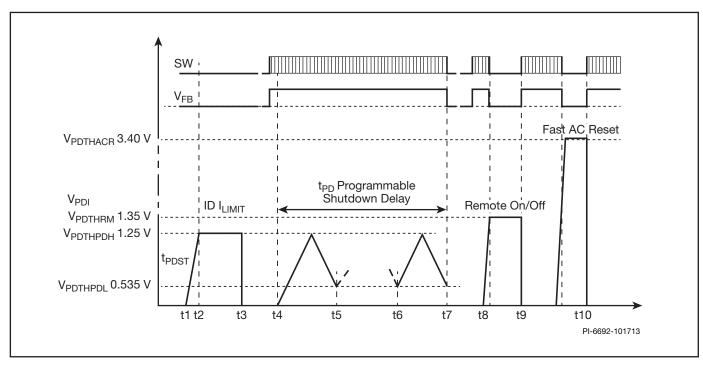

#### Programmable Shutdown Delay

The default auto-restart shutdown delay time  $\rm t_{\rm SD(AR)}$  (typ. 35 ms) can optionally be extended by connecting a capacitor to the PROGRAM pin. Once a lost regulation fault is detected the PROGRAM pin voltage is cycled 128 times between  $V_{\text{PD(DL)}}$  (typ. 0.5 V) and  $V_{PD(DU)}$  (typ. 1.2 V) as shown in Figure 10. Figure 6 depicts the relationship between extended shutdown delay time, added PROGRAM pin capacitor and current limit programming resistor.

#### Remote On/Off and Fast AC Reset

The PROGRAM pin can be used to turn on/off the device remotely. If the voltage on the pin is set to 1.35 V externally, the device stops switching. After releasing the PROGRAM pin the PROGRAM pin device commences switching when the voltage drops below 0.535 V.

Figure 6. Optional Shutdown Time Extension Programming.

The PROGRAM pin can also be used to reset the device latch after a latching OVP or OTP event. If the voltage on the pin is set to 3.4 V externally, the device latch is reset. Once the voltage drops below 0.535 V, device will start switching.

Figure 7. Current Limit Compensation Over Line.

## High-Voltage Bus Sensing

LinkSwitch-HP senses indirectly the HV voltage bus  $V_{\text{BUS}}$  during the power MOSFET on-time by monitoring the current flowing out of the FEEDBACK pin. During the MOSFET on-time the voltage across the auxiliary winding is proportional to the voltage across the input winding. The current flowing through resistor  $R_{\text{FB1}}$  (see Figure 8) is therefore representing  $V_{\text{BUS}}$ . Indirect line sensing minimizes power dissipation and is used for line UV or line OV protection and current limit compensation over line.

At power-up the current out of the FEEDBACK pin has to exceed the line undervoltage turn-on threshold (brown-in) current I\_{FB(UVREF)} = -250  $\mu A$  (typ.) before switching is enabled. During normal operation switching is disabled if the FEEDBACK pin current falls below the line undervoltage turn-off threshold (brown-out) current I\_{FB(UVOFF)} = -100  $\mu A$  (typ.) for at least 8 consecutive switching cycles. After switching has ended, the device enters auto-restart. The applicable auto-restart off-period t\_AR(OFF) = 150 ms (typ.).

Figure 8. Indirect High-Voltage Bus Sensing.

Switching is also stopped if the FEEDBACK pin current exceeds the line overvoltage threshold current  $I_{FB(OV)} = -1.15$  mA (typ.) for at least 2 consecutive switching cycles.

#### **Current Limit Compensation Over Line**

The high-voltage bus is sensed by means of measuring the current out of the FEEDBACK pin during the MOSFET on-time. To limit available overload power over line the set current limit is compensated as shown in Figure 7. The compensation is disabled at peak currents below 50% of the set current limit, and is re-enabled at 62.5% of the set current limit.

#### Soft-Start

A digital soft-start is implemented to reduce component stress at power supply start-up. The internal reference voltage will ramp up to 2 V during  $t_{\text{SOFT}}$  (typ. 15 ms) at start-up. The loop will typically close (output reaches regulation) during this time to ensure smooth output voltage rise.

#### **Fault Filter**

This is the digital filter to handle all the fault conditions including line overvoltage, line undervoltage, output overvoltage, and output undervoltage, thermal shutdown as well as package level fault (pin open-circuit or pin to pin short-circuit).

#### Transconductance Amplifier

The controller uses a high gain (typ. 70 dB) transconductance amplifier to ensure exceptional output regulation.

Figure 9. Line Sensing and Auto-Restart Flow Chart.

Figure 10. PROGRAM (PD) Pin Timing Diagram.

#### OSC

This is an adjustable frequency oscillator. Based on error voltage, the frequency will adjust from 32 kHz at light load to 132 kHz at heavy load. The oscillator employes  $\pm 5$  kHz frequency jitter to reduce EMI levels.

## **Current Limit Comparator**

This is a high-speed current limit comparator. It compares the current from the power MOSFET to the internal current reference. Once the current reaches the threshold the MOSFET on-cycle is terminated.

#### Multi-Cycle Modulation (MCM)

When voltage on COMPENSATION pin reaches  $V_{\text{C(MCM)}}$  (about 1.25 V) the peak drain current is reduced to 25% of programmed value and the switching frequency approaches  $f_{\text{MCM}} = 32 \text{ kHz}$  (typical). During MCM operation the controller intelligently

maintains a relatively high output sampling rate while reducing the average switching frequency to keep the output voltage in regulation. Switching at 25% of the set current limit reduces the transformer core flux density significantly. This and the intelligent MCM operation reduce audible noise well below acceptable levels. LNK666x has a maximum MCM off-time  $T_{\text{MCM(OFF)}} = 0.5$  ms (typ.). The high minimum output sampling rate provides excellent transient load response from 0% to 50% or 100% of nominal load while offering typically below 100 mW no-load input power.

LNK67xx has a maximum MCM off-time  $T_{\text{MCM(OFF)}} = 4$  ms (typ.). The lower minimum output sampling rate enables designs below 30 mW no-load input power while providing fair transient load performance for load steps from 0% to 50% or 100% of nominal load.

## **Applications Example**

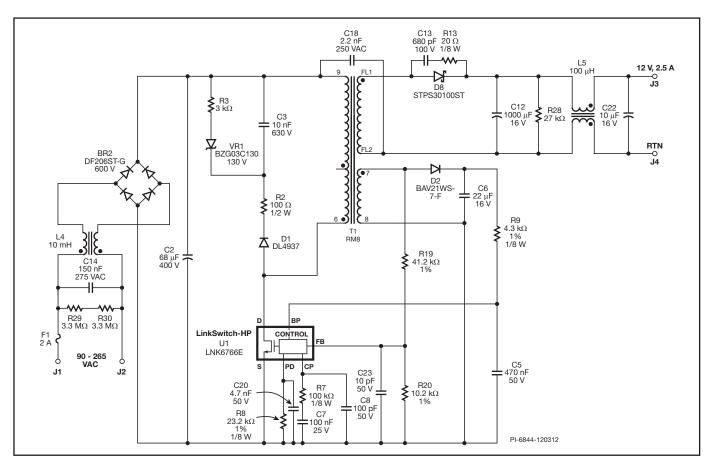

#### 30 W, 12 V Universal Adapter

The circuit shown in Figure 11 is a high efficiency universal input 30 W, 12 V output adapter using the LNK6766E.

The supply uses primary winding coupled sensing for the following features: output regulation, line undervoltage lockout, input and output OVP. With primary winding sense there is no need for an external secondary referenced error amplifier such as a TL431 and optocoupler. The winding sense of bus voltage also eliminates the need for direct input voltage sensing which requires more components and is more dissipative than winding sense method.

Output regulation is  $\pm 5\%$ , active-on efficiency is 86% and no-load input power is less than 30 mW.

The rectified and filtered input voltage is applied to the primary winding of T1. The other side of the primary is driven by the integrated power MOSFET in U1. Diode D1, C3, R2, R3 and VR1 comprise the clamp circuit, limiting the leakage inductance turn-off voltage spike to safe value. Zener diode VR1 also helps to reduce input power consumption during no-load conditions.

Start-up of the power supply is initiated by sensing the forward negative pulse current from feedback winding through R19 into

the FEEDBACK pin. This sensing is accomplished by periodically turning on the power MOSFET to sense input voltage condition with very short low frequency sampling pulses. During the forward pulse sampling time the FEEDBACK pin is held to zero volts by an internal clamp. When negative forward pulse current exceeds 250  $\mu\text{A}$ , LinkSwitch-HP for two consecutive switching cycles will initiate start-up with a soft-start sequence that reduces component stress and allows the output to rise in a smooth monotonic manner. The desired input voltage for start-up is determined by the turns ratio of primary winding to feedback winding and the value of R19.

Regulation is accomplished by sampling the feedback winding during flyback period through the resistor divider R19 and R20 through FEEDBACK pin. This sampled voltage is compared to an internal error amplifier threshold of 2 V. The value of R19 is already determined by the line undervoltage function so the output regulation point is determined by setting the proper value for R20.

The loop compensation is provided by the network from COMPENSATION pin to ground. In the case above, a low frequency to mid frequency gain of 20 dB for the error amplifier is established by R7 and C7. Capacitor C8 functions essentially as a noise filter and is typically 100 pF. There is also an internal 16 kHz filter within the device. It is advised to limit R7 to no greater than 260 k $\Omega$  to avoid stability and noise sensitivity.

Figure 11. Schematic of a Universal Input 30 W, 12 V, 2.5 A Adapter.

## LinkSwitch-HP

The transient load response is dependent on the loop gain and minimum switching frequency. The values of R7 and C7 shown here typically give good transient response for most designs. When the supply is at no-load, the minimum switching frequency at no-load will create a delay to respond to any step load event during the off-time. In the case above, the minimum frequency is 250 Hz so there is a potential 4 ms delay to response. If a faster response is desired from no-load initial condition there is the option to use the LNK666x which has a minimum frequency of 2 kHz. There is a trade-off in using this family as no-load input power will be slightly higher and a smaller pre-load resistor will be required.

In order to have good efficiency, regulation performance and stability, the transformer leakage inductance should be minimized. Low leakage will minimize ringing on the sense winding which can create an error in the feedback sampling. The example above uses split primary winding technique to lower leakage inductance. Leakage inductance should not be greater than 2% of nominal primary inductance and 1% is typically the desirable target value.

Resistor R28 serves as a pre-load resistor to minimize output voltage rising in no-load condition. The pre-load resistor should be no smaller than is necessary to maintain output within specification limits to minimize added dissipation. In this example, the added pre-load dissipation is only 4.8 mW.

LinkSwitch-HP provides an internal current source to bias the BYPASS pin which is necessary for start-up. When the supply is operating and in regulation an external bias is provided from the rectified flyback voltage from the bias winding (D2 and C6). Resistor R9 is sourced from the bias voltage across C6 into the

BYPASS pin to provide external bias. The external bias current should set via R9 to be at least 500  $\mu A$  to guarantee the internal current source of LinkSwitch-HP is turned off as this will allow the supply to operate more efficiently, especially at light load. For best no-load performance the external supply voltage across C6 should be minimized (typically 8-9 V) and the current into the BYPASS pin set by R9 should be as low as possible. Input overvoltage protection is done through sensing the negative forward pulse of feedback winding. When the negative forward voltage is sufficiently high to produce more than 1.15 mA current into the FEEDBACK pin, for 2 consecutive on-cycles the device will stop switching for auto-restart delay period.

Output overvoltage protection is achieved by sensing the flyback pulse through the FEEDBACK pin. When the FEEDBACK pin sees 2.5 V or greater for 16 consecutive cycles, the supply will latch off. If non-latching OVP is desired then changing C5 from 0.47  $\mu$ F to 4.7  $\mu$ F will change fault mode accordingly (see Table 3 for details).

OCP protection is accomplished by sensing when the output drops below 0.925 of nominal regulation value for a duration greater than specified delay time. In the example above, the total delay time is about 50 ms. Capacitor C20 extends the default internal delay time of 35 ms (see Figure 6 for details). The latching shut-off option is used in the design above.

The primary current limit of LinkSwitch-HP can be adjusted by selecting the value for R8 (see Table 4 for details). For this design 60% of maximum current limit was chosen. A lower current limit setting is typical for an adapter where lower  $R_{\mbox{\tiny DS(ON)}}$  is desirable for higher efficiency and also lower thermal rise of LinkSwitch-HP.

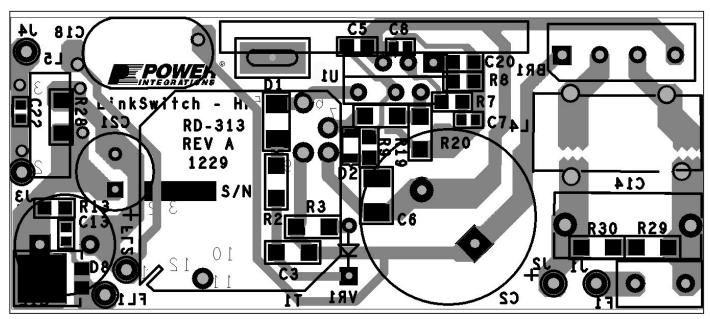

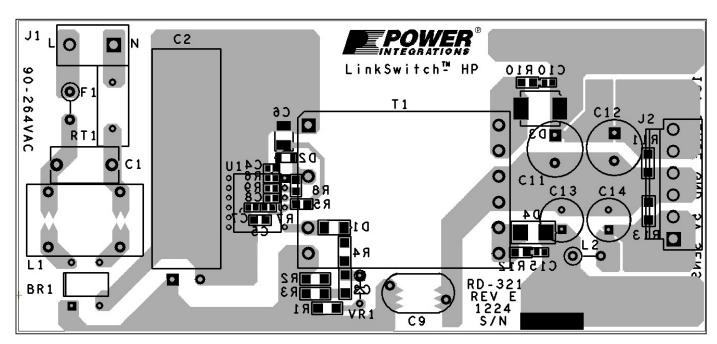

#### Layout Considerations for eSIP-7C Package

Figure 12 is the layout for a 30 W adapter shown in the schematic Figure 11. An eSIP-7C package is used as indicated by the suffix in LNK6766E which allows the use of a stand-up heat sink. The mounting pin for the heat sink should be electrically isolated. It can be seen that the primary return trace wraps around the LinkSwitch-HP device which acts as a shield around the critical external control related components of LinkSwitch-HP. These components include R7, R8, R19, R20 and C5, C8, C20. Of particular importance is placing the bypass capacitor C5 and COMPENSATION pin noise filter capacitor C8 as close as possible to SOURCE pin with very short trace lengths to COMPENSATION and BYPASS pins as shown. If an electrolytic capacitor is selected as the bypass capacitor (C5) then an additional 100 nF (C5) ceramic must also be fitted. The ground trace wrap, tight layout and single point grounding to SOURCE pin of these components avoids having noise related issues during peak loads or during line transient such as surge or ESD events.

Another consideration for ESD and line surge is the primary-side termination of the Y capacitor. The Y capacitor C18 should

be tied to the positive terminal of the bulk capacitor C2 in order to route the potential of high currents away from the more sensitive primary return traces.

Because of the tight layout common to adapter applications, this design uses triple insulated wire and flying leads for output winding termination to avoid secondary arcing to core during ESD events.

The trace connecting the drain to transformer should be very short and the primary clamp circuitry should be grouped together and away from the more sensitive components. The bias winding return and return of bias capacitor C6 should be routed separately to the negative terminal of the input capacitor C2 away from SOURCE pin.

The secondary rectifying loop that includes the secondary winding, the output diode D8, and the first output capacitor C13 should be as tight as possible to minimize adding series inductance which can reduce high load efficiency and degrade the quality of regulation.

Figure 12. Layout for 30 W Adapter Using a eSIP-7C Package (View From Bottom Copper Layer).

#### Layout Considerations for eDIP-12B package

The schematic extract in Figure 13 is an example of LinkSwitch-HP used in a dual output LCD monitor supply using eDIP-12B package. In this design the exposed metal tab on the topside of package is left open (no heat sink). The SOURCE pins of LinkSwitch-HP provide heat sinking through connection to the source copper pad of PCB. This technique is adequate for device dissipation up to 0.85 W (1/2 square inch of copper area required). The layout guidelines described for eSIP-7C are the same for eDIP-12B with an added consideration about sensitive component layout. The return referenced components C4, C8, C16, R9, R7 must be placed directly under the LinkSwitch-HP package as shown in Figure 14. This requires that these particular components be SMD type as this allows an ideal noise-immune layout.

#### **Output Power Table Assumptions**

- 12 V output.

- · Schottky rectification.

- 82% efficiency.

- V<sub>OR</sub> = 135 V.

- $K_p = 0.4$  for 85-265 VAC input and  $K_p = 0.6$  for 195-265 VAC input.

- $V_{MIN}$  = 100 V for 85-265 VAC input and  $V_{MIN}$  = 250 V for 195-265 VAC input.

- 0.85 W device dissipation for open frame designs with PCB heat sink.

## **Quick Design Checklist**

All LinkSwitch-HP designs should be verified on the bench particularly for specified worst-case stress conditions. The following set of tests are strongly recommended:

- Maximum drain voltage Verify that VDS does not exceed 675 V for LNK677X series and 600 V for LNK6X6X series. This gives a 50 V margin for design variations.

- 2. Under all conditions, the maximum Drain current should be below the specified absolute maximum ratings.

- 3. Thermal check At rated maximum output power, minimum input voltage and maximum ambient temperature, verify that the maximum allowed temperature is not exceeded for any component in the design. Of particular importance is checking the temperature rise of the major power conversion components such as transformer, output diodes, input bridge, primary clamp circuit and LinkSwitch-HP. Under the stated conditions above, LinkSwitch-HP tab temperature should not exceed 110 °C.

Figure 13. 17 W LCD Monitor Supply (+18 V, +5 V).

Figure 14. Layout for LCD Monitor Supply Using eDIP-12B Package.

## LinkSwitch-HP

#### Absolute Maximum Ratings(3)

| DRAIN Pin Voltage              | 0.3 V to 725 V (677x)                        |

|--------------------------------|----------------------------------------------|

| DRAIN Pin Voltage              | -0.3 V to 650 V (666x/676x)                  |

| DRAIN Pin Peak Current:        | 1.6 x I <sub>LIMIT(TYP)</sub> <sup>(1)</sup> |

| BYPASS Pin Voltage             | 0.3 V to 9 V                                 |

| BYPASS Pin Current             | 100 mA                                       |

| FEEDBACK Pin Voltage           | 0.3 V to 9 V <sup>(2)</sup>                  |

| COMPENSATION Pin Voltage       | 0.3 V to 9 V                                 |

| PROGRAM/DELAY Pin Voltage      | 0.3 V to 9 V                                 |

| Storage Temperature            | 65 °C to 150 °C                              |

| Operating Junction Temperature | 40 °C to 150 °C(4)                           |

#### Notes:

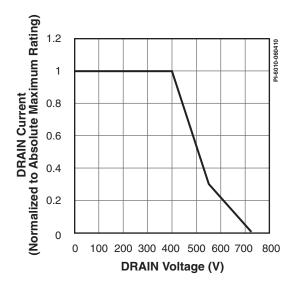

- 1. Peak DRAIN current is allowed while the DRAIN voltage is simultaneously less than 400 V.

- 2. -1 V for current pulses ≤5 mA out of the pin and a duration of ≤500 ns.

- Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect product reliability.

- 4. Normally limited by internal circuitry.

## **Thermal Resistance**

| Thermal Resistance: | E Package                                |                                                                          |

|---------------------|------------------------------------------|--------------------------------------------------------------------------|

|                     | (θ , , )                                 | 105 °C/W <sup>(1)</sup>                                                  |

|                     | (θ <sub>1</sub> )                        |                                                                          |

|                     | K Package                                |                                                                          |

|                     | (θ , )                                   | 45 °C/W <sup>(3)</sup> , 38 °C/W <sup>(4)</sup>                          |

|                     | (θ ο ο ο ο ο ο ο ο ο ο ο ο ο ο ο ο ο ο ο | 45 °C/W <sup>(3)</sup> , 38 °C/W <sup>(4)</sup><br>2 °C/W <sup>(2)</sup> |

|                     | V Package                                |                                                                          |

|                     | (θ)                                      | 74 °C/W <sup>(3)</sup> , 63 °C/W <sup>(4)</sup>                          |

#### Notes:

- 1. Free standing with no heat sink.

- 2. Measured at the back surface of tab.

- Soldered (including exposed pad for K package) to typical application PCB with a heat sinking area of 0.36 sq. in. (232 mm²), 2 oz. (610 g/m²) copper clad.

- Soldered (including exposed pad for K package) to typical application PCB with a heat sinking area of 1 sq. in. (645 mm²), 2 oz. (610 g/m²) copper clad.

| $(\Theta^{JC})$                                  |                          | 74 °C/VV®, 63 °C/V<br>2 °C/V  | $V_{(2)}^{(4)}$ 2 oz. (610 g/m <sup>2</sup> )                                    | ) copper cla | d.   |     | ( //  |

|--------------------------------------------------|--------------------------|-------------------------------|----------------------------------------------------------------------------------|--------------|------|-----|-------|

| Parameter                                        | Symbol                   | SOURCE = 0 V;                 | <b>litions</b> $\Gamma_J = -40 \text{ to } 125 ^{\circ}\text{C}$ wise Specified) | Min          | Тур  | Max | Units |

| <b>Control Functions</b>                         |                          |                               |                                                                                  |              |      |     |       |

| Switching Frequency                              | f <sub>osc</sub>         | Average value                 | e, T <sub>J</sub> = +25 °C,                                                      | 120          | 132  | 136 | kHz   |

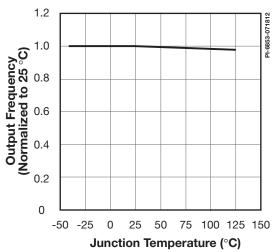

| Switching Frequency<br>Temperature Variation     | $\Delta f_{	extsf{OSC}}$ | 0 °C ≤ T <sub>J</sub> ≤ +100  | O°C, See Note A                                                                  |              |      | ±10 | %     |

| Frequency Jitter<br>Deviation                    | Δf                       | $f_{OSC} = 1$                 | 28 kHz                                                                           |              | ±5   |     | kHz   |

| Frequency Jitter<br>Modulation Rate              | f <sub>M</sub>           |                               |                                                                                  |              | 250  |     | Hz    |

| Maximum Duty Cycle                               | DC <sub>MAX</sub>        | $V_{FB} < V_{FB(REF)}$        | T <sub>J</sub> = +25 °C                                                          | 62           | 64   | 66  | %     |

| Maximum Duty Cycle<br>Temperature Variation      | $\Delta DC_{MAX}$        | $V_{FB} = V_{FB(REF)}$        | See Note A<br>0 °C ≤ T <sub>J</sub> ≤ +100 °C                                    |              |      | +2% | %     |

| Minimum Peak Current to Set Current Limit Ratio  | k <sub>PS</sub>          |                               | -25 °C<br>= di/dt <sub>((LIMIT)</sub>                                            | 22.5         | 25   |     | %     |

| Multi-Cycle<br>Modulation Switching<br>Frequency | f <sub>MCM</sub>         | $T_J = A$                     | -25 °C                                                                           | 25           | 32   |     | kHz   |

| Multi-Cycle                                      | _                        | T .05 %                       | LNK666x                                                                          |              | 0.5  |     |       |

| Modulation Max Off-Time                          | T <sub>MCM(OFF)</sub>    | $T_J = +25  ^{\circ}\text{C}$ | LNK67xx                                                                          |              | 4    |     | - ms  |

| Soft-Start Time                                  | t <sub>soft</sub>        | $T_J = A$                     | -25 °C                                                                           |              | 15   |     | ms    |

| Auto-Restart Shut-<br>Down Default Delay         | t <sub>SD(AR)</sub>      | T <sub>J</sub> = +25 °C       |                                                                                  |              | 35   |     | ms    |

|                                                  | t <sub>AR(ON)</sub>      | T <sub>J</sub> = +25 °C       | , t <sub>SOFT</sub> + t <sub>SD(AR)</sub>                                        |              | 50   |     |       |

| Auto-Restart                                     | T <sub>AR(OFF)1</sub>    | First switch                  | h off-period                                                                     |              | 150  |     | ms    |

|                                                  | T <sub>AR(OFF)2</sub>    | Subsequent sv                 | vitch off-periods                                                                |              | 1500 |     |       |

| Parameter                                                   | Symbol                  | Cond<br>SOURCE = 0 V; T<br>(Unless Otherv        | Min                                                    | Тур          | Max               | Units |                     |  |

|-------------------------------------------------------------|-------------------------|--------------------------------------------------|--------------------------------------------------------|--------------|-------------------|-------|---------------------|--|

| Control Functions (cont.)                                   |                         |                                                  |                                                        |              |                   |       |                     |  |

| Transconductance<br>Amplifier Gain                          | g <sub>M</sub>          | $T_J = +$                                        | 25 °C                                                  | 95           | 115               | 125   | μΑ/V                |  |

| Transconductance<br>Amplifier Gain<br>Temperature Variation | Δg <sub>M</sub>         | 0 °C ≤ T <sub>J</sub> :<br>See N                 | ≤ +100 °C<br>lote A                                    |              |                   | ±20   | %                   |  |

| Transconductance<br>Amplifier Max Output<br>Current         | I <sub>GM</sub>         | $T_J = +$                                        | 25 °C                                                  | 10.0         | 12.5              | 15.0  | μА                  |  |

| COMPENSATION Pin Input Impedance                            | Z <sub>CP</sub>         | See N                                            | lote A                                                 | 30           |                   |       | ΜΩ                  |  |

| Bypass (BP) Input                                           |                         |                                                  |                                                        |              |                   | _     |                     |  |

| OVP/UVP/OTP<br>Programming<br>Capacitor Value               | C <sub>BP</sub>         |                                                  | T <sub>J</sub> = +25 °C<br>See Table 3 for programming |              | 0.47<br>4.7<br>47 |       | μΕ                  |  |

| BYPASS Pin Voltage                                          | V <sub>BP</sub>         |                                                  |                                                        |              | 5.75              | 6.04  | V                   |  |

| BYPASS Pin<br>Voltage Hysteresis                            | V <sub>BP</sub>         |                                                  |                                                        | 5.46<br>0.85 | 0.95              | 1.1   | V                   |  |

|                                                             |                         | \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \           | LNK6xx3                                                | -6.8         | -4.8              | -2.0  | mA                  |  |

|                                                             | I <sub>CH1</sub>        | $V_{BP} = 0 V$<br>$T_{J} = +25  ^{\circ}C$       | LNK6xx4-5                                              | -9.2         | -6.6              | -2.8  |                     |  |

| BYPASS Pin                                                  |                         | $V_{DS} \ge 50 \text{ V}$                        | LNK6xx6-7                                              | -12.0        | -8.3              | -4.3  |                     |  |

| Charge Current                                              |                         | V <sub>BP</sub> = 5 V<br>T <sub>J</sub> = +25 °C | LNK6xx3                                                | -4.7         | -2.7              | -1.5  | mA                  |  |

|                                                             | I <sub>CH2</sub>        |                                                  | LNK6xx4-5                                              | -7.0         | -4.0              | -2.2  |                     |  |

|                                                             | \                       | V <sub>DS</sub> ≥ 50 V                           | LNK6xx6-7                                              | -8.8         | -5.2              | -2.9  |                     |  |

| BYPASS Pin Shutdown<br>Threshold Current                    | l <sub>BPSD</sub>       | $T_J = +$                                        | 25 °C                                                  | 5.7          | 8.2               | 10.7  | mA                  |  |

| BYPASS Pin<br>Shutdown Delay                                |                         | $T_J = +$                                        | 25 °C                                                  |              | 8                 |       | Switching<br>Cycles |  |

| BYPASS Pin<br>Source Current                                | I <sub>BPSC</sub>       | $V_{BP} = T_{J} = +$                             | = 6 V<br>25 °C                                         |              |                   | -0.5  | mA                  |  |

| BYPASS Pin Charge<br>Current Temperature<br>Variation       | $\Delta I_{	ext{BPSC}}$ | See N                                            | lote A                                                 |              | 0.5               |       | %/°C                |  |

| BYPASS Pin<br>Shunt Voltage                                 | V <sub>BP(SHUNT)</sub>  | I <sub>BP</sub> = 3                              | 2 mA                                                   | 6.1          | 6.4               | 6.7   | V                   |  |

|                                                             | I <sub>BPS1</sub>       | T <sub>J</sub> = +25 °C,                         | See Note B                                             |              |                   | 525   | μА                  |  |

| BYPASS Pin                                                  |                         |                                                  | LNKxxx3                                                |              | 0.9               | 1.2   |                     |  |

|                                                             |                         |                                                  | LNKxxx4                                                |              | 1.0               | 1.3   | mA                  |  |

| Supply Current                                              | I <sub>BPS2</sub>       | MOSFET switching at fosc                         | LNKxxx5                                                |              | 1.1               | 1.4   |                     |  |

|                                                             |                         | USC                                              | LNKxxx6                                                |              | 1.3               | 1.6   |                     |  |

|                                                             |                         |                                                  | LNKxxx7                                                |              | 1.4               | 1.7   |                     |  |

| Parameter                                                                 | Symbol                  | SOURCE = 0 V; T                                   | itions<br>40 to 125 °C<br>wise Specified)                      | Min   | Тур              | Max   | Units               |

|---------------------------------------------------------------------------|-------------------------|---------------------------------------------------|----------------------------------------------------------------|-------|------------------|-------|---------------------|

| Voltage Sense (FB) Input                                                  | t                       |                                                   |                                                                |       |                  |       |                     |

| FEEDBACK Pin<br>Reference Voltage                                         | $V_{\text{FBth}}$       | T <sub>J</sub> = +                                | 25 °C                                                          | 1.974 | 2.000            | 2.026 | V                   |

| FEEDBACK Pin<br>Reference Voltage<br>Temperature Variation                | $\Delta V_{FB(th)}$     | 0 °C ≤ T <sub>J</sub> :<br>See N                  | ≤ +100 °C<br>lote A                                            |       | -0.01            |       | %/°C                |

| Line Undervoltage<br>Turn-On Threshold<br>Current                         | I <sub>FB(UV,REF)</sub> | T <sub>ON</sub> = 220 ns                          | , T <sub>J</sub> = +25 °C                                      |       | -250             |       | μА                  |

| FEEDBACK Pin Bus<br>Voltage Reference<br>Current Temperature<br>Variation | $\Delta l_{FB(REF)}$    | T <sub>on</sub> = 220 ns, 0 ° See N               | C ≤ T <sub>J</sub> ≤ +100 °C<br>Note A                         |       |                  | ±10   | %                   |

| Line Undervoltage<br>Turn-Off Threshold<br>Current                        | <br> FB(UVOFF)          | $T_{ON} = 2$ $T_{J} = +$                          |                                                                | -115  | -100             | -85   | μА                  |

| Line Undervoltage<br>Turn-Off Delay                                       |                         | T <sub>J</sub> = 25 °C                            |                                                                |       | 8                |       | Switching Cycles    |

| Line Overvoltage<br>Turn-Off Threshold<br>Current                         | I <sub>FB(OV)</sub>     | T <sub>ON</sub> = 220 ns, T <sub>J</sub> = +25 °C |                                                                | -1200 | -1150            | -1100 | μА                  |

| Line Overvoltage<br>Turn-Off Delay                                        |                         | $T_J = +$                                         | 25 °C                                                          |       | 2                |       | Switching<br>Cycles |

| Output Overvoltage<br>Detection Threshold<br>Voltage                      | V <sub>FB(OVP)</sub>    | $T_J = +$                                         | .25 °C                                                         | 2.375 | 2.5              | 2.625 | V                   |

| Output Overvoltage<br>Detection Delay                                     |                         | $T_J = +$                                         | 25 °C                                                          |       | 16               |       | Switching<br>Cycles |

| FEEDBACK Pin<br>Auto-Restart<br>Threshold Voltage                         | V <sub>FB(AR)</sub>     | $T_J = +$                                         | 25 °C                                                          | 1.794 | 1.85             | 1.906 | V                   |

| Current Limit<br>Reduction Onset<br>Threshold Current                     | I <sub>FB(LIM)</sub>    | T <sub>ON</sub> = 220 ns                          | , T <sub>J</sub> = +25 °C                                      |       | -210             |       | μА                  |

| Current Limit<br>Reduction Slope                                          | I <sub>LIM(LINE)</sub>  | 0 °C ≤ T <sub>J</sub> ≤ +100 °C                   | $-463 \mu A < I_{FB} \le I_{FB(LIM)}$<br>$I_{FB} < -463 \mu A$ |       | -0.032<br>-0.008 |       | %/μΑ                |

| FEEDBACK Pin                                                              | T <sub>SAMP1</sub>      |                                                   | $I_{PK} = I_{SET}$                                             |       | 2.5              | 2.65  |                     |

| Sampling Delay Time                                                       | T <sub>SAMP2</sub>      | $0 \text{ °C} \leq T_{J} \leq +100 \text{ °C}$    | $I_{PK} = 0.25 \times I_{SET}$                                 |       | 1.2              | 1.3   | μS                  |

| Missing Feedback<br>Voltage Protection<br>Sense Delay Time                | T <sub>MFVP</sub>       | T <sub>J</sub> = +25 °C                           |                                                                |       | 0.8              |       | μS                  |

| Missing Feedback<br>Voltage Protection<br>Delay                           |                         |                                                   |                                                                |       | 4                |       | Switching<br>Cycles |

|                                                      |                        |                                                                |                                                    |       | 1     | T     |                     |

|------------------------------------------------------|------------------------|----------------------------------------------------------------|----------------------------------------------------|-------|-------|-------|---------------------|

| Parameter                                            | Symbol                 | Conc<br>SOURCE = 0 V;<br>(Unless Other                         | Min                                                | Тур   | Max   | Units |                     |

| Multi-Function (PD) Inpu                             | ut                     |                                                                |                                                    |       |       |       |                     |

| PROGRAM/DELAY<br>Pin Voltage                         | V <sub>PD</sub>        | $T_J = -$                                                      | +25 °C                                             | 1.20  | 1.25  | 1.30  | V                   |

| PROGRAM/DELAY<br>Pin Time Lower<br>Voltage Threshold | $V_{PD(DL)}$           | T <sub>J</sub> = -                                             | +25 °C                                             | 0.50  | 0.535 | 0.57  | V                   |

| PROGRAM/DELAY<br>Pin Time Upper<br>Voltage Threshold | V <sub>PD(DU)</sub>    | T <sub>J</sub> = -                                             | +25 °C                                             | 1.20  | 1.25  | 1.30  | V                   |

| Fast AC Reset<br>Threshold                           | V <sub>PDTHACR</sub>   |                                                                |                                                    | 3.06  | 3.4   | 3.74  | V                   |

| Remote On/Off                                        | .,                     | T 05.00                                                        | Threshold                                          | 1.25  | 1.35  | 1.45  |                     |

| Threshold                                            | V <sub>PDTHRM</sub>    | T <sub>J</sub> = +25 °C                                        | Hysteresis                                         |       | 0.8   |       | V                   |

| Remote On/Off Delay                                  |                        | $T_J = -$                                                      | +25 °C                                             |       | 8     |       | Switching<br>Cycles |

| <b>Circuit Protection</b>                            |                        |                                                                |                                                    |       |       |       |                     |

|                                                      |                        | LNK6xx3                                                        | di/dt = 180 mA/ $\mu$ s<br>T <sub>J</sub> = +25 °C | 0.716 | 0.77  | 0.824 |                     |

|                                                      |                        | LNK6xx4                                                        | di/dt = 245 mA/ $\mu$ s<br>T <sub>J</sub> = +25 °C | 0.967 | 1.04  | 1.113 |                     |

| Self Protection<br>Current Limit                     | I <sub>LIMIT</sub>     | LNK6xx5                                                        | di/dt = 305 mA/ $\mu$ s<br>T <sub>J</sub> = +25 °C | 1.209 | 1.30  | 1.391 | А                   |

|                                                      |                        | LNK6xx6                                                        | di/dt = 460 mA/ $\mu$ s<br>T <sub>J</sub> = +25 °C | 1.814 | 1.95  | 2.087 |                     |

|                                                      |                        | LNK6xx7                                                        | di/dt = 610 mA/ $\mu$ s<br>T <sub>J</sub> = +25 °C | 2.418 | 2.60  | 2.782 |                     |

| Programmed Current Limit Variation                   | $\Delta l_{\sf LIMIT}$ |                                                                | or programming<br>10 °C, See Note A                |       |       | ±7    | %                   |

| Operational Peak Current Variation                   | $\Delta l_{PK(OP)}$    | $I_{PK(OP)} = 25 - 0 \text{ °C} \le T_{J} \le +10$             | 100% × I <sub>LIMIT</sub> ,<br>0 °C, See Note A    |       |       | ±7    | %                   |

| Thermal Shutdown<br>Temperature                      | T <sub>SD</sub>        |                                                                |                                                    | 135   | 142   | 150   | °C                  |

| Thermal Shutdown<br>Hysteresis                       | T <sub>SDH</sub>       | $C_{_{BP}} = 0.47 \ \mu F \text{ or } C_{_{BP}} = 4.7 \ \mu F$ |                                                    |       | 75    |       | °C                  |

| Leading Edge<br>Blanking Time                        | t <sub>LEB</sub>       | T <sub>J</sub> = +25 °C<br>See Note A                          |                                                    | 175   | 220   |       | ns                  |

| Current Limit<br>Delay Time                          | t <sub>ILD</sub>       | $T_J = -$                                                      | +25 °C                                             |       | 100   |       | ns                  |

| Minimum Switch ON-Time                               | T <sub>ON(MIN)</sub>   |                                                                | + t <sub>ILD(MAX)</sub><br>+25 °C                  | 325   | 400   | 500   | ns                  |

## LinkSwitch-HP

| Parameter            | Symbol                    | Conditions SOURCE = 0 V; T <sub>J</sub> = -40 to 125 °C (Unless Otherwise Specified) |                                                  | Min | Тур  | Max   | Units |

|----------------------|---------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------|-----|------|-------|-------|

| Output               |                           |                                                                                      |                                                  |     |      |       |       |

|                      |                           | LNK6xx3                                                                              | T <sub>J</sub> = +25 °C                          |     | 6.9  | 7.97  |       |

|                      |                           | $I_{\rm D} = 100  {\rm mA}$                                                          | T <sub>J</sub> = +100 °C                         |     | 10.5 | 12.08 |       |

|                      |                           | LNK6xx4                                                                              | T <sub>J</sub> = +25 °C                          |     | 4.6  | 5.30  |       |

|                      |                           | $I_{\rm D} = 150  {\rm mA}$                                                          | T <sub>J</sub> = +100 °C                         |     | 7.0  | 8.09  |       |

| ON Chata Daniatanaa  |                           | LNK6xx5                                                                              | T <sub>J</sub> = +25 °C                          |     | 3.5  | 4.03  | 0     |

| ON-State Resistance  | R <sub>DS(ON)</sub>       | $I_{\rm D} = 200  {\rm mA}$                                                          | T <sub>J</sub> = +100 °C                         |     | 5.4  | 6.21  | Ω     |

|                      |                           | LNK6xx6<br>I <sub>D</sub> = 300 mA                                                   | T <sub>J</sub> = +25 °C                          |     | 2.3  | 2.65  |       |

|                      |                           |                                                                                      | T <sub>J</sub> = +100 °C                         |     | 3.6  | 4.14  |       |

|                      |                           | LNK6xx7<br>I <sub>D</sub> = 400 mA                                                   | T <sub>J</sub> = +25 °C                          |     | 1.8  | 2.07  |       |

|                      |                           |                                                                                      | T <sub>J</sub> = +100 °C                         |     | 2.7  | 3.11  |       |

| OFF-State Drain      |                           | $V_{PD} = Floating$                                                                  | V <sub>DS</sub> = 560 V, T <sub>J</sub> = 125 °C |     |      | 470   | ^     |

| Leakage Current      | DSS                       |                                                                                      | V <sub>DS</sub> = 325 V, T <sub>J</sub> = 100 °C |     |      | 10    | μА    |

| 5                    | D) /                      | LNK677x, $V_{PD}$ = Floating,<br>$T_{J}$ = +25 °C                                    |                                                  | 725 |      |       | .,    |

| Breakdown Voltage    | BV <sub>DSS</sub> LNK6665 | LNK666x/L                                                                            | NK676x, $V_{PD}$ = Floating,<br>$T_{J}$ = +25 °C | 650 |      |       | V     |

| DRAIN Supply Voltage |                           |                                                                                      |                                                  | 50  |      |       | V     |

| Rise Time            | t <sub>R</sub>            | Measure                                                                              | ed in a typical flyback                          |     | 100  |       |       |

| Fall Time            | T <sub>F</sub>            |                                                                                      | verter application                               |     | 50   |       | ns    |

## NOTES:

A. Parameter not tested over specified temperature range. Guaranteed by design and characterization.

B. Average device switching frequency below 1 kHz.

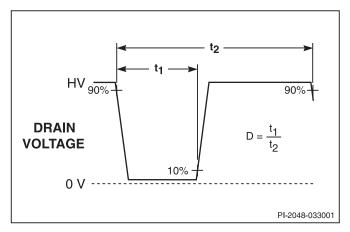

Figure 15. Duty Cycle Measurement.

## **Typical Performance Characteristics**

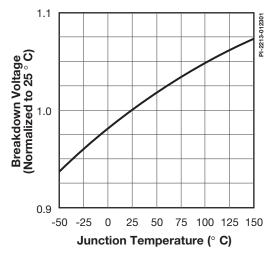

Figure 16. Breakdown vs. Temperature.

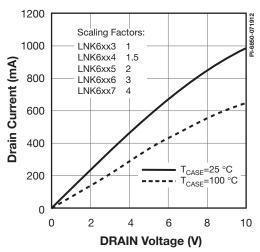

Figure 18. Output Characteristic.

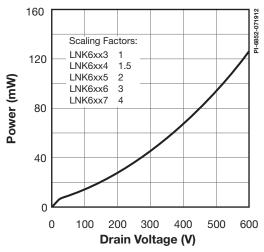

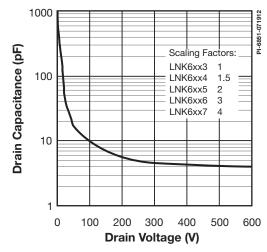

Figure 20. Drain Capacitance Power.

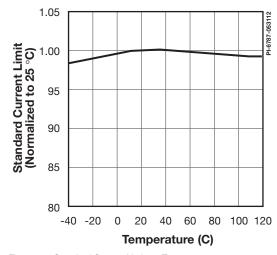

Figure 17. Standard Current Limit vs. Temperature.

Figure 19. C<sub>OSS</sub> vs. Drain Voltage.

Figure 21. Frequency vs. Temperature.

## **Typical Performance Characteristics**

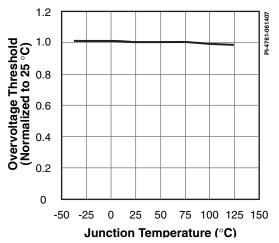

Figure 22. Overvoltage Threshold vs. Temperature.

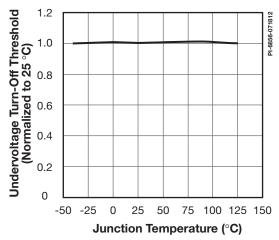

Figure 24. Overvoltage Threshold vs. Temperature.

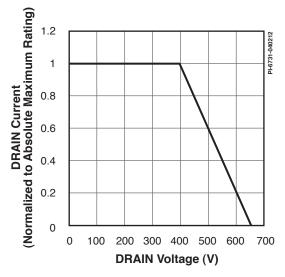

Figure 26. Maximum Allowable Drain Current vs. Drain Voltage (LNK6773-6777).

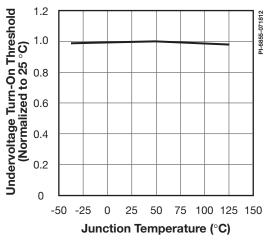

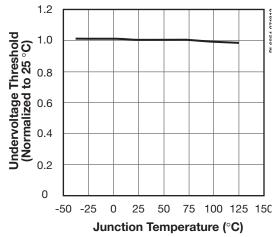

Figure 23. Undervoltage Threshold vs. Temperature.

Figure 25. Undervoltage Threshold vs. Temperature.

Figure 27. Maximum Allowable Drain Current vs. Drain Voltage (LNK6763-6767/LNK6663-6667).

## **Part Ordering Information**

| Revision | Notes                                                                      | Date     |

|----------|----------------------------------------------------------------------------|----------|

| А        | Initial Release.                                                           | 08/12    |

| Α        | Updated Table 2.                                                           | 08/23/12 |

| Α        | Updated page 5.                                                            | 10/24/12 |

| В        | Formatting changes. K <sub>PS</sub> Min value updated.                     | 12/04/12 |

| В        | Fixed Table references.                                                    | 02/26/13 |

| С        | Released K package parts. Updated $\Delta V_{ER/rb}$ Typ value on page 14. | 03/14    |

## For the latest updates, visit our website: www.powerint.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### Patent Information

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

#### **Life Support Policy**

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The PI logo, TOPSwitch, TinySwitch, LYTSwitch, DPA-Switch, PeakSwitch, CAPZero, SENZero, LinkZero, HiperPFS, HiperTFS, HiperLCS, Qspeed, EcoSmart, Clampless, E-Shield, Filterfuse, StakFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2014, Power Integrations, Inc.

## **Power Integrations Worldwide Sales Support Locations**

#### World Headquarters

5245 Hellyer Avenue San Jose, CA 95138, USA. Main: +1-408-414-9200 Customer Service: Phone: +1-408-414-9665 Fax: +1-408-414-9765

e-mail: usasales@powerint.com

## China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 Fax: +86-21-6354-6325 e-mail: chinasales@powerint.com

### China (ShenZhen)

3rd Floor, Block A, Zhongtou International Business Center, No. 1061, Xiang Mei Rd, FuTian District, ShenZhen, China, 518040

Phone: +86-755-8379-3243 Fax: +86-755-8379-5828 e-mail: chinasales@powerint.com

#### Germany

Lindwurmstrasse 114 80337 Munich Germany Phone: +49-895-527-39110 Fax: +49-895-527-39200 e-mail: eurosales@powerint.com

#### India

Vasanthanagar Bangalore-560052 India Phone: +91-80-4113-8020 Fax: +91-80-4113-8023 e-mail: indiasales@powerint.com

#1. 14th Main Road

#### Ital

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy

Phone: +39-024-550-8701 Fax: +39-028-928-6009 e-mail: eurosales@powerint.com

#### Japan

Kosei Dai-3 Bldg.

2-12-11, Shin-Yokohama,

Kohoku-ku

Yokohama-shi Kanagwan

222-0033 Japan

Phone: +81-45-471-1021

Fax: +81-45-471-3717

e-mail: japansales@powerint.com

#### Korea

RM 602, 6FL

Korea City Air Terminal B/D, 159-6

Samsung-Dong, Kangnam-Gu,

Seoul, 135-728, Korea

Phone: +82-2-2016-6610

Fax: +82-2-2016-6630

e-mail: koreasales@powerint.com

#### Singapore

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160 Fax: +65-6358-2015

e-mail: singaporesales@powerint.com

#### Taiwan

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist. Taipei 11493, Taiwan R.O.C. Phone: +886-2-2659-4570 Fax: +886-2-2659-4550 e-mail: taiwansales@powerint.com

#### Europe HQ

1st Floor, St. James's House East Street, Farnham Surrey GU9 7TJ United Kingdom Phone: +44 (0) 1252-730-141 Fax: +44 (0) 1252-727-689 e-mail: eurosales@powerint.com

## Applications Hotline

World Wide +1-408-414-9660

#### Applications Fax

World Wide +1-408-414-9760