2-Channel Echo Canceler with Multifunction ADPCM Transcoder

# **GENERAL DESCRIPTION**

The ML7202-001 is an LSI supporting 2-channel transmit/receive. Each channel of transmit/receive has a built-in line echo canceler and full-duplex ADPCM transcoder. The ML7202-001, which performs functions such as the DTMF tone and single tone generation, and tone detection, transmit/receive data mute, gain control, and VOX, is ideally suited to applications such as basestations of ADPCM-based cordless telephone systems like Asian-prevailing PHS (Personal Handyphone System).

# FEATURES

- Single 3.3 V power supply (DVDD1, 2, AVDD: 3.0 to 3.6 V)

- ADPCM: ITU-T Recommendation G.726 (32 kbps)

- PCM interface code format: ITU-T Recommendation G.711 (64 kbps), µ-law or A-law selectable

- Built-in echo canceler

- Echo attenuation: 30 dB (typ.) white noise

- Cancelable echo delay time: 64ms (max)

- Serial ADPCM and PCM transmission rate: 64 to 2048 kbps

- Digital interface synchronization mode: Long Frame Sync

- Time slot assignment

- μ-law/A-law setting: Supports 32 slots (BCLK setting: 2.048 MHz external input)

- Transmit/receive mute function and transmit/receive programmable gain setting

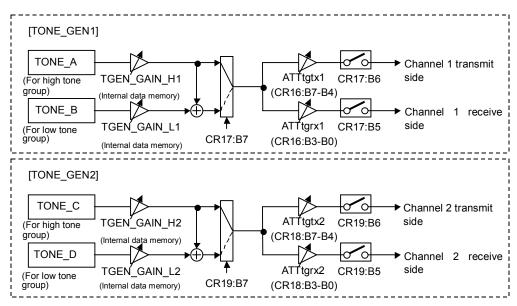

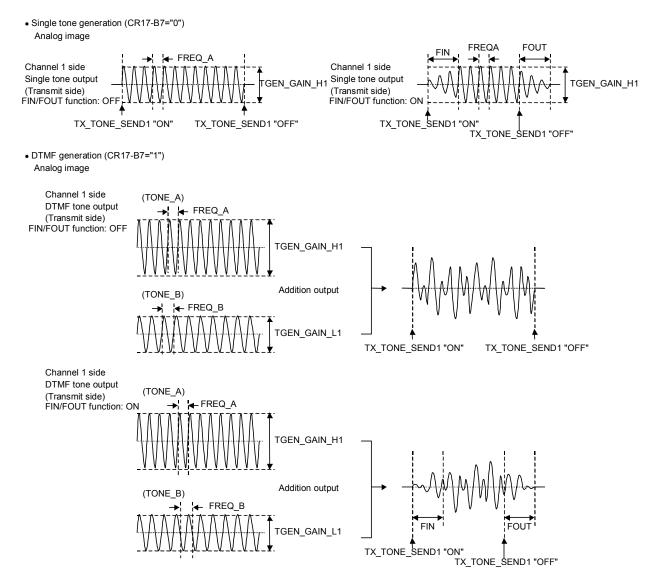

- Built-in DTMF tone and single tone generators

- Single tone detector

- 2100 Hz (default)

- Built-in VOX functions

- Transmit side : Voice/silence detection

- Receive side : Background noise generation during silence

- Parallel microcontroller interface

- Master clock frequency: 19.2 MHz

- Hardware and software power-down mode

- Operating temperature range: -40°C to +85°C

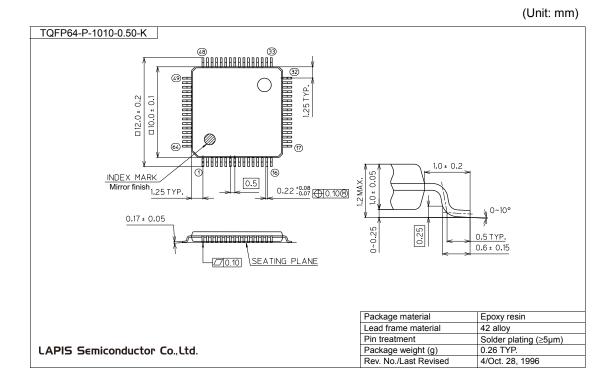

- Package:

- 64-pin plastic TQFP (TQFP64-P-1010-0.50-K) (ML7202-001TB)

#### ML7202-001

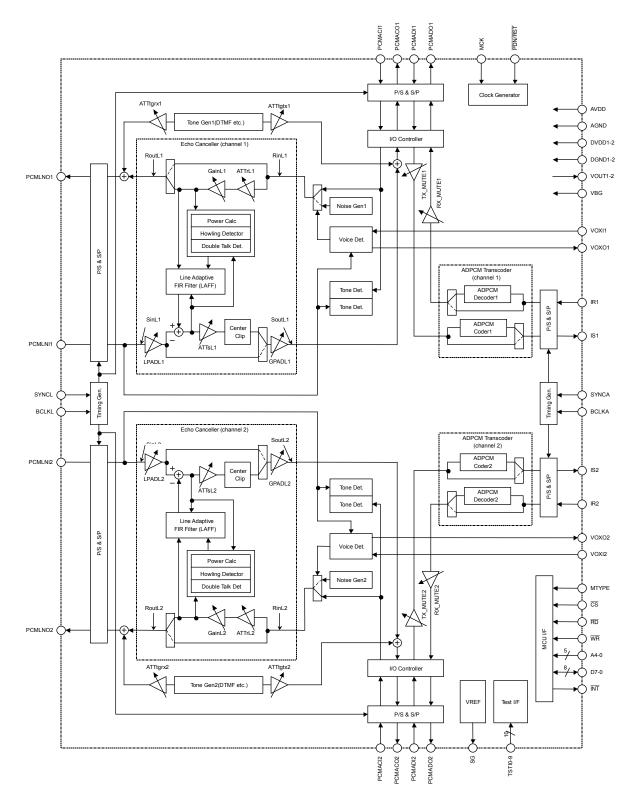

#### **BLOCK DIAGRAM**

\* Transmit side : Direction from the PCMLNI1-pin (or the PCMLNI2-pin) toward the IS1-pin (or the IS2-pin) Receive side : Direction from the IR1-pin (or the IR2-pin) toward the PCMLNO1-pin (or the PCMLNO2-pin)

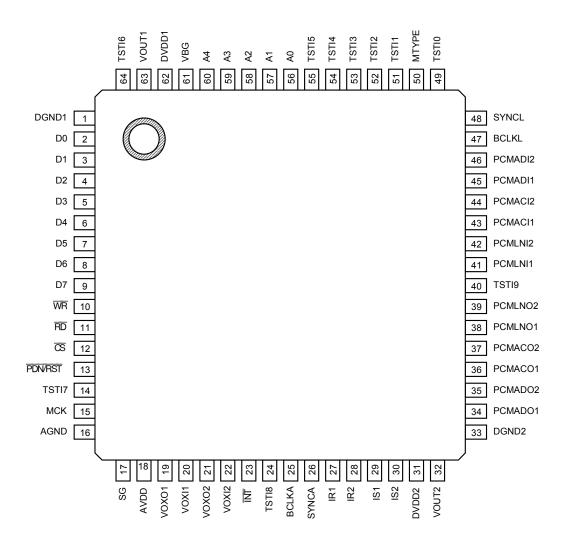

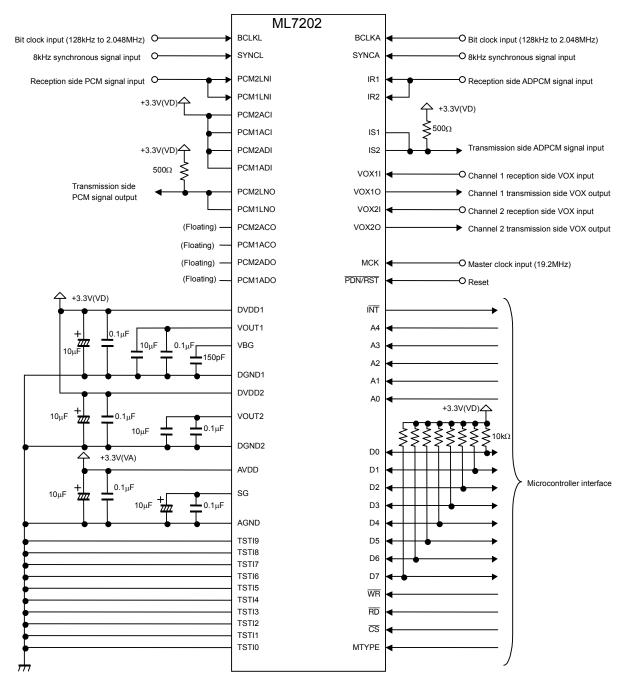

# **PIN CONFIGURATION (TOP VIEW)**

**64-Pin Plastic TQFP**

#### ML7202-001

# **PIN DESCRIPTIONS**

| Pin | Symbol  | I/O | State when<br>PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|-----|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DGND1   | _   | _                             | Digital ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

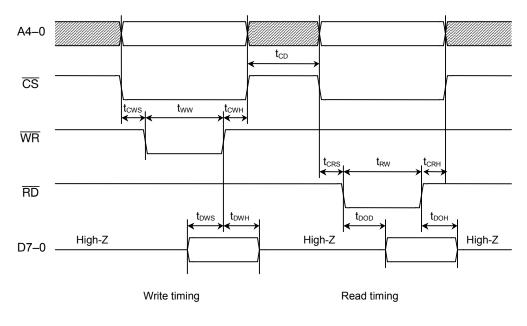

| 2   | D0      | I/O | I                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | D1      | I/O | I                             | Data 1/O ning for accessing control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4   | D2      | I/O | I                             | Data I/O pins for accessing control registers.<br>This LSI contains 32-byte control registers and reads/writes by an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | D3      | I/O | I                             | external microcontroller are via the $\overline{WR}$ , $\overline{RD}$ , and $\overline{CS}$ pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6   | D4      | I/O | I                             | See "Microcontroller Interface Write/Read Timing" in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7   | D5      | I/O | 1                             | "ELECTRICAL CHARACTERISTICS" Section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8   | D6      | I/O | I                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9   | D7      | I/O | <u> </u>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10  | WR      |     | I                             | Write enable input pin for accessing the control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11  | RD      | Ι   | I                             | Read enable input pin for accessing the control registers. This pin is<br>enabled when the MTYPE pin is set to "0" and is disabled when the<br>MTYPE pin is set to "1". When this pin is disabled, fix this pin to "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12  | CS      | I   | I                             | Chip select input pin for the control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

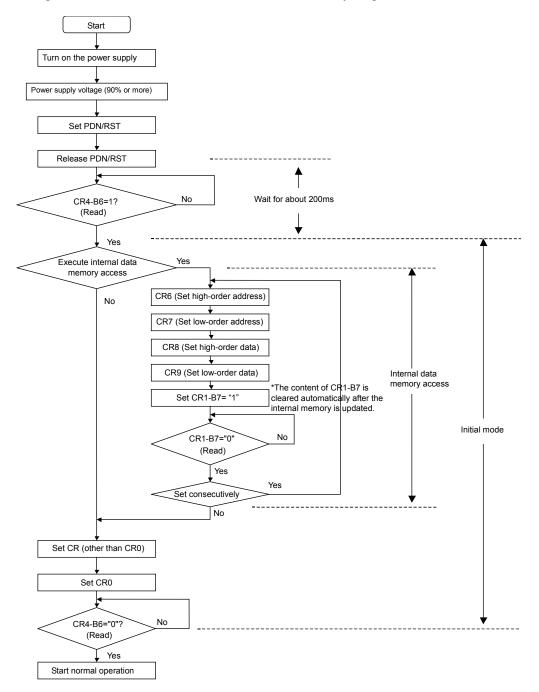

| 13  | PDN/RST | I   | "0"                           | Power-down and reset control input pin. When this pin is set to "0", the LSI is powered down. In power down mode, all of the control registers, internal data memories, coefficients in the echo canceler and the ADPCM transcoder are reset.<br>For normal operation, set this pin to "1". Since the power-down reset function is determined by the OR'ed value of a negative logic of this pin and the CR0-B7 (SPDN), set the CR0-B7 (SPDN) to "0" when using the pin.<br>When applying power, hold the pin in "0" for 250 $\mu$ S or longer from the master clock input (20 clocks minimum) after the digital supply (DVDD1 and DVDD2) voltage and the analog supply (AVDD) voltage reach 90% of their nominal value. See "Reset Function" in the "TIMING DIAGRAM" Section. Note that the specifications prescribed in this data sheet may not be satisfied until the requirements of inputting a minimum of 20 master clock pulses and holding the pin in "0" for 250 $\mu$ S or more are met. |

| 14  | TSTI7   | Ι   |                               | Input pin for LSI manufacturer's tests. Fix this pin to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15  | МСК     | I   | I                             | Master clock input pin. The input frequency shall be 19.2 MHz. The master clock can be asynchronized to SYNCL, SYNCA, BCLKL, and BCLKA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16  | AGND    | _   | _                             | Analog ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 17  | SG      | 0   | "0"                           | Output pin for analog signal ground in the LSI. The output voltage is about 1.4 V. Connect 10 $\mu$ F and 0.1 $\mu$ F (ceramic type) bypass capacitors between this pin and the AGND pin. This output cannot be directly used as analog signal ground. A buffer should be placed when this output is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18  | AVDD    | _   | _                             | +3.3 V analog power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin | Symbol | I/O | PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

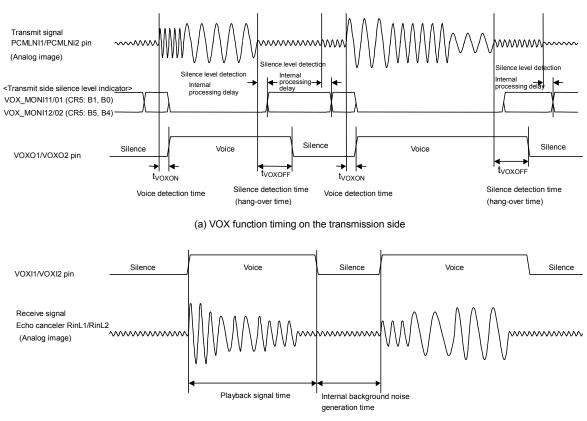

| 19  | VOXO1  | ο   | "0"             | Output pin for the VOX function on the transmit side of channel 1. This pin is enabled when CR21-B7 (VOX_ON1) is set to "1". This pin is used for identifying the voice/silence state by detecting the power of the transmit signal. At detection of voice, a logic "1" is output to this pin and at detection of silence, logic "0" is output. CR21-B6 and B5 (VOX_ON_LVL11 and_ VOX_ON_LVL01) are used for setting the threshold to be identified. This signal is also output to CR5-B2 (VOX_OUT1). Figure 4 shows the timing diagram for the VOX function. The transmit signal refers to the PCMLNI1 pin input signal.                                                                                                                                                                    |

| 20  | VOXI1  | I   | I               | Input pin for the VOX function on the receive side (line echo canceler<br>RinL1 side) of channel 1. This pin is enabled when CR21-B7<br>(VOX_ON1) is set to "1". When this pin is a logic "1", receive side<br>speech signals are fed to the RinL1. When this pin is a logic "0", the<br>background noise generator's output is fed to the RinL1 instead of the<br>receive side speech signals. Use CR21-B1 and B0<br>(RX_NOISE_LVL11 and RX_NOISE_LVL01) for setting the level of<br>the background noise. Set CR21-B2 (VOX_IN1) to "0" when using this<br>pin, since this pin is OR'ed with CR21-B2 (VOX_IN1) internally.<br>When the application has a means to detect silence with the receive<br>side speech signals, this function could be made use of as comfort<br>noise generator. |

| 21  | VOXO2  | ο   | "0"             | Output pin for the VOX function on the transmit side of channel 2. This pin is enabled when CR22-B7 (VOX_ON2) is set to "1". This pin is used for identifying the voice/silence state by detecting the power of the transmit signal. At detection of voice, a logic "1" is output to this pin and at detection of silence, logic "0" is output. CR22-B6 and B5 (VOX_ON_LVL12 and_ VOX_ON_LVL02) are used for setting the threshold to be identified. This signal is also output to CR5-B6 (VOX_OUT2). Figure 4 shows the timing diagram for the VOX function. The transmit signal refers to the PCMLNI2 pin input signal.                                                                                                                                                                    |

| 22  | VOXI2  | I   | I               | Input pin for the VOX function on the receive side (line echo canceler<br>RinL2 side) of channel 2. This pin is enabled when CR22-B7<br>(VOX_ON2) is set to "1". When this pin is a logic "1", receive side<br>speech signals are fed to the RinL2. When this pin is a logic "0", the<br>background noise generator's output is fed to the RinL2 instead of the<br>receive side speech signals. Use CR22-B1 and B0<br>(RX_NOISE_LVL12 and RX_NOISE_LVL02) for setting the level of<br>the background noise. Set CR22-B2 (VOX_IN2) to "0" when using this<br>pin, since this pin is OR'ed with CR22-B2 (VOX_IN2) internally.<br>When the application has a means to detect silence with the receive<br>side speech signals, this function could be made use of as comfort<br>noise generator. |

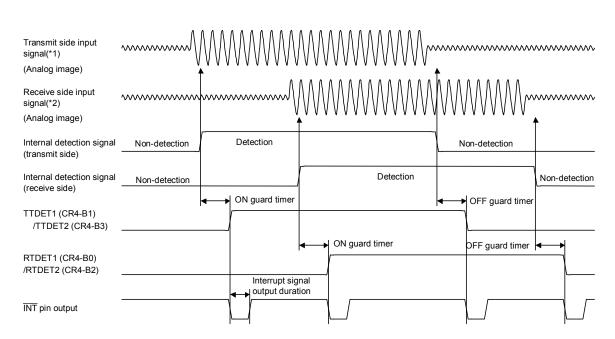

| 23  | ĪNT    | 0   | "1"             | Interrupt request output pin. An interrupt is generated when the transmit/receive tone detector in each channel detects a tone signal of 2100 Hz (default). An interrupt also is generated when the state changes from tone detection to non-detection of 2100 Hz (default). When an interrupt event occurs, the pin outputs a logic "0" for 0.7 $\mu$ s. When the interrupt event remains unchanged, the pin outputs a logic "1". By reading CR4-B3 to B0, it is possible to identify the detected channel and the path (on the transmit side/receive side).                                                                                                                                                                                                                                |

| Pin | Symbol | I/O | PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | TSTI8  | I   | I               | Input pin for testing. Fix this pin to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

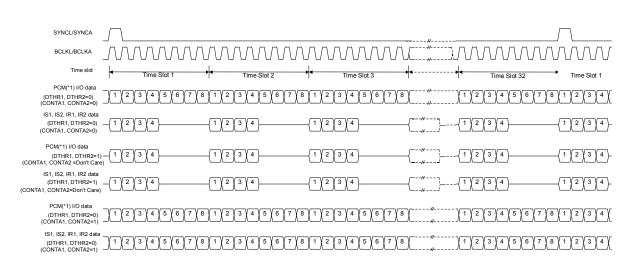

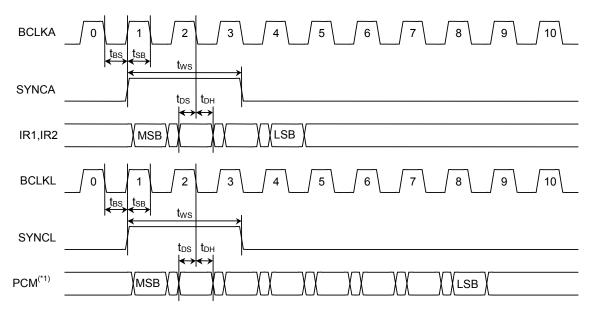

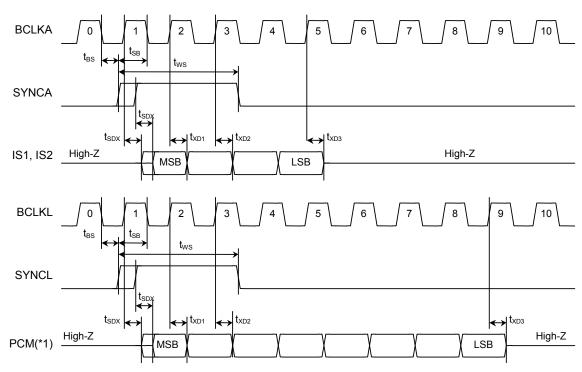

| 25  | BCLKA  | I   | I               | Shift clock input pin for ADPCM data (IS1, IS2, IR1, and IR2). The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26  | SYNCA  | 1   | I               | frequency is within the range of 64 to 2048 kHz.<br>8 kHz synchronous signal input pin for ADPCM data. This signal must<br>be synchronized with the BCLKA signal. This signal indicates the<br>location of MSB of ADPCM data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27  | IR1    | 1   | I               | 4-bit ADPCM data input pin on the receive side of channel 1. The signal that is input to this pin is output to the PCMADO1 pin when CR0-B3 (IOSEL) is set to "1" and the signal is output to the PCMLNO1 pin when CR0-B3 is set to "0". This ADPCM data is shifted on the falling edge of BCLKA, synchronized to SYNCA and input serially starting from MSB.<br>When CR2-B7 (CONTA1) is set to "1", this pin is configured as an 8-bit PCM data input and the data is processed skipping the ADPCM transcoder. When CR2-B5 (DTHR1) is set to "1", the output pin set by CR0-B3 (IOSEL) is configured as a 4-bit ADPCM data output and the 4-bit ADPCM input data is output as it is.<br>When CR2-B5 (DTHR1) is set to "1", the MUTE function is disabled and, even if CR2-B7 (CONTA1) is set to "1", the pin is not configured as an 8-bit PCM data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28  | IR2    | I   | I               | 4-bit ADPCM data input of the processed side of channel 2. The signal that is input to this pin is output to the PCMADO2 pin when CR0-B3 (IOSEL) is set to "1" and the signal is output to the PCMLNO2 pin when CR0-B3 is set to "0". This ADPCM data is shifted on the falling edge of BCLKA, synchronized to SYNCA and input serially starting from MSB.<br>When CR3-B7 (CONTA2) is set to "1", this pin is configured as an 8-bit PCM data input and the data is processed skipping the ADPCM transcoder. When CR3-B5 (DTHR2) is set to "1", the output pin set by CR0-B3 (IOSEL) is configured as a 4-bit ADPCM data output and the 4-bit ADPCM input data is output as it is.<br>When CR3-B5 (DTHR2) is set to "1", the MUTE function is disabled, and even if CR3-B7 (CONTA2) is set to "1", the pin is not configured as an 8-bit PCM data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 29  | IS1    | 0   | Hi-Z            | ADPCM data output pin on the transmit side of channel 1. When CR0-B3 (IOSEL) is set to "1", the signal that is input from the PCMADI1 pin is output from this pin. When CR0-B3 is set to "0", the signal that is input from the PCMLNII1 pin is output. ADPCM data is output serially starting from MSB, synchronized to the rising edges of BCLKA and SYNCA, and this pin gets in a high impedance state except when the 4-bit ADPCM data is being output. Also during power-down/reset and initial mode, this pin is put in a high impedance state. When CR2-B7 (CONTA1) is set to "1", this pin is configured as an 8-bit PCM data output skipping the ADPCM transcoder. This pin gets in a high impedance state except when the 8-bit PCM data is being output. When CR2-B5 (DTHR1) is set to "1", the 4-bit ADPCM input data from the input pin set by CR0-B3 (IOSEL) is output from this pin as it is. This pin gets in a high impedance state except when CR2-B5 (DTHR1) is set to "1", the 4-bit ADPCM data is being output. When CR2-B5 (DTHR1) is set to "1", the 4-bit ADPCM input data from the input pin set by CR0-B3 (IOSEL) is output from this pin as it is. This pin gets in a high impedance state except when the 4-bit ADPCM data is being output. When CR2-B5 (DTHR1) is set to "1", the 4-bit ADPCM input data from the input pin set by CR0-B3 (IOSEL) is output from this pin as it is. This pin gets in a high impedance state except when the 4-bit ADPCM data is being output. When CR2-B5 (DTHR1) is set to "1", the 4-bit data is being output. |

| Pin | Symbol  | I/O | PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----|---------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 30  | IS2     | 0   | Hi-Z            | ADPCM data output pin on the transmit side of channel 2. M<br>CR0-B3 (IOSEL) is set to "1", the signal that is input from<br>PCMADI2 pin is output from this pin. When CR0-B3 is set to "0<br>signal that is input from the PCMLNII2 pin is output. ADPCM d<br>output serially starting from MSB, synchronized to the rising edg<br>BCLKA and SYNCA, and this pin gets in a high impedance<br>except when the 4-bit ADPCM data is being output.<br>Also during power-down/reset and initial mode, this pin is put in a<br>impedance state.<br>When CR3-B7 (CONTA2) is set to "1", this pin is configured as an<br>PCM data output skipping the ADPCM transcoder. This pin get<br>high impedance state except when the 8-bit PCM data is being of<br>When CR3-B5 (DTHR2) is set to "1", the 4-bit ADPCM input data<br>the input pin set by CR0-B3 (IOSEL) is output from this pin as<br>This pin gets in a high impedance state except when the 4-bit AD<br>data is being output. When CR3-B5 (DTHR2) is set to "1", the M<br>function is disabled, and the pin is not configured as an 8-bit PCM<br>output even if CR3-B7 (CONTA2) is set to "1".                             |  |  |

| 31  | DVDD2   |     |                 | +3.3 V digital power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 32  | VOUT2   | 0   | About 2.6 V     | Regulator output pin. The output voltage is about 2.6 V.<br>Connect 10 $\mu$ F and 0.1 $\mu$ F bypass capacitors between this pin and the DGND2 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 33  | DGND2   | _   | _               | Digital Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 34  | PCMADO1 | 0   | Hi-Z            | PCM data output pin of channel 1. This pin is enabled when CR0-B3<br>(IOSEL) is set to "1" and is put in a high impedance state when<br>CR0-B3 is set to "0". The PCM data is output serially starting from<br>MSB, synchronized to the rising edges of BCLKL and SYNCL, and the<br>pin gets in a high impedance state except when the 8-bit PCM data is<br>being output. Also during power-down reset and initial mode, the pin is<br>also put in a high impedance.<br>When CR2-B5 (DTHR1) is set to "1", this pin is configured as a 4-bit<br>ADPCM data output and 4-bit ADPCM input data from the IR1 pin is<br>output as it is. This pin gets in a high impedance state except when<br>the 4-bit ADPCM data is being output. When CR2-B7 (CONTA1) is set<br>to "1", the ADPCM transcoder goes into a through mode and 8-bit<br>PCM input data from the IR1 pin is output as it is from this pin. The pin<br>gets in a high impedance state except when the 8-bit PCM data is<br>being output.<br>When CR2-B5 (DTHR1) is set to "1", the MUTE function is disabled<br>and the pin is not configured as an 8-bit PCM data output even if<br>CR2-B7 (CONTA1) is set to "1". |  |  |

#### FEDL7202-001-01

# LAPIS Semiconductor Co.,Ltd.

| Pin | Symbol  | I/O | PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35  | PCMADO2 | 0   | Hi-Z            | PCM data output pin of channel 2. This pin is enabled when CR0-B3<br>(IOSEL) is set to "1" and is put in a high impedance state when<br>CR0-B3 is set to "0". The PCM data is output serially starting from<br>MSB, synchronized to the rising edges of BCLKL and SYNCL, and the<br>pin gets in a high impedance state except when the 8-bit PCM data is<br>being output. Also during power-down reset and initial mode, the pin is<br>also put in a high impedance.<br>When CR3-B5 (DTHR2) is set to "1", this pin is configured as a 4-bit<br>ADPCM data output and 4-bit ADPCM input data itself from the IR2 pin<br>is output. This pin gets in a high impedance state except when the<br>4-bit ADPCM data is being output. When CR3-B7 (CONTA2) is set to<br>"1", the ADPCM transcoder goes into a through mode and 8-bit PCM<br>input data from the IR2 pin is output as it is from this pin. The pin gets<br>in a high impedance state except when the 8-bit PCM data is being<br>output.<br>When CR3-B5 (DTHR2) is set to "1", the MUTE function is disabled<br>and the pin is not configured as an 8-bit PCM data output even if<br>CR3-B7 (CONTA2) is set to "1". |

| 36  | PCMACO1 | 0   | Hi-Z            | PCM data output pin of channel 1 line echo canceler. This pin is<br>enabled when CR0-B3 (IOSEL) is set to "1". When CR0-B3 is set to<br>"0", the pin is put in a high impedance. PCM data is output serially<br>starting from MSB, synchronized to the rising edges of BCLKL and<br>SYNCL, and the pin gets in a high impedance state except when the<br>8-bit PCM data is being output. Also during power-down reset and<br>initial mode, the pin is put in a high impedance.<br>During an end-to-end 4-bit ADPCM transparent mode defined by<br>CR2-B5 (DTHR1) set to "1", this pin is configured as 4-bit ADPCM data<br>output, and the line echo canceler, the VOX function, and the tone<br>detector are disabled. The 4-bit ADPCM input data from the PCMLNI1<br>pin is output as it is, and the pin gets in a high impedance state except<br>when the 4-bit ADPCM data is being output.<br>Note that the pin is not configured as an 8-bit PCM data output when<br>CR2-B5 (DTHR1) is set to "1" even if CR2-B7 (CONTA1) is set to "1".                                                                                                                               |

| 37  | PCMACO2 | 0   | Hi-Z            | PCM data output pin of channel 2 line echo canceler. This pin is<br>enabled when CR0-B3 (IOSEL) is set to "1". When CR0-B3 is set to<br>"0", the pin is put in a high impedance. PCM data is output serially<br>starting from MSB, synchronized to the rising edges of BCLKL and<br>SYNCL, and the pin gets in a high impedance state except when the<br>8-bit PCM data is being output. Also during power-down reset and<br>initial mode, the pin is put in a high impedance.<br>During an end-to-end 4-bit ADPCM transparent mode defined by<br>CR3-B5 (DTHR2) set to "1", this pin is configured as 4-bit ADPCM data<br>output, the VOX function, and the tone detector are disabled. The 4-bit<br>ADPCM input data from the PCMLNI2 pin is output as it is, and the pin<br>gets in a high impedance state except when the 4-bit ADPCM data is<br>being output.<br>Note that the pin is not configured as an 8-bit PCM data output when<br>CR3-B5 (DTHR2) is set to "1" even if CR3-B7 (CONTA2) is set to "1".                                                                                                                                                           |

| Pin | Symbol  | I/O | PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38  | PCMLNO1 | 0   | Hi-Z            | PCM data output pin of line echo canceler of channel 1. The PCM data is output serially starting from MSB, synchronized to the rising edges of BCLKL and SYNCL. The pin gets in a high impedance state except when the 8-bit PCM data is being output. Also during power-down reset and initial mode, the pin is put in a high impedance. During an end-to-end 4-bit ADPCM transparent mode defined by CR2-B5 (DTHR1) set to "1", this pin is configured as 4-bit ADPCM data output, and the line echo canceler, the VOX function, and the tone detector are disabled. The 4-bit ADPCM input data from the input pin set by CR0-B3 (IOSEL) is output as it is from this pin. The pin gets in a high impedance state except when the 4-bit ADPCM data is being output. Note that the pin is not configured as an 8-bit PCM data output when CR2-B5 (DTHR1) is set to "1" even if CR2-B7 (CONTA1) is set to "1". |

| 39  | PCMLNO2 | 0   | Hi-Z            | PCM data output pin of line echo canceler of channel 2. The PCM data is output serially starting from MSB, synchronized to the rising edges of BCLKL and SYNCL. The pin gets in a high impedance state except when the 8-bit PCM data is being output. Also during power-down reset and initial mode, the pin is put in a high impedance. During an end-to-end 4-bit ADPCM transparent mode defined by CR3-B5 (DTHR2) set to "1", this pin is configured as 4-bit ADPCM data output, and the line echo canceler, the VOX function, and the tone detector are disabled. The 4-bit ADPCM input data from the input pin set by CR0-B3 (IOSEL) is output as it is from this pin. The pin gets in a high impedance state except when the 4-bit ADPCM data is being output. Note that the pin is not configured as an 8-bit PCM data output when CR3-B5 (DTHR2) is set to "1" even if CR3-B7 (CONTA2) is set to "1". |

| 40  | TSTI9   | I   | I               | Input pin for testing. Fix this pin to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 41  | PCMLNI1 | I   | I               | PCM data input pin of line echo canceler of channel 1. This PCM input signal is shifted on the falling edge of BCLKL and is input starting from MSB. The start of PCM data (MSB) is identified by the rising edge of SYNCL. When CR2-B5 (DTHR1) is set to "1", the pin is configured as a 4-bit ADPCM data input and the input data from this pin is output as it is to the output pin set by CR0-B3 (IOSEL).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 42  | PCMLNI2 | I   | I               | PCM data input pin of line echo canceler of channel 2. This PCM input signal is shifted on the falling edge of BCLKL and is input starting from MSB. The start of PCM data (MSB) is identified by the rising edge of SYNCL. When CR3-B5 (DTHR2) is set to "1", the pin is configured as a 4-bit ADPCM data input and the input data from this pin is output as it is to the output pin set by CR0-B3 (IOSEL).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 43  | PCMACI1 | I   | I               | PCM data input pin of line echo canceler of channel 1. This pin is<br>enabled when CR0-B3 (IOSEL) is set to "1" and when CR0-B3 is set to<br>"0", input to the pin is disabled. When the input is disabled, fix the pin<br>to "0" or "1". The PCM input signal is shifted on the rising edge of<br>BCLKL and is input starting from MSB. The start of PCM data (MSB)<br>is identified by the rising edge of SYNCL. When CR2-B5 (DTHR1) is<br>set to "1", the pin is configured as a 4-bit ADPCM data input and 4-bit<br>ADPCM data input from the PCMLNO1 is output from this pin as it is.                                                                                                                                                                                                                                                                                                                    |

| 44  | PCMACI2 | I   | I               | PCM data input pin of line echo canceler of channel 2. This pin is<br>enabled when CR0-B3 (IOSEL) is set to "1" and when CR0-B3 is set to<br>"0", input to the pin is disabled. When the input is disabled, fix the pin<br>to "0" or "1". The PCM input signal is shifted on the rising edge of<br>BCLKL and is input starting from MSB. The start of PCM data (MSB)<br>is identified by the rising edge of SYNCL. When CR3-B5 (DTHR2) is<br>set to "1", the pin is configured as a 4-bit ADPCM data input and 4-bit<br>ADPCM data input from the PCMLNO2 is output from this pin as it is.                                                                                                                                                                                                                                                                                                                    |

#### FEDL7202-001-01

# LAPIS Semiconductor Co., Ltd.

| Pin | Symbol  | I/O | PDN/RST<br>="0" | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45  | PCMADI1 | I   | I               | PCM data input pin of channel 1. When CR0-B3 (IOSEL) is set to "1",<br>input to this pin is enabled; and when CR0-B3 is set to "0", input to the<br>pin is disabled. When the pin input is disabled, fix the pin to "0" or "1".<br>The PCM input signal is shifted on the falling edge of BCLKL and is<br>input starting from MSB. The beginning of PCM data (MSB) is<br>identified by the rising edge of SYNCL. When CR2-B5 (DTHR1) is set<br>to "1", the pin is configured as a 4-bit ADPCM data input and the 4-bit<br>ADPCM data input from this pin is output to the IS1 pin as it is. When<br>CR2-B7 (CONTA1) is set to "1", the ADPCM transcoder goes into a<br>through mode and 8-bit PCM data input from this pin is output to the<br>IS1 pin as it is. |

| 46  | PCMADI2 | I   | Ι               | PCM data input pin of channel 2. When CR0-B3 (IOSEL) is set to "1", input to this pin is enabled; and when CR0-B3 is set to "0", input to the pin is disabled. When the pin input is disabled, fix the pin to "0" or "1". The PCM input signal is shifted on the falling edge of BCLKL and is input starting from MSB. The beginning of PCM data (MSB) is identified by the rising edge of SYNCL. When CR3-B5 (DTHR2) is set to "1", the pin is configured as a 4-bit ADPCM data input and the 4-bit ADPCM data input from this pin is output to the IS2 pin as it is. When CR3-B7 (CONTA2) is set to "1", the ADPCM data input to the IS2 pin as it is.                                                                                                         |

| 47  | BCLKL   | I   | I               | Shift clock input pin for PCM data (PCMLN01/PCMLNI1, PCMAC01<br>/PCMACI1, PCMAD01/PCMADI1, PCMLN02/PCMLNI2, PCMAC02<br>/PCMACI2, and PCMAD02/PCMADI2).<br>The input frequency is 64 to 2048 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 48  | SYNCL   | I   | I               | 8 kHz synchronous signal input pin for PCM data. This signal must be synchronized to the BCLKL signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 49  | TSTI0   | 1   | I               | Input pin for testing. Fix this pin to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

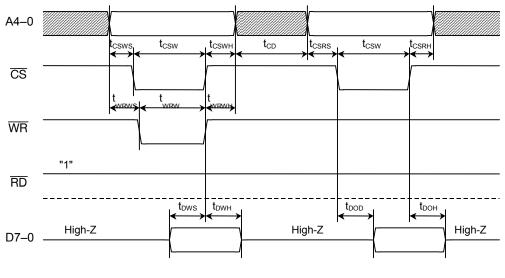

| 50  | MTYPE   | I   | I               | Microcontroller interface select pin. When the pin is set to "0", the pin is in read/write independent control mode; and when it is set to "1", the pin is in read/write shared (R/W) control mode.<br>When this pin is set to "1", fix the $\overline{RD}$ pin to "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 51  | TSTI1   | 1   | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 52  | TSTI2   | i   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 53  | TSTI3   | I   | i               | Input pins for LSI manufacturer's testing. Fix these pins to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 54  | TSTI4   | I   | I               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 55  | TSTI5   | I   | I               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 56  | A0      | I   | I               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 57  | A1      | I   | I               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 58  | A2      | Ι   |                 | Address input pins for accessing the control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 59  | A3      | I   | I               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 60  | A4      | I   | I               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 61  | VBG     | 0   | About<br>1.2 V  | Regulator reference voltage output pin. The output voltage is about 1.2 V.<br>Connect a 150 pF bypass capacitor between this pin and the DGND1 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 62  | DVDD1   | —   |                 | +3.3 V digital power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |