8-bit Microcontrollers

## MC9RS08KA8/4

### **Target Applications**

- High-brightness LED

- · Lighting systems control

- Toys

- Small handheld devices

- Space-constrained applications

- Small appliances

- AC line voltage monitoring

- · Battery charger

- ASIC replacement

#### Overview

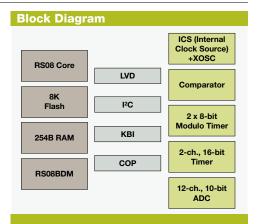

The MC9RS08KA8 microcontroller unit (MCU) is an extremely cost-effective and highly integrated, device intended for home appliances, health care equipment and as a general-purpose microcontroller. This device is composed of standard on-chip modules including a very small and highly efficient RS08 CPU core, 254 bytes RAM, 8K bytes flash, two 8-bit modulo timers,12-channel 10-bit ADC, 2-channel 16-bit timer/PWM, inter-integrated circuit bus module, keyboard interrupt and analog comparator. The device is available in 16- and 20-pin packages.

### **Cost-Effective Development tools**

For more information on development tools, please refer to the Freescale Development Tool Selector Guide (SG1011).

# CodeWarrior® Development Studio for Microcontrollers 6.1

#### Complimentary\*

CodeWarrior Development Studio for Microcontrollers is an integrated tool suite that supports software development for Freescale's 8-bit or 32-bit microcontrollers. Designers can further accelerate application development with the help of the Processor Expert<sup>TM</sup> tool, which is an award-winning rapid application development tool in the CodeWarrior tool suite.

#### DEMO9RS08KA8 \$50 MSRP

Cost-effective demonstration board with potentiometer, LEDs and a built-in USB-BDM cable for debugging and programming.

|  | Package Options |             |                  |  |

|--|-----------------|-------------|------------------|--|

|  | Part Number     | Package     | Temp. Range      |  |

|  | MC9RS08KA8CWG   | 16-pin SOIC | -40° C to +85° C |  |

|  | MC9RS08KA8CWJ   | 20-pin SOIC | -40° C to +85° C |  |

|  | MC9RS08KA8CPJ   | 20-pin PDIP | -40° C to +85° C |  |

|  | MC9RS08KA8CPG   | 16-pin PDIP | -40° C to +85° C |  |

|  | MC9RS08KA4CWJ   | 20-pin SOIC | -40° C to +85° C |  |

|  | MC9RS08KA4CWG   | 16-pin SOIC | -40° C to +85° C |  |

|  | MC9RS08KA4CPJ   | 20-pin PDIP | -40° C to +85° C |  |

|  | MC9RS08KA4CPG   | 16-pin PDIP | -40° C to +85° C |  |

<sup>\*</sup> Subject to license agreement and registration

| Features                                                                                                                                                                             | Benefits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                      | - Deficition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B-bit RS08 Central Processor Unit (CPU)     Up to 10 MHz (bus frequency) RS08 CPU at 1.8 volts for 100 ns minimum instruction time                                                   | Offers high performance for applications expected by betters, even at law valte                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                      | Offers high performance for applications operated by battery—even at low voltage                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Subset of HC08 instruction set with added BGND instruction                                                                                                                           | Provides source code compatibility with 68HC05/68HC08/S08 Allows easier code debugging through additional BGND instruction Offers direct access to the shadow PC register through additional SHA and SLA instructions                                                                                                                                                                                                                                                                                            |

| Supports tiny/short address mode                                                                                                                                                     | <ul> <li>Allows single-byte instructions for the most frequently used operations, including INC, DEC, ADD, SUB, LDA, STA and CLR</li> <li>Offers optimized coding efficiency and code density</li> </ul>                                                                                                                                                                                                                                                                                                         |

| <ul> <li>Index addressing scheme through memory mapped registers X and D[X] within the tiny address range</li> </ul>                                                                 | <ul> <li>Allows emulation for HC08/S08-style zero-offset index addressing mode instructions</li> <li>Performs index addressing through X and D[X] registers with all direct, tiny and short addressing instructions capable of operating on/with X and D[X] registers</li> <li>Extends addressing to the entire memory space through the paging scheme</li> </ul>                                                                                                                                                |

| 14 byte code-efficient RAM     X and D[X] mapped within code-efficient tiny address space     16 byte code-efficient peripheral register space                                       | Enables direct access to the code-efficient RAM through single-byte tiny/short address mode instructions     Provides code-efficient access to most frequently accessed peripherals within the short addressing space     Enables most frequently used variables and software flags to optimize coding efficiency                                                                                                                                                                                                |

| Page window                                                                                                                                                                          | Provides access to entire 8K through 128 pages of 64 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Simplified interrupt mechanism                                                                                                                                                       | Helps eliminate hardware overhead for the vector lookup and the stacking mechanism     Provides short wake-up latency for WAIT/STOP     SHA/SLA instructions enable multi-level software stacking implementation                                                                                                                                                                                                                                                                                                 |

| Subroutine call/return mechanism                                                                                                                                                     | Allows single level of subroutine call through hardware stacking with a shadow PC register     Allows fast jump to subroutine (JSR/BSR) and return from subroutine (RTS) operation                                                                                                                                                                                                                                                                                                                               |

| Integrated Third-Generation Flash                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| • Extremely fast, byte-writable programming— up to 20 µs/byte                                                                                                                        | Helps reduce production programming costs through ultra fast programming     Helps lower system power consumption from shorter writes                                                                                                                                                                                                                                                                                                                                                                            |

| Offers 1 KB write/erase cycles minimum over temperature                                                                                                                              | Allows electrically erasable nonvolatile memory to help reduce firmware development cycle                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Flexible Clock Options                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Internal clock source module containing a frequency-locked loop (FLL) controlled by internal or<br/>external reference</li> </ul>                                           | Helps eliminate the cost of all external clock components     Reduces board space     Increases system reliability     Provides more options to use internal or external reference clock                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>Precision trimming of internal reference allows typical 0.2 percent resolution and +1 percent to -1 percent<br/>deviation over operating temperature and voltage</li> </ul> | Provides one of the most accurate internal clock sources on the market for the money                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Internal reference clock can be trimmed from 31.25 kHz to 39.065 kHz, allowing for maxim 10 MHz Bus frequency output                                                                 | Allows for trimming to adjust bus clock in specific applications                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Timer                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2 x 8-bit modulo timer with 8-bit prescaler                                                                                                                                          | Generates periodic trigger for time-based software loops using timer overflow interrupt                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2-ch., 16-bit timer/PWM                                                                                                                                                              | Provide selectable input capture, output compare or buffered edge or center-aligned PWM on each channel                                                                                                                                                                                                                                                                                                                                                                                                          |

| Allows external timer clock source                                                                                                                                                   | Utilizes TCLK input as event trigger; the timer can be used as an 8-bit event counter                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ADC                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| • 12-ch., 10-bit resolution                                                                                                                                                          | Easily interface to analog inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • 2.5 µs conversion time; automatic compare function                                                                                                                                 | 400 sample/second conversion rate allows for sampling high-speed signals     Used to set conversion complete and generate interrupt only when result matches condition, freeing up system resources                                                                                                                                                                                                                                                                                                              |

| Trigger conversion using RTI counter                                                                                                                                                 | Takes periodic measurements without CPU involvement     Can be used in STOP3 with compare function to take measurements and wake MCU only when compare value is reached                                                                                                                                                                                                                                                                                                                                          |

| Analog Comparator                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Option to compare to internal reference                                                                                                                                              | Requires only a single pin for input signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Option to route comparator output directly to pin                                                                                                                                    | Allows other components in system to see result of comparator with minimal delay                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Allows operation in MCU STOP mode                                                                                                                                                    | Offers function to wake up the MCU from WAIT/STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ·                                                                                                                                                                                    | • Official fullication to wake up the wido from warr/offor                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1 <b>°C</b> ■ Inter-integrated circuit bus module capable of operation up to 100 kbps with maximum bus loading                                                                       | Provide communication interface     Extend more peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Real-Time Interrupt                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Real-time interrupt trigger with 3-bit prescaler     Built-in low-power 1 kHz clock source                                                                                           | Allows periodic wake-up or software trigger with delay ranging from 8 ms to 1.024s     Options to use low-power 1 kHz internal clock to drive the RTI     Minimizes power consumption in MCU STOP                                                                                                                                                                                                                                                                                                                |

| Up to 18 GPIOs Including One Output-Only and One Input-Only Pin                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Software selectable pull-ups on ports when used as input (internal pull-up on RESET)                                                                                                 | Eliminates need for external resistors to help reduce customer system cost                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Software selectable slew rate control on ports when used on output                                                                                                                   | Configures ports for slower slew rate to help minimize noise emissions from the MCU                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8-pin keyboard interrupt module with software selectable polarity on edge or edge/level modes                                                                                        | Helps to virtually eliminate external glue logic when interfacing to simple keypads using keyboard scan with programmable pull-up/pull-down functionality                                                                                                                                                                                                                                                                                                                                                        |

| System Protection                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal clock                                                                              | Resets device in instance of runaway or corrupted code                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal clock<br>source or bus clock                                                       | Resets device in instance of runaway or corrupted code     Helps protect in case of clock loss with independent clock source                                                                                                                                                                                                                                                                                                                                                                                     |

| source or bus clock  • Low voltage detection with reset or interrupt                                                                                                                 | Helps protect in case of clock loss with independent clock source     Allows system to write/save important variables before voltage drops to low     Holds devices in reset until reliable voltage levels are reapplied to the part                                                                                                                                                                                                                                                                             |

| source or bus clock  • Low voltage detection with reset or interrupt  • Illegal opcode and illegal address detection with reset                                                      | Helps protect in case of clock loss with independent clock source     Allows system to write/save important variables before voltage drops to low     Holds devices in reset until reliable voltage levels are reapplied to the part     Resets device in instance of runaway or corrupted code                                                                                                                                                                                                                  |

| source or bus clock  • Low voltage detection with reset or interrupt                                                                                                                 | Helps protect in case of clock loss with independent clock source     Allows system to write/save important variables before voltage drops to low     Holds devices in reset until reliable voltage levels are reapplied to the part                                                                                                                                                                                                                                                                             |

| source or bus clock  • Low voltage detection with reset or interrupt  • Illegal opcode and illegal address detection with reset                                                      | Helps protect in case of clock loss with independent clock source     Allows system to write/save important variables before voltage drops to low     Holds devices in reset until reliable voltage levels are reapplied to the part     Resets device in instance of runaway or corrupted code                                                                                                                                                                                                                  |

| source or bus clock  Low voltage detection with reset or interrupt  Illegal opcode and illegal address detection with reset  Security feature for flash                              | Helps protect in case of clock loss with independent clock source     Allows system to write/save important variables before voltage drops to low     Holds devices in reset until reliable voltage levels are reapplied to the part     Resets device in instance of runaway or corrupted code     Helps prevent unauthorized access to memory to protect valuable software intellectual property      Provides single-wire debugging and emulation interface     Eliminates need for expensive emulation tools |

| source or bus clock  Low voltage detection with reset or interrupt  Illegal opcode and illegal address detection with reset  Security feature for flash  Background Debugging System | Helps protect in case of clock loss with independent clock source  Allows system to write/save important variables before voltage drops to low Holds devices in reset until reliable voltage levels are reapplied to the part  Resets device in instance of runaway or corrupted code  Helps prevent unauthorized access to memory to protect valuable software intellectual property  Provides single-wire debugging and emulation interface                                                                    |

Learn More:

For current information about Freescale products and documentation, please visit www.freescale.com.