# Am2965/Am2966

Octal Dynamic Memory Drivers with Three-State Outputs

#### DISTINCTIVE CHARACTERISTICS

- Controlled rise and fall characteristics Internal resistors provide symmetrical drive to HIGH and LOW states, eliminating need for external series resistor.

- Output swings designed to drive 16K and 64K RAMs

- $V_{OH}$  guaranteed at  $V_{CC}$  -1.15V. Undershoot going LOW guaranteed at less than 0.5V.

- Large capacitive drive capability

35mA min source or sink current at 2.0V. Propagation delays specified for 50pF and 500pF loads.

- Pin-compatible with 'S240 and 'S244

Non-inverting Am2966 replaces 74S244; inverting Am2965 replaces 74S240. Faster than 'S240/244 under equivalent load.

- No-glitch outputs

Outputs forced into OFF state during power up and down. No glitch coming out of three-state.

# **GENERAL DESCRIPTION**

The Am2965 and Am2966 are designed and specified to drive the capacitive input characteristics of the address and control lines of MOS dynamic RAMs. The unique design of the lower output driver includes a collector resistor to control undershoot on the HIGH-to-LOW transition. The upper output driver pulls up to  $V_{\rm CC}$  – 1.15V to be compatible with MOS memory and is designed to have a rise time symmetrical with the lower output's controlled fall time. This allows optimization of Dynamic RAM performance.

The Am2965 and Am2966 are pin-compatible with the popular 'S240 and 'S244 with identical 3-state output enable controls. The Am2965 has inverting drivers and the Am2966 has non-inverting drivers.

The inclusion of an internal resistor in the lower output driver eliminates the requirement for an external series resistor, therefore reducing package count and the board area required. The internal resistor controls the output fall and undershoot without slowing the output rise.

These devices are designed for use with the Am2964 Dynamic Memory Controller where large dynamic memories with highly capacitive input lines require additional buffering. Driving eight address lines or four RAS and four CAS lines with drivers on the same silicon chip also provides a significant performance advantage by minimizing skew between drivers. Each device has specified skew between drivers to improve the memory access worst case timing over the min and max tpD difference of unspecified devices.

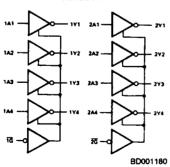

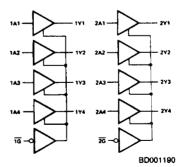

#### **BLOCK DIAGRAM**

Am2965

### Am2966

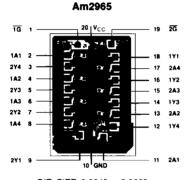

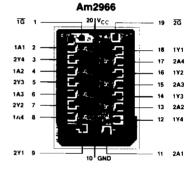

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation

#### Am2965

| Inputa |   | Outputs |

|--------|---|---------|

| G A    |   | Υ       |

| Н      | Х | Z       |

| L      | Н | L       |

| LLL    |   | H       |

Am2966

| Inputs |   | Outputs |

|--------|---|---------|

| Ğ      | A | Y       |

| Н      | Х | Z       |

| L      | L | L       |

| L      | Н | - Н     |

CD004870

## **METALLIZATION AND PAD LAYOUT**

DIE SIZE 0.094" x 0.060"

DIE SIZE 0.094" x 0.066"

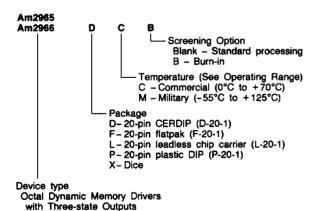

## **ORDERING INFORMATION**

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Combinations |                                                               |  |  |  |  |

|--------------------|---------------------------------------------------------------|--|--|--|--|

| Am2965<br>Am2966   | PC<br>DC, DCB, DM,<br>DMB<br>FM, FMB<br>LC, LM, LMB<br>XC, XM |  |  |  |  |

### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

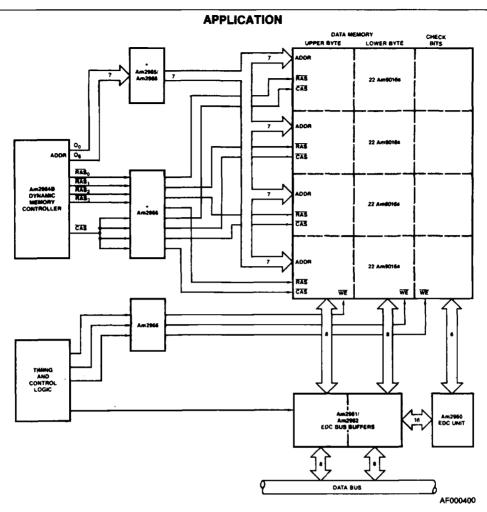

\*Address and RAS/CAS drivers each drive 22 RAM inputs at each output. Timing skew is minimized by using one device for address lines and one device for RAS/CAS, spreading the CAS loading over four drivers to equalize the capacitive load on each driver.

# DYNAMIC MEMORY CONTROL WITH ERROR DETECTION AND CORRECTION

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C Temperature (Ambient) |

|---------------------------------------------------------|

| Under Bias55°C to +125°C                                |

| Supply Voltage to Ground Potential                      |

| Continous0.5V to +7.0V                                  |

| DC Voltage Applied to Outputs For                       |

| High Output State0.5V to V <sub>CC</sub> Max            |

| DC Input Voltage0.5V to +7.0V                           |

| DC Output Current, Into Outputs200mA                    |

| DC Input Current30mA to +5.0mA                          |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

| Commercial (C) Devices               |                          |

|--------------------------------------|--------------------------|

| Temperature                          | 0°C to +70°C             |

| Supply Voltage                       | + 4.75V to + 5.25V       |

| Military (M) Devices                 |                          |

| Temperature                          | 55°C to +125°C           |

| Supply Voltage                       | +4.5V to +5.5V           |

| Operating ranges define those limits | over which the function- |

| ality of the device is guaranteed.   |                          |

# DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters       | Descriptions                             |          | Test Conditions (Note 1)                                                      |                                       | Min                         | Typ<br>(Note 2)       | Max  | Units |

|------------------|------------------------------------------|----------|-------------------------------------------------------------------------------|---------------------------------------|-----------------------------|-----------------------|------|-------|

| V <sub>OH</sub>  | Output HIGH Volta                        | ige      | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OH</sub> = -1mA                | V <sub>CC</sub> -1.15       | V <sub>CC</sub> -0.7V |      | Volts |

| M                | Outrook LOW Make                         |          | V <sub>CC</sub> = MIN                                                         | I <sub>OL</sub> = 1mA                 |                             |                       | 0.5  | Volts |

| VOL              | Output LOW Volta                         | ge       | VIN = VIH or VIL                                                              | I <sub>OL</sub> = 12mA                |                             |                       | 0.8  |       |

| VIH              | Input HIGH Level                         |          | Guaranteed input logical HIGH voltage for all inputs                          |                                       | 2.0                         |                       |      | Volts |

| VIL              |                                          |          | Guaranteed input logical LOW voltage for all inputs                           |                                       |                             |                       | 0.8  | Volts |

| Vį               | Input Clamp Voltage                      |          | VCC = MIN, IIN = -18m                                                         | 1A                                    | 1                           |                       | -1.2 | Volts |

|                  |                                          |          |                                                                               | DATA                                  |                             |                       | -200 |       |

| IĮĽ              | Input LOW Curren                         | t        | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4V                                 | TG, 2G                                |                             |                       | -400 | μΑ    |

| Iн               | Input HIGH Current                       |          | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7V                                 |                                       | 1                           |                       | 20   | μΑ    |

| f)               | Input HIGH Current Vo                    |          | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0V                                 |                                       |                             |                       | 0.1  | mA    |

| lozh             | Off-State Current V <sub>O</sub> = 2.7V  |          | V <sub>O</sub> = 2.7V                                                         |                                       |                             |                       | 100  | μΑ    |

| <sup>‡</sup> OZL | Off-State Current V <sub>O</sub> = 0.4V  |          |                                                                               | 1                                     |                             | -200                  | μA   |       |

| lor              | Output Sink Curre                        | nt       | t V <sub>OL</sub> = 2.0V                                                      |                                       | 50                          | ·                     |      | mA    |

| ЮН               | Output Source Cu                         | rrent    | V <sub>OH</sub> = 2.0V                                                        | V <sub>OH</sub> = 2.0V                |                             |                       |      | mA    |

| Isc              | Output Short Circuit Current<br>(Note 3) |          | V <sub>CC</sub> = MAX                                                         |                                       | -60<br>(see I <sub>OH</sub> |                       | -200 | mA    |

| lcc              | Supply Current .                         |          | All Outputs HIGH                                                              | V <sub>CC</sub> = MAX<br>Outputs Open |                             | 24                    | 50   |       |

|                  |                                          | Am2965   | All Outputs LOW                                                               |                                       |                             | 86                    | 125  | ]     |

|                  |                                          |          | All Outputs Hi-Z                                                              |                                       |                             | 86                    | 125  | mA.   |

|                  |                                          | All Outp | All Outputs HIGH                                                              |                                       |                             | 53                    | 75   |       |

|                  |                                          | Am2966   | All Outputs LOW                                                               | V <sub>CC</sub> = MAX                 |                             | 92                    | 130  | 1     |

|                  |                                          |          | All Outputs Hi-Z                                                              |                                       |                             | 116                   | 150  | 1     |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Range for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

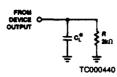

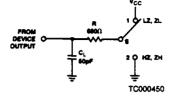

## SWITCHING TEST CIRCUIT

\*tpd specified at C = 50 and 500pF.

Figure 1. Capacitive Load Switching.

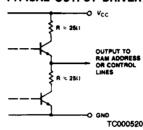

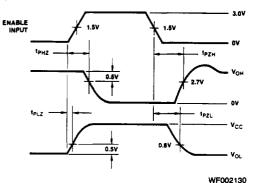

Figure 2. Three-State Enable/Disable.

## TYPICAL OUTPUT DRIVER

# SWITCHING CHARACTERISTICS (TA = +25°C, VCC = 5.0V)

| <b>Parameters</b>                                 | Description                                    | Test Condit                            | Test Conditions        |    | Тур  | Max              | Units |

|---------------------------------------------------|------------------------------------------------|----------------------------------------|------------------------|----|------|------------------|-------|

|                                                   |                                                |                                        | C <sub>L</sub> = 0pF   |    | 6    | (Note 4)         |       |

| t <sub>PLH</sub>                                  | Propagation Delay Time from LOW-to-HIGH Output | 1                                      | C <sub>L</sub> = 50pF  | 6  | 9    | 15               | ns    |

| EOW-IO-Mari Output                                | Figure 1 Test Circuit                          | C <sub>L</sub> = 500pF                 | 18                     | 22 | 30   |                  |       |

|                                                   |                                                | Figure 3 Voltage Levels and Waveforms  | C <sub>L</sub> = 0pF   |    | 4    | (Note 4)         | ns    |

| tPHL Propagation Delay Time<br>HIGH-to-LOW Output | Propagation Delay Time from                    |                                        | C <sub>L</sub> = 50pF  | 5  | 7    | 15               |       |

|                                                   | That Pio-Eon Cupat                             |                                        | C <sub>L</sub> = 500pF | 18 | 22   | 30               |       |

| †PLZ                                              | Output Disable Time from                       | Figures 2 and 4, S = 1                 |                        |    | 11   | 50               |       |

| †PHZ                                              | LOW, HIGH                                      | Figures 2 and 4, S = 2                 |                        |    | 6.5  | 12               | ns    |

| <sup>t</sup> PZL                                  | Output Enable Time from                        | Figures 2 and 4, S = 1                 |                        |    | 12   | 20               |       |

| <sup>†</sup> РZH                                  | LOW, HIGH Figures 2 and 4, S = 2               |                                        |                        |    | 12   | 20               | ns    |

| <sup>t</sup> SKEW                                 | Output-to-Output Skew                          | Figures 1 and 3, C <sub>L</sub> = 50pF |                        |    | ±0.5 | ±3.0<br>(Note 5) | ns    |

| VONP                                              | Output Voltage Undershoot                      | Figures 1 and 3, C <sub>L</sub> = 50pF |                        |    | 0    | -0.5             | Volts |

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified (Note 6)

|                          |                           |                       |                            | COMMERCIAL |      | MILITARY |      |       |

|--------------------------|---------------------------|-----------------------|----------------------------|------------|------|----------|------|-------|

| Parameters               | Description               | Test Conditions       |                            | Min        | Max  | Min      | Max  | Units |

|                          | Propagation Delay Time    |                       | C <sub>L</sub> = 50pF      | 4          | 17   | 4        | 20   | ns    |

|                          | LOW-to-HIGH Output        | Figures 1 and 3       | C <sub>L</sub> = 500pF     | 18         | 35   | 18       | 40   |       |

| . Propagation Delay Time |                           | C <sub>L</sub> = 50pF | 4                          | 17         | 4    | 20       |      |       |

| TPHL .                   | tPHL HIGH-to-LOW Output   | Figures 1 and 3       | C <sub>L</sub> = 500pF     | 18         | 35   | 18       | 40   | ns    |

| telz                     | Output Disable Time from  | Simusa O and 4        | S = 1                      |            | 24   |          | 24   | ns    |

| <sup>t</sup> PHZ         | LOW, HIGH                 | Figures 2 and 4       | S = 2                      |            | 16   |          | 16   |       |

| tpzL                     | Output Enable Time from   | Figures 2 and 4       | S = 1                      |            | 28   |          | 28   | ns    |

| tрzн                     | LOW, HIGH                 | rigures 2 and 4       | S = 2                      |            | 28   |          | 28   |       |

| VONP                     | Output Voltage Undershoot | Figures 1 and 3, C    | Figures 1 and 3, CL = 50pF |            | -0.5 |          | -0.5 | Volts |

Notes: 4. Typical time shown for reference only - not tested.

5. Time Skew specification is guaranteed by design but not tested.

6. AC performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9.

7.  $T_C = -55$  to +125°C for Flatpak versions.

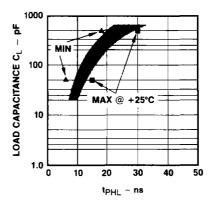

# TYPICAL SWITCHING CHARACTERISTICS

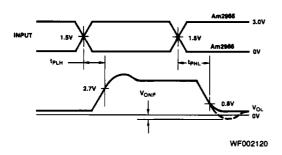

### **VOLTAGE WAVEFORMS**

$t_f = t_f = 2.5 \text{ns}$  f = 2.5 MHz $t_{DW} = 200 \text{ns}$

Figure 3. Output Drive Levels.

The RAM Driver symmetrical output design offers significant improvement over a standard Schottky output by providing a balanced drive output impedance (\*25 $\Omega$  both HIGH and LOW), and by pulling up to MOS VOH levels (VCC – 1.5V). External resistors, not required with the RAM Driver, protect standard Schottky drivers from error causing undershoot but also slow the output rise by adding to the internal R.

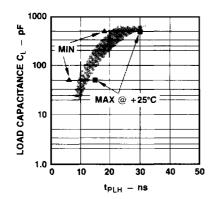

Figure 5.  $t_{PLH}$  for  $V_{OH} = 2.7$  Vol vs.  $C_L$ .

$t_{\Gamma} = t_{f} = 2.5 \text{ns}$  f = 1 MHz $t_{DW} = 800 \text{ns}$

Figure 4. Three-State Control Levels.

The RAM Driver is optimized to drive LOW at maximum speed based on safe undershoot control and to drive HIGH with a symmetrical speed characteristic. This is an optimum approach, because the dominant RAM loading characteristic is input capacitance.

The curves shown below provide performance characteristics typical of both the inverting (Am2965) and non-inverting (Am2966) RAM Drivers.

Figure 6. tpHL for Vol = 0.8 Volts vs. CL.

The curves above depict the typical tPLH and tPHL for the RAM Driver outputs as a function of load capacitance. The minimums and maximums are shown for worst case design. The typical band is provided as a guide for intermediate capacitive loads.