# DIGITAL AMPLIFIER POWER STAGE

#### **Features**

- PVDD range from 10.8V to 16.5V

- Support single-ended input audio PWM (AD) modulated signal

- Support differential input audio PWM (AD & BD) modulated signal

- Loudspeaker output power for stereo (BTL)

- 10W x 2CH @ THD+N=0.4% into  $8\Omega$  at 15V

- 8W x 2CH @ THD+N=8.4% into 8Ω at 12V

- Loudspeaker output power for mono (BTL)

- 20W x 1CH @ THD+N=0.45% into  $8\Omega$  at 15V

- Over-temperature protection

- Over-current protection

- Under-voltage detection

- Error report

- Built-in anti-pop function

- 24-pin E-TSSOP thermally-enhanced package

#### **Applications**

- TV audio

- DVD Receiver

- Home Theaters

#### **Description**

The AD9256H is a high performance stereo digital amplifier power stage. It can deliver 10W x 2CH output power into  $8\Omega$  loudspeaker for stereo or 20W x 1ch output power into  $4\Omega$  loudspeaker for mono in BTL configuration within <1% THD+N at 15V supply.

A patented, built-in anti-pop function can reduce the speaker's pop noise without requiring complex anti-pop sequence in PWM input.

The AD9256H's chip is integrated with over-temperature, over-current, and under-voltage protection circuits. These additions safeguard the AD9256H against fault conditions that could damage the chip and system catastrophically.

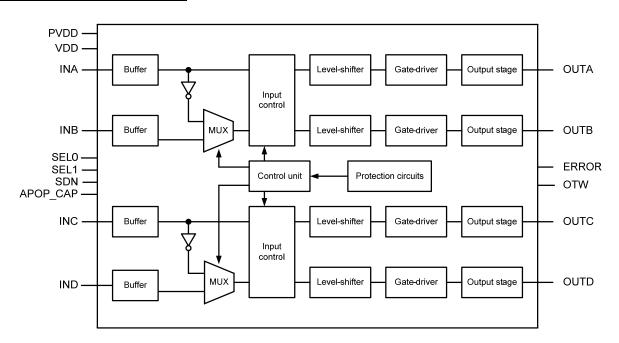

#### **Functional Block Diagram**

Publication Date: Jan. 2011 Revision: 1.1 1/21

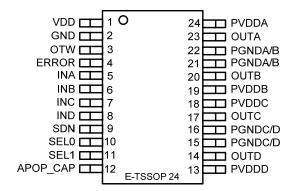

### **Pin Assignments**

## **Pin Description**

| PIN | NAME     | TYP | DESCRIPTION                                                       |

|-----|----------|-----|-------------------------------------------------------------------|

| 1   | VDD      | Р   | Power supply for digital circuit                                  |

| 2   | GND      | Р   | Ground for digital circuit                                        |

| 3   | OTW      | 0   | Over temperature warning.                                         |

| 4   | ERROR    | 0   | Error pointer                                                     |

| 5   | INA      | I   | PWM input A                                                       |

| 6   | INB      | I   | PWM input B                                                       |

| 7   | INC      | I   | PWM input C                                                       |

| 8   | IND      | I   | PWM input D                                                       |

| 9   | SDN      | I   | Shutdown (active-low) with soft pulled resistor 100kohm to ground |

| 10  | SEL0     | I   | Mode select pin 0                                                 |

| 11  | SEL1     | I   | Mode select pin 1                                                 |

| 12  | APOP_CAP | 0   | Anti-pop capacitor                                                |

| 13  | PVDDD    | Р   | Power supply for half bridge D                                    |

| 14  | OUTD     | 0   | Half-bridge output D                                              |

| 15  | PGNDC/D  | Р   | Ground for half bridge C/D                                        |

| 16  | PGNDC/D  | Р   | Ground for half bridge C/D                                        |

| 17  | OUTC     | 0   | Half-bridge output C                                              |

| 18  | PVDDC    | Р   | Power supply for half bridge C                                    |

| 19  | PVDDB    | Р   | Power supply for half bridge B                                    |

| 20  | OUTB     | 0   | Half-bridge output B                                              |

| 21  | PGNDA/B  | Р   | Ground for half bridge A/B                                        |

| 22  | PGNDA/B  | Р   | Ground for half bridge A/B                                        |

| 23  | OUTA     | 0   | Half-bridge output A                                              |

| 24  | PVDDA    | Р   | Power supply for half bridge A                                    |

Publication Date: Jan. 2011 Revision: 1.1 **2/21**