DS3130-1.0

# 2 MBIT PCM SIGNALLING CIRCUIT

# MJ1445

# TIMESLOT ZERO RECEIVER

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

The MJ1445 establishes synchronisation by detecting the synchronising word when it is received at the remote end of the transmission system. The MJ1444 has been designed to generate this synchronisation word at the sending end of the system in accordance with CCITT recommendation G732.

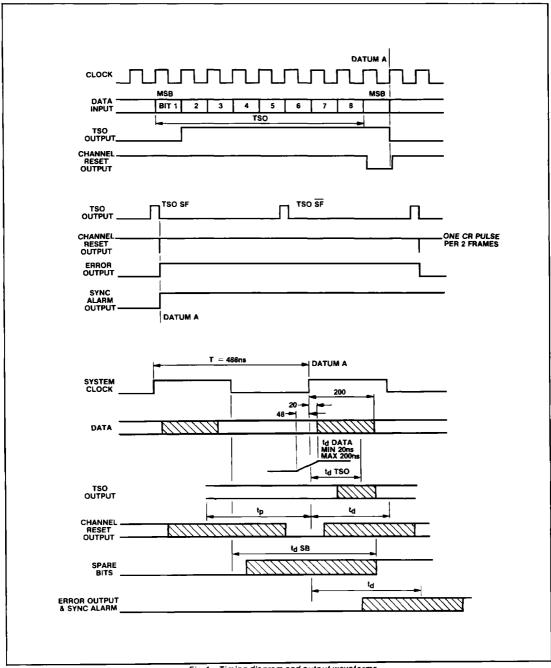

Corruption of individual synchronisation words is signified by an 'Error' output, loss of synchronisation is indicated by a 'Sync Alarm' output and follows CCITT G732 in that loss of synchronism is assumed when 3 consecutive synchronisation words have been received with errors.

The 'Channel Reset' output goes low for the first period of the clock after time slot 0 in sync frames whenever the MJ1445 has established that the receiver terminal is in synchronisation in order that the rest of the receiver terminal may be reset.

The 'TSO' output is high for a period of 8 bits starting from the end of the first bit of the synchronising word. The spare data bits from the synchronising word are provided as parallel outputs.

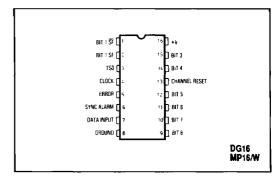

Fig.1 Pin connections

### **FEATURES**

- 5V ±5% Supply 20 mA Typical.

- Conforms to CCITT Recommendation G732

- Synchronising Word Error Monitor

- Out of Sync. Alarm

- All Inputs and Outputs are TTL Compatible

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### **Electrical Ratings**

+Vcc Inputs

Vcc + 0.5V Gnd - 0.3V

Vcc. Gnd -- 0.3V Outputs

# **Thermal Ratings**

Max Junction Temperature 175°C

Thermal Resistance: Chip to Case Chip to Amb

35°C/Watt 120°C/Watt

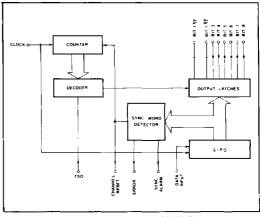

Fig.2 Block diagram MJ1445

#### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated):

Supply voltage,  $V_{CC} = 5V \pm 0.25V$

Ambient temperature, T<sub>amb</sub> = -10°C to +70°C

# Static Characteristics

| Characteristic                                     | Symbol                             | Pins                                         | Value |      |      | 11-10- | -                                                        |

|----------------------------------------------------|------------------------------------|----------------------------------------------|-------|------|------|--------|----------------------------------------------------------|

|                                                    |                                    |                                              | Min.  | Typ. | Max. | Units  | Conditions                                               |

| Low level input voltage                            | V <sub>IL</sub>                    | 4, 7                                         | -0.3  |      | 0.8  |        |                                                          |

| Low level input current } High level input current | I <sub>IN</sub>                    | 4, 7                                         |       | 1    | 50   | μΑ     |                                                          |

| High level input voltage                           | V <sub>IH</sub>                    | 4, 7                                         | 2.4   |      | νœ   | v      |                                                          |

| Low level output voltage                           | $V_{OL}$                           | 1, 2, 3, 5, 6<br>9, 10, 11, 12<br>13, 14, 15 |       |      | 0.5  | v      | I <sub>sınk</sub> = 2 mA                                 |

| High level output voltage<br>Supply current        | V <sub>он</sub><br>I <sub>сс</sub> |                                              | 2.8   | 20   | 40   | mA     | I <sub>source</sub> = 200 μA<br>V <sub>CC</sub> = 5.25 V |

#### **Dynamic Characteristics**

| Characteristic                                                                | Symbol  | Value |      |      | 1 lastin | O dial            |  |

|-------------------------------------------------------------------------------|---------|-------|------|------|----------|-------------------|--|

|                                                                               |         | Min.  | Тур. | Max. | Units    | Conditions        |  |

| Max. clock frequency                                                          | fmax    | 2.2   |      |      | MHz      |                   |  |

| Input delay of data input                                                     | td data | 20    |      | 200  | ns       | fclock = 2.048MHz |  |

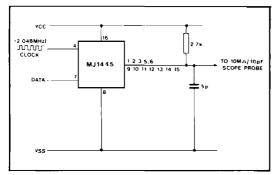

| Propagation delay, clock to TS0 output                                        | ta TSO  | 40    |      | 200  | ns       | Fig.3             |  |

| Propagation delay clock to error output, sync alarm and CH. Reset output high | ta      | 50    |      | 400  | ns       | Fig.3             |  |

| Propagation delay, clock to CH. Reset output low $(T - t_p)$                  | t₽      | 100   |      | 450  | ns       | Fig.3             |  |

| Propagation delay clock to spare bits                                         | ta sb   | 50    |      | 300  | ns       | Fig.3             |  |

Fig.3 Test conditions, all outputs

# **FUNCTIONAL DESCRIPTION**

#### Functions listed by pin number

# 1. Blt 1 SF

This output is set to the level of data bit 1 during time slot 0 of non sync frames. The data becomes true on the first falling edge of the clock during TS1.

# 2. Bit 1 SF

This output is set to the level of data bit 1 during time slot 0 of sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 3 TS0

This output provides a positive pulse of 8 clock periods in every frame starting from the end of the first bit of the synchronising word of the received data.

#### 4. Clock

System clock input (2.048 MHz for a 2 MBit PCM system).

#### 5.Error

This output goes high at the end of time slot 0 in the 2nd sync frame following the frame with sync word errors. If consecutive sync words occur with errors this output will remain high. If a sync alarm is generated this output will remain high until sync is regained.

### 6. Sync Alarm

This output goes high at the end of time slot 0 output in the 3rd consecutive sync frame containing sync word errors. It returns low at the end of TS0 output in the 3rd consecutive frame received correctly (sync and non sync).

# 7. Data Input

Serial data (2MBit/s) at this input is clocked through the SIPO shift register and examined by the sync word detector.

## 8. GND

Zero volts

# 9, 10, 11, 12, 14, 15. Bits 3 to 8

These parallel outputs are set to the level of the spare data bits (3 to 8) of time slot 0 of non sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 13. Channel reset

This output goes low for the first period of the clock after time slot 0 of the received data as long as synchronisation has been established. This pulse can be used to reset the rest of the receiver terminal.

# 16. V<sub>CC</sub>

Positive supply 5V ±5%.

Fig.4 Timing diagram and output waveforms