# **ADSD-1410S** Dual 14-Bit, 10MSPS Sampling A/D Converter

# FEATURES

- 14-bit resolution; 10MSPS sampling rate

- Functionally complete; ±2.5V input range

- No missing codes over full temperature range

- Edge-triggered

- ±5V supplies, 1.6 Watts

- 76dB SNR, -83dB THD

- Ideal for both time and frequency domain applications

# **GENERAL DESCRIPTION**

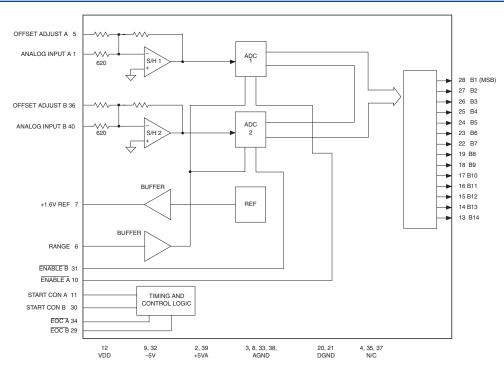

The ADSD-1410S is a functionally complete, dual 14-bit, 10MSPS, sampling A/D converter. Its standard, 40-pin, triple-wide SMT DIP contains two fast-settling sample/hold amplifiers, two 14-bit A/D converters, multiplexed output buffers, a precision reference, and all the timing and control logic necessary to operate from either two or a single start convert pulse.

The ADSD-1410S is optimized for wideband frequencydomain applications and is fully FFT tested. The ADSD-1410S requires only  $\pm$ 5V supplies and typically consumes 1.6 Watts. The digital output power supply is capable of directly driving 5V or 3V logic systems. Models are available in either commercial 0 to +70°C or military -55 to +125°C operating temperature ranges.

## **INPUT/OUTPUT CONNECTIONS**

| PIN | FUNCTION      | PIN | FUNCTION      |

|-----|---------------|-----|---------------|

| 1   | INPUT A       | 40  | INPUT B       |

| 2   | +5VA          | 39  | +5VA          |

| 3   | ANALOG GROUND | 38  | ANALOG GROUND |

| 4   | N.C.          | 37  | N.C.          |

| 5   | OFFSET A      | 36  | OFFSET B      |

| 6   | RANGE         | 35  | N.C.          |

| 7   | 1.6V REF      | 34  | EOC A         |

| 8   | ANALOG GROUND | 33  | ANALOG GROUND |

| 9   | -5V           | 32  | -5V           |

| 10  | ENABLE A      | 31  | ENABLE B      |

| 11  | START A       | 30  | START B       |

| 12  | VDD           | 29  | EOC B         |

| 13  | BIT 14 (LSB)  | 28  | BIT 1 (MSB)   |

| 14  | BIT 13        | 27  | BIT 2         |

| 15  | BIT 12        | 26  | BIT 3         |

| 16  | BIT 11        | 25  | BIT 4         |

| 17  | BIT 10        | 24  | BIT 5         |

| 18  | BIT 9         | 23  | BIT 6         |

| 19  | BIT 8         | 22  | BIT 7         |

| 20  | DGND          | 21  | DGND          |

Figure 1. ADSD-1410S Functional Block Diagram

# ABSOLUTE MAXIMUM RATINGS

| PARAMETERS                           | LIMITS             | UNITS |

|--------------------------------------|--------------------|-------|

| +5Vcc Supply (Pins 2, 39)            | 0 to +6            | Volts |

| -5VEE Supply (Pins 9, 32)            | 0 to –6            | Volts |

| VDD Supply (Pin 12)                  | -0.3 to (Vcc +0.3) | Volts |

| Digital Inputs (Pins 10, 11, 30, 31) | -0.3 to (VDD +0.3) | Volts |

| Analog Input (Pins 1, 40)            | ±7                 | Volts |

| Lead Temp. (10 seconds)              | +300               | С     |

### **FUNCTIONAL SPECIFICATIONS**

(TA = +25°C, VCC = +5V, VDD = +5V, VEE = -5V, 10MSPS sampling rate, Vin =  $\pm 2.5V$  and a minimum 7 minute warmup unless otherwise specified.)

| ANALOG INPUTS                                                                                                             | MIN.                     | TYP.                   | MAX.                  | UNITS                      |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|-----------------------|----------------------------|

| Input Voltage Range<br>Input Impedence<br>Input Capacitance                                                               | <br>610<br>              | ±2.5V<br>620<br>7      | <br>630<br>15         | Volts<br>Ω<br>pF           |

| DIGITAL INPUTS                                                                                                            | ·                        |                        |                       |                            |

| Logic Levels<br>Logic "1"<br>Logic "0"<br>Logic Loading "1"<br>Logic Loading "0"                                          | +2.4<br>                 | <br>                   | +0.8<br>+10<br>-10    | Volts<br>Volts<br>μΑ<br>μΑ |

| PERFORMANCE                                                                                                               |                          |                        |                       |                            |

| Integral Non-Linearity<br>+25°C (fin=10kHz)<br>0 to +70°C<br>-55 to +125°C<br>Differential Non-Linearity<br>(fin = 10kHz) |                          | ±1<br>±1<br>±2         |                       | LSB<br>LSB<br>LSB          |

| +25°C<br>0 to +70°C<br>-55 to +125°C                                                                                      | -0.99<br>-0.99<br>-0.99  | ±0.5<br>±0.5<br>±0.75  | +1.5<br>+1.5<br>+1.75 | LSB<br>LSB<br>LSB          |

| Offset Error<br>+25°C (see Figure 3)<br>0 to +70°C<br>-55 to +125°C                                                       |                          | ±0.25<br>±0.25<br>±0.5 | ±0.5<br>±0.5<br>±0.8  | %FSR<br>%FSR<br>%FSR       |

| Gain Error<br>+25°C (see Figure 3)<br>0 to +70°C<br>-55 to +125°C                                                         |                          | ±0.3<br>±0.3<br>±0.6   | ±0.6<br>±0.6<br>±0.8  | %FSR<br>%FSR<br>%FSR       |

| No Missing Codes<br>14 Bits<br>Resolution                                                                                 | -55 to +125°C<br>14 Bits |                        |                       |                            |

| OUTPUTS                                                                                                                   |                          |                        |                       |                            |

| Output Coding                                                                                                             | Offset Bin.              |                        |                       |                            |

| Logic Level<br>Logic "1" VDD = +5V<br>VDD = +3.3V                                                                         | +3.8<br>+2.48            |                        |                       | Volts<br>Volts             |

| Logic "0" VDD = +5V<br>VDD = +3.3V                                                                                        | _                        |                        | +0.5<br>+0.5          | Volts<br>Volts             |

| Logic Loading "1" VDD = +5V<br>VDD = +3.3V                                                                                |                          | <br>_                  | 8<br>4                | mA<br>mA                   |

| Logic Loading "0" VDD = +5V<br>VDD = +3.3V                                                                                | _                        | _                      | +8<br>+4              | mA<br>mA                   |

| Internal Reference<br>Voltage, +25°C<br>0 to +70°C<br>External Current                                                    | +1.5<br>+1.5<br>—        | +1.6<br>+1.6<br>—      | +1.7<br>+1.7<br>5     | Volts<br>Volts<br>mA       |

| DYNAMIC PERFORMANCE                 | MIN.  | TYP.         | MAX.  | UNITS       |

|-------------------------------------|-------|--------------|-------|-------------|

| Total Harm. Distort. (-0.5dB)       |       |              |       |             |

| dc to 500kHz                        | _     | -84          | -80   | dB          |

| 500kHz to 5MHz                      | _     | -83          | -77   | dB          |

| Signal-to-Noise Ratio               |       |              |       |             |

| (w/o distortion, -0.5dB             |       |              |       |             |

| dc to 500kHz                        | 74    | 76           | _     | dB          |

| 500kHz to 5MHz                      | 74    | 76           | _     | dB          |

| Signal-to-Noise Ratio               |       |              |       |             |

| (and distortion, -0.5dB)            |       |              |       |             |

| dc to 500kHz                        | 72    | 75           | _     | dB          |

| 500kHz to 5MHz                      | 72    | 75           | _     | dB          |

| Spurious Free Dyn. Range ①          |       |              |       |             |

| dc to 500kHz                        | -     | -87          | -82   | dB          |

| 500kHz to 5MHz                      | -     | -86          | -80   | dB          |

| wo-tone IMD                         |       |              |       |             |

| Distortion (fin = 4.85MHz,          |       |              |       |             |

| fs = 10MHz, -0.5dB)                 | _     | -80          | _     | dB          |

| nput Bandwidth (-3dB)               |       |              |       |             |

| Small Signal (-20dB input)          | _     | 14           | _     | MHz         |

| Large Signal (-0.5dB input)         | _     | 14           | _     | MHz         |

| Aperture Delay Time                 | _     | _            | ±10   | ns          |

| Aperature Uncertainty               | _     | _            | 5     | ps          |

| S/H Acq. Time, (to ±0.003%FSR)      |       |              |       |             |

| Step input                          | _     | _            | 25    | ns          |

| Feedthrough Rejection               |       |              |       |             |

| (fin = 5MHz)                        | _     | 85           | _     | dB          |

| Voise                               | _     | 250          | _     | μVrms       |

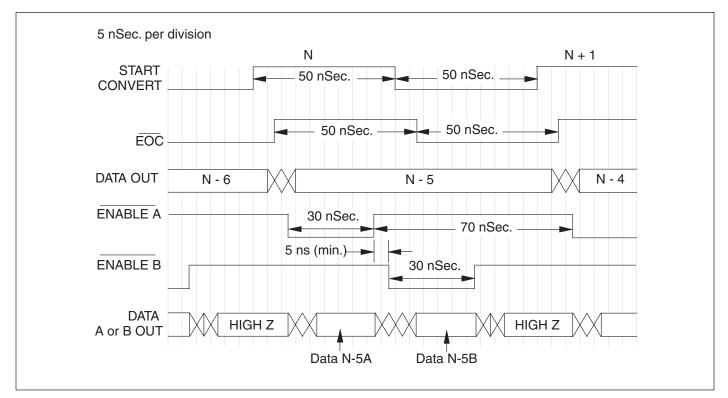

| TIMING SPECIFICATIONS               |       | 1            |       |             |

| Conversion Bate                     | 1     | _            | 10    | MHz         |

| Start Convert High                  | 25    | 50           | 500   | ns          |

| Start Convert Low                   | 25    | 50           | 500   | ns          |

| tart Convert to EOC                 | 20    | 00           | 0000  | 110         |

| Delay                               | 2     | 6            | 10    | ns          |

| EOC to Data Valid                   | -     | Ŭ            |       | 110         |

| Delay                               | 0     | 7            | 12    | ns          |

| Output Enable Delay                 | 1     | 6            | 13    | ns          |

| Output Disable Delay                | 1     | 6            | 13    | ns          |

| POWER REQUIREMENTS                  |       |              |       |             |

|                                     |       |              |       |             |

| Power Supply Ranges<br>-5VEE Supply | -5.25 | -5.0         | -4.75 | Volts       |

| +5Vcc Supply                        | -5.25 | -5.0<br>+5.0 | +5.25 | Volts       |

| VDD Supply                          | +4.75 | +5.0         | Vcc   | Volts       |

| VDD Supply                          | +3.0  | +5.0         | VCC   | VUIIS       |

| Power Supply Currents               |       |              |       |             |

| -5VEE Supply                        | -100  | -89          |       | mA          |

| +5Vcc Supply                        | -100  | +230         | +245  | mA          |

| VDD Supply                          |       | +2.0         | +5.0  | mA          |

| Power Dissipation                   |       | 1.6          | 1.7   | Watts       |

| Power Supply Rejection              |       | 1.0          | ±0.01 | %FSR%V      |

| PHYSICAL/ENVIRONMENTAL              |       |              | 10.01 | /01 011/0 V |

|                                     | -     |              |       | 1           |

| 0                                   |       | 1            |       |             |

|                                     |       |              |       |             |

| ADSD-1410S                          | 0     | —            | +70   | °C          |

| ADSD-1410S<br>ADSD-1410S-EX         | -55   | _            | +125  | °C          |

|                                     | -     |              | 1     | -           |

D

#### Footnote:

① Same specification as In-Band Harmonics and Peak Harmonics.

# **TECHNICAL NOTES**

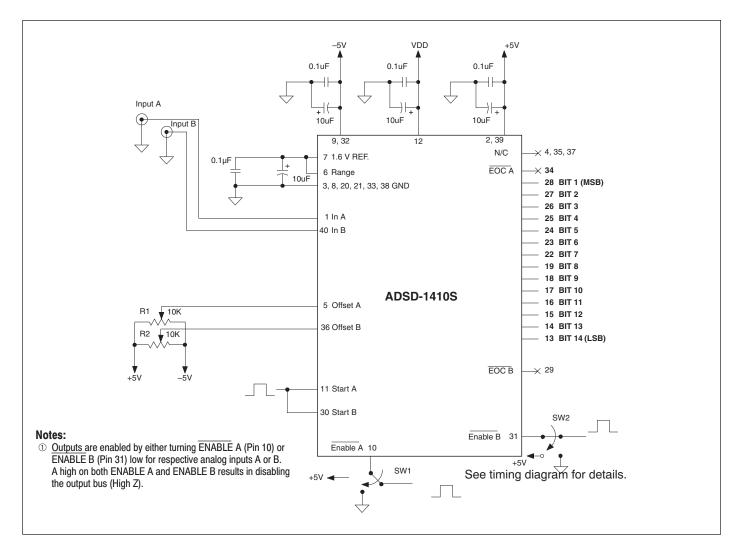

Rated performance requires using good high-frequency circuit board layout techniques. Connect the digital and analog grounds to one point, the analog ground plane beneath the converter. Due to the inductance and resistance of the power supply return paths, return the analog and digital ground separately to the power supplies.

# **CALIBRATION PROCEDURE**

- Connect the converter per Figure 3. Apply a pulse of 50 nanoseconds typical to START CONVERT (pin 11) at a rate of 2MHz. This rate is chosen to reduce flicker if LED's are used on the outputs for calibration purposes.

- 2. Zero (Offset) Adjustments

Apply a precision voltage reference source between ANALOG INPUT A (pin 1) and SIGNAL GROUND (pin 3), then adjust the reference source output per Table 2. Adjust trimpot R1 until the code flickers equally between 10 0000 0000 0000 and 10 0000 0000 0001.

3. Repeat above step for Analog Input B (Pin 40). Use trimpot R2 for the zero (Offset) adjustment .

| Table 2. | Offset | Adjustment |

|----------|--------|------------|

|----------|--------|------------|

| Input | Offset Adjust |  |

|-------|---------------|--|

| Range | +1/2 LSB      |  |

| ±2.5V | +0.000153V    |  |

#### Table 3. Output Coding

| OUTPUT CODING<br>MSB   INPUT RANGE<br>LSB   BIPOLAR<br>±2.5V   BIPOLAR<br>SCALE     11   1111   1111   +2.499695   +FS - 1LSB     11   1000   0000   0000   +1.875000   +3/4FS     11   0000   0000   +1.250000   +1/2FS     10   0000   0000   ±0.000000   0     01   0000   0000   -1.250000   -1/2FS     00   1000   0000   -1.875000   -3/4FS     00   0000   0001   -2.499695   -FS+1LSB     00   0000   0000   -2.500000   -FS |                      |                                              |                                                      |                                              |                                                                           |                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------|------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|

| 11 1000 0000 +1.875000 +3/4FS   11 0000 0000 0000 +1.250000 +1/2FS   10 0000 0000 ±0.000000 0 0   01 0000 0000 0000 -1.250000 -1/2FS   00 1000 0000 0000 -1.875000 -3/4FS   00 0000 0001 -2.499695 -FS+1LSB                                                                                                                                                                                                                          |                      |                                              |                                                      |                                              |                                                                           | =                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11<br>10<br>01<br>00 | 1000<br>0000<br>0000<br>0000<br>1000<br>0000 | 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 | 0000<br>0000<br>0000<br>0000<br>0000<br>0000 | +1.875000<br>+1.250000<br>±0.00000<br>-1.250000<br>-1.875000<br>-2.499695 | +3/4FS<br>+1/2FS<br>0<br>-1/2FS<br>-3/4FS<br>-FS+1LSB |

4. To confirm proper operation of the device, vary the precision reference voltage source to obtain the output coding listed in Table 3.

Figure 2. ADSD-1410S Timing Diagram

Figure 3. ADSD-1410S Connection Diagram

# THERMAL REQUIREMENTS

The ADSD-1410S sampling A/D converter is fully characterized and specified over the commercial operating temperature (ambient) range of 0 to  $+70^{\circ}$ C and military temperature range of -55 to  $+125^{\circ}$ C (EX suffix). All room-temperature (T<sub>A</sub> =  $+25^{\circ}$ C) production testing is performed without the use of heat sinks or forced-air cooling. Thermal impedance figures for each device are listed in their respective specification tables.

These devices do not normally require heat sinks, however, standard precautionary design and layout procedures should

be used to ensure devices do not overheat. The ground and power planes beneath the package, as well as all pcb signal runs to and from the device, should be as heavy as possible to help conduct heat away from the package. Electricallyinsulating, thermally-conductive "pads" may be installed underneath the package. Minimal air flow over the surface can greatly help reduce the package temperature.

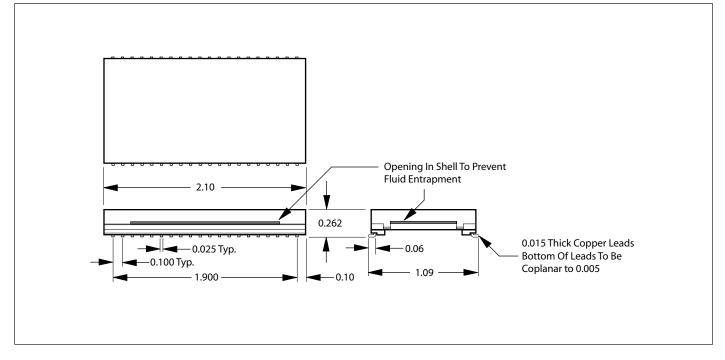

## MECHANICAL DIMENSIONS INCHES (mm)

### **ORDERING INFORMATION**

| MODEL NUMBER  | OPERATING TEMP. RANGE |

|---------------|-----------------------|

| ADSD-1410S    | 0 to +70°C            |

| ADSD-1410S-EX | –55 to +125°C         |

Contact C&D Technologies (Datel) for high-reliability versions

#### C&D Technologies (DATEL), Inc.

11 Cabot Boulevard, Mansfield, MA 02048-1151 Tel: 508.339.3000, 800.233.2765 Fax: 508.339.6356 www.cd4power.com E-mail: sales@cdtechno.com

ISO 9001:2000 REGISTERED

DS-0559A 06/06

C&D Technologies (NCL), Ltd. Milton Keynes, England Tel: +44 (0) 1908.615232 E-mail: mk@cdtechno.com C&D Technologies (DATEL) S.a.r.I. Montigny Le Bretonneux, France Tel: +33 (0) 1.34.60.01.01 E-mail: france@cdtechno.com C&D Technologies (DATEL) GmbH München, Germany Tel: +49 (0) 89.544334.0 E-mail: munich@cdtechno.com C&D Technologies KK Tokyo and Osaka, Japan Tel: +81 3.3779.1031, 6.6354.2025 E-mail: tokyo@cdtechno.com, osaka@cdtechno.com C&D Technologies (DATEL) China Shanghai, People's Republic of China Tel: +86.50273678 E-mail: shanghai@cdtechno.com

DATEL makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice. The DATEL logo is a registered DATEL, Inc. trademark.