# 4 1 1 2 三洋半導体開発ニュース"

*No.*N 6735

O2000

暫定規格

# LC864032B / 28B 24B / 20B

CMOS LSI ROM32K / 28K / 24K / 20K バイト RAM256 バイト, CRT 表示用 RAM528 バイト内蔵 8 ビット 1 チップマイクロコンピュータ

#### 概要

LC864032B / 28B / 24B / 20B は、最小バスサイクルタイム  $0.5\mu s$  で動作する CPU 部を核に、32K / 28K / 24K / 20K パイト ROM, 256 パイト RAM, 528 パイト CRT 表示用 RAM, +v プション / OSD 機能(クローズドキャプション機能の実現には LA7945 等のフロントエンド IC が必要)、16 ピットタイマ / カウンタ、10 チャネル× 7 ピット PWM, 4 チャネル× 4 ピット AD コンパータ、8 ピット同期式シリアルインタフェース、2 系統の入出力端子を内蔵した I<sup>2</sup>C パス対応シリアルインタフェース、11 要因 9 ベクタ割り込み機能等を 1 チップに集積したクローズドキャプション TV 制御用 8 ピットマイクロコンピュータです。

#### 特長

**ROM**

幅広いプログラム ROM バリエーション:32K / 28K / 24K / 20K バイト

- ・32512 x 8 ビット(LC864032B)

- ・28672 × 8 ビット(LC864028B)

- ・24576 x 8 ビット(LC864024B)

- ・20480 × 8 ビット(LC864020B)

#### RAM

- ・256 × 8 ビット

- ・528 × 8 ビット (CRT 表示用)

## CRT 表示用 RAM

フルビデオ RAM 32 文字×16 行:528×8 ビット

注意: 本製品は I<sup>2</sup>C バス・インタフェース回路を部分的に内蔵しています。ソフトウェアと組み合わせて I<sup>2</sup>C バス・インタフェースを利用することができます。

P<sup>2</sup>C バス・インタフェースを利用する場合には、プログラム ROM コードをご発注頂く時に , 事前にその旨ご申告下さい。申告に基づき , 以下の特典が受けられます。

Purchase of SANYO I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patents Rights to use these components in an I<sup>2</sup>C system, provided that the system comforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

- ■本書記載の製品は、極めて高度の信頼性を要する用途(生命維持装置、航空機のコントロールシステム等、 多大な人的・物的損害を及ぼす恐れのある用途)に対応する仕様にはなっておりません。そのような場合に は、あらかじめ三洋電機販売窓口までご相談下さい。

- ■本書記載の規格値(最大定格、動作条件範囲等)を瞬時たりとも越えて使用し、その結果発生した機器の欠陥について、弊社は責任を負いません。

www.

#### OSD 機能

- ・FCC オプション機能実現を可能

- 1)テキストモード

- 2)カラー文字表示

- 3) 小文字表示

- 4)イタリック文字表示

LC864000 シリーズ表示機能について

|     | 項目            | FCC <b>規格</b> | LC864000 | 備考     | LC864000 シリーズ機能          |

|-----|---------------|---------------|----------|--------|--------------------------|

| 1.  | テキストモード       | オプション         |          | 15 行表示 |                          |

| 2 . | キャプションモード     |               |          |        | ・最大表示文字数: 32文字×16行       |

|     | 1)ロール・アップ     |               |          | 最大4行表示 | ・キャラクタ色:8色               |

|     | 2)ポップ・オン      |               |          | 最大4行表示 | ·全背景色出力可:8色              |

|     | 3)ペイント・オン     |               |          | 最大4行表示 | ・ラウンディング                 |

|     | 4)カラー表示       | オプション         |          |        | ・キャラクタジェネレータ ROM:        |

|     | 5 ) イタリック文字表示 |               |          | // 4   | 6 × 9 ドット× 128 文字        |

|     | 6)アンダーライン表示   |               |          |        | 112 文字: キャブションスタンダード(固定) |

|     | 7)フラッシュ表示     |               |          |        | 16文字 : 任意設定可             |

| 3 . | OSD E-F       |               |          |        |                          |

|     | 1)8行/16行      |               |          |        | <b>4</b> ///             |

|     | 表示切り換え        |               |          |        |                          |

|     | 2 )標準 / 2 倍 / |               |          |        |                          |

|     | 4 倍文字表示       |               |          | JAZSIS |                          |

|     | 3 )バックグラウンド色  |               |          | 8色     | //                       |

|     | 4 )フリンジ       |               |          | 8色     |                          |

|     | (文字縁取り)       |               |          |        |                          |

<sup>\*</sup>キャプションモードを使用する際には、LA7945等のデータスライサを御使用ください。

#### 内蔵端子

- •R, G, B, BL **出力端子内蔵**

- ・外部 RGB 信号入力可能 (RI, GI, BI, BLI)

# パスサイクルタイム / 命令サイクルタイム

LC864032B / 28B / 24B / 20B は 1 命令サイクルタイムに ROM を 2 回読み出す構成のために当社の 4 ピットマイコン (LC66000 シリーズ) に比較して同じ命令サイクルタイムでも約 1.7 倍の処理能力を持ちます。 パスサイクルタイムは ROM の読み出し速度を表します。

| パスサイクルタイム | 命令サイクルタイム | システムクロック発振源            | 発振周波数  | 電源電圧       |

|-----------|-----------|------------------------|--------|------------|

| 0.5µs     | 1.0µs     | セラミック (CF) 発振          | 12MHz  | 4.5 ~ 5.5V |

| 7.5μs     | /15.0μs   | <b>内蔵</b> RC <b>発振</b> | 800kHz | 4.5 ~ 5.5V |

#### ポート

・入出力ポート : 3ポート(20本) ニブル単位で入出力指定可能なポート : 1ポート(8本) ビット単位で入出力指定可能なポート : 2ポート(12本) 15∨耐圧ポート : 1ポート(4本) ・入力ポート : 2ポート(8本) ・15∨耐圧出力ポート : 1ポート(6本)

# www.ADヨシパーラt4U.com

・4 チャネル× 4 ビット AD コンパータ

#### シリアルインタフェース

- ·I<sup>2</sup>C パス対応シリアルインタフェース

- ・8 ビットシリアルインタフェース(LSB / MSB 先頭切り換え可能)

- ・8 ビットボーレートジェネレータ内蔵

- 10 **チャネル**× 7 **ピット** PWM 出力

- PWM 専用出力端子内蔵

- ・スタティック出力可能(プログラマブル)

#### タイマ

・タイマ0:16ビットタイマ/カウンタ

2 ビットプリスケーラ + 8 ビットプログラマブルプリスケーラ内蔵

モード0: プログラマブルプリスケーラ付き8ビットタイマ×2チャネル

モード1: プログラマブルプリスケーラ付き8ピットタイマ+8ピットカウンタ

モード2: プログラマブルプリスケーラ付き 16 ビットタイマ

モード3:16 ビットカウンタ

タイマの分解能は tCYC 固定。

・ペースタイマ:クロック選択機能

システムクロック、タイマ0のプログラマブルプリスケーラ出力より選択

リモコン受信回路 (P73 / INT3 / T0IN 端子と共用)

- ・ノイズ除去機能

- ・極性切り換え機能

### ウォッチドッグタイマ

- ・RC 外付けによるウォッチドッグタイマ

- ・割り込み、システムリセットの選択可能

#### 割り込み

- ・11 要因 9 ベクタ

- (1)**外部割り込み** INT0

- (2)**外部割り込み** INT1

- (3)外部割り込み INT2, タイマ/カウンタ TOL (下位 8 ビット)

- (4)外部割り込み INT3, ベースタイマ

- (5) タイマ / カウンタ TOH (上位8 ビット)

- (6)シリアルインタフェース0(SIO0)

- $(7)I^{2}C$

- (8) キャプション / OSD (垂直同期信号割り込み)

- (9)ポート0

- ・割り込み優先レジスタ内蔵

マイコンの割り込みは低レベル,高レベル,最高レベルの3レベルの多重割り込みが可能です。外部割り込みINT2,タイマ/カウンタTOL(下位8ビット)から、ポート0の7つの割り込み要因は、割り込み優先レジスタにより低レベル,高レベルの割り込み優先が指定できます。

また、外部割り込みINT0,INT1は、低レベル、最高レベルの割り込み優先が指定できます。

## サブルーチンスタックレベル

・最大 128 レベル(スタックは RAM の中に設定)

### 高速乗除算命令内蔵

- ・16 ビット×8 ビット(実行時間:7命令サイクルタイム)

- ・16 ビット : 8 ビット (実行時間: 7 命令サイクルタイム)

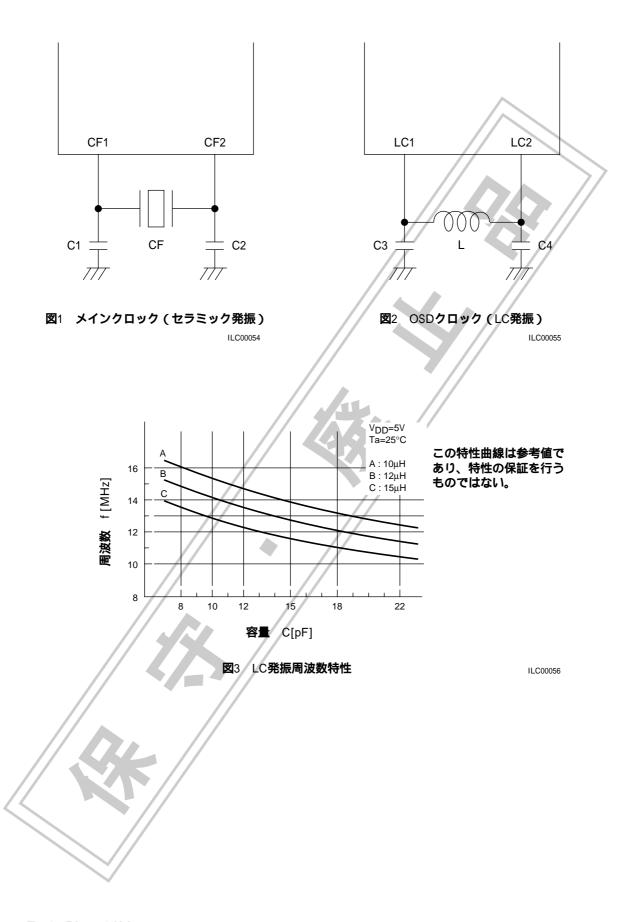

## 3種類の発振回路

・RC 発振回路(内蔵) : システムクロック用・CF 発振回路 : システムクロック用

・LC **発振回路** : CRT **同期用**

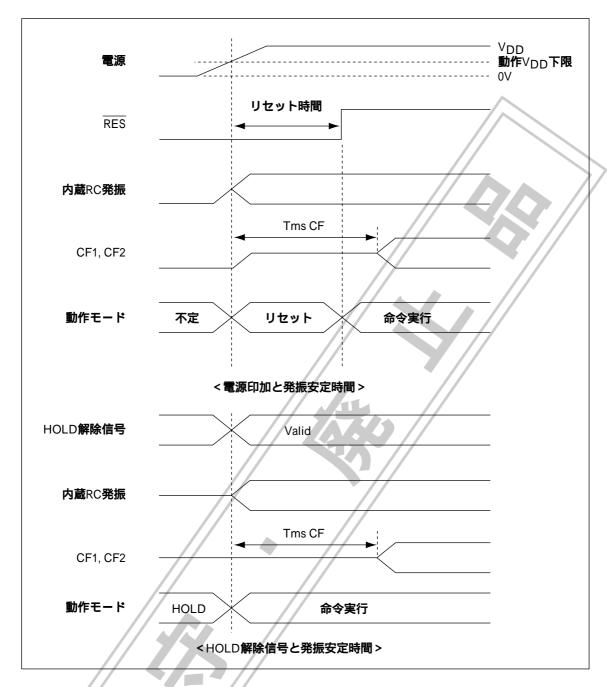

#### スタンバイ機能

·HALT **E-**

命令の実行を停止するモードであり、リセットまたは割り込みの発生により解除可能です。

·HOLD モード

CF 発振、RC 発振を停止するモードです。HOLD モードを解除するには、次の3つの方法があります。

- 1) リセット端子に'L' レベルを入力する。

- 2) P70 / INTO 端子または P71 / INT1 端子に指定されたレベルを入力する。

- 3)ポート0で割り込み条件が成立する。

## 出荷形態

• DIP52S

### 開発ツール

・エバチップ : LC864098・窓付き EPROM : LC86E4032・ワンタイム : LC86P4032

・エミュレータ : EVA86000(本体) + ECB864000(エバチップボード) + POD864000(ポッド)

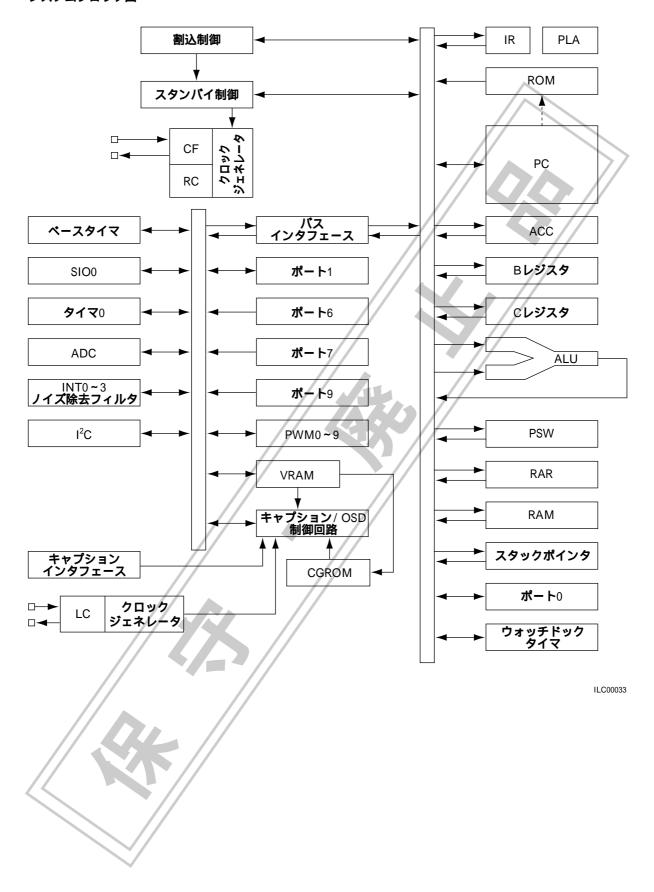

## システムブロック図

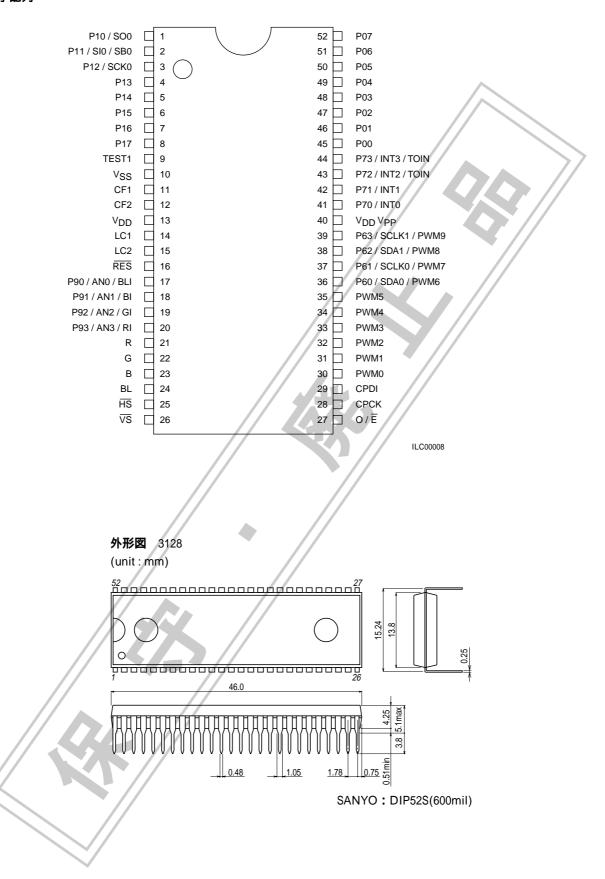

#### 端子配列

# 端子機能

| 端子名       | 番号      | 入出力    | 機能説明                               | オプション         |

|-----------|---------|--------|------------------------------------|---------------|

| TEST1     | 9       | 出力     | テスト端子(オープンで使用)                     |               |

| Vss       | 10      | -      | 電源の - 端子                           |               |

| CF1       | 11      | 入力     | セラミック発振子用入力端子                      |               |

| CF2       | 12      | 出力     | セラミック発振子用出力端子                      |               |

| VDD       | 13      | -      | 電源の+端子                             |               |

| LC1       | 14      | 入力     | LC 発振回路入力端子                        |               |

| LC2       | 15      | 出力     | LC 発振回路出力端子                        |               |

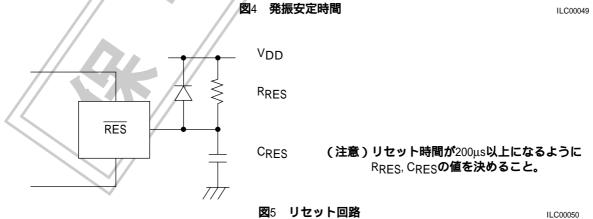

| RES       | 16      | 入力     | リセット端子                             |               |

| R         | 21      | 出力     | RGB 映像出力の赤(R)出力端子                  |               |

| G         | 22      | 出力     | RGB 映像出力の緑(G)出力端子                  | 7.57          |

| В         | 23      | 出力     | RGB <b>映像出力の青</b> (B)出力端子          |               |

| BL        | 24      | 出力     | ファストプランキング(fast blanking)制御記号      | <b>V</b> ///  |

|           |         |        | TV の映像信号とキャプション / OSD の映像信号の切り換え   |               |

| HS        | 25      | 入力     | 水平同期信号入力端子(Horizontal Sync signal) |               |

| VS        | 26      | 入力     | 垂直同期信号入力端子(Vertical Sync signal)   |               |

| O/E       | 27      | 入力     | フィールド制御端子                          |               |

|           |         |        | (キャプションデータスライサと接続)                 |               |

| CPCK      | 28      | 入力     | キャプションクロック入力端子                     |               |

|           |         |        | (キャプションデータスライサと接続)                 |               |

| CPDI      | 29      | 入力     | キャプションデータ入力端子                      |               |

|           |         |        | (キャプションデータスライサと接続)                 |               |

| PWM0 ~    | 30 ~ 35 | 出力     | PWM0 ~ 5 <b>の専用出力端子</b>            |               |

| PWM5      |         |        | 15V <b>耐圧</b>                      |               |

| VDDVPP    | 40      | -      | 電源の+端子                             |               |

| *1        |         |        |                                    |               |

| ポート0      |         |        | 8 ピットの入出力ポート                       | プルアップ抵抗       |

| P00 ~ P07 | 45 ~ 52 | 入出力    | 4 ビット単位の入出力指定可能                    | 有/無           |

|           |         | ' \_'' | HOLD 解除入力                          | 出力形式          |

|           |         |        | 割り込み入力                             | CMOS / Nch-OD |

| ポート1      |         |        | 8ピットの入出力ポート                        | 出力形式          |

| P10 ~ P17 | 1 ~ 8   | 入出力    | 1 ピット単位の入出力指定可能                    | CMOS / Nch-OD |

|           | . •     |        | 端子機能                               |               |

|           |         |        | P10 SIO0 データ出力                     |               |

|           |         | // 4   | P11 SIO0 データ入力 / パス入出力             |               |

|           |         |        | P12 SIO0 クロック入出力                   |               |

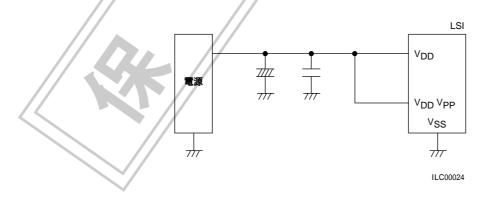

<sup>\*1</sup> VDD端子とVDDVPP端子は電気的にショートしてください。

| 端子名          | 番号      | 入出力 | 機能説明 オプション                                     |

|--------------|---------|-----|------------------------------------------------|

| ポート6         |         |     | 4 ピットの入出力ポート                                   |

| P60 ~ P63    | 36 ~ 39 | 入出力 | 1 ビット単位の入出力指定可能                                |

|              |         |     | 15V <b>耐圧</b>                                  |

|              |         |     | 端子機能                                           |

|              |         |     | P60   I <sup>2</sup> C データ入出力 / PWM6 出力        |

|              |         |     | P61   I <sup>2</sup> C <b>クロック出力</b> / PWM7 出力 |

|              |         |     | P62   I <sup>2</sup> C データ入出力 / PWM8 出力        |

|              |         |     | P63       I <sup>2</sup> C クロック出力 / PWM9 出力    |

| ポート7         |         |     | 4 ピットの入力ポート プルアップ抵抗                            |

| P70          | 41      | 入出力 | 端子機能 有/無                                       |

| P71 ~ P73    | 42 ~ 44 | 入力  | P70   INT0 入力 / HOLD 解除入力 /                    |

|              |         |     | ウォッチドッグタイマ用 Nch-Tr 出力                          |

|              |         |     | P71   INT1 入力 / HOLD 解除入力                      |

|              |         |     | P72   INT2 入力 / タイマ 0 イベント入力                   |

|              |         |     | P73   INT3 入力 ( ノイズ除去フィルタ付入力 )                 |

|              |         |     | / タイマ0イベント入力                                   |

|              |         |     | インタラプト受付形式、ベクタアドレス                             |

|              |         |     | 立 立 立 H L ベ<br>ち ち ち レ レ ク                     |

|              |         |     | 上   下 上下 ペ   ペ   ダ                             |

|              |         |     | が が が ル ル                                      |

|              |         |     | INTO × 03H                                     |

|              |         |     | INT1 × OBH                                     |

|              |         |     | INT2 × × 13H                                   |

|              |         |     | INT3 x x 1BH                                   |

| <b>ポート</b> 9 |         |     | 4 ピットの入力ポート                                    |

| P90 ~ P93    | 17 ~ 20 | 入力  | 端子機能                                           |

|              |         |     | AD 変換入力ポート (4本)                                |

|              |         |     | 外部 RGB 映像信号入力ポート                               |

|              |         | /   | P90 BLI <b>外部</b> RGB <b>映像信号入力</b>            |

|              |         |     | P91 BI <b>外部</b> RGB <b>映像信号入力</b>             |

|              |         |     | P92 GI <b>外部</b> RGB <b>映像信号入力</b>             |

|              |         | //  | P93 RI <b>外部</b> RGB <b>映像信号入力</b>             |

# リセット期間中の端子の状態

|          | 3 43 D (MR) |                    |

|----------|-------------|--------------------|

| 端子名      | 入出力モード      | オプションでプルアップオプション有  |

|          |             | 指定時のプルアップ抵抗の状態     |

| ポート 0, 7 | 入力 //       | 固定プルアップ抵抗有り        |

| ポート1     | 入力          | プログラマブルプルアップ抵抗 OFF |

# 1. **絶対最大定格** / Ta=25 , VSS=0V

| 項目        | 記号                  | 適用端子・備考            | 条件               |        | 規格    |      |                       |      |

|-----------|---------------------|--------------------|------------------|--------|-------|------|-----------------------|------|

|           | iio 🖰               | 旭川圳丁州与             | <b>ホ</b> ロ       | VDD[V] | min   | typ  | max                   | unit |

| 最大電源電圧    | VDDMAX              | VDD, VDDVPP        | ADD=ADDAbb       |        | - 0.3 | ~    | + 7.0                 | V    |

| 入力電圧      | V <sub>I</sub> (1)  | ・ポート 71, 72, 73, 9 |                  |        | - 0.3 | ~    | V <sub>DD</sub> + 0.3 |      |

|           |                     | •RES, HS, VS, CPCK |                  |        |       |      |                       |      |

|           |                     | •CPDI, O / E       |                  |        |       |      |                       |      |

| 出力電圧      | V <sub>O</sub> (1)  | R, G, B, BL        |                  |        | - 0.3 | ~    | V <sub>DD</sub> + 0.3 |      |

|           | V <sub>O</sub> (2)  | PWM0 ~ PWM5        |                  |        | - 0.3 | ~    | 15                    |      |

| 入出力電圧     | V <sub>IO</sub> (1) | ポート 0, 1, 70       |                  |        | - 0.3 | ~    | V <sub>DD</sub> + 0.3 | 7    |

|           | V <sub>IO</sub> (2) | ポート6               |                  |        | - 0.3 | 27   | 15                    |      |

| 高 ピーク出力電流 | IOPH(1)             | ポート 0, 1           | プルアップ MOS Tr. 出力 |        | - 2   |      |                       | mA   |

| レ         |                     |                    | 適用1端子当り          |        |       |      |                       |      |

| ベ         | IOPH(2)             | ポート 0, 1           | CMOS 出力          |        | - 4   | 4/   |                       |      |

| ル         |                     |                    | 適用1端子当り          |        |       | ~ // |                       |      |

| 出         | IOPH(3)             | R, G, B, BL        | CMOS 出力          |        | - 5   |      |                       |      |

| カ         |                     |                    | 適用 1 端子当り        |        |       |      |                       |      |

| 電 合計出力電流  | IOAH(1)             | ポート1               | 適用全端子合計          |        | - 10  |      |                       |      |

| 流         | IOAH(2)             | ポート0               | 適用全端子合計          |        | - 10  |      |                       |      |

|           | IOAH(3)             | R, G, B, BL        | 適用全端子合計          |        | - 12  |      |                       |      |

| 低 ピーク出力電流 | ` '                 | ポート 0, 1           | 適用 1 端子当り        |        |       |      | 20                    |      |

| レ         | IOPL(2)             | <b>ポート</b> 70      | 適用 1 端子当り        |        |       |      | 30                    |      |

| ベ         | IOPL(3)             | •R, G, B, BL       | 適用1端子当り          |        |       |      | 5                     |      |

| ル         |                     | ・ポート6              |                  |        |       |      |                       |      |

| 出         |                     | •PWM0 ~ PWM5       |                  |        |       |      |                       |      |

| 力合計出力電流   | IOAL(1)             | ポート0               | 適用全端子合計          |        |       |      | 40                    |      |

| 電         | IOAL(2)             | ポート 1, 70          | 適用全端子合計          |        |       |      | 40                    |      |

| 流         | IOAL(3)             | R, G, B, BL        | 適用全端子合計          |        |       |      | 12                    |      |

|           | IOAL(4)             | ・ポート6              | 適用全端子合計          |        |       |      | 30                    |      |

|           |                     | •PWM0 ~ PWM5       |                  |        |       |      |                       |      |

| 許容消費電力    | Pdmax               | DIP52S             | Ta= - 30 ~ + 70  |        |       |      | 430                   | mW   |

| 動作周囲温度    | Topg                |                    |                  |        | - 30  | ~    | 70                    |      |

| 保存周囲温度    | Tstg                |                    |                  |        | - 55  | ~    | 150                   |      |

2. **許容動作範囲** / Ta = - 30 ~ + 70 , VSS=0V

|                 | 記号                  | <b>油田港乙、供老</b>                                                                            | タル                                     |           | 規格                  |      |                     |      |

|-----------------|---------------------|-------------------------------------------------------------------------------------------|----------------------------------------|-----------|---------------------|------|---------------------|------|

|                 | 記ち                  | 適用端子・備考                                                                                   | 条件                                     | VDD[V]    | min                 | typ  | max                 | unit |

| 動作電源電圧          | VDD                 | VDD                                                                                       | 0.98μs tCYC<br>tCYC 1.02μs             |           | 4.5                 |      | 5.5                 | V    |

| メモリ保持電源電圧       | VHD                 | VDD                                                                                       | HOLD <b>モード時</b><br>RAM, <b>レジスタ保持</b> |           | 2.0                 |      | 5.5                 |      |

| 高レベル入力電圧        | VIH(1)              | ポート 0(シュミット)                                                                              | 出力ディセーブル                               | 4.5 ~ 5.5 | 0.6VDD              |      | VDD                 | •    |

|                 | VIH(2)              | ・ポート 1(シュミット) ・ポート 6 ・ポート 72, 73 ・HS, VS, O / E ・CPCK, CPDI ・ポート 9 外部 RGB, BL 入力          |                                        | 4.5 ~ 5.5 | 0.75VDD             |      | V <sub>DD</sub>     |      |

|                 | VIH(3)              | ・ポート 70<br>ポート入力 /<br>割り込み側<br>・ポート 71<br>・RES (シュミット)                                    | 出力 Nch Tr. オフ                          | 4.5 ~ 5.5 | 0.75V <sub>DD</sub> |      | VDD                 |      |

|                 | VIH(4)              | ポート 70<br>ウオッチドッグタイマ側                                                                     | 出力 Nch Tr. オフ                          | 4.5 ~ 5.5 | VDD<br>- 0.5        |      | VDD                 |      |

|                 | VIH(5)              | ポート9<br>ポート入力                                                                             | 1                                      | 4.5 ~ 5.5 | 0.7V <sub>DD</sub>  |      | VDD                 |      |

| 低レベル入力電圧        | V <sub>I</sub> L(1) | ポート 0(シュミット)                                                                              | 出力ディセーブル                               | 4.5 ~ 5.5 | Vss                 |      | 0.2V <sub>DD</sub>  |      |

|                 | V <sub>IL</sub> (2) | ・ポート 1(シュミット) ・ポート 6 ・ポート 72, 73 ・HS, VS, O / E ・CPCK, CPDI ・ポート 9 外部 RGB, BL 入力          | 出力ディセーブル                               | 4.5 ~ 5.5 | Vss                 |      | 0.25V <sub>DD</sub> |      |

|                 | VIL(3)              | <ul><li>・ポート70</li><li>ポート入力 /</li><li>割り込み側</li><li>・ポート71</li><li>・RES(シュミット)</li></ul> | Neh Tr. オフ                             | 4.5 ~ 5.5 | Vss                 |      | 0.25VDD             |      |

|                 | V <sub>IL</sub> (4) | ポート 70<br>ウオッチドッグタイマ側                                                                     | Nch Tr. オフ                             | 4.5 ~ 5.5 | Vss                 |      | 0.6VDD              |      |

|                 | V <sub>IL</sub> (5) | ポート9<br>ポート入力                                                                             |                                        | 4.5 ~ 5.5 | VSS                 |      | 0.3VDD              | •    |

| 命令サイクルタイム       | tCYC(1)             |                                                                                           | OSD <b>機能</b>                          | 4.5 ~ 5.5 | 0.98                | 1    | 1.02                | μs   |

|                 | tCYC(2)             |                                                                                           | OSD 機能無し                               | 4.5 ~ 5.5 | 0.98                |      | 30                  |      |

| 発振周波数範囲<br>(注1) | FmCF                | CF1, CF2                                                                                  | 12MHz セラミック発振時<br>図 1 参照               | 4.5 ~ 5.5 | 11.76               | 12   | 12.24               | MHz  |

|                 | FmLC                | LC1, LC2                                                                                  | 12.5MHz LC <b>発振</b><br>図 2 参照         | 4.5 ~ 5.5 | 11                  |      | 13.2                |      |

|                 | FmRC                |                                                                                           | 内蔵 RC 発振                               | 4.5 ~ 5.5 | 0.4                 | 0.8  | 2.0                 |      |

| 発振安定時間          | tmsCF               | CF1, CF2                                                                                  | 12MHz セラミック発振時                         |           |                     | 0.02 | 0.2                 | ms   |

| (注2)            |                     |                                                                                           | 図4参照                                   |           |                     |      |                     |      |

<sup>(</sup>注1) 発振定数は表 1,2 参照のこと。なお、LC 発振周波数はセラミック発振周波数 ± 100kHz を避けること。 WW LC 発振特性は図 3 を参考のこと。

<sup>(</sup>注2) 発振安定時間は、電源印加後、HOLD モード解除後、メインクロック発振停止解除後、発振が安定する のに必要な時間です。図4参照のこと。

3. **電気的特性** / Ta = - 30 ~ + 70 . Vss=0V

| 項目          | 記号                  | 適用端子・備考                             | 条件                              |           | 規格                    |                    |     |     |

|-------------|---------------------|-------------------------------------|---------------------------------|-----------|-----------------------|--------------------|-----|-----|

| **F         | 記つ                  |                                     | ЖIT                             | VDD[V]    | min                   | typ                | max | un  |

| 高レベル入力電流    | I <sub>I</sub> H(1) | ・ポート1                               | 出力ディセーブル                        | 4.5 ~ 5.5 |                       |                    | 1   | μΑ  |

|             |                     | ・プルアップ MOS Tr                       | プルアップ MOS Tr. オフ                |           |                       |                    |     |     |

|             |                     | 無しのポート0                             | VIN=VDD                         |           |                       |                    |     |     |

|             |                     |                                     | (出力 Tr. のオフリーク電流                |           |                       |                    |     |     |

|             |                     |                                     | を含む)                            |           |                       |                    |     |     |

|             | I <sub>I</sub> H(2) | ・プルアップ MOS Tr.                      | VIN=VDD                         | 4.5 ~ 5.5 |                       |                    | 1   |     |

|             |                     | 無しのポート7                             | 22                              |           | // ,                  |                    |     |     |

|             |                     | • Nch-MOS Tr.                       |                                 |           |                       |                    |     |     |

|             |                     | off <b>時のポート</b> 6                  |                                 |           |                       |                    | /// |     |

|             |                     | ・ポート9                               |                                 |           |                       |                    |     |     |

|             |                     | •RES                                |                                 |           |                       |                    |     |     |

|             |                     | •HS, VS, O / E                      |                                 |           |                       | 7//                |     |     |

|             |                     | • CPCK, CPDI                        |                                 |           |                       |                    |     |     |

| 低レベル入力電流    | I <sub> </sub> L(1) | ・ポート1                               | 出力ディセーブル                        | 4.5 ~ 5.5 | - 1                   |                    |     | -   |

| ルレベルハ川电ル    | 'IL(')              | ・プルアップ MOS Tr                       | ロハティ ピーフル<br>  プルアップ MOS Tr. オフ | 4.5 ~ 5.5 | <u> </u>              |                    |     |     |

|             |                     | 無しのポート0                             |                                 |           |                       |                    |     |     |

|             |                     | 無しのかートリ                             | VIN=VSS                         |           | / //                  |                    |     |     |

|             |                     |                                     | (出力 Tr. のオフリーク電流                |           |                       |                    |     |     |

|             | I (0)               | <b>- 1</b> 1 2 <b>- 1</b> 1 1 0 0 T | を含む)                            | 45 55     | // .                  |                    |     | -   |

|             | I <sub>I</sub> L(2) | ・プルアップ MOS Tr.                      | VIN=VSS                         | 4.5 ~ 5.5 | - 1                   |                    |     |     |

|             |                     | 無しのポート7                             | 4                               |           |                       |                    |     |     |

|             |                     | • Nch-MOS Tr.                       |                                 |           |                       |                    |     |     |

|             |                     | off <b>時のポート</b> 6                  |                                 |           |                       |                    |     |     |

|             |                     | ・ポート9                               |                                 |           |                       |                    |     |     |

|             | I <sub>1</sub> L(3) | •RES                                | VIN=VSS                         | 4.5 ~ 5.5 | - 1                   |                    |     |     |

|             |                     | • HS, VS, O / E                     |                                 |           |                       |                    |     |     |

|             |                     | •CPCK, CPDI                         |                                 |           |                       |                    |     |     |

| 高レベル出力電圧    | VOH(1)              | ・CMOS 出力の                           | IOH= - 1.0mA                    | 4.5 ~ 5.5 | V <sub>DD</sub> - 1   |                    |     | \ \ |

|             |                     | ポート 0, 1                            |                                 |           |                       |                    |     |     |

|             | VOH(2)              | •R, G, B, BL                        | IOH= - 0.1mA                    | 4.5 ~ 5.5 | V <sub>DD</sub> - 0.5 |                    |     |     |

| 低レベル出力電圧    | VOL(1)              | ポート 0, 1                            | IOL=10mA                        | 4.5 ~ 5.5 |                       |                    | 1.5 |     |

|             | V <sub>OL</sub> (2) | ポート 0, 1                            | • IOL=1.6mA                     | 4.5 ~ 5.5 |                       |                    | 0.4 |     |

|             | //                  |                                     | ・ポート 0, 1 <b>の合計電流</b>          |           |                       |                    |     |     |

|             | // 5                |                                     | は 40mA <b>以下の時</b>              |           |                       |                    |     |     |

|             | VOL(3)              | ・ポート6                               | • IOL=3.0mA                     | 4.5 ~ 5.5 |                       |                    | 0.4 |     |

|             |                     | •R, G, B, BL                        | ・全端子の1本当りの                      |           |                       |                    |     |     |

|             | ~                   | •PWM0 ~ PWM5                        | IOL は3mA 以下の時                   |           |                       |                    |     |     |

|             | VOL(4)              | ポート70                               | IOL=1mA                         | 4.5 ~ 5.5 |                       |                    | 0.4 |     |

| プルアップ       | Rpu                 | ・ポート 0, 1                           | VOH=0.9VDD                      | 4.5 ~ 5.5 | 13                    | 38                 | 80  | k۵  |

| MOS Tr. 抵抗  |                     | ·ポート7                               |                                 |           |                       |                    |     |     |

| 出力オフリーク電流   | IOFF(1)             | ・ポート6                               | VOUT=13.5V                      | 4.5 ~ 5.5 |                       |                    | 5   | μ   |

|             |                     | •PWM0 ~ PWM5                        |                                 |           |                       |                    |     |     |

| ヒステリシス電圧    | VHIS                | ・ポート 0, 1                           | 出力ディセーブル                        | 4.5 ~ 5.5 |                       | 0.1V <sub>DD</sub> |     | ٧   |

|             |                     | ·ポート6,7                             |                                 |           |                       |                    |     |     |

|             |                     | •RES                                |                                 |           |                       |                    |     |     |

|             |                     | • HS, VS, O / E                     |                                 |           |                       |                    |     |     |

|             |                     | •CPCK, CPDI                         |                                 |           |                       |                    |     |     |

| 端子容量        | СР                  | 全端子                                 | •f=1MHz                         | 4.5 ~ 5.5 |                       | 10                 |     | pl  |

|             |                     |                                     | ・被測定端子以外は、                      |           |                       |                    |     | '   |

| w.DataSheet | 4U.com              |                                     | VIN=VSS                         |           |                       |                    |     |     |

|             | 1                   | 1                                   | 1111 100                        | 1         |                       |                    |     | 1   |

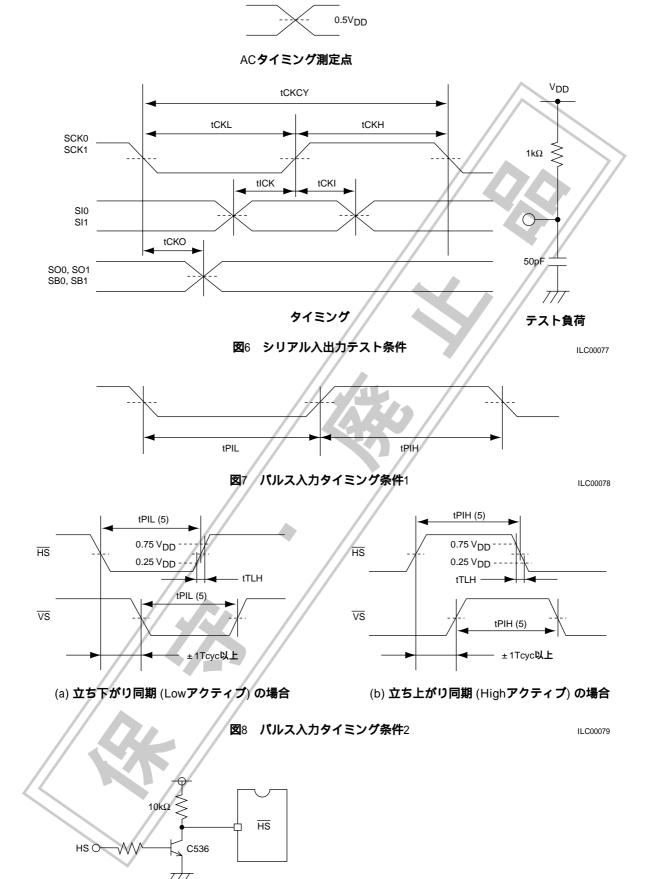

4. **シリアル入出力特性** / Ta = - 30 ~ + 70 , V<sub>SS</sub>=0V

|         | 項目                                        | 記号       | 適用端子・備考       | <br>条件               |           | 規格   |            |           |      |

|---------|-------------------------------------------|----------|---------------|----------------------|-----------|------|------------|-----------|------|

|         | 切口 ロー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |          | 旭州纳丁、湘传       | <b>水</b> 口           | VDD[V]    | min  | typ        | max       | unit |

| シス      |                                           | tCKCY(1) | •SCK0         | ・図6参照                | 4.5 ~ 5.5 | 2    |            |           | tCYC |

| ᄓ       | 低レベル                                      | tCKL(1)  | •SCLK0, SCLK1 |                      | 4.5 ~ 5.5 | 1    |            |           |      |

| アクロ     | パルス幅                                      |          |               |                      |           |      |            |           |      |

| ルーツ     | 高レベル                                      | tCKH(1)  |               |                      | 4.5 ~ 5.5 | 1 /  |            |           |      |

| クク      | パルス幅                                      |          |               |                      |           |      |            |           |      |

| 口出      |                                           | tCKCY(2) | •SCK0         | ・オープンドレイン出力時は        | 4.5 ~ 5.5 | 2    |            |           |      |

| ッカ      | 低レベル                                      | tCKL(2)  | •SCLK0, SCLK1 | 1kΩ <b>の</b> プルアップ抵抗 | 4.5 ~ 5.5 | // 🛦 | 1 / 2tCKCY |           | >    |

| クロックロッ  | パルス幅                                      |          |               | を外付けする。              |           |      |            |           |      |

|         | 高レベル                                      | tCKH(2)  |               | · 図 6 参照             | 4.5 ~ 5.5 |      | 1 / 2tCKCY | 7 //      |      |

| ク       | パルス幅                                      |          |               |                      |           |      |            |           |      |

| シデ      | - タセット                                    | tICK     | •SI0          | •SCK0, SCLK0, SCLK1  | 4.5 ~ 5.5 | 0.1  | V /        |           | μs   |

|         | 'ップ時間                                     |          | •SB0          | の立ち上がりに対し            | ľ         |      | 7//        |           |      |

| ア       |                                           |          | •SDA0         | て規定する。               |           |      |            |           |      |

| ル       |                                           |          | •SDA1         | ·図6参照                |           |      |            |           |      |

| ᄾᆝᆕ     | ・ タホ - ルド                                 | tCKI     |               |                      | 4.5 ~ 5.5 | 0.1  |            |           |      |

| 力 時     | 間                                         |          |               |                      |           | 7 // | ľ          |           |      |

| シシ      | リアルクロック                                   | tCKO(1)  | •SO0          | •SCK0, SCLK0, SCLK1  | 4.5 ~ 5.5 |      |            | 7 /12tCYC |      |

| リ が     | 外部クロック                                    |          | •SB0          | の立ち下がりに対し            |           |      |            | + 0.2     |      |

|         | の出力遅延                                     |          | •SDA0         | て規定する。               |           |      |            |           |      |

| ル 時     | 間                                         |          | •SDA1         | ・オープンドレイン出力時は        |           |      |            |           |      |

| 出   · · |                                           |          |               | 1kΩ <b>の</b> プルアップ抵抗 |           |      |            |           |      |

| カ       |                                           |          |               | を外付けする。              |           |      |            |           |      |

|         |                                           |          |               | ·図6参照                |           |      |            |           |      |

| シ       | リアルクロック                                   | tCKO(2)  | •SO0          | •SCK0, SCLK0, SCLK1  | 4.5 ~ 5.5 |      |            | 1 / 3tCYC |      |

| が       | 内部クロック                                    |          | •SB0          | の立ち下がりに対し            |           |      |            | + 0.2     |      |

| 時       | の出力遅延                                     |          | •SDA0         | て規定する。               |           |      |            |           |      |

| 時       | 間                                         |          | •SDA1         | ・オープンドレイン出力時は        |           |      |            |           |      |

|         |                                           |          | //            | 1kΩ <b>の</b> プルアップ抵抗 |           |      |            |           |      |

|         |                                           |          |               | を外付けする。              |           |      |            |           |      |

|         |                                           |          |               | · <b>図</b> 6参照       |           |      |            |           |      |

# 5. **パルス入力条件** / Ta = **-** 30 **~ +** 70 , VSS=0V

| 項目          | 記号         | 適用端子・備考         | 条件               |           | 規格   |      |     |      |

|-------------|------------|-----------------|------------------|-----------|------|------|-----|------|

|             | 心力         | 旭州坳丁、湘石         | 赤竹               | VDD[V]    | min  | typ  | max | unit |

| 高・低レベル      | tPIH(1)    | •INT0, INT1     | ・割り込み要因フラグ       | 4.5 ~ 5.5 | 1    |      |     | tCYC |

| パルス幅        | tPIL(1)    | •INT2 / T0IN    | をセットできる。         |           |      |      |     |      |

|             |            |                 | ・タイマ/カウンタ0が      |           |      |      |     |      |

|             |            |                 | パルスカウントできる。      |           |      |      |     |      |

|             | tPIH(2)    | ノイズ除去フィルタの      | ・割り込み要因フラグ       | 4.5 ~ 5.5 | 2    |      |     |      |

|             | tPIL(2)    | 時定数が1/1の        | をセットできる。         |           |      |      |     |      |

|             |            | 場合の INT3 / T0IN | ・タイマ/カウンタ0が      |           |      |      |     | 7    |

|             |            |                 | パルスカウントできる。      |           |      |      |     |      |

|             | tPIH(3)    | ノイズ除去フィルタの      | ・割り込み要因フラグ       | 4.5 ~ 5.5 | 32   |      |     |      |

|             | tPIL(3)    | 時定数が1/16の       | をセットできる。         |           |      |      |     |      |

|             |            | 場合の INT3 / T0IN | ・タイマ/カウンタ0が      |           |      | V /  |     |      |

|             |            |                 | パルスカウントできる。      |           |      | ~ // |     |      |

|             | tPIL(4)    | RES             | リセットできる。         | 4.5 ~ 5.5 | 200  |      |     | μs   |

|             | tPIH(5)    | HS, VS          | 表示位置の制御ができる。     | 4.5 ~ 5.5 | 2    |      |     | tCYC |

|             | tPIL(5)    |                 | HS, VS のアクティブエッジ |           |      |      |     |      |

|             |            |                 | は, 1tCYC 以上離れて   |           | 7 // |      |     |      |

|             |            |                 | いること。図8参照        |           |      |      |     |      |

| 立上がり / 立下がり | tTHL, tTLH | HS              | 図8参照             | 4.5 ~ 5.5 |      |      | 500 | ns   |

| 時間          |            |                 |                  |           |      |      |     |      |

# 6.AD **変換特性** / Ta = - 30 ~ + 70 , V<sub>SS</sub>=0V

| 項目       | 記号    | 適用端子・備考     | 条件                   |        | 規格  |         |         |      |

|----------|-------|-------------|----------------------|--------|-----|---------|---------|------|

|          | 10 5  | 河边圳丁、州之     | 7K T                 | VDD[V] | min | typ     | max     | unit |

| 分解能      |       |             | 7//                  |        |     | 4       |         | bit  |

| 絶対精度     |       |             |                      |        |     | ± 1 / 4 | ± 1 / 2 | LSB  |

| コンパレート   | tCAD  | Vref 選択後、変換 | 1 ビット変換時間            |        |     |         | 1.96    | μs   |

| 変換時間     |       | 結果確定まで      | =2 × tCYC            |        |     |         |         |      |

| リファレンス電流 | IREF  | //          | (ラダー抵抗を規定する)         |        |     | 1.0     | 2.0     | mA   |

| アナログ入力   | VAIN  | AN0 ~ AN3   |                      |        | Vss |         | VDD     | V    |

| 電圧範囲     |       |             |                      |        |     |         |         |      |

| アナログポート  | IAINH |             | VAIN=V <sub>DD</sub> |        |     |         | 1       | μΑ   |

| 入力電流     | IAINL |             | VAIN=VSS             |        | - 1 |         |         |      |

## 7. **消費電流特性** / Ta = - 30 ~ + 70 , VSS=0V

| 項目         | 記号         | 適用端子・備考 | 条件                 |           | 規格   |      |      |      |

|------------|------------|---------|--------------------|-----------|------|------|------|------|

|            | 10 5       | 旭加州了一桶。 | 水口                 | VDD[V]    | min  | typ  | max  | unit |

| 通常動作時消費    | IDDOP(1)   | VDD     | •FmCF=12MHz        | 4.5 ~ 5.5 |      | 15   | 25   | mA   |

| 電流 (注4)    |            |         | セラミック発振時           |           |      |      |      |      |

|            |            |         | •FmLC=12.5MHz      |           |      |      |      |      |

|            |            |         | LC 発振時             |           |      |      |      |      |

|            |            |         | ・システムクロックは12MHz 側  |           |      |      |      |      |

|            |            |         | ・内蔵 RC 発振は停止       |           |      |      |      |      |

| HALT E - F | IDDHALT(1) | VDD     | •HALT <b>モード</b>   | 4.5 ~ 5.5 |      | 5    | 10   | mΑ   |

| 消費電流(注4)   |            |         | •FmCF=12MHz        |           |      |      |      |      |

|            |            |         | セラミック発振時           |           |      |      | 7 // |      |

|            |            |         | •FmLC=0Hz          |           |      |      |      |      |

|            |            |         | (発振停止)             |           |      | V /  |      |      |

|            |            |         | ・システムクロックは12MHz側   | r I       |      | ~ // |      |      |

|            |            |         | ・内蔵 RC 発振は停止       |           |      |      |      |      |

|            | IDDHALT(2) | VDD     | • HALT <b>モード</b>  | 4.5 ~ 5.5 |      | 400  | 800  | μΑ   |

|            |            |         | •FmCF=0MHz         |           |      |      |      |      |

|            |            |         | (発振停止)             |           | 7 // |      |      |      |

|            |            |         | •FmLC=0Hz          |           |      |      |      |      |

|            |            |         | (発振停止)             |           |      |      |      |      |

|            |            |         | ・システムクロックは内蔵 RC    |           |      |      |      |      |

| HOLD E - F | IDDHOLD(1) | VDD     | ·HOLD <b>E = F</b> | 4.5 ~ 5.5 |      | 0.05 | 20   | μΑ   |

| 消費電流(注4)   | IDDHOLD(2) |         | ・全発振停止             |           |      |      |      |      |

<sup>(</sup>注4) 消費電流は出力 Tr. および プルアップ MOS Tr. に流れる電流を含まない。

表1 セラミック発振保証定数(メインクロック)

| TO COCOOMING THE COCOO (O'TOO DO ) |     |            |      |      |  |  |

|------------------------------------|-----|------------|------|------|--|--|

| 発振の種類                              | メ-カ | 発振子        | C1   | C2   |  |  |

| 12MHz セラミック発振 ムラタ                  |     | CSA12.0MTZ | 33pF | 33pF |  |  |

|                                    |     | CSA12.0MT  | 33pF | 33pF |  |  |

|                                    |     | CST12.0MT  | 内蔵   |      |  |  |

|                                    | 京セラ | KBR-12.0M  | 22pF | 22pF |  |  |

C1, C2はK公差(±10%) SL特性を使用すること。

表2 LC 発振推奨定数 (OSD クロック)

| 発振の種類         | 1                | C3   | C4   |

|---------------|------------------|------|------|

| 12.5MHz LC 発振 | <u>-</u><br>12μΗ | 16pF | 16pF |

- (注意) ・回路パタ ンの影響を受けるので、発振に関わる部品はできるだけパタ ン長を伸ばさないように近くに 配置すること。

- ・上記以外の発振子を用いた場合には、特性を保証できない。

www.DataShc図94推奨インタフェース回路 ILC00080

- ■本書記載の製品は、定められた条件下において、記載部品単体の性能・特性・機能などを規定するものであり、お客様の製品(機器)での性能・特性・機能などを保証するものではありません。部品単体の評価では予測できない症状・事態を確認するためにも、お客様の製品で必要とされる評価・試験を必ず行って下さい。

- ■弊社は、高品質・高信頼性の製品を供給することに努めております。しかし、半導体製品はある確率で故障が生じてしまいます。この故障が原因となり、人命にかかわる事故、発煙・発火事故、他の物品に損害を与えてしまう事故などを引き起こす可能性があります。機器設計時には、このような事故を起こさないような、保護回路・誤動作防止回路等の安全設計、冗長設計・機構設計等の安全対策を行って下さい。

- ■本書記載の製品が、外国為替及び外国貿易法に定める規制貨物(役務を含む)に該当する場合、輸出する際に同法に基づく輸出許可が必要です。

- ■弊社の承諾なしに、本書の一部または全部を、転載または複製することを禁止します。

www

- ■本書に記載された内容は、製品改善および技術改良等により将来予告なしに変更することがあります。したがって、ご使用の際には、「納入仕様書」でご確認下さい。

- ■この資料の情報(掲載回路および回路定数を含む)は一例を示すもので、量産セットとしての設計を保証するものではありません。また、この資料は正確かつ信頼すべきものであると確信しておりますが、その使用にあたって第3者の工業所有権その他の権利の実施に対する保証を行うものではありません。